JP2005236108A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2005236108A JP2005236108A JP2004044617A JP2004044617A JP2005236108A JP 2005236108 A JP2005236108 A JP 2005236108A JP 2004044617 A JP2004044617 A JP 2004044617A JP 2004044617 A JP2004044617 A JP 2004044617A JP 2005236108 A JP2005236108 A JP 2005236108A

- Authority

- JP

- Japan

- Prior art keywords

- conductive layer

- electrode terminal

- case

- semiconductor device

- chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/34—Strap connectors, e.g. copper straps for grounding power devices; Manufacturing methods related thereto

- H01L2224/39—Structure, shape, material or disposition of the strap connectors after the connecting process

- H01L2224/40—Structure, shape, material or disposition of the strap connectors after the connecting process of an individual strap connector

- H01L2224/401—Disposition

- H01L2224/40135—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/40137—Connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being arranged next to each other, e.g. on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45117—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 400°C and less than 950°C

- H01L2224/45124—Aluminium (Al) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73221—Strap and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1301—Thyristor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

Abstract

【課題】 半導体装置に用いられている配線の寄生インダクタンスの低減化。

【解決手段】 絶縁基板26上に形成されている導電層28と、導電層28に形成されているIGBTチップ34と、導電層28に形成されているダイオードチップ38と、それらを包囲するケース42と、導電層28に接続されているとともにケース42外へ伸びているコレクタ電極端子54と、IGBTチップ34とダイオードチップ38に接続されているとともにケース42外へ伸びているエミッタ電極端子66を備えている。エミッタ電極端子66は、IGBTチップ34とダイオードチップ38との間を平板で架橋するとともに、その平板と導電層28が平行な位置関係で形成されている。

【選択図】 図2

【解決手段】 絶縁基板26上に形成されている導電層28と、導電層28に形成されているIGBTチップ34と、導電層28に形成されているダイオードチップ38と、それらを包囲するケース42と、導電層28に接続されているとともにケース42外へ伸びているコレクタ電極端子54と、IGBTチップ34とダイオードチップ38に接続されているとともにケース42外へ伸びているエミッタ電極端子66を備えている。エミッタ電極端子66は、IGBTチップ34とダイオードチップ38との間を平板で架橋するとともに、その平板と導電層28が平行な位置関係で形成されている。

【選択図】 図2

Description

本発明は、半導体装置の寄生インダクタンスを低減する技術に関する。

主電流が流れる半導体チップ(典型的にはIGBT(Insulated Gate Bipolar Transistor)で構成されている)と、その半導体チップがターンオフする過渡的なタイミングに、その半導体チップを逆方向へ流れようとする電流をバイパスするバイパス用半導体チップ(典型的にはダイオードで構成されている)が並列に接続された構成を備える半導体装置が知られている。この種の半導体装置は、例えば3相インバータ回路等に利用されている。その3相インバータ回路では、U相、V相、W相へ電流を出力する回路のアッパー側部とロー側部のそれぞれに半導体装置が組み込まれ、合計6個の半導体装置が利用されている。

近年、電気自動車等に利用される3相インバータ回路を大電流で扱いたいという要望が強くなってきている。この3相インバータ回路を大電流で動作させると、そのスイッチング時の電流変化率に半導体装置の配線等に起因する寄生のインダクタンスが乗じて、スパイク状のサージ電圧が大きくなるという問題が生じてくる。そこで、この半導体装置の配線に起因する寄生のインダクタンスを低減する重要性が増しており、その技術の一例が特許文献1と特許文献2に記載されている。

特開平6−45509号公報(その公報の図1参照)

特開平9−102578号公報(その公報の図1参照)

近年、電気自動車等に利用される3相インバータ回路を大電流で扱いたいという要望が強くなってきている。この3相インバータ回路を大電流で動作させると、そのスイッチング時の電流変化率に半導体装置の配線等に起因する寄生のインダクタンスが乗じて、スパイク状のサージ電圧が大きくなるという問題が生じてくる。そこで、この半導体装置の配線に起因する寄生のインダクタンスを低減する重要性が増しており、その技術の一例が特許文献1と特許文献2に記載されている。

特許文献1と特許文献2の半導体装置は、半導体チップの一方の主電極に至る配線の一部と、他方の主電極に至る配線の一部とを平行に相対向して形成し、それぞれの配線内を互いに逆方向へ電流を流すことで、その電流によって発生する磁束を相殺して寄生インダクタンスを低減する技術を利用したものである。

しかしながら、特許文献1と特許文献2のいずれの半導体装置でも、配線と半導体チップを電気的に接続するために配線の一部にアルミワイヤが用いられている。このアルミワイヤの寄生のインダクタンスの低減を図るために、特許文献1ではアルミワイヤ同士を平行に形成し、そのアルミワイヤ内を互いに逆方向の電流を流すことで対処している。しかしながら、アルミワイヤのような細線同士を平行に形成することは非常に困難であり、そのため寄生のインダクタンスの低減が十分とは言えない。また、特許文献2では平板形状の配線に対してアルミワイヤを平行に配置し、この平板内を流れる電流とアルミワイヤ内を流れる電流を互いに逆方向に流すことで寄生のインダクタンスの低減化を図っている。しかしながらアルミワイヤは所定の形状でカーブしており、平板に対して完全に平行な位置関係とはならず、寄生のインダクタンスの低減が十分とは言えない。

本発明の目的は、アルミワイヤを利用せずに、寄生インダクタンスが低減された半導体装置を提供することを目的とする。

本発明の目的は、アルミワイヤを利用せずに、寄生インダクタンスが低減された半導体装置を提供することを目的とする。

本発明の半導体装置は絶縁基板を備えている。その絶縁基板上に導電層が形成されている。その導電層に半導体チップの一方の主電極が接続されている。さらにその導電層にバイパス用半導体チップの一方の主電極が接続されている。絶縁基板と導電層と半導体チップとバイパス用半導体チップとはケースによって包囲されている。

導通確保用に第1端子部材と第2端子部材が用意されている。第1端子部材は、導電層に接続されておりケース外へ伸びている。第2端子部材は、半導体チップの他方の主電極とバイパス用の半導体チップの他方の主電極に接続されており、ケース外へと伸びている。

本発明の半導体装置の一つの特徴は、第2端子部材が半導体チップとバイパス用半導体チップとの間を平板で架橋するとともに、その平板と導電層が平行な位置関係で形成されていることである。換言すると、第2端子部材の一部を利用して、半導体チップとバイパス用半導体チップとの間を平板で架橋することで、この平板と導電層が平行な位置関係で容易に構成されることを実現している。

導通確保用に第1端子部材と第2端子部材が用意されている。第1端子部材は、導電層に接続されておりケース外へ伸びている。第2端子部材は、半導体チップの他方の主電極とバイパス用の半導体チップの他方の主電極に接続されており、ケース外へと伸びている。

本発明の半導体装置の一つの特徴は、第2端子部材が半導体チップとバイパス用半導体チップとの間を平板で架橋するとともに、その平板と導電層が平行な位置関係で形成されていることである。換言すると、第2端子部材の一部を利用して、半導体チップとバイパス用半導体チップとの間を平板で架橋することで、この平板と導電層が平行な位置関係で容易に構成されることを実現している。

上記の半導体装置の半導体チップに電流が流れる場合(オン状態)を説明する。電源の正側に第1端子部材を接続し、負側に第2端子部を接続する場合を例として説明する。半導体チップがオンすると、ケース外からケース内に向かって第1端子部材を亘って電流が流れ込む。その電流は導電層を経由して半導体チップに供給される。半導体チップを通過した電流は、第2端子部材を流れてケース外に向かって流れる。

導電層と第2端子部材が平行な位置関係に形成されており、それぞれを流れる電流もまた逆方向へ向かって流れている。したがって、この箇所で寄生のインダクタンスが低減されている。また、バイパス用半導体チップに電流が流れる場合でも、導電層と第2端子部材を逆方向へ電流が流れるために寄生のインダクタンスが低減される。

導電層と第2端子部材が平行な位置関係に形成されており、それぞれを流れる電流もまた逆方向へ向かって流れている。したがって、この箇所で寄生のインダクタンスが低減されている。また、バイパス用半導体チップに電流が流れる場合でも、導電層と第2端子部材を逆方向へ電流が流れるために寄生のインダクタンスが低減される。

第1端子部材と第2端子部材がケース外へ対向して平行に伸びていることが好ましい。

ケース内外に亘って伸びている第1端子部材と第2端子部材が、対向して平行に伸びている。このため、それぞれの端子部材を流れる電流は互いに逆方向へ向かって流れる。そのため、それぞれの電流によって発生する磁束が相殺され、この端子部材の間の寄生のインダクタンスが低減されている

特許文献2に記載されている半導体装置では、ケース外の配線に関してまで寄生インダクタンスの低減化を考慮した設計がされておらず、そのためサージ電圧を低減する効果は十分とは言えない。本発明の半導体装置では、従来構造に比して、ケース内とケース外のいずれの配線に関しても寄生のインダクタンスを低減しているために、サージ電圧の低減効果が大きい。

ケース内外に亘って伸びている第1端子部材と第2端子部材が、対向して平行に伸びている。このため、それぞれの端子部材を流れる電流は互いに逆方向へ向かって流れる。そのため、それぞれの電流によって発生する磁束が相殺され、この端子部材の間の寄生のインダクタンスが低減されている

特許文献2に記載されている半導体装置では、ケース外の配線に関してまで寄生インダクタンスの低減化を考慮した設計がされておらず、そのためサージ電圧を低減する効果は十分とは言えない。本発明の半導体装置では、従来構造に比して、ケース内とケース外のいずれの配線に関しても寄生のインダクタンスを低減しているために、サージ電圧の低減効果が大きい。

第1端子部材と第2端子部材が略矩形の平板であることが好ましい。

半導体チップとバイパス用半導体チップとを結ぶ方向に沿って第1端子部材の長手方向を配置することができる。また、それと平行に第2端子部材を配置することによって、第2端子部材により半導体チップとバイパス用半導体チップを架橋することができる。したがって、第1端子部材と第2端子部材とがケース内とケース外のいずれにおいても対向するとともに平行に伸びている。また、その第2端子部材は導電層に対しても平行な位置関係に形成されることになる。

上記の半導体装置では、第2端子部材の全領域が、第1端子部材あるいは導電層に対して平行な位置関係で対向しているために、その寄生のインダクタンスの低減効果は極めて大きい。さらに、第1端子部材と第2端子部材が直線的に形成されており、そのため半導体チップとバイパス用半導体チップに電流を供給するためのケース外からケース内に至る導通経路が、最短の距離で構成されている。導通経路が最短化されることで寄生のインダクタンスの低減に効果があるとともに、半導体装置の小型化という点でも極めて有効である。

半導体チップとバイパス用半導体チップとを結ぶ方向に沿って第1端子部材の長手方向を配置することができる。また、それと平行に第2端子部材を配置することによって、第2端子部材により半導体チップとバイパス用半導体チップを架橋することができる。したがって、第1端子部材と第2端子部材とがケース内とケース外のいずれにおいても対向するとともに平行に伸びている。また、その第2端子部材は導電層に対しても平行な位置関係に形成されることになる。

上記の半導体装置では、第2端子部材の全領域が、第1端子部材あるいは導電層に対して平行な位置関係で対向しているために、その寄生のインダクタンスの低減効果は極めて大きい。さらに、第1端子部材と第2端子部材が直線的に形成されており、そのため半導体チップとバイパス用半導体チップに電流を供給するためのケース外からケース内に至る導通経路が、最短の距離で構成されている。導通経路が最短化されることで寄生のインダクタンスの低減に効果があるとともに、半導体装置の小型化という点でも極めて有効である。

本発明によれば、アルミワイヤを利用することなく、寄生のインダクタンスが低減された半導体装置を提供することができる。

最初に実施例の主要な特徴を列記する。

(第1実施形態) 半導体チップはIGBTで構成されるものに限らず、MOSFET、サイリスタなどのスイッチング素子を適用してもよい。

(第2実施形態) 第1電極端子と第2電極端子の形状は、矩形、L字状の平板に限定されず、要はその第1電極端子と第2電極端子が平行な位置関係で対向してればよい。所定の角度でカーブしていても、屈曲していても構わない。半導体装置が使用される状況に合わせてその形状は適宜設計すればよい。なお、対向する箇所の第1電極端子と第2電極端子の幅は同一であるのが好ましい。寄生のインダクタンスの低減効果が大きくなる。さらに、その対向する距離は小さい方が好ましい。寄生のインダクタンスの低減効果がさらに大きくなる。

(第1実施形態) 半導体チップはIGBTで構成されるものに限らず、MOSFET、サイリスタなどのスイッチング素子を適用してもよい。

(第2実施形態) 第1電極端子と第2電極端子の形状は、矩形、L字状の平板に限定されず、要はその第1電極端子と第2電極端子が平行な位置関係で対向してればよい。所定の角度でカーブしていても、屈曲していても構わない。半導体装置が使用される状況に合わせてその形状は適宜設計すればよい。なお、対向する箇所の第1電極端子と第2電極端子の幅は同一であるのが好ましい。寄生のインダクタンスの低減効果が大きくなる。さらに、その対向する距離は小さい方が好ましい。寄生のインダクタンスの低減効果がさらに大きくなる。

図面を参照して以下に各実施例を詳細に説明する。

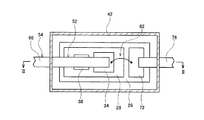

(第1実施例) 図1に第1実施例の半導体装置の模式的な水平断面図を示し、その図1中のII−II線断面図を図2に示す。図1は図2のI−I線断面に相当する。

まず、図2の断面図を参照してその構成を説明する。

図示42はプラスチック等の樹脂からなるケースであり、後述する各構成要素を包囲している。このケース42は、底面に位置する放熱板44の周縁から上方に向けて側壁が伸びるとともに、その上面を塞ぐ格好で形成されている。放熱板44は熱伝導度の大きい材料で形成されており、半導体装置を動作させたときに発生する熱をケース42の外へ逃がし易いように作用している。放熱板44は金属で構成するのが好ましい。

(第1実施例) 図1に第1実施例の半導体装置の模式的な水平断面図を示し、その図1中のII−II線断面図を図2に示す。図1は図2のI−I線断面に相当する。

まず、図2の断面図を参照してその構成を説明する。

図示42はプラスチック等の樹脂からなるケースであり、後述する各構成要素を包囲している。このケース42は、底面に位置する放熱板44の周縁から上方に向けて側壁が伸びるとともに、その上面を塞ぐ格好で形成されている。放熱板44は熱伝導度の大きい材料で形成されており、半導体装置を動作させたときに発生する熱をケース42の外へ逃がし易いように作用している。放熱板44は金属で構成するのが好ましい。

図中26は絶縁層であり、裏面には裏面側導電層24が蒸着されており、表面の一部にも導電層28が形成されている。絶縁層26は、裏面側導電層24が放熱板44に半田22によって接続固定され、ケース42に位置決めされる。

導電層28上の一部に半田32を介してIGBTチップ34(半導体チップの一例)が固定されている。このIGBTチップ34のコレクタ電極は図面下側であり、したがって、導電層28と電気的に接続している。

導電層28上の一部には、半田36を介してダイオードチップ38(バイパス用半導体チップの一例)も固定されている。このダイオードチップ38は、IGBTチップ34をターンオフした過渡的なタイミングで、そのIGBTチップ34を逆方向へ流れようとする電流をバイパスして流すように作用する。したがって、このダイオードチップ38はIGBTチップ34に対して逆並列に形成されている。したがって、ダイオードチップ38のカソードが図面下側であり、導電層28に電気的に接続している。

導電層28上の一部に半田32を介してIGBTチップ34(半導体チップの一例)が固定されている。このIGBTチップ34のコレクタ電極は図面下側であり、したがって、導電層28と電気的に接続している。

導電層28上の一部には、半田36を介してダイオードチップ38(バイパス用半導体チップの一例)も固定されている。このダイオードチップ38は、IGBTチップ34をターンオフした過渡的なタイミングで、そのIGBTチップ34を逆方向へ流れようとする電流をバイパスして流すように作用する。したがって、このダイオードチップ38はIGBTチップ34に対して逆並列に形成されている。したがって、ダイオードチップ38のカソードが図面下側であり、導電層28に電気的に接続している。

半田52を介してコレクタ電極端子54の一端が導電層28に接続している。このコレクタ電極端子54はケース42外へ伸びている。

IGBTチップ34のエミッタ電極に半田62を介してエミッタ電極端子66が接続している。このエミッタ電極端子66は半田64を介してダイオードチップ38のアノード電極にも接続している。さらにこのエミッタ電極端子66はケース外へと伸びている。

コレクタ電極端子54とエミッタ電極端子66は矩形の形状を有し、その短辺方向の幅は等しい。エミッタ電極端子66は、IGBTチップ34のエミッタ電極とダイオードチップ38のアノード電極を架橋するように形成されている。IGBTチップ34とダイオードチップ38の高さは半田32、36で等しく調整される。そのため、エミッタ電極端子66をIGBTチップ34とダイオードチップ38に接続すると、エミッタ電極端子66は導電層28の面に対して平行な位置関係に置かれ、コレクタ電極端子54に対向して平行に伸びる位置関係に調整される。したがって、コレクタ電極端子54とエミッタ電極端子66は、ケース42の外へ向けて対向するとともに平行な位置関係で形成されている。

コレクタ電極端子54とエミッタ電極端子66は、図示しないバスバーなどを介して外部の回路に接続して用いられる。コレクタ電極端子54は主電源に対して正側に接続し、エミッタ電極端子66は主電源に対して負側に接続して用いられる。

IGBTチップ34のエミッタ電極に半田62を介してエミッタ電極端子66が接続している。このエミッタ電極端子66は半田64を介してダイオードチップ38のアノード電極にも接続している。さらにこのエミッタ電極端子66はケース外へと伸びている。

コレクタ電極端子54とエミッタ電極端子66は矩形の形状を有し、その短辺方向の幅は等しい。エミッタ電極端子66は、IGBTチップ34のエミッタ電極とダイオードチップ38のアノード電極を架橋するように形成されている。IGBTチップ34とダイオードチップ38の高さは半田32、36で等しく調整される。そのため、エミッタ電極端子66をIGBTチップ34とダイオードチップ38に接続すると、エミッタ電極端子66は導電層28の面に対して平行な位置関係に置かれ、コレクタ電極端子54に対向して平行に伸びる位置関係に調整される。したがって、コレクタ電極端子54とエミッタ電極端子66は、ケース42の外へ向けて対向するとともに平行な位置関係で形成されている。

コレクタ電極端子54とエミッタ電極端子66は、図示しないバスバーなどを介して外部の回路に接続して用いられる。コレクタ電極端子54は主電源に対して正側に接続し、エミッタ電極端子66は主電源に対して負側に接続して用いられる。

図1の水平断面図に示すように、IGBTチップ34とダイオードチップ38と半田52が直線上の位置関係に配置されている。この位置関係に配置されることで、エミッタ電極端子66がIGBTチップ34とダイオードチップ38に電気的に接続するとともに、コレクタ電極端子54に対して平行な位置関係で対向することを可能にしている。また、コレクタ電極端子54とエミッタ電極端子66が、ケース42の外からケース42の内に至るまで直線に沿って形成されるために、その距離が最短となっている。半導体装置をコンパクトに構成することができる。

この半導体装置は、IGBTチップ34のオン・オフを制御するゲート電位を供給するゲート部をさらに備えている。絶縁層26上の一部にゲート用導電層72が形成されており、そのゲート用導電層72に半田74を介してゲート電極端子76の一端が接続している。このゲート電極端子76はケース42の外まで伸びており、このゲート電極端子76を介してケース42の外のゲート用電源(図示しない)からゲート電位が供給される。アルミワイヤ82はゲート用導電層72とIGBTチップ34のゲート電極を電気的に結線しており、このアルミワイヤ82を介してゲート電位はIGBTチップ34のゲート電極に供給される。

本実施例では、ゲート部は図面右側に配置されているが、このゲート部の配置位置は特に限定されず、ケース42内のどの位置に配置されていてもよい。例えば、図1に示す平面図の図面上側、あるいは図面の下側に配置されていてもよい。

図5に変形例の一例として水平断面図を示す。この半導体装置は、IGBTチップ34とダイオードチップ38の図面左右の配置位置が、図1の半導体装置とは逆に配置されている。そのため、IGBTチップ38にゲート電位を供給し易いように、ゲート部は図面上側に配置されている。このように、半導体装置の構成や半導体装置が用いられる状況に合わせて適宜設計すればよい。

本実施例では、ゲート部は図面右側に配置されているが、このゲート部の配置位置は特に限定されず、ケース42内のどの位置に配置されていてもよい。例えば、図1に示す平面図の図面上側、あるいは図面の下側に配置されていてもよい。

図5に変形例の一例として水平断面図を示す。この半導体装置は、IGBTチップ34とダイオードチップ38の図面左右の配置位置が、図1の半導体装置とは逆に配置されている。そのため、IGBTチップ38にゲート電位を供給し易いように、ゲート部は図面上側に配置されている。このように、半導体装置の構成や半導体装置が用いられる状況に合わせて適宜設計すればよい。

次に、図1の半導体装置の動作について説明する。

ゲート電極端子76を介してIGBTチップ34にゲート電位がゲート用電源から供給されると、IGBTチップ34はオン状態となる。すると主電源の正側からコレクタ電極端子54を亘って電流が供給される(図2の矢印参照)。この供給電流は半田52を通過して導電層28を図面左から図面右に向かって流れ、半田32を介してIGBTチップ34に供給される。このIGBTチップ34を通過した供給電流は、半田62を通って図面右から図面左に亘ってエミッタ電極端子66内を流れ、主電源の負側へと流れる(図2の矢印参照)。

本実施例ではまず、コレクタ電極端子54のケース42の外から内に至る箇所と、それに対応してエミッタ電極端子66がケース42の内から外に至る箇所が平行な位置関係で対向しており、さらにこの箇所を流れる電流は互いに逆方向へ流れているので、この電流によって発生する磁束は相殺される。したがって、この間の寄生のインダクタンスが低減されている。

さらに、導電層28とエミッタ電極端子66を流れる電流も、それぞれが逆方向へ向かって流れており、この箇所でも寄生のインダクタンスが低減されている。

また、このIGBTチップ34をターンオフした過渡的なタイミングで流れる逆回復電流は、ダイオードチップ38を介して上記とは逆の方向へ電流が流れるが、この場合もコレクタ電極端子54とエミッタ電極端子66との間、さらにエミッタ電極端子66と導電層28との間で寄生のインダクタンスの低減効果がある。この逆回復電流の変化率はリカバリーサージ電圧の原因となるために、この逆回復電流が流れる場合に寄生のインダクタンスが小さくなるということは、半導体装置の破壊を抑制するのに極めて有効である。

このように、本実施例の半導体装置では、エミッタ電極端子66と、コレクタ電極端子54あるいは導電層28が、全領域に亘って平行な位置関係で対向するために、その寄生のインダクタンスの低減効果は極めて大きい。さらに、IGBTチップ34あるいはダイオードチップ38のいずれを電流が流れたとしても、寄生のインダクタンスを低減することができる。

また、従来の構造のように、アルミワイヤを多く用いる必要がなく、構成が簡単化されており、製造プロセスの面でも有利である。

ゲート電極端子76を介してIGBTチップ34にゲート電位がゲート用電源から供給されると、IGBTチップ34はオン状態となる。すると主電源の正側からコレクタ電極端子54を亘って電流が供給される(図2の矢印参照)。この供給電流は半田52を通過して導電層28を図面左から図面右に向かって流れ、半田32を介してIGBTチップ34に供給される。このIGBTチップ34を通過した供給電流は、半田62を通って図面右から図面左に亘ってエミッタ電極端子66内を流れ、主電源の負側へと流れる(図2の矢印参照)。

本実施例ではまず、コレクタ電極端子54のケース42の外から内に至る箇所と、それに対応してエミッタ電極端子66がケース42の内から外に至る箇所が平行な位置関係で対向しており、さらにこの箇所を流れる電流は互いに逆方向へ流れているので、この電流によって発生する磁束は相殺される。したがって、この間の寄生のインダクタンスが低減されている。

さらに、導電層28とエミッタ電極端子66を流れる電流も、それぞれが逆方向へ向かって流れており、この箇所でも寄生のインダクタンスが低減されている。

また、このIGBTチップ34をターンオフした過渡的なタイミングで流れる逆回復電流は、ダイオードチップ38を介して上記とは逆の方向へ電流が流れるが、この場合もコレクタ電極端子54とエミッタ電極端子66との間、さらにエミッタ電極端子66と導電層28との間で寄生のインダクタンスの低減効果がある。この逆回復電流の変化率はリカバリーサージ電圧の原因となるために、この逆回復電流が流れる場合に寄生のインダクタンスが小さくなるということは、半導体装置の破壊を抑制するのに極めて有効である。

このように、本実施例の半導体装置では、エミッタ電極端子66と、コレクタ電極端子54あるいは導電層28が、全領域に亘って平行な位置関係で対向するために、その寄生のインダクタンスの低減効果は極めて大きい。さらに、IGBTチップ34あるいはダイオードチップ38のいずれを電流が流れたとしても、寄生のインダクタンスを低減することができる。

また、従来の構造のように、アルミワイヤを多く用いる必要がなく、構成が簡単化されており、製造プロセスの面でも有利である。

(第2実施例) 図3に第2実施例の半導体装置の模式的な水平断面図を示し、その図3中のIV−IV線断面図を図4に示す。図3は図4のIII−III線断面に相当する。なお、第1実施例と同一の構成要素に関しては、同一符号を付してその説明を省略する。

本実施例は、コレクタ電極端子55とエミッタ電極端子65とゲート電極端子75が、ケース42の上面側へ向けて伸びている例である。それぞれの端子をケース42の上面から引き出したい場合には、本実施例のような構成を適用すればよい。

図4に示すように、エミッタ電極端子55とコレクタ電極端子65は、ケース42の上面からケース42の外へ向かって伸びている箇所で平行な位置関係で対向しており、さらにそれぞれの電極端子を流れる電流は逆方向へ流れているために、発生する磁束は相殺されて寄生のインダクタンスが低減されている。

さらに、IGBTチップ34とダイオードチップ38を架橋する領域に対応するエミッタ電極端子65は平板で構成されており、導電層28と平行な位置関係で対向している。したがって、この箇所も寄生のインダクタンスが低減されることになる。

本実施例は、コレクタ電極端子55とエミッタ電極端子65とゲート電極端子75が、ケース42の上面側へ向けて伸びている例である。それぞれの端子をケース42の上面から引き出したい場合には、本実施例のような構成を適用すればよい。

図4に示すように、エミッタ電極端子55とコレクタ電極端子65は、ケース42の上面からケース42の外へ向かって伸びている箇所で平行な位置関係で対向しており、さらにそれぞれの電極端子を流れる電流は逆方向へ流れているために、発生する磁束は相殺されて寄生のインダクタンスが低減されている。

さらに、IGBTチップ34とダイオードチップ38を架橋する領域に対応するエミッタ電極端子65は平板で構成されており、導電層28と平行な位置関係で対向している。したがって、この箇所も寄生のインダクタンスが低減されることになる。

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

本発明では、アルミワイヤを多用しないことから、次のような効果が期待できる。まず、構成が簡単となり製造プロセスが容易である。また部品点数が低減されるために、コストの面でも効果がある。さらに、アルミワイヤを利用する従来技術では、超音波接合を利用してボンディングさせるために、半導体チップなどに損傷が生じる場合がある。本発明ではそのような問題が生じないために、半導体装置の特性の安定や歩留まりの向上という点でも効果が期待できる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

本発明では、アルミワイヤを多用しないことから、次のような効果が期待できる。まず、構成が簡単となり製造プロセスが容易である。また部品点数が低減されるために、コストの面でも効果がある。さらに、アルミワイヤを利用する従来技術では、超音波接合を利用してボンディングさせるために、半導体チップなどに損傷が生じる場合がある。本発明ではそのような問題が生じないために、半導体装置の特性の安定や歩留まりの向上という点でも効果が期待できる。

22、32、36、52、62、64、74:半田

24:裏面側導電層

26:絶縁層

28:導電層

34:IGBTチップ

38:ダイオードチップ

42:ケース

44:放熱板

54:コレクタ電極端子

66:エミッタ電極端子

72:ゲート用導電層

76:ゲート電極端子

82:アルミワイヤ

24:裏面側導電層

26:絶縁層

28:導電層

34:IGBTチップ

38:ダイオードチップ

42:ケース

44:放熱板

54:コレクタ電極端子

66:エミッタ電極端子

72:ゲート用導電層

76:ゲート電極端子

82:アルミワイヤ

Claims (3)

- 絶縁基板と、

絶縁基板上に形成されている導電層と、

導電層に一方の主電極が接続されている半導体チップと、

導電層に一方の主電極が接続されているバイパス用半導体チップと、

絶縁基板と導電層と半導体チップとバイパス用半導体チップとを包囲するケースと、

導電層に接続されているとともに、ケース外へ伸びている第1端子部材と、

半導体チップの他方の主電極とバイパス用半導体チップの他方の主電極に接続されているとともに、ケース外へ伸びている第2端子部材とを備え、

第2端子部材は、半導体チップとバイパス用半導体チップとの間を平板で架橋するとともに、その平板と導電層が平行な位置関係で形成されていることを特徴とする半導体装置。 - 前記第1端子部材と前記第2端子部材がケース外へ対向して平行に伸びていることを特徴とする請求項1の半導体装置。

- 前記第1端子部材と前記第2端子部材が略矩形の平板であることを特徴とする請求項2の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004044617A JP2005236108A (ja) | 2004-02-20 | 2004-02-20 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004044617A JP2005236108A (ja) | 2004-02-20 | 2004-02-20 | 半導体装置 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2005236108A true JP2005236108A (ja) | 2005-09-02 |

Family

ID=35018728

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004044617A Pending JP2005236108A (ja) | 2004-02-20 | 2004-02-20 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2005236108A (ja) |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007081155A (ja) * | 2005-09-14 | 2007-03-29 | Hitachi Ltd | 半導体装置 |

| JP2007329427A (ja) * | 2006-06-09 | 2007-12-20 | Honda Motor Co Ltd | 半導体装置 |

| JP2008021796A (ja) * | 2006-07-12 | 2008-01-31 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2008098308A (ja) * | 2006-10-10 | 2008-04-24 | Honda Motor Co Ltd | 半導体装置 |

| US8129836B2 (en) | 2006-06-09 | 2012-03-06 | Honda Motor Co., Ltd. | Semiconductor device |

| WO2013080698A1 (ja) | 2011-11-28 | 2013-06-06 | 日産自動車株式会社 | 電力変換装置 |

| JP2014127582A (ja) * | 2012-12-26 | 2014-07-07 | Toyota Motor Corp | 半導体モジュール |

| WO2015001727A1 (ja) * | 2013-07-03 | 2015-01-08 | 株式会社デンソー | 半導体装置 |

| US9351423B2 (en) | 2012-06-29 | 2016-05-24 | Denso Corporation | Semiconductor device and semiconductor device connection structure |

| US9379049B2 (en) | 2012-07-04 | 2016-06-28 | Panasonic Intellectual Property Management Co., Ltd. | Semiconductor apparatus |

| CN110299350A (zh) * | 2018-03-21 | 2019-10-01 | 株式会社东芝 | 半导体装置 |

-

2004

- 2004-02-20 JP JP2004044617A patent/JP2005236108A/ja active Pending

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007081155A (ja) * | 2005-09-14 | 2007-03-29 | Hitachi Ltd | 半導体装置 |

| JP2007329427A (ja) * | 2006-06-09 | 2007-12-20 | Honda Motor Co Ltd | 半導体装置 |

| US8129836B2 (en) | 2006-06-09 | 2012-03-06 | Honda Motor Co., Ltd. | Semiconductor device |

| JP2008021796A (ja) * | 2006-07-12 | 2008-01-31 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| JP2008098308A (ja) * | 2006-10-10 | 2008-04-24 | Honda Motor Co Ltd | 半導体装置 |

| WO2013080698A1 (ja) | 2011-11-28 | 2013-06-06 | 日産自動車株式会社 | 電力変換装置 |

| US9755544B2 (en) | 2011-11-28 | 2017-09-05 | Nissan Motor Co., Ltd. | Power conversion device |

| US9351423B2 (en) | 2012-06-29 | 2016-05-24 | Denso Corporation | Semiconductor device and semiconductor device connection structure |

| US9379049B2 (en) | 2012-07-04 | 2016-06-28 | Panasonic Intellectual Property Management Co., Ltd. | Semiconductor apparatus |

| JP2014127582A (ja) * | 2012-12-26 | 2014-07-07 | Toyota Motor Corp | 半導体モジュール |

| CN105359269A (zh) * | 2013-07-03 | 2016-02-24 | 株式会社电装 | 半导体装置 |

| US20160133597A1 (en) * | 2013-07-03 | 2016-05-12 | Denso Corporation | Semiconductor device |

| JP2015015301A (ja) * | 2013-07-03 | 2015-01-22 | 株式会社デンソー | 半導体装置 |

| WO2015001727A1 (ja) * | 2013-07-03 | 2015-01-08 | 株式会社デンソー | 半導体装置 |

| US9595500B2 (en) | 2013-07-03 | 2017-03-14 | Denso Corporation | Semiconductor device |

| CN105359269B (zh) * | 2013-07-03 | 2017-12-01 | 株式会社电装 | 半导体装置 |

| CN110299350A (zh) * | 2018-03-21 | 2019-10-01 | 株式会社东芝 | 半导体装置 |

| CN110299350B (zh) * | 2018-03-21 | 2023-04-11 | 株式会社东芝 | 半导体装置 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9762140B2 (en) | Semiconductor device | |

| US8461623B2 (en) | Power semiconductor module | |

| JP6366612B2 (ja) | 電力用半導体モジュール | |

| JP6288301B2 (ja) | ハーフブリッジパワー半導体モジュール及びその製造方法 | |

| JP5798412B2 (ja) | 半導体モジュール | |

| US11355477B2 (en) | Power semiconductor module and power conversion device | |

| JP6320433B2 (ja) | 電力用半導体モジュール | |

| JP6750620B2 (ja) | 半導体モジュール | |

| US11605613B2 (en) | Semiconductor device | |

| JP2019029457A (ja) | 半導体モジュール | |

| JP6603676B2 (ja) | ハーフブリッジパワー半導体モジュール及びその製造方法 | |

| US20150194372A1 (en) | Semiconductor apparatus | |

| US11923266B2 (en) | Semiconductor module circuit structure | |

| JP4853493B2 (ja) | 半導体装置 | |

| JP2005236108A (ja) | 半導体装置 | |

| JP2020009834A (ja) | 半導体装置 | |

| JP6490027B2 (ja) | 半導体装置 | |

| JP2024008998A (ja) | 電子回路、半導体モジュール及び半導体装置 | |

| JP2008306872A (ja) | 半導体装置 | |

| US20220189930A1 (en) | Module | |

| CN210516724U (zh) | 一种功率半导体模块和功率半导体器件 | |

| JP5171199B2 (ja) | パワーモジュール | |

| JP7010036B2 (ja) | 半導体モジュール | |

| JP4243043B2 (ja) | 半導体モジュール | |

| US20230170292A1 (en) | Semiconductor device |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061102 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070309 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080226 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080701 |