JP6139731B2 - 光電変換装置の作製方法 - Google Patents

光電変換装置の作製方法 Download PDFInfo

- Publication number

- JP6139731B2 JP6139731B2 JP2016057800A JP2016057800A JP6139731B2 JP 6139731 B2 JP6139731 B2 JP 6139731B2 JP 2016057800 A JP2016057800 A JP 2016057800A JP 2016057800 A JP2016057800 A JP 2016057800A JP 6139731 B2 JP6139731 B2 JP 6139731B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- silicon substrate

- type

- oxide

- photoelectric conversion

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Photovoltaic Devices (AREA)

Description

いる。その代表例としては、単結晶シリコンや多結晶シリコンなどのシリコン基板を用い

た太陽電池が知られており、その変換効率を高めるための研究開発が活発に行われている

。

。p型シリコン基板は、n型シリコン基板よりも拡散長が長く、基板内で発生した少数キ

ャリアを効率良く収集しやすい。

が、シリコン基板中にホウ素と酸素が共存していると深い準位が形成され、該準位にキャ

リアが捕獲されやすくなる。このため、ライフタイムが低下してしまう。この現象は、強

光照射時に発生することから光劣化ともいわれ、太陽電池の変換効率を低下させる一要因

となっている。

度のシリコン基板を太陽電池に用いる技術が特許文献1に開示されている。

因を有さない。さらに、シリコン基板中の不純物汚染がある場合には、電子の捕獲断面積

が正孔の捕獲断面積より大きくなるため、汚染量が十分に少なければ、正孔が少数キャリ

アであるn型シリコン基板の方がライフタイムを大きくすることができる。したがって、

最近ではn型シリコン基板を用いた太陽電池の開発も進められている。

陥の影響も強く受ける。そのため、バルク特性改善の効果を得るには、表面欠陥の低減が

重要となる。

面積が増加するため、表面欠陥の絶対量も増加してしまう。表面欠陥は表面再結合を促進

し、実効的なライフタイムを低下させる原因となる。

を更に向上させることができ、光電変換装置の電気特性を向上させることができる。特に

、前述の理由から、n型シリコン基板を用いた場合に、ライフタイムを向上させやすい。

ン層を設けた光電変換装置の作製方法を提供することを目的の一つとする。また、当該光

電変換装置を提供することを目的の一つとする。

ーション膜を設けたヘテロ接合型の光電変換装置の作製方法および当該光電変換装置に関

する。

1の工程と、シリコン基板の一方の面上に、i型またはn型の導電型を有しシリコン基板

よりもキャリア濃度の低い第1の半導体層を形成する第2の工程と、第1の半導体層上に

、n型の導電型を有しシリコン基板よりもキャリア濃度の高い第2の半導体層を形成する

第3の工程と、シリコン基板の他方の面上に、i型またはp型の導電型を有する第3の半

導体層を形成する第4の工程と、第3の半導体層上に、p型の導電型を有し第3の半導体

層よりもキャリア濃度の高い第4の半導体層を形成する第5の工程と、第4の半導体層上

に透光性導電膜を形成する第6の工程と、第2の半導体層上に第1の電極を形成する第7

の工程と、透光性導電膜上に第2の電極を形成する第8の工程と、を有し、第2の工程お

よび第4の工程は、原料ガスにアルゴンとモノシランを含み、両者の流量比X(X=アル

ゴン流量/モノシラン流量)を0<X<0.8とした条件のプラズマCVD法で行うこと

を特徴とする光電変換装置の作製方法である。

ために付すものであり、順序や数を限定するものではないことを付記する。

に第4の半導体層を形成する方法でもよい。

ことが好ましい。

リコン半導体層を用いることができる。または、第1の半導体層、第2の半導体層、第3

の半導体層をシリコン半導体層とし、第4の半導体層を酸化物半導体層としてもよい。

い。

好ましい。

、酸化モリブデン、酸化タングステン、酸化マンガン、酸化レニウムで形成することが好

ましい。

コン基板と、シリコン基板の一方の面上に形成された、i型またはn型の導電型を有し、

シリコン基板よりもキャリア濃度の低い第1の半導体層と、第1の半導体層上に形成され

た、n型の導電型を有し、第1の半導体層よりもキャリア濃度の高い第2の半導体層と、

シリコン基板の他方の面上に形成された、i型またはp型の導電型を有する第3の半導体

層と、第3の半導体層上に形成された、p型の導電型を有し、第3の半導体層よりもキャ

リア濃度の高い第4の半導体層と、第4の半導体層上に形成された透光性導電膜と、を有

し、第1の半導体層および第3の半導体層に含有されるアルゴンの濃度は、1.2×10

18atoms/cm3以上2.2×1018atoms/cm3以下であることを特徴

とする光電変換装置である。

に第4の半導体層が形成されていてもよい。

ことが好ましい。

リコン半導体層を用いることができる。または、第1の半導体層、第2の半導体層、第3

の半導体層をシリコン半導体層とし、第4の半導体層を酸化物半導体層としてもよい。

好ましい。

ることが好ましい。

、酸化モリブデン、酸化タングステン、酸化マンガン、酸化レニウムで形成されているこ

とが好ましい。

ことができ、光電変換装置の電気特性を向上させることができる。また、電気特性が良好

な光電変換装置を提供することができる。

以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれ

ば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈さ

れるものではない。なお、実施の形態を説明するための全図において、同一部分または同

様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略することがある

。

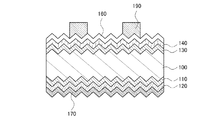

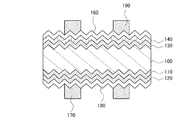

本実施の形態では、本発明の一態様における光電変換装置の構成および作製方法について

説明する。

コン基板100の一方の面上に第1の半導体層110、第2の半導体層120、第1の電

極170が順に積層され、シリコン基板100の他方の面上には、第3の半導体層130

、第4の半導体層140、透光性導電膜160、第2の電極190が順に積層された構成

を有している。なお、第2の電極190はグリッド電極であり、第2の電極190が形成

された面側が受光面となる。

成としても良い。その場合は、第4の半導体層140と第1の電極170との間に、透光

性導電膜180を設けることが好ましい。

4の半導体層140が形成される構造としてもよい。第4の半導体層140によるシリコ

ン表面のパッシベーション効果が高い場合は、第3の半導体層130を省くことができる

。

工された面では入射光が多重反射し、光電変換領域内には光が斜めに進行することから光

路長が増大する。また、裏面反射光が表面で全反射する、所謂光閉じ込め効果を起こさせ

ることもできる。

を施した構成であっても良い。凹凸加工によって上記光学的効果が得られる一方で、シリ

コン基板の表面積が増大するため、表面欠陥の絶対量が増大してしまう。したがって、光

学的効果と表面欠陥量のバランスを考慮し、より良好な電気特性が得られるように実施者

が構造を決定すればよい。

図3、および図4のそれぞれの構成を任意に複合した構成としてもよい。

できる。ただし、本発明の一態様においては、n型の単結晶シリコン基板を用いることが

好ましい。極力不純物を低減した単結晶シリコン基板においても少なからず不純物が含ま

れており、該不純物が形成する準位にキャリアは捕獲される。該不純物の濃度が十分に小

さく、かつ同程度であるp型単結晶シリコン基板およびn型単結晶シリコン基板の比較に

おいては、電子捕獲断面積が、正孔捕獲断面積より大きいため、正孔が少数キャリアとな

るn型シリコン基板の方がライフタイムは大きくなる。

シリコン基板の方が拡散長は大きい。そのため、n型単結晶シリコン基板を用いる場合に

は、拡散長を考慮して基板厚を薄くすることが好ましい。ただし、基板厚を薄くすると光

の利用効率が低下するため、短絡電流密度が低下してしまう問題がある。

極力低減することが必要となる。本発明の一態様においては、低酸素濃度のn型単結晶シ

リコン基板を用いる。例えば、酸素濃度が8×1017atoms/cm3以下、好まし

くは5×1017atoms/cm3以下、更に好ましくは3×1017atoms/c

m3以下のn型単結晶シリコン基板を用いる。ここで、単結晶シリコン中の酸素とは、格

子間酸素を指す。このような低酸素濃度のシリコンウェハは、FZ(Floating

Zone)法や、MCZ(Magnetic field applied Czoch

ralski)法などで作製することができる。また、上記酸素濃度は、フーリエ変換赤

外分光法(換算係数4.81×1017/cm2)で求めることができる。

ン半導体層を用いることができ、シリコン基板100の表面の欠陥を終端することができ

る。例えば、第1の半導体層110および第3の半導体層130には、プラズマCVD法

で形成される非晶質シリコンを用いることができる。

基板100よりもキャリア濃度の低いi型またはn型のシリコン層、第3の半導体層13

0には、i型またはp型のシリコン層を用いることができる。

置する所謂真性半導体の他、半導体に含まれるp型を付与する不純物およびn型を付与す

る不純物が共に1×1018cm−3以下の濃度であり、暗伝導度に対して光伝導度が高

い半導体を指す。

には、相対的にキャリア濃度の高いn型材料またはp型材料の導電型をn+型またはp+

型、相対的にキャリア濃度の低いn型材料またはp型材料の導電型をn−型またはp−型

と呼称する。

ることが好ましい。このとき、n−型のシリコン層の暗伝導度は、1×10−9S/cm

〜1×10−4S/cm、好ましくは1×10−8S/cm〜1×10−5S/cm、さ

らに好ましくは1×10−8S/cm〜1×10−6S/cmとする。

ることが好ましい。このとき、p−型のシリコン層の暗伝導度は、1×10−10S/c

m〜1×10−5S/cm、好ましくは1×10−9S/cm〜1×10−6S/cm、

さらに好ましくは1×10−9S/cm〜1×10−7S/cmとする。

ンを含むシリコン層を用いる。アルゴンを含む原料ガスを用いてシリコン層をパッシベー

ション層としてシリコン基板表面に形成することで、シリコン基板の表面欠陥を極力低減

させることができる。

n型単結晶シリコン基板の両面に形成したサンプルのライフタイムを示す図である。該非

晶質シリコンは、プラズマCVDを用い、反応室に原料ガス(アルゴン:モノシラン=1

:(0〜1))を導入し、反応室内の圧力を160Pa、電極間隔を17mm以下、カソ

ード電極の面積を基準とする電力密度を40mW/cm2(RF電源60MHz)、基板

温度を220℃以下とする条件で抵抗率約9Ω・cmのn型単結晶シリコン基板上に膜厚

100nmで形成している。また、ライフタイムは、μPCD(microwave d

etected photoconductivity decay)法を用いて測定し

ている。

値を有するように変化する傾向を示す。すなわち、原料ガス中のアルゴン比率には適切な

範囲があることがわかる。アルゴン添加なしで形成したサンプルを基準にすると、原料ガ

スの流量比X(X=アルゴン流量/モノシラン流量)は、0<X<0.8(0より大きく

0.8より小さい値)が好ましく、0.1≦X≦0.7(0.1以上0.7以下の値)が

より好ましく、0.1≦X≦0.6(0.1以上0.6以下の値)がさらに好ましいとい

える。

ラズマ化したモノシランからのプラズマダメージを緩和することができる。ただし、アル

ゴンを多く含む原料ガスでは、プラズマ化したアルゴン自身によっても被成膜面にプラズ

マダメージを与えるため、アルゴンは適切な上記範囲の量を添加することが好ましい。

ectrometry)を用い、ガラス基板上に非晶質シリコン層を形成したサンプルの

アルゴン(m/z=40)の挙動を調べた結果である。比較したサンプルには、モノシラ

ンのみを原料ガスとして形成したサンプルA、およびアルゴン/モノシラン=0.25の

比率の原料ガスで形成したサンプルBを用いている。サンプルAでは、アルゴンは検出さ

れず、サンプルBでは、約300℃〜500℃の昇温でアルゴンが検出されていることが

わかる。

を行い、非晶質シリコン層中のアルゴン濃度とライフタイムとの関係を調べた結果である

。なお、非晶質シリコン層中のアルゴン濃度は、TDS分析を室温(25℃)〜600℃

で行い、その間に放出されるアルゴン(m/z=40)の総量、サンプル面積、およびサ

ンプルの膜厚から算出している。また、ライフタイムは、ヨウ素アルコール溶液によるケ

ミカルパッシベーションを行ったn型の単結晶シリコン基板のライフタイムを1として規

格化した相対値で表している。

切な範囲があることがわかる。ケミカルパッシベーションのサンプルを基準にすると、膜

中のアルゴン濃度は、1.2×1018atoms/cm3以上2.2×1018ato

ms/cm3以下が好ましく、1.3×1018atoms/cm3以上2.1×101

8atoms/cm3以下がより好ましいといえる。膜中に含まれるアルゴンはシリコン

と結合を作らず、適量の場合は膜の応力緩和などの効用があり、パッシベーション層の品

質向上に作用する。ただし、膜中に含まれるアルゴンが上記値より多い場合は、膜応力を

誘発、シリコン同士の結合を阻害、不純物準位の形成などの不具合が生じることがあり、

パッシベーション層としての品質を低下させてしまう。

る不純物元素を極力低減させることが好ましい。プラズマCVD法等で形成されるシリコ

ン層などには、原料ガスが高純度であっても成膜チャンバー中に残留する大気成分やクリ

ーニングガス成分が不純物として膜中に取り込まれやすい。これらの不純物はエネルギー

ギャップ中に不純物準位を形成し、キャリアの捕獲などの悪影響を与える。

17atoms/cm3以下とすることで、その影響をほとんど排除できることが判明し

ている。また、クリーニングガスの成分であるフッ素の膜中濃度は、窒素および/または

酸素の膜中濃度以下にすることが好ましいことも判明している。

としてシリコン基板100の表面に形成することで、該シリコン基板のライフタイムを向

上させることができ、電気特性が良好な光電変換装置を形成することができる。特に、該

シリコン基板の表面に凹凸を設ける場合には、その効果が顕著となる。

もキャリア密度の高い層である。例えば、第2の半導体層120には、n型となる不純物

が添加された非晶質シリコンまたは微結晶シリコンを用いることができる。

0と第2の半導体層120との間には、第1の半導体層110を介してn−n+接合が形

成される。つまり、第2の半導体層120は、BSF層(Back Surface F

ield層)として作用する。BSF層を形成することにより、少数キャリアがp−n接

合側にはね返されることから、第1の電極170近傍でのキャリアの再結合を防止するこ

とができる。

導体層130よりもキャリア密度の高い層である。シリコン基板100がn型の場合には

、第4の半導体層140はp型(p+型)であり、シリコン基板100と第4の半導体層

140との間には、第3の半導体層130を介してp−n接合が形成される。例えば、第

4の半導体層140には、p型となる不純物が添加された非晶質シリコンまたは微結晶シ

リコンを用いることができる。

toms/cm3以下のn型単結晶シリコン基板を用いる。なお、表裏に凹凸加工を行う

場合は、単結晶シリコン基板の表面に(100)面を有する基板を用いることが好ましい

。

0)面を有する単結晶シリコン基板をシリコン基板100として用いる場合に適用できる

。シリコン基板100に多結晶シリコン基板を用いる場合は、ドライエッチング法などで

凹凸加工を行えばよい。

の表面から10〜20μmに残留するダメージ層をウエットエッチング工程にて取り除く

。エッチング液には、比較的高濃度のアルカリ溶液、例えば、10〜50%の水酸化ナト

リウム水溶液、または同濃度の水酸化カリウム水溶液を用いることができる。または、フ

ッ酸と硝酸を混合した混酸や、それらに酢酸を混合した混酸を用いても良い。

酸としては、例えば、0.5%フッ酸と1%過酸化水素水の混合液(FPM)などを用い

ることができる。またはRCA洗浄などを行っても良い。なお、この酸洗浄工程は省いて

も良い。

ングレートの違いを利用して形成する。エッチング液には比較的低濃度のアルカリ溶液、

例えば、1〜5%の水酸化ナトリウム水溶液、または同濃度の水酸化カリウム水溶液を用

いることができ、好ましくは、数%のイソプロピルアルコールを添加する。エッチング液

の温度は70〜90℃とし、30〜60分間、シリコン基板をエッチング液に浸漬する。

この処理により、シリコン基板100表面に、微細な略四角錐状の複数の凸部、および隣

接する凸部間で構成される凹部からなる凹凸を形成することができる。

均一な酸化層が形成されるため、該酸化層を取り除く。また、該酸化層にはアルカリ溶液

の成分が残存しやすいため、それを取り除く目的もある。アルカリ金属、例えばNaイオ

ンやKイオンがシリコン中に侵入するとライフタイムが劣化し、光電変換装置の電気特性

が著しく低下してしまう。なお、この酸化層を除去するには、1〜5%の希フッ酸を用い

れば良い。

コン基板100の表面をエッチングし、金属成分などの不純物を除去することが好ましい

。酢酸を混合することで、硝酸の酸化力を維持し、エッチング工程を安定にする効果、お

よびエッチングレートを調整する効果が得られる。例えば、各酸の体積比率は、フッ酸:

硝酸:酢酸=1:(1.5〜3):(2〜4)とすることができる。なお、本明細書では

、フッ酸、硝酸および酢酸の混酸液をフッ硝酢酸と呼ぶ。また、このフッ硝酢酸を用いた

エッチング工程では、凸部の頂点の断面における角度を大きくする方向に変化させること

から、表面積が低減し、表面欠陥の絶対量を低減することができる。なお、このフッ硝酢

酸を用いたエッチングを行う場合は、上述の希フッ酸を用いた酸化層の除去工程を省くこ

ともできる。ここまでの工程により、図8(A)に示すシリコン基板100の断面形状が

形成される。

第1の半導体層110を形成する。第1の半導体層110の厚さは3nm以上100nm

以下とすることが好ましい。本実施の形態において、第1の半導体層110は、アルゴン

が添加されたi型の非晶質シリコン層であり、膜厚は5nmとする。

入し、反応室内の圧力を100Pa以上200Pa以下、電極間隔を10mm以上40m

m以下、カソード電極の面積を基準とする電力密度を8mW/cm2以上120mW/c

m2以下、基板温度を150℃以上300℃以下とする条件で形成することができる。前

述したように、反応室に導入する原料ガス中のアルゴンおよびモノシランの流量比X(X

=アルゴン流量/モノシラン流量)は、0<X<0.8とすることが好ましい。なお、該

流量比率が遵守されていれば、原料ガスに水素などを加えてもよい。また、第1の半導体

層110をn−型のシリコン層とするには、上記原料ガスにホスフィンなどのn型のドー

パントを含むガスを添加すればよい。

。第2の半導体層120の厚さは3nm以上100nm以下とすることが好ましい。本実

施の形態において、第2の半導体層120はn型(n+型)の非晶質シリコンであり、膜

厚は10nmとする。

0.5%)を1:(1〜50)の流量比率で導入し、反応室内の圧力を100Pa以上2

00Pa以下とし、電極間隔を10mm以上40mm以下とし、カソード電極の面積を基

準とする電力密度を8mW/cm2以上120mW/cm2以下、基板温度を150℃以

上300℃以下とする条件で形成することができる。

130を形成する。第3の半導体層130の厚さは、3nm以上100nm以下とするこ

とが好ましい。本実施の形態において、第3の半導体層130は、アルゴンが添加された

i型の非晶質シリコン層であり、膜厚は5nmとする。

。なお、第3の半導体層130をp−型のシリコン層とするには、上記原料ガスにジボラ

ンなどのp型のドーパントを含むガスを添加すればよい。

。第4の半導体層140の厚さは3nm以上100nm以下とすることが好ましい。本実

施の形態において、第4の半導体層140はp型(p+型)の非晶質シリコンであり、膜

厚は10nmとする。

.1%)を1:(2〜50)の流量比率で導入し、反応室内の圧力を100Pa以上20

0Pa以下とし、電極間隔を8mm以上40mm以下とし、カソード電極の面積を基準と

する電力密度を8mW/cm2以上50mW/cm2以下、基板温度を150℃以上30

0℃以下とする条件で形成することができる。

解効率の良い周波数60MHzのRF電源を用いることが好ましい。原料ガスの分解効率

を上げることで、シリコン表面の未結合手を終端しやすくなる。ただし、13.56MH

z、27.12MHz、または100MHzのRF電源を用いても良い。また、連続放電

だけでなく、パルス放電にて形成を行っても良い。ON/OFF制御、またはHigh/

Low制御のパルス放電を行うことで、膜質の向上や気相中で発生するパーティクルを低

減することができる。

1の電極170には、銀、アルミニウム、銅などの低抵抗金属を用いることができ、スパ

ッタ法や真空蒸着法などで形成することができる。または、スクリーン印刷法を用いて、

銀ペーストや、銅ペーストなどの導電性樹脂で形成しても良い。

)参照)。透光性導電膜160には、例えば、インジウム錫酸化物、珪素を含むインジウ

ム錫酸化物、亜鉛を含む酸化インジウム、酸化亜鉛、ガリウムを含む酸化亜鉛、アルミニ

ウムを含む酸化亜鉛、酸化錫、フッ素を含む酸化錫、アンチモンを含む酸化錫、またはグ

ラフェン等を用いることができる。また、透光性導電膜160は単層に限らず、異なる膜

の積層でも良い。例えば、インジウム錫酸化物とアルミニウムを含む酸化亜鉛の積層や、

インジウム錫酸化物とフッ素を含む酸化錫の積層などを用いることができる。膜厚は総厚

で10nm以上1000nm以下とする。

B)に示した構造が形成できればよい。例えば、第1の半導体層110を形成し、その次

に第3の半導体層130を形成しても良い。

して第2の電極190を形成する。ここで用いる導電性樹脂には、銀ペースト、銅ペース

ト、ニッケルペースト、モリブデンペーストなどを用いることができる。また、第2の電

極190は、銀ペーストと銅ペーストを積層するなど、異なる材料の積層であっても良い

。また、導電性樹脂の供給は、ディスペンス法やインクジェット法を用いてもよい。

120上に設け、該透光性導電膜状に第1の電極170をグリッド状に形成する工程を行

えばよい。

けばよい。

にレジストマスクなどを設ければよい。

本実施の形態では、実施の形態1とは異なる光電変換装置、およびその作製方法について

説明する。なお、実施の形態1と共通する点については、その詳細を省略する。

る第4の半導体層140の構成材料のみが異なり、その他は同じである。

任意に複合した構成、または、図2、図3、および図4のそれぞれの構成を任意に複合し

た構成としてもよい。

以上、好ましくは2.5eV以上の遷移金属酸化物を主成分とする酸化物半導体層を用い

ることができる。特に元素周期表における第4族乃至第8族に属する金属の酸化物である

ことが好ましい。該金属の酸化物は、シリコンが光吸収を示す波長範囲において、高い透

光性を有する。

化クロム、酸化モリブデン、酸化タングステン、酸化マンガン、酸化レニウムなどを用い

ることができる。中でも特に、酸化モリブデンは大気中でも安定であり、吸湿性が低く、

扱いやすいため好ましい。

できる。また、上記酸化物半導体は、故意に不純物を添加しない場合においても、金属酸

化物中の欠陥や成膜工程中に取り込まれた微量の不純物がドナー準位またはアクセプタ準

位を形成するため、n型またはp型の導電型を示す。

チ化学社製タングステンボート(BB−3)に入れ、1×10−4Pa以下の真空下で、

0.2nm/秒の成膜速度でシリコン基板上に抵抗加熱蒸着を行うと、シリコン基板の導

電型の違いでI−V特性の異なる素子が形成される。図10(A)はn型のシリコン基板

上に、図10(B)はp型のシリコン基板上に、それぞれ上記方法で酸化モリブデン膜を

形成した素子のI−V特性である。図10(A)は整流性を示し、図10(B)はオーム

性を示していることから、図10(A)の特性を示す素子はp−n接合が形成されている

といえる。したがって、上記方法で成膜した酸化モリブデン膜の導電型はp型であること

がわかる。

.8×10−3S/cm(暗伝導度)、屈折率1.6〜2.2(波長550nm)、消衰

係数6×10−4〜3×10−3(波長550nm)、Taucプロットから求めたバン

ドギャップは、2.8〜3eVであった。

せることができ、キャリアのライフタイムを向上させることができる。

し、パッシベーション層としたときのキャリアのライフタイムは、約400μsecであ

ることがμPCD(microwave detected photoconduct

ivity decay)法で確かめられている。

マCVD法で形成した非晶質シリコン膜の光吸収係数の比較である。酸化モリブデン膜は

、広い波長範囲で光吸収係数が小さいことがわかる。

に用いることによって、光電変換装置の窓層での光吸収損失が低減し、光吸収領域におい

て効率良く光電変換を行うことできるようになる。

陥を低減するパッシベーション効果が高い。したがって、本実施の形態における光電変換

装置は、特に第3の半導体層130が不要な図3の構成を含む構造とすることが好ましい

。

いて図8および図9を説明する工程を用いて作製することができる。

パッタ法、またはイオンプレーティング法などの気相法により成膜することができる。膜

厚は10〜100nmとすることが好ましい。

、酸化モリブデン材料単体の蒸着、または酸化モリブデン材料とp型の導電型を付与する

不純物を共蒸着する方法を用いればよい。共蒸着とは、一つの処理室内で複数の蒸発源か

ら同時に蒸着を行う蒸着法である。また、スパッタ法では、酸化モリブデン、モリブデン

、またはそれらにp型の導電型を付与する不純物を含む材料をターゲットとし、酸素、ま

たは酸素とアルゴンなどの希ガスとの混合ガスをスパッタガスとする方法を用いればよい

。また、イオンプレーティング法では、上記スパッタ法と同様の材料を用いて、酸素を含

むプラズマ中で膜を形成すればよい。

説明した材料および方法を用いて作製した。セルサイズは132.25cm2であり、測

定には、ソーラーシミュレータにより発生させた疑似太陽光(AM1.5、照射強度は1

00mW/cm2)を用いた。

作製工程において、アルゴン/モノシラン流量比が0のセルAと、アルゴン/モノシラン

流量比が0.25のセルBとのI−V特性を比較した図である。

がわかる。すなわち、パッシベーション層へのアルゴン添加によるライフタイム向上が光

電変換装置の電気特性向上に寄与していることがわかる。

110 第1の半導体層

120 第2の半導体層

130 第3の半導体層

140 第4の半導体層

160 透光性導電膜

170 第1の電極

180 透光性導電膜

190 第2の電極

Claims (1)

- n型の導電型を有するシリコン基板を準備する第1の工程と、

前記シリコン基板の一方の面上に、n型の導電型を有し前記シリコン基板よりもキャリア濃度の低い第1の半導体層を形成する第2の工程と、

前記第1の半導体層上に、n型の導電型を有し前記シリコン基板よりもキャリア濃度の高い第2の半導体層を形成する第3の工程と、

前記シリコン基板の他方の面上に、p型の導電型を有する第3の半導体層を形成する第4の工程と、

前記第3の半導体層上に、p型の導電型を有し前記第3の半導体層よりもキャリア濃度の高い第4の半導体層を形成する第5の工程と、

前記第4の半導体層上に透光性導電膜を形成する第6の工程と、

前記第2の半導体層上に第1の電極を形成する第7の工程と、

前記透光性導電膜上に第2の電極を形成する第8の工程と、

を有し、

前記第1の半導体層、前記第2の半導体層および前記第3の半導体層は、シリコンを有し、

前記第4の半導体層は、酸化モリブデンで形成され、

前記第2の工程および前記第4の工程は、原料ガスにアルゴンとモノシランを含み、両者の流量比X(X=アルゴン流量/モノシラン流量)を0<X<0.8とした条件のプラズマCVD法で行うことを特徴とする光電変換装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016057800A JP6139731B2 (ja) | 2016-03-23 | 2016-03-23 | 光電変換装置の作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016057800A JP6139731B2 (ja) | 2016-03-23 | 2016-03-23 | 光電変換装置の作製方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011274196A Division JP2013125884A (ja) | 2011-12-15 | 2011-12-15 | 光電変換装置の作製方法および光電変換装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016106440A JP2016106440A (ja) | 2016-06-16 |

| JP6139731B2 true JP6139731B2 (ja) | 2017-05-31 |

Family

ID=56120300

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016057800A Expired - Fee Related JP6139731B2 (ja) | 2016-03-23 | 2016-03-23 | 光電変換装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6139731B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN109309138A (zh) * | 2018-12-13 | 2019-02-05 | 苏州腾晖光伏技术有限公司 | 一种异质结太阳电池及其制备方法 |

| KR102689097B1 (ko) * | 2019-08-30 | 2024-07-25 | 케이힌 람테크 가부시키가이샤 | 적층 구조체, 및 적층 구조체의 제조 방법 |

| CN117766597A (zh) * | 2023-12-22 | 2024-03-26 | 滁州捷泰新能源科技有限公司 | 高效双面电极太阳能电池 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6229180A (ja) * | 1985-07-30 | 1987-02-07 | Sanyo Electric Co Ltd | 光起電力素子 |

| JPH02263429A (ja) * | 1989-04-03 | 1990-10-26 | Sumitomo Metal Ind Ltd | 薄膜の形成方法 |

| US20090139558A1 (en) * | 2007-11-29 | 2009-06-04 | Shunpei Yamazaki | Photoelectric conversion device and manufacturing method thereof |

| US20090293948A1 (en) * | 2008-05-28 | 2009-12-03 | Stichting Energieonderzoek Centrum Nederland | Method of manufacturing an amorphous/crystalline silicon heterojunction solar cell |

| JP5503946B2 (ja) * | 2008-11-28 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 光電変換装置 |

| JP2013125884A (ja) * | 2011-12-15 | 2013-06-24 | Semiconductor Energy Lab Co Ltd | 光電変換装置の作製方法および光電変換装置 |

-

2016

- 2016-03-23 JP JP2016057800A patent/JP6139731B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016106440A (ja) | 2016-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5456168B2 (ja) | 光電変換装置の製造方法 | |

| US9112086B2 (en) | Photoelectric conversion device | |

| US20120273036A1 (en) | Photoelectric conversion device and manufacturing method thereof | |

| JP5927027B2 (ja) | 光電変換装置 | |

| JP2009033208A (ja) | 積層型光起電力素子の製造方法 | |

| JP5948148B2 (ja) | 光電変換装置 | |

| JP5826094B2 (ja) | p型半導体材料、および光電変換装置の作製方法 | |

| JP6139731B2 (ja) | 光電変換装置の作製方法 | |

| JP2017005270A (ja) | 光電変換装置の作製方法 | |

| JP6254348B2 (ja) | 光電変換装置 | |

| US9437768B2 (en) | Photoelectric conversion device | |

| JP2013125884A (ja) | 光電変換装置の作製方法および光電変換装置 | |

| JP6990764B2 (ja) | 太陽電池およびその製造方法 | |

| WO2013111312A1 (ja) | 光起電力装置およびその製造方法、光起電力モジュール | |

| JP2004119491A (ja) | 薄膜太陽電池の製造方法およびその方法で製造された薄膜太陽電池 | |

| JP5927028B2 (ja) | 光電変換装置 | |

| JP2007287926A (ja) | 集積化薄膜光電変換装置の製造方法および、その製造方法で得られうる集積化薄膜光電変換装置。 | |

| WO2019004126A1 (ja) | 光電変換装置の製造方法 | |

| JP2013074038A (ja) | 光電変換装置の製造方法及び光電変換装置 | |

| JPH05267698A (ja) | 光起電力装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161025 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161214 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170425 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170427 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6139731 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |