JP6120841B2 - Iii−vエピタキシャル層を成長させるための方法 - Google Patents

Iii−vエピタキシャル層を成長させるための方法 Download PDFInfo

- Publication number

- JP6120841B2 JP6120841B2 JP2014520601A JP2014520601A JP6120841B2 JP 6120841 B2 JP6120841 B2 JP 6120841B2 JP 2014520601 A JP2014520601 A JP 2014520601A JP 2014520601 A JP2014520601 A JP 2014520601A JP 6120841 B2 JP6120841 B2 JP 6120841B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- substrate

- iii

- gate

- electrical insulators

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 87

- 239000010410 layer Substances 0.000 claims description 174

- 239000000758 substrate Substances 0.000 claims description 109

- 239000004065 semiconductor Substances 0.000 claims description 77

- 239000000872 buffer Substances 0.000 claims description 67

- 230000008569 process Effects 0.000 claims description 37

- 238000004519 manufacturing process Methods 0.000 claims description 30

- 239000011241 protective layer Substances 0.000 claims description 26

- 238000005530 etching Methods 0.000 claims description 23

- 238000002955 isolation Methods 0.000 claims description 16

- 238000002513 implantation Methods 0.000 claims description 14

- 239000012535 impurity Substances 0.000 claims description 13

- 239000000615 nonconductor Substances 0.000 claims description 12

- 229910052710 silicon Inorganic materials 0.000 claims description 11

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 8

- 239000012212 insulator Substances 0.000 claims description 7

- 238000000059 patterning Methods 0.000 claims description 6

- 230000000903 blocking effect Effects 0.000 claims description 5

- 229910052732 germanium Inorganic materials 0.000 claims description 3

- 230000002457 bidirectional effect Effects 0.000 claims description 2

- 238000003491 array Methods 0.000 claims 2

- 238000009413 insulation Methods 0.000 description 25

- 229910002704 AlGaN Inorganic materials 0.000 description 24

- 230000015556 catabolic process Effects 0.000 description 17

- 239000000463 material Substances 0.000 description 17

- 238000000151 deposition Methods 0.000 description 16

- 229910052751 metal Inorganic materials 0.000 description 15

- 239000002184 metal Substances 0.000 description 15

- 229920002120 photoresistant polymer Polymers 0.000 description 14

- 230000008021 deposition Effects 0.000 description 12

- 238000010292 electrical insulation Methods 0.000 description 12

- 238000001312 dry etching Methods 0.000 description 11

- 230000004888 barrier function Effects 0.000 description 10

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 9

- 230000001681 protective effect Effects 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 230000008901 benefit Effects 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- 230000006911 nucleation Effects 0.000 description 7

- 238000010899 nucleation Methods 0.000 description 7

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 6

- 208000012868 Overgrowth Diseases 0.000 description 6

- 239000011248 coating agent Substances 0.000 description 6

- 238000000576 coating method Methods 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 125000004429 atom Chemical group 0.000 description 5

- 230000015572 biosynthetic process Effects 0.000 description 5

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 5

- 230000005669 field effect Effects 0.000 description 5

- 229910052731 fluorine Inorganic materials 0.000 description 5

- 239000011737 fluorine Substances 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- 238000013459 approach Methods 0.000 description 4

- 238000011109 contamination Methods 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- 239000001257 hydrogen Substances 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 4

- 229910052757 nitrogen Inorganic materials 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 230000001133 acceleration Effects 0.000 description 3

- 229910021529 ammonia Inorganic materials 0.000 description 3

- -1 and InAlGaN) Inorganic materials 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 230000005684 electric field Effects 0.000 description 3

- 238000011065 in-situ storage Methods 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 239000002346 layers by function Substances 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 230000000737 periodic effect Effects 0.000 description 3

- 230000008929 regeneration Effects 0.000 description 3

- 238000011069 regeneration method Methods 0.000 description 3

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 239000012491 analyte Substances 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 238000006243 chemical reaction Methods 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 229910052738 indium Inorganic materials 0.000 description 2

- 230000000977 initiatory effect Effects 0.000 description 2

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 2

- 239000011777 magnesium Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- 229910001199 N alloy Inorganic materials 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910052768 actinide Inorganic materials 0.000 description 1

- 150000001255 actinides Chemical class 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 239000012670 alkaline solution Substances 0.000 description 1

- 238000005275 alloying Methods 0.000 description 1

- 229910052787 antimony Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 230000003592 biomimetic effect Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 238000002485 combustion reaction Methods 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 239000002019 doping agent Substances 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 238000005566 electron beam evaporation Methods 0.000 description 1

- 238000005187 foaming Methods 0.000 description 1

- 229910021478 group 5 element Inorganic materials 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 229910052747 lanthanoid Inorganic materials 0.000 description 1

- 150000002602 lanthanoids Chemical class 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 230000015654 memory Effects 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000002028 premature Effects 0.000 description 1

- 230000001902 propagating effect Effects 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000007858 starting material Substances 0.000 description 1

- 238000002207 thermal evaporation Methods 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052727 yttrium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0642—Isolation within the component, i.e. internal isolation

- H01L29/0649—Dielectric regions, e.g. SiO2 regions, air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02518—Deposited layers

- H01L21/02521—Materials

- H01L21/02538—Group 13/15 materials

- H01L21/0254—Nitrides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02365—Forming inorganic semiconducting materials on a substrate

- H01L21/02612—Formation types

- H01L21/02617—Deposition types

- H01L21/02636—Selective deposition, e.g. simultaneous growth of mono- and non-monocrystalline semiconductor materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/30604—Chemical etching

- H01L21/30612—Etching of AIIIBV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/31051—Planarisation of the insulating layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76202—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using a local oxidation of silicon, e.g. LOCOS, SWAMI, SILO

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76202—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using a local oxidation of silicon, e.g. LOCOS, SWAMI, SILO

- H01L21/76213—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using a local oxidation of silicon, e.g. LOCOS, SWAMI, SILO introducing electrical inactive or active impurities in the local oxidation region, e.g. to alter LOCOS oxide growth characteristics or for additional isolation purpose

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/76224—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using trench refilling with dielectric materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/201—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys

- H01L29/205—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds including two or more compounds, e.g. alloys in different semiconductor regions, e.g. heterojunctions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66431—Unipolar field-effect transistors with a heterojunction interface channel or gate, e.g. HFET, HIGFET, SISFET, HJFET, HEMT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/778—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface

- H01L29/7786—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT

- H01L29/7787—Field effect transistors with two-dimensional charge carrier gas channel, e.g. HEMT ; with two-dimensional charge-carrier layer formed at a heterojunction interface with direct single heterostructure, i.e. with wide bandgap layer formed on top of active layer, e.g. direct single heterostructure MIS-like HEMT with wide bandgap charge-carrier supplying layer, e.g. direct single heterostructure MODFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/20—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only AIIIBV compounds

- H01L29/2003—Nitride compounds

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Junction Field-Effect Transistors (AREA)

Description

基板(例えば、Si、SiGe、Ge、基板およびそれらの組み合わせ、好ましくはSi基板(例えば<111>Si基板))を準備すること、

上記基板上にエピタキシャルな半導体のバッファ層(例えばIII−Vバッファ層(例えばIII−窒化物層))を設けて、当該エピタキシャルな半導体のバッファ層および基板の間に(例えば導電性の)界面を形成すること、または当該バッファ層を設けることによって当該界面を得ること、ならびに、

上記界面における電流を遮断するために、当該界面にある基板に1つ以上の局所的な電気絶縁を形成することを包含している。そのような絶縁は、シャロートレンチアイソレーション(STI)、LOCOS、不純物インプランテーション、ディープトレンチエッチングおよびこれらの組み合わせであり得る。上記基板における上記1つ以上の局所的な絶縁は、規則的なパターンに形成され得る。

基板(例えば、Si、SiGe、Ge、絶縁体上のSi、絶縁体上のGe基板およびそれらの組み合わせ、好ましくはSi基板(例えば<111>Si基板))を準備すること;

上記基板上にエピタキシャルな半導体のバッファ層(例えばIII−Vバッファ層(例えばIII−窒化物層))を設けることによって、当該バッファ層および上記基板の間に導電性界面を得ること;

上記導電性界面における電流を遮断するために、上記導電性界面および部分的に上記基板に、1つ以上の局所的な電気絶縁を形成すること;ならびに、

上記1つ以上の局所的な電気絶縁を、少なくとも1つの上記局所的な電気絶縁が当該素子の高圧の端子および低圧の端子の間に配置されるように、素子と位置合わせすることを包含している。

基板(例えば、Si、SiGe、Ge、基板およびそれらの組み合わせ、好ましくはSi基板(例えば<111>Si基板))、

上記基板上にあるバッファ層(例えばIII−Vバッファ層(例えばIII−窒化物層))を備えており、

上記バッファ層は、当該バッファおよび上記基板の間に界面を有しており、

導電性パスは、1つ以上の電気絶縁(例えば、シャロートレンチアイソレーション(STI)、LOCOS、不純物インプランテーション、ディープトレンチエッチングおよびこれらの組み合わせ)によって遮断されていることを特徴とし、上記基板およびバッファ層の間の上記界面に存在している。

(b)上記1つ以上の局所的な電気絶縁の間の間隙は、0.2μm〜20μmの幅、より好ましくは0.5μm〜10μmの幅、より一層好ましくは1μm〜5μmの幅であるか、および/または、

(c)上記1つ以上の局所的な電気絶縁の規則的なパターンの周期は、ゲートからドレインまでの距離より小さく、当該周期および距離は、同一平面にあり、好ましくは実質的に同一方向にある、ことが好ましい。

基板(例えば、Si、SiGe、Ge、基板およびそれらの組み合わせ、好ましくはSi基板(例えば<111>Si基板))を準備すること、

上記基板上にエピタキシャルな半導体のバッファ層(例えばIII−Vバッファ層(例えばIII−窒化物層))を設け、このようにして界面を形成すること;および、

上記界面にある基板に1つ以上の局所的な電気絶縁(例えば、シャロートレンチアイソレーション(STI)、LOCOS、不純物インプランテーション、ディープトレンチエッチングおよびこれらの組み合わせ)を形成することを包含している。基板における1つ以上の局所的な絶縁は、規則的なパターンに形成され得る。

基板(例えば、Si、SiGe、Ge、基板およびそれらの組み合わせ、好ましくはSi基板(例えば<111>Si基板))、

上記基板上にあるバッファ層(例えばIII−Vバッファ層(例えばIII−窒化物層))を備えており、

上記バッファ層は、当該バッファおよび上記基板の間に界面を有しており、

導電性パスは、上記基板およびバッファ層の間の上記界面に存在しており、上記界面に流れる電流を妨げるために当該界面に形成されている1つ以上の電気絶縁(例えば、シャロートレンチアイソレーション(STI)、LOCOS、不純物インプランテーション、ディープトレンチエッチングおよびこれらの組み合わせ)によって遮断されていることを特徴とする。

(b)上記1つ以上の局所的な電気絶縁の間の間隙は、0.2μm〜20μmの幅、より好ましくは0.5μm〜10μmの幅、より一層好ましくは1μm〜5μmの幅であるか、および/または、

(c)上記1つ以上の局所的な電気絶縁の規則的なパターンの周期は、ゲートからドレインまでの距離より小さく、当該周期および距離は、同一平面にあり、好ましくは実質的に同一方向にある、ことが好ましい。

感受性の生物学的要素、生物学的に生成された材料または生物模倣物;

生物学的な要素との分析物の相互作用から生じる信号を他の信号に変換する変換器または検出器の構成要素;ならびに、

付属する電子部品またはシグナルプロセッサからなる。

図1は、従来技術に係る半導体素子の断面図である。

図2は、本発明に係る半導体素子を製造する方法の断面図である。

図3a〜bは、本発明に係る半導体素子を製造する方法の断面図である。

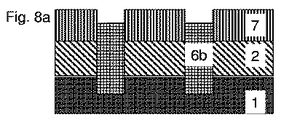

図4〜7および図8a〜dは、本発明に係る半導体素子を製造する方法の断面図である。

図9a〜fは、本発明に係る半導体素子を製造する方法の平面図である。

本発明は、特定の実施態様に関して図面を参照して説明されているが、本発明は、それらに限定されることなく、特許請求の範囲のみによって限定される。説明されている図面は、概略に過ぎず、非限定的である。図面において、いくつかの要素の大きさは、拡大されており、例示を目的とする大きさを描写していない。寸法および相対的な寸法は、本発明の実施に対する実際の縮尺と対応していない。

本発明の一例において、基板(層1)上のエピタキシャルバッファ構造(層2)は、AlN核生成層によって構成されているとともに、GaN(層3)、Al(Ga)N(層4)、およびSiN(層5)から構成される(Al(Ga)N(層4)およびSiN(層5)は任意)保護積層によってそのまま覆われた1つ以上の(In)AlGaNバッファ層によって任意に構成されている(従来技術を示す比較図1を参照)。構造は、基板とバッファ構成層(図1において矢印で示されている)との間に形成された導電チャネルをさらに備えている。この構造には、種々の標準的な半導体プロセスの工程(例えば、リソグラフィ、エッチング、堆積、インプラント、または酸化など)を実行し得、バッファ層上における選択的なエピタキシャル再成長のために、当該構造をMOCVD反応装置にさらに再導入し得る。一例において、基板(1)は、Si<111>である。他の例において、基板(1)はGe<111>である。また、他の例において、基板(1)は、結晶性Geの被覆を有しているSiである。上述のSiおよびGeの間には、SiGe移行層が存在し得る。

Claims (9)

- 高出力用途、高圧用途、高出力RF増幅器、多重化および双方向性電源スイッチングの1つ以上に好適なトランジスタまたはダイオードである半導体構造を含んでいる素子を製造する方法であって、

Si、SiGe、Ge、絶縁体上のSiおよび絶縁体上のGeの1つ以上を含んでいる基板を準備する工程;

上記基板上にIII−V族のエピタキシャルな半導体のバッファ層を設けることによって、上記バッファ層および基板の間に導電性界面を得る工程;

上記バッファ層を覆う1つ以上の保護層を形成する工程;

上記1つ以上の保護層を形成した後に、上記III−V族のエピタキシャルな半導体のバッファ層を貫いて上記基板の中まで、表面を規定している1つ以上の局所的な電気絶縁体を上記導電性界面に形成することによって、上記導電性界面における電流を遮断する工程、ここで、

上記半導体構造がトランジスタであるとき、上記1つ以上の局所的な電気絶縁体のうちの少なくとも1つは、当該トランジスタのゲートおよびドレインの間に形成されているか、または当該トランジスタのゲートは、上記1つ以上の局所的な電気絶縁体のまっすぐ上に置かれており、

上記半導体構造がダイオードであるとき、上記1つ以上の局所的な電気絶縁体のうちの少なくとも1つは、当該ダイオードのカソードおよびアノードの間に形成されている;

上記1つ以上の局所的な電気絶縁体の、上記表面を平坦化する工程;

上記表面を平坦化することの後に、上記1つ以上の保護層を除去する工程;ならびに

上記1つ以上の保護層を除去することの後に、III−V族のエピタキシャル層を選択的かつエピタキシャルに成長させる工程を包含している、方法。 - 上記1つ以上の局所的な電気絶縁体は、シャロートレンチアイソレーション、LOCOS、不純物インプランテーション、ディープトレンチエッチングおよびこれらの組み合わせのうち少なくとも1つによって形成される、請求項1に記載の方法。

- 上記1つ以上の局所的な電気絶縁体は、規則的なパターンに形成される、請求項1に記載の方法。

- 上記素子は、ゲートおよびドレインを含んでおり、当該ゲートは、ゲート−ドレイン距離だけ当該ドレインから離されており、

上記規則的なパターンの周期は、上記ゲート−ドレイン距離より小さく、

上記規則的なパターンにおける複数の上記局所的な絶縁体の配列物、ならびに上記ゲートおよびドレインの配列物は、同一平面、および実質的に同一方向にある、請求項3に記載の方法。 - 上記1つ以上の電気絶縁体のそれぞれは、25nm〜2.5μmの幅を有している、請求項1に記載の方法。

- 上記1つ以上の電気絶縁体のうち2つの隣接する電気絶縁体が、0.2μm〜20μmの幅の間隙によって離されている、請求項1に記載の方法。

- 上記1つ以上の保護層は、III−V族の層、SiN層およびそれらの組み合わせからなる群から選択される1つ以上の層を含んでいる、請求項1に記載の方法。

- 上記1つ以上の保護層は、(i)上記バッファ層上に付与されているGaNのスタック、(ii)GaN層上に付与されているAlN、および(iii)AlN層上に付与されているSiN層を含んでいる、請求項7に記載の方法。

- 上記基板およびバッファ層の少なくとも1つを、複数の局所的な上記電気絶縁体を用いてパターニングすることによってIII−V族の層を選択的に再成長させることを含んでいる上記再成長プロセスを実施することをさらに包含している、請求項1に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB1112327.0 | 2011-07-18 | ||

| GBGB1112327.0A GB201112327D0 (en) | 2011-07-18 | 2011-07-18 | Method for growing III-V epitaxial layers |

| PCT/EP2012/063317 WO2013010828A1 (en) | 2011-07-18 | 2012-07-06 | Method for growing iii-v epitaxial layers |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014521229A JP2014521229A (ja) | 2014-08-25 |

| JP2014521229A5 JP2014521229A5 (ja) | 2016-08-04 |

| JP6120841B2 true JP6120841B2 (ja) | 2017-04-26 |

Family

ID=44586778

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014520601A Active JP6120841B2 (ja) | 2011-07-18 | 2012-07-06 | Iii−vエピタキシャル層を成長させるための方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US9230803B2 (ja) |

| EP (1) | EP2735030B1 (ja) |

| JP (1) | JP6120841B2 (ja) |

| KR (1) | KR101674274B1 (ja) |

| CN (1) | CN103765592B (ja) |

| GB (1) | GB201112327D0 (ja) |

| WO (1) | WO2013010828A1 (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102012207501B4 (de) * | 2012-05-07 | 2017-03-02 | Forschungsverbund Berlin E.V. | Halbleiterschichtenstruktur |

| CN103117294B (zh) | 2013-02-07 | 2015-11-25 | 苏州晶湛半导体有限公司 | 氮化物高压器件及其制造方法 |

| TWI493617B (zh) * | 2013-10-07 | 2015-07-21 | Nat Univ Tsing Hua | 部分隔離矽基板之三族氮化物半導體裝置之製作方法 |

| KR102188493B1 (ko) | 2014-04-25 | 2020-12-09 | 삼성전자주식회사 | 질화물 단결정 성장방법 및 질화물 반도체 소자 제조방법 |

| US9761439B2 (en) * | 2014-12-12 | 2017-09-12 | Cree, Inc. | PECVD protective layers for semiconductor devices |

| US9923060B2 (en) * | 2015-05-29 | 2018-03-20 | Analog Devices, Inc. | Gallium nitride apparatus with a trap rich region |

| US9484412B1 (en) | 2015-09-23 | 2016-11-01 | International Business Machines Corporation | Strained silicon—germanium integrated circuit with inversion capacitance enhancement and method to fabricate same |

| GB2547661A (en) * | 2016-02-24 | 2017-08-30 | Jiang Quanzhong | Layered vertical field effect transistor and methods of fabrication |

| US10134603B2 (en) * | 2016-09-22 | 2018-11-20 | Infineon Technologies Ag | Method of planarising a surface |

| US10074721B2 (en) | 2016-09-22 | 2018-09-11 | Infineon Technologies Ag | Method of fabricating a semiconductor wafer that includes producing a planarised surface having both a mesa surface and an insulating layer surface |

| US10734303B2 (en) * | 2017-11-06 | 2020-08-04 | QROMIS, Inc. | Power and RF devices implemented using an engineered substrate structure |

| US10741666B2 (en) * | 2018-11-19 | 2020-08-11 | Vanguard International Semiconductor Corporation | High electron mobility transistor and method for forming the same |

| US10666353B1 (en) * | 2018-11-20 | 2020-05-26 | Juniper Networks, Inc. | Normal incidence photodetector with self-test functionality |

| CN111463273A (zh) * | 2020-03-25 | 2020-07-28 | 西北工业大学 | 一种基于氮化镓异质结外延的长关型hemt器件及其制备方法 |

| WO2021257965A1 (en) * | 2020-06-19 | 2021-12-23 | Macom Technology Solutions Holdings, Inc. | Suppression of parasitic acoustic waves in integrated circuit devices |

| CN113130643B (zh) * | 2020-12-18 | 2022-11-25 | 英诺赛科(苏州)科技有限公司 | 半导体器件以及制造半导体器件的方法 |

| US11888054B2 (en) | 2020-12-18 | 2024-01-30 | Innoscience (Suzhou) Technology Co., Ltd. | Semiconductor device and method for manufacturing the same |

| CN113224193B (zh) * | 2021-04-12 | 2022-06-14 | 华南理工大学 | 结合嵌入电极与钝化层结构的InGaN/GaN多量子阱蓝光探测器及其制备方法与应用 |

| WO2022217539A1 (zh) * | 2021-04-15 | 2022-10-20 | 苏州晶湛半导体有限公司 | 半导体结构及其制作方法 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE3644410A1 (de) * | 1986-12-24 | 1988-07-07 | Licentia Gmbh | Photoempfaenger |

| US5077231A (en) * | 1991-03-15 | 1991-12-31 | Texas Instruments Incorporated | Method to integrate HBTs and FETs |

| US5243207A (en) * | 1991-03-15 | 1993-09-07 | Texas Instruments Incorporated | Method to integrate HBTs and FETs |

| JP2891204B2 (ja) * | 1996-09-27 | 1999-05-17 | 日本電気株式会社 | 半導体装置の製造方法 |

| DE69940074D1 (de) * | 1998-09-14 | 2009-01-22 | Panasonic Corp | Verfahren zur herstellung einer halbleitervorrichtung |

| JP2000196029A (ja) * | 1998-12-28 | 2000-07-14 | Sony Corp | 半導体装置とその製造方法 |

| JP4521542B2 (ja) * | 1999-03-30 | 2010-08-11 | ルネサスエレクトロニクス株式会社 | 半導体装置および半導体基板 |

| JP2002170877A (ja) * | 2000-12-01 | 2002-06-14 | Sharp Corp | 半導体装置の製造方法 |

| US6756633B2 (en) * | 2001-12-27 | 2004-06-29 | Silicon Storage Technology, Inc. | Semiconductor memory array of floating gate memory cells with horizontally oriented floating gate edges |

| JP4136939B2 (ja) | 2002-01-09 | 2008-08-20 | 松下電器産業株式会社 | 半導体装置およびその製造方法 |

| JP2003332676A (ja) * | 2002-05-08 | 2003-11-21 | Mitsubishi Electric Corp | 半導体光装置 |

| US7449728B2 (en) | 2003-11-24 | 2008-11-11 | Tri Quint Semiconductor, Inc. | Monolithic integrated enhancement mode and depletion mode field effect transistors and method of making the same |

| US7247889B2 (en) | 2004-12-03 | 2007-07-24 | Nitronex Corporation | III-nitride material structures including silicon substrates |

| DE102005010821B4 (de) | 2005-03-07 | 2007-01-25 | Technische Universität Berlin | Verfahren zum Herstellen eines Bauelements |

| EP2175494B1 (en) * | 2006-03-16 | 2015-03-25 | Fujitsu Limited | Compound semiconductor device and manufacturing method of the same |

| US7955960B2 (en) | 2007-03-22 | 2011-06-07 | Hynix Semiconductor Inc. | Nonvolatile memory device and method of fabricating the same |

| KR100966989B1 (ko) * | 2007-03-22 | 2010-06-30 | 주식회사 하이닉스반도체 | 플래시 메모리 소자의 제조 방법 |

| US7875907B2 (en) * | 2007-09-12 | 2011-01-25 | Transphorm Inc. | III-nitride bidirectional switches |

| JP2010016089A (ja) * | 2008-07-02 | 2010-01-21 | Nec Electronics Corp | 電界効果トランジスタ、その製造方法、及び半導体装置 |

| US20100155831A1 (en) * | 2008-12-20 | 2010-06-24 | Power Integrations, Inc. | Deep trench insulated gate bipolar transistor |

| JP2011082216A (ja) * | 2009-10-02 | 2011-04-21 | Fujitsu Ltd | 化合物半導体装置及びその製造方法 |

| CN101719465B (zh) | 2009-11-27 | 2015-10-21 | 晶能光电(江西)有限公司 | 硅衬底GaN基半导体材料的制造方法 |

-

2011

- 2011-07-18 GB GBGB1112327.0A patent/GB201112327D0/en not_active Ceased

-

2012

- 2012-07-06 EP EP12740090.1A patent/EP2735030B1/en active Active

- 2012-07-06 KR KR1020147003437A patent/KR101674274B1/ko active IP Right Grant

- 2012-07-06 WO PCT/EP2012/063317 patent/WO2013010828A1/en active Application Filing

- 2012-07-06 CN CN201280035896.6A patent/CN103765592B/zh active Active

- 2012-07-06 JP JP2014520601A patent/JP6120841B2/ja active Active

- 2012-07-06 US US14/232,933 patent/US9230803B2/en active Active

-

2015

- 2015-12-10 US US14/965,550 patent/US9748331B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20160099309A1 (en) | 2016-04-07 |

| EP2735030B1 (en) | 2017-03-15 |

| EP2735030A1 (en) | 2014-05-28 |

| CN103765592B (zh) | 2017-09-19 |

| KR20140063593A (ko) | 2014-05-27 |

| US9230803B2 (en) | 2016-01-05 |

| JP2014521229A (ja) | 2014-08-25 |

| WO2013010828A1 (en) | 2013-01-24 |

| CN103765592A (zh) | 2014-04-30 |

| US20140167114A1 (en) | 2014-06-19 |

| US9748331B2 (en) | 2017-08-29 |

| KR101674274B1 (ko) | 2016-11-08 |

| GB201112327D0 (en) | 2011-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6120841B2 (ja) | Iii−vエピタキシャル層を成長させるための方法 | |

| US9935190B2 (en) | Forming enhancement mode III-nitride devices | |

| US9543424B2 (en) | Method for growing III-V epitaxial layers and semiconductor structure | |

| US8487316B2 (en) | Method of manufacturing an integrated semiconductor substrate structure with device areas for definition of GaN-based devices and CMOS devices | |

| JP5885750B2 (ja) | バッファ降伏電圧が増大されたhemt | |

| JP2013131736A (ja) | 半導体装置および半導体装置の製造方法 | |

| US20080203471A1 (en) | Nitride semiconductor device and method for producing nitride semiconductor device | |

| KR20140124273A (ko) | 질화물 반도체 소자 및 그 제조 방법 | |

| You et al. | Vertical GaN devices: Process and reliability | |

| WO2019194042A1 (ja) | トランジスタの製造方法 | |

| JP2008118044A (ja) | 電界効果トランジスタ及びその製造方法 | |

| US7276423B2 (en) | III-nitride device and method with variable epitaxial growth direction | |

| US9391179B2 (en) | Vertical GaN JFET with low gate-drain capacitance and high gate-source capacitance | |

| US11532739B2 (en) | Integrated enhancement/depletion mode HEMT and method for manufacturing the same | |

| JP2008159691A (ja) | 窒化物半導体結晶成長基板、窒化物半導体素子および窒化物半導体結晶成長基板の製造方法 | |

| US10446677B2 (en) | Semiconductor structures and method for fabricating the same | |

| Piedra | Design-space and scalable technology for GaN based power transistors | |

| JP2008153371A (ja) | 縦型電界効果トランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160617 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20160617 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20160705 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160726 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20161026 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20161122 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170328 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6120841 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |