以下に、本願の開示する信号制御回路、情報処理装置及びデューティ算出方法の実施例を図面に基づいて詳細に説明する。なお、以下の実施例により本願の開示する信号制御回路、情報処理装置及びデューティ算出方法が限定されるものではない。

図1は、情報処理装置の概略構成図である。本実施例に係る情報処理装置は、チップセット100、DIMM2、及びCentral Processing Unit(CPU)3を有する。

チップセット100は、メモリコントローラ10を搭載する。そして、メモリコントローラ10は、メモリインタフェース回路1を有する。

DIMM2は、記憶媒体であるDRAM(Dynamic Random Access Memory)を有する記憶装置である。DIMM2は、データのリード要求及びクロック信号を後述するメモリインタフェース回路1から受信する。そして、DIMM2は、受信したクロック信号からデータストローブ(DQS)信号を生成する。そして、DIMM2は、DQS信号をデータ(DQ)信号とともにメモリインタフェース回路1へ送信する。

CPU3は、DIMM2からデータを読み出す命令であるリード要求のコマンドをチップセット100上のメモリコントローラ10へ送信する。そして、CPU3は、リード要求で指定したデータをメモリコントローラ10から受信する。その後、CPU3の演算処理部31は、受信したデータに対して処理を実行する。

メモリコントローラ10は、リード要求のコマンドをCPU3から受信する。そして、メモリコントローラ10は、内部クロック信号を生成し、生成した内部クロック信号とともにリード要求をメモリインタフェース回路1に対して送信する。その後、メモリコントローラ10は、メモリインタフェース回路1が取り込んだデータを取得する。そして、メモリコントローラ10は、取得したデータをCPU3へ送信する。

メモリインタフェース回路1は、リード要求をメモリコントローラ10から受信する。さらに、メモリインタフェース回路1は、内部クロック信号をメモリコントローラ10から受信する。そして、メモリインタフェース回路1は、リード要求とともにクロック(CK)信号をDIMM2へ送信する。

その後、メモリインタフェース回路1は、データストローブ(DQS)信号及びデータ(DQ)信号を受信する。次に、メモリインタフェース回路1は、DQS信号に遅延を与えて内部クロック信号との同期をとる。具体的には、メモリインタフェース回路1は、DQS信号の立上りとDQS信号に固定遅延を与えた信号の立上りが内部クロック信号の立下りの前後にくるように、データストローブ(DQS)信号に遅延を与える。そして、メモリインタフェース回路1は、遅延を与えたDQS信号のエッジのタイミングで、DQ信号からデータを取り込む。その後、メモリインタフェース回路1は、取り込んだデータをCPU3へ送信する。

また、本実施例に係るメモリインタフェース回路1は、DQS信号の立上りの位相を内部クロック信号に合わせた場合のDQSに与えた遅延及びDQS信号の立下りの位相を内部クロック信号に合わせた場合のDQSに与えた遅延を求める。そして、メモリインタフェース回路1は、メモリコントローラ10の外部、例えばCPU3に求めた各遅延を通知する。そして、CPU3は、メモリインタフェース回路1が求めた各遅延からDQS信号のデューティをデューティ算出部14で算出する。

この場合、例えば、CPU3は、DQS信号のデューティをモニタ(不図示)へ表示するなどにより、情報処理装置の管理者などにDQS信号のデューティの状態を通知する。これにより、管理者は、デューティ異常の発生を迅速に把握することができ、データ異常発生時の原因の切り分けを迅速に行うことができる。

そこで、次に、図2を参照して、本実施例に係るデューティの算出を行うメモリインタフェース回路1及び情報処理装置の詳細を説明する。図2は、実施例1に係るメモリインタフェース回路及び情報処理装置のブロック図である。図2では、デューティ算出の機能について説明するため、例えば、DIMM2へのクロック(CK)信号の送信などの機能を有する各部は省略してある。

図2に示すように、本実施例に係るメモリインタフェース回路1は、立上側位相判定回路11、立下側位相判定回路12、可変遅延設定値比較部13、及びデータ取込部30を有する。

立上側位相判定回路11は、内部クロック信号の立下りとDQS信号の立上りのタイミングを合わせるための遅延量を求める回路である。データ取込部30は、立上側位相判定回路11で求められた遅延量が与えられたDQS信号を用いて、DQ信号からデータの取り込みを行う。次に、立上側位相判定回路11の詳細について説明する。

立上側位相判定回路11は、可変遅延付加部111、固定遅延付加部112、ラッチ113、位相判定部114、及び可変遅延制御部115を有する。

可変遅延付加部111は、DQS信号をDIMM2から受信する。また、可変遅延付加部111は、DQS信号に与える遅延量を指定する可変遅延設定値を可変遅延制御部115から受ける。そして、可変遅延付加部111は、可変遅延設定値で指定されるステップ数分の遅延量をDQS信号に与える。ここで、ステップとは、予め決められた遅延量をDQS信号に与える単位である。すなわち、可変遅延付加部111は、ステップ数を可変遅延制御部115から受信し、受信したステップ数で予め決められた遅延量を乗算した値を遅延量としてDQS信号に与える。以下では、可変遅延付加部111が与える遅延量を「立上用可変遅延量」という。そして、可変遅延付加部111は、立上用可変遅延量を与えたDQS信号をラッチ113及び固定遅延付加部112へ出力する。

固定遅延付加部112は、立上用可変遅延量が与えられたDQS信号の入力を可変遅延付加部111から受ける。そして、固定遅延付加部112は、立上用可変遅延量が与えられたDQS信号に予め決められた遅延量を与える。以下では、固定遅延付加部112が与える遅延量を「立上用固定遅延量」という。その後、固定遅延付加部112は、立上用可変遅延量及び立上用固定遅延量が付加されたDQS信号をラッチ113へ出力する。

ラッチ113は、立上用可変遅延量が与えられたDQS信号の入力を可変遅延付加部111から受ける。また、ラッチ113は、立上用可変遅延量及び立上用固定遅延量が付加されたDQS信号の入力を固定遅延付加部112から受ける。以下では、可変遅延付加部111から出力された信号を「立上用先行信号」と呼び、固定遅延付加部112から出力された信号を「立上用後行信号」と呼ぶ。

また、ラッチ113は、内部クロック信号の入力をクロック発生部15から受ける。さらに、ラッチ113は、立上用インヒビット(Inhibit:IH)信号の入力を可変遅延制御部115から受ける。

ラッチ113は、立上用IH信号がLowの場合、内部クロック信号の立下りのタイミングで立上用先行信号及び立上用後行信号の位相情報を取り込む。本実施例では、ラッチ113は、信号がHighレベルの場合、位相情報を「1」として取り込み、信号がLowレベルの場合、位相情報を「0」として取り込む。例えば、内部クロック信号が立下りのタイミングで、立上用先行信号がHighで、立上用後行信号がLowの場合、立上用先行信号の位相情報として「1」を取り込み、立上用後行信号の位相情報として「0」を取り込む。

そして、ラッチ113は、立上用先行信号及び立上用後行信号の位相情報を位相判定部114へ出力する。

位相判定部114は、位相情報の組み合わせに対応する位相状態を記憶する。例えば、位相判定部114は、図3Aで表される立上用判定テーブル201を記憶する。図3Aは、立上用判定テーブルの一例の図である。図3Aでは、位相情報として数字を2つ並べているが、前段が立上用後行信号の値を表し、後段が立上用先行信号の値を表す。

位相判定部114は、立上用先行信号及び立上用後行信号の位相情報の入力をラッチ113から受ける。そして、位相判定部114は、受信した位相情報の組み合わせに対応する位相状態を立上用判定テーブル201から取得する。その後、位相判定部114は、取得した位相状態を可変遅延制御部115へ出力する。以下では、DQS信号の位相が内部クロック信号の位相に比べて遅れた位相状態を、「遅れた位相状態」という。また、DQS信号の位相がクロック信号の位相に比べて進んだ位相状態を、「進んだ位相状態」という。さらに、DQS信号の位相とクロック信号の位相が一致している位相状態を、「一致した位相状態」という。

可変遅延制御部115は、位相状態の入力を位相判定部114から受ける。そして、可変遅延制御部115は、遅れた位相状態の場合、DQS信号の位相を1ステップ分進ませた可変遅延設定値を求める。すなわち、可変遅延制御部115は、可変遅延付加部111へ通知したステップ数から1を減算したステップ数を可変遅延設定値とする。そして、可変遅延制御部115は、求めた可変遅延設定値を可変遅延付加部111へ送信する。

また、可変遅延制御部115は、進んだ位相状態の場合、現在のDQS信号の位相からさらに予め決められた1ステップ分遅らせる可変遅延設定値を求める。すなわち、可変遅延制御部115は、可変遅延付加部111へ通知したステップ数に1を加算したステップ数を可変遅延設定値とする。そして、可変遅延制御部115は、求めた可変遅延設定値を可変遅延付加部111へ送信する。

また、可変遅延制御部115は、一致した位相状態の場合、可変遅延設定値を保持する指示を可変遅延付加部111へ送信する。さらに、可変遅延制御部115は、可変遅延付加部111へ通知した可変遅延設定値を可変遅延設定値比較部13へ出力する。以下、この可変遅延制御部115から出力される可変遅延設定値を、「立上用設定値」という。この立上用設定値が、「第1遅延量」の一例にあたる。

立下側位相判定回路12は、内部クロック信号の立下りとDQS信号の立下りのタイミングを合わせるための遅延量を求める回路である。

立下側位相判定回路12は、可変遅延付加部121、固定遅延付加部122、ラッチ123、位相判定部124、及び可変遅延制御部125を有する。

可変遅延付加部121は、DQS信号をDIMM2から受信する。また、可変遅延付加部121は、DQS信号に与える遅延量を指定する可変遅延設定値を可変遅延制御部125から受ける。そして、可変遅延付加部121は、可変遅延設定値により指定された遅延量をDQS信号に与える。以下では、可変遅延付加部121が与える遅延量を「立下用可変遅延量」という。そして、可変遅延付加部121は、立下用可変遅延量を与えたDQS信号をラッチ123及び固定遅延付加部122へ出力する。

固定遅延付加部122は、立下用可変遅延量が与えられたDQS信号の入力を可変遅延付加部121から受ける。そして、固定遅延付加部122は、立下用可変遅延量が与えられたDQS信号に予め決められた遅延量を与える。以下では、固定遅延付加部122が与える遅延量を「立下用固定遅延量」という。その後、固定遅延付加部122は、立下用可変遅延量及び立下用固定遅延量が付加されたDQS信号をラッチ123へ出力する。

ラッチ123は、立下用可変遅延量が与えられたDQS信号の入力を可変遅延付加部121から受ける。また、ラッチ123は、立下用可変遅延量及び立下用固定遅延量が付加されたDQS信号の入力を固定遅延付加部122から受ける。以下では、可変遅延付加部121から出力された信号を「立下用先行信号」と呼び、固定遅延付加部122から出力された信号を「立下用後行信号」と呼ぶ。

また、ラッチ123は、クロック信号の入力をクロック発生部15から受ける。さらに、ラッチ123は、立下用インヒビット(Inhibit:IH)信号の入力を可変遅延制御部125から受ける。

ラッチ123は、立下用IH信号がLowの場合、クロック信号の立下りのタイミングで立下用先行信号と立下用後行信号の位相情報を取り込む。

そして、ラッチ123は、立下用先行信号及び立下用後行信号の位相情報を位相判定部124へ出力する。

位相判定部124は、位相情報の組み合わせに対応する位相状態を記憶する。例えば、位相判定部124は、図3Bで表される立下用判定テーブル202を記憶する。図3Bは、立下用判定テーブルの一例の図である。

位相判定部124は、立下用先行信号及び立下用後行信号の位相情報の入力をラッチ123から受ける。そして、位相判定部124は、受信した位相情報の組み合わせに対応する位相状態を立下用判定テーブル202から取得する。その後、位相判定部124は、取得した位相状態を可変遅延制御部125へ出力する。

可変遅延制御部125は、位相状態の入力を位相判定部124から受ける。そして、可変遅延制御部125は、遅れた位相状態の場合、DQS信号の位相を予め決められた1ステップ分進ませた可変遅延設定値を求める。すなわち、可変遅延制御部115は、可変遅延付加部111へ通知したステップ数から1を減算したステップ数を可変遅延設定値とする。そして、可変遅延制御部125は、求めた可変遅延設定値を可変遅延付加部121へ送信する。

また、可変遅延制御部125は、進んだ位相状態の場合、DQS信号の位相を予め決められた1ステップ分遅らせる可変遅延設定値を求める。すなわち、可変遅延制御部115は、可変遅延付加部111へ通知したステップ数に1を加算したステップ数を可変遅延設定値とする。そして、可変遅延制御部125は、求めた可変遅延設定値を可変遅延付加部121へ送信する。

また、可変遅延制御部125は、一致した位相状態の場合、可変遅延設定値を保持する指示を可変遅延付加部121へ送信する。さらに、位相が一致した場合、可変遅延制御部125は、可変遅延設定値を可変遅延設定値比較部13へ出力する。以下、この可変遅延制御部125から出力される可変遅延設定値を、「立下用設定値」という。この立下用設定値が、「第2遅延量」の一例にあたる。

可変遅延設定値比較部13は、立上用設定値の入力を可変遅延制御部115から受ける。また、可変遅延設定値比較部13は、立下用設定値の入力を可変遅延制御部125から受ける。

可変遅延設定値比較部13は、立上用設定値と立下用設定値の差分を求める。そして、可変遅延設定値比較部13は、求めた立上用設定値と立下用設定値の差分をデューティ算出部14へ出力する。以上に説明した、立上側位相判定回路11及び立下側位相判定回路12が、「遅延量取得部」の一例にあたる。

デューティ算出部14は例えば図1におけるCPU3などで実現される。デューティ算出部14は、立上用設定値と立下用設定値の差分を可変遅延設定値比較部13から受信する。

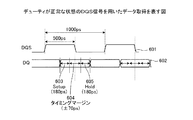

そして、デューティ算出部14は、受信した立上用設定値と立下用設定値の差分を用いてDQS信号のデューティを算出する。以下、図4A、図4B、及び図5を参照して、デューティ算出部14によるデューティの算出方法について説明する。図4Aは、デューティが50%の場合のDQS信号の両エッジの遅延を表す図である。図4Bは、デューティが50%以外の場合のDQS信号の両エッジの遅延を表す図である。また、図5は、両エッジの遅延とデューティのズレ量との関係を表す図である。

図4Aの信号301は、デューティが50%の場合のDQS信号を表す。信号302は、立上用IH信号を表す。信号303は、立上用先行信号を表す。信号304は、立上用後行信号を表す。信号303及び信号304は、信号302がLowの場合に値が取得される。すなわち、タイミング308で、信号303及び信号304の値が取得される。

また、信号305は、立下用IH信号を表す。信号306は、立下用先行信号を表す。信号307は、立下用後行信号を表す。信号306及び信号307は、信号305がLowの場合に値が取得される。すなわち、タイミング309で、信号306及び信号307の値が取得される。

本実施例では、DQS信号の周期がクロック信号の周期の2倍であるため、DQS信号のデューティが50%の場合、立上用先行信号である信号303に与えられる遅延310と、立下用先行信号である信号306に与えられる遅延311とは等しい。

図4Bの信号312は、デューティが50%より大きい場合のDQS信号を表す。信号313は、立上用IH信号を表す。信号314は、立上用先行信号を表す。信号315は、立上用後行信号を表す。信号314及び信号315は、信号313がLowの場合に値が取得される。すなわち、タイミング319で、信号314及び信号315の値が取得される。

信号316は、立下用IH信号を表す。信号317は、立下用先行信号を表す。信号318は、立下用後行信号を表す。信号317及び信号318は、信号316がLowの場合に値が取得される。すなわち、タイミング320で、信号317及び信号318の値が取得される。

DQS信号のデューティが50%以外の場合、立上用先行信号である信号314に与えられる遅延321と、立下用先行信号である信号317に与えられる遅延322とは一致しない。

そして、図5に示すように、信号301と信号312との差である期間323は、信号314に与えられる遅延321と信号317に与えられる遅延322との差分と等しくなる。

そして、可変遅延付加部111及び可変遅延付加部121が与える遅延量は、立上用設定値及び立下用設定値から算出される。すなわち、遅延321は、立上用設定値に1ステップ分の単位遅延量を乗算した値である。また、遅延322は、立下用設定値に1ステップ分の単位遅延量を乗算した値である。

そこで、デューティ算出部14は、受信した立上用設定値及び立下用設定値のそれぞれに1ステップ分の単位遅延量を乗算し、求めた値同士の差分を求めることで、DQS信号のデューティのズレ量が算出できる。

そして、DQS信号のデューティは、DQS信号のHighレベル部分の幅をDQS信号の周期で除算した値をパーセンテージで表示することで得られる。そこで、デューティは、立上用設定値と立下用設定値との差分をXとした場合、デューティ=50+aXという関数で表すことができる。ここで、aは、1ステップ分の単位遅延量をDQS信号の周期で除算した値をパーセンテージに直した値である。すなわち、デューティ算出部14は、立上用設定値と立下用設定値との差分を50+aXに代入してデューティを算出する。

立上用設定値及び立下用設定値とデューティ算出部14によって算出されるデューティとの関係は、図6の表330のようになる。図6は、立上用設定値及び立下用設定値とデューティ算出部によって算出されるデューティとの関係を表す図である。表330に示すように、Xが0より大きければ、デューティは50%より大きい。すなわち、Highレベルの幅がLowレベルの幅に比べて大きい。Xが0であれば、デューティは50%である。すなわち、Highレベルの幅とLowレベルの幅が等しい。Xが0より小さければ、デューティは50%より小さい。すなわち、Highレベルの幅がLowレベルの幅に比べて小さい。

例えば、Xが3で、DQS信号の周期が1000psで、1ステップ分の単位遅延量が20psの場合で具体例を説明する。この場合、デューティが50%であれば、DQS信号のHighレベルの幅は500psとなる。また、係数aは、a=(20/1000)×100=2となる。そこで、Xが3の場合のデューティは、50+(2×3)=56%となる。このように、デューティ算出部14は、立上用設定値及び立下用設定値からデューティを算出する。

図2に戻り説明を続ける。デューティ算出部14は、算出したデューティをモニタに表示するなどして、現在のデューティ比を情報処理装置の操作者に通知する。

次に、図7を参照して、本実施例に係るメモリインタフェース回路によるデューティ算出処理の流れについて説明する。図7は、実施例1に係るメモリインタフェース回路によるデューティ算出処理のフローチャートである。

ラッチ113は、立上用先行信号及び立上用後行信号の位相情報を取得する(ステップS1)。

次に、位相判定部114は、立上用先行信号及び立上用後行信号の位相情報の入力をラッチ113から受ける。そして、位相判定部114は、立上用先行信号及び立上用後行信号の位相情報からDQS信号の位相状態を判定する。そして、位相判定部114は、DQS信号の位相状態を可変遅延制御部115へ出力する。

可変遅延制御部115は、DQS信号の位相状態の入力を位相判定部114から受信する。そして、可変遅延制御部115は、DQS信号の立上りの位相と内部クロック(CLK)の位相との関係を判定する(ステップS2)。位相が一致した場合(ステップS2:一致)、可変遅延制御部115は、立上用設定値を可変遅延設定値比較部13へ出力する。

これに対して、位相が進んでいる場合(ステップS2:進んでいる)、可変遅延制御部115は、立上用設定値に1を加算し(ステップS3)、ステップS1へ戻る。また、位相が遅れている場合(ステップS2:遅れている)、立上用設定値から1を減算し(ステップS4)、ステップS1へ戻る。

一方、ラッチ123は、立下用先行信号及び立下用後行信号の位相情報を取得する(ステップS5)。

次に、位相判定部124は、立下用先行信号及び立下用後行信号の位相情報の入力をラッチ123から受ける。そして、位相判定部124は、立下用先行信号及び立下用後行信号の位相情報からDQS信号の位相状態を判定する。そして、位相判定部124は、DQS信号の位相状態を可変遅延制御部125へ出力する。

可変遅延制御部125は、DQS信号の位相状態の入力を位相判定部124から受信する。そして、可変遅延制御部125は、DQS信号の立下りの位相と内部クロック(CLK)の位相との関係を判定する(ステップS6)。位相が一致した場合(ステップS6:一致)、可変遅延制御部125は、立下用設定値を可変遅延設定値比較部13へ出力する。

これに対して、位相が進んでいる場合(ステップS6:進んでいる)、可変遅延制御部125は、立下用設定値に1を加算し(ステップS7)、ステップS5へ戻る。また、位相が遅れている場合(ステップS6:遅れている)、可変遅延制御部125は、立下用設定値から1を減算し(ステップS8)、ステップS5へ戻る。

可変遅延設定値比較部13は、立上用設定値の入力を可変遅延制御部115から受け、立下用設定値の入力を可変遅延制御部125から受ける。そして、可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求める(ステップS9)。可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分をデューティ算出部14へ出力する。

デューティ算出部14は、立上用設定値と立下用設定値との差分の入力を可変遅延設定値比較部13から受ける。そして、デューティ算出部14は、受信した差分を用いてDQS信号のデューティを算出する(ステップS10)。

次に、図8を参照して、DQS信号の位相が内部クロック(CLK)に対し、進んでいる場合のデューティ算出処理の全体的な流れを説明する。図8は、DQS信号の位相が進んでいる場合のデューティ算出処理のタイミングチャートである。

図8の横軸は時間の経過を表す。また、信号401は、立上用先行信号を表す。また、信号402は、立上用後行信号を表す。また、信号403は、立上用IH信号を表す。また、信号404は、立下用先行信号を表す。また、信号405は、立下用後行信号を表す。また、信号406は、立下用IH信号を表す。信号401及び信号402は、立上用IH信号403がLowの場合に値が取得される。すなわち、B0、B1、及びB2のタイミングで、ラッチ113は、信号401及び信号402の値を取得する。信号404及び信号405は、立下用IH信号406がLowの場合に値が取得される。すなわち、A0、A1、及びA2のタイミングで、ラッチ123は、信号404及び信号405の値を取得する。

立上り側位相調整では、可変遅延付加部111は、信号401に立上用設定値が「n−1」分の可変遅延を与えている(ステップS20)。信号402は、信号401に固定遅延が付加された信号となっている。

タイミングB0において、ラッチ113は、信号401及び信号402の値を取得する(ステップS21)。この場合、ラッチ113は、信号401の値として「1」を取得し、信号402の値として「1」を取得する。位相判定部114は、「11」という位相情報の組をラッチ113から受ける(ステップS22)。ここで、位相情報の組を表す「11」は、先頭bitが後行信号の値を表し、末尾bitが先行信号の値を表す。以下では、先行信号及び後行信号の位相情報の組を、単に「位相情報」という場合がある。

位相判定部114は、進んだ位相状態であると判定する。そして、位相判定部114は、進んだ位相状態である旨を可変遅延制御部115へ通知する(ステップS23)。可変遅延制御部115は、立上用設定値に1を加算し新たな立上用設定値を求める。図8では、可変遅延制御部115は、「n−1」であった立上用設定値に1を加算して、新たな立上用設定値として「n」を求めている。そして、可変遅延制御部115は、求めた立上用設定値を可変遅延付加部111へ通知する(ステップS24)。

可変遅延付加部111は、立上用設定値の入力を可変遅延制御部115から受けて、1ステップ分遅延量を増加させた遅延をDQS信号に与える(ステップS25)。

タイミングB1において、ラッチ113は、信号401及び信号402の値を取得する(ステップS26)。この場合、ラッチ113は、信号401の値として「1」を取得し、信号402の値として「0」を取得する。位相判定部114は、「01」という位相情報をラッチ113から受ける(ステップS27)。

位相判定部114は、位相情報が「01」であることから、DQS信号の位相が一致したと判定する(ステップS28)。そして、位相判定部114は、一致した位相状態である旨を可変遅延制御部115へ通知する。可変遅延制御部115は、位相が一致したことから、この時の立上用設定値を可変遅延設定値比較部13へ出力する(ステップS29)。

一方、立下り側位相調整では、可変遅延付加部121は、信号404に立下用設定値が「m−1」分の可変遅延を与えている(ステップS30)。信号405は、信号404に固定遅延が付加された信号となっている。

タイミングA0において、ラッチ123は、信号404及び信号405の値を取得する(ステップS31)。この場合、ラッチ123は、信号404の値として「0」を取得し、信号405の値として「0」を取得する。位相判定部124は、「00」という位相情報をラッチ123から受ける(ステップS32)。

位相判定部124は、進んだ位相状態である判定する。そして、位相判定部124は、進んだ位相状態である旨を可変遅延制御部125へ通知する(ステップS33)。可変遅延制御部125は、立下用設定値に1を加算し新たな立下用設定値を求める。図8では、可変遅延制御部125は、「m−1」であった立下用設定値に1を加算して、新たな立下用設定値として「m」を求めている。そして、可変遅延制御部125は、求めた立下用設定値を可変遅延付加部121へ通知する(ステップS34)。

可変遅延付加部121は、立下用設定値の入力を可変遅延制御部125から受けて、1ステップ分遅延量を増加させた遅延をDQS信号に与える(ステップS35)。

タイミングA1において、ラッチ123は、信号404及び信号405の値を取得する(ステップS36)。この場合、ラッチ123は、信号404の値として「0」を取得し、信号405の値として「1」を取得する。位相判定部124は、「10」という位相情報をラッチ123から受ける(ステップS37)。

位相判定部124は、位相情報が「10」であることから、DQS信号の位相が一致したと判定する。そして、位相判定部124は、一致した位相状態である旨を可変遅延制御部125へ通知する(ステップS38)。可変遅延制御部125は、位相が一致したことから、この時の立下用設定値を可変遅延設定値比較部13へ出力する(ステップS39)。

可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求める(ステップS40)。

その後、可変遅延設定値比較部13は、求めた差分をデューティ算出部14へ通知する。デューティ算出部14は、受信した立上用設定値と立下用設定値との差分を用いてDQS信号のデューティを算出し、操作者に通知する。

次に、図9を参照して、DQS信号の位相が内部クロック(CLK)に対し、遅れている場合のデューティ算出処理の全体的な流れを説明する。図9は、DQS信号の位相が遅れている場合のデューティ算出処理のタイミングチャートである。

図9の横軸は時間の経過を表す。また、信号501は、立上用先行信号を表す。また、信号502は、立上用後行信号を表す。また、信号503は、立上用IH信号を表す。また、信号504は、立下用先行信号を表す。また、信号505は、立下用後行信号を表す。また、信号506は、立下用IH信号を表す。信号501及び信号502は、立上用IH信号503がLowの場合に値が取得される。すなわち、B0、B1、及びB2のタイミングで、ラッチ113は、信号501及び信号502の値を取得する。信号504及び信号505は、立下用IH信号506がLowの場合に値が取得される。すなわち、A0、A1、及びA2のタイミングで、ラッチ123は、信号504及び信号505の値を取得する。

立上り側位相調整では、可変遅延付加部111は、信号501に立上用設定値が「n+1」分の可変遅延を与えている(ステップS50)。信号502は、信号501に固定遅延が付加された信号となっている。

タイミングB0において、ラッチ113は、信号501及び信号502の値を取得する(ステップS51)。この場合、ラッチ113は、信号501の値として「0」を取得し、信号502の値として「0」を取得する。位相判定部114は、「00」という位相情報をラッチ113から受ける(ステップS52)。

位相判定部114は、遅れた位相状態であると判定する。そして、位相判定部114は、遅れた位相状態である旨を可変遅延制御部115へ通知する(ステップS53)。可変遅延制御部115は、立上用設定値から1を減算し新たな立上用設定値を求める。図9では、可変遅延制御部115は、「n+1」であった立上用設定値から1を減算して、新たな立上用設定値として「n」を求めている。そして、可変遅延制御部115は、求めた立上用設定値を可変遅延付加部111へ通知する(ステップS54)。

可変遅延付加部111は、立上用設定値の入力を可変遅延制御部115から受けて、1ステップ分遅延量を減少させた遅延をDQS信号に与える(ステップS55)。

タイミングB1において、ラッチ113は、信号501及び信号502の値を取得する(ステップS56)。この場合、ラッチ113は、信号501の値として「1」を取得し、信号502の値として「0」を取得する。位相判定部114は、「01」という位相情報をラッチ113から受ける(ステップS57)。

位相判定部114は、位相情報が「01」であることから、一致した位相状態であると判定する(ステップS58)。そして、位相判定部114は、一致した位相状態である旨を可変遅延制御部115へ通知する。可変遅延制御部115は、位相が一致したことから、この時の立上用設定値を可変遅延設定値比較部13へ出力する(ステップS59)。

一方、立下り側位相調整では、可変遅延付加部121は、信号504に立下用設定値が「m+1」分の可変遅延を与えている(ステップS60)。信号505は、信号504に固定遅延が付加された信号となっている。

タイミングA0において、ラッチ123は、信号504及び信号505の値を取得する(ステップS61)。この場合、ラッチ123は、信号504の値として「1」を取得し、信号505の値として「1」を取得する。位相判定部124は、「11」という位相情報をラッチ123から受ける(ステップS62)。

位相判定部124は、遅れた位相状態であると判定する。そして、位相判定部124は、遅れた位相状態である旨を可変遅延制御部125へ通知する(ステップS63)。可変遅延制御部125は、立下用設定値から1を減算し新たな立下用設定値を求める。図9では、可変遅延制御部125は、「m+1」であった立下用設定値から1を減算して、新たな立下用設定値として「m」を求めている。そして、可変遅延制御部125は、求めた立下用設定値を可変遅延付加部121へ通知する(ステップS64)。

可変遅延付加部121は、立下用設定値の入力を可変遅延制御部125から受けて、1ステップ分遅延量を減少させた遅延をDQS信号に与える(ステップS65)。

タイミングA1において、ラッチ123は、信号504及び信号505の値を取得する(ステップS66)。この場合、ラッチ123は、信号504の値として「0」を取得し、信号502の値として「1」を取得する。位相判定部124は、「10」という位相情報をラッチ123から受ける(ステップS67)。

位相判定部124は、位相情報が「10」であることから、位相が一致した位相状態であると判定する。そして、位相判定部124は、一致した位相状態である旨を可変遅延制御部125へ通知する(ステップS68)。可変遅延制御部125は、位相が一致したことから、この時の立下用設定値を可変遅延設定値比較部13へ出力する(ステップS69)。

可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求める(ステップS70)。

その後、可変遅延設定値比較部13は、求めた差分をデューティ算出部14へ通知する。デューティ算出部14は、受信した立上用設定値と立下用設定値との差分を用いてDQS信号のデューティを算出し、操作者に通知する。

以上に説明したように、本実施例に係る信号制御回路であるメモリインタフェース回路は、DQS信号の立上りと内部クロック信号の立下りの位相を合わせるための立上用設定値に加えて、DQS信号の立下りと内部クロック信号の立下りの位相を合わせるための立下用設定値とを求める。そして、メモリインタフェース回路は、立上用設定値と立下用設定値の差分からDQS信号のデューティを求める。これにより、DQS信号の実際の状態に応じたデューティの測定が可能となる。また、操作者は、迅速にデューティの劣化を把握することができる。

なお、本実施例では、内部クロック信号の立下りでDQS信号の位相情報を取得する例で説明したが、内部クロック信号は立下りに限定するものではない。

また、既存の立上りの位相を合わせるための回路に加えて、立下り用の位相を合わせてその場合の遅延量を求める回路を設けることで、本願の機能を実現することができ、回路規模の増大を抑えつつ、デューティ測定の回路を実装することができる。

また、本実施例では、メモリコントローラ10の外部でデューティの算出を行ったが、これに限らず、メモリコントローラ10が、同様の計算を用いてデューティの算出を行い、求めたデューティをメモリコントローラ10の外部へ出力してもよい。

図13は、実施例3に係るメモリインタフェース回路のブロック図である。本実施例に係る情報処理システムは、立上用設定値と立下用設定値を同じ位相判定回路を用いて求めることが実施例1と異なるものである。以下の説明では、実施例1と同じ機能を有する各部については説明を省略する。

位相判定回路17は、図2における立上側位相判定回路11及び立下側位相判定回路12の機能をまとめた回路である。動作の概要としては、位相判定回路17は、最初に立上側位相判定回路11と同様の動作を行い立上用設定値を求め、次に立下側位相判定回路12と同様の動作を行い立下用設定値を求める。以下に詳細を説明する。

位相判定回路17は、可変遅延付加部171、固定遅延付加部172、ラッチ173、位相判定部174、及び可変遅延制御部175を有する。

可変遅延付加部171は、図2における可変遅延付加部111及び可変遅延付加部121と同様の動作を行う。

固定遅延付加部172は、図2における固定遅延付加部112及び固定遅延付加部122と同様の動作を行う。

ラッチ173は、立上りの位相判定を行う場合には、立上用IH信号の入力をエッジ切替部21から受ける。そして、ラッチ173は、図2におけるラッチ113と同様の動作を行う。また、立下りの位相判定を行う場合には、立下用IH信号の入力をエッジ切替部21から受ける。そして、ラッチ173は、図2におけるラッチ123と同様の動作を行う。

位相判定部174は、立上りの位相判定を行う場合、立上りのエッジを用いた位相判定を行うためのエッジ切替信号をエッジ切替信号発生部20から受ける。その場合、位相判定部174は、図2における位相判定部114と同様の動作を行う。また、位相判定部174は、立下りの位相判定を行う場合、立下りのエッジを用いた位相判定を行うためのエッジ切替信号をエッジ切替信号発生部20から受ける。その場合、位相判定部174は、図2における位相判定部124と同様の動作を行う。

加えて、位相判定部174は、求めた位相情報をエッジ切替信号発生部20へ出力する。

可変遅延制御部175は、立上りの位相判定を行う場合、立上りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。また、立上りの位相判定を行う場合、可変遅延制御部175は、可変遅延付加部171に返す可変遅延設定値として、立上用設定値をエッジ切替部22から受信する。その場合、可変遅延制御部175は、図2における可変遅延制御部115と同様に立上りの位相判定の処理における可変遅延設定値を求める。そして、可変遅延制御部175は、求めた立上りの位相判定処理における可変遅延設定値を順次上書きしながら立上用可変遅延設定値保持部18に格納する。その後、立上りの位相が一致すると、可変遅延制御部175は、立上用設定値の算出完了の通知を立上用可変遅延設定値保持部18へ出力する。

また、可変遅延制御部175は、立下りの位相判定を行う場合、立下りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。また、立下りの位相判定を行う場合、可変遅延制御部175は、可変遅延付加部171に返す可変遅延設定値として、立下用設定値をエッジ切替部22から受信する。その場合、可変遅延制御部175は、図2における可変遅延制御部125と同様に立下りの位相判定の処理における可変遅延設定値を求める。そして、可変遅延制御部175は、求めた立下りの位相判定における可変遅延設定値を順次上書きしながら立下用可変遅延設定値保持部19に格納する。その後、立下りの位相が一致すると、可変遅延制御部175は、立下用設定値の算出完了の通知を立上用可変遅延設定値保持部18へ出力する。

エッジ切替部21は、IH信号の入力を可変遅延制御部175から受ける。このIH信号は、実施例1における立上用IH信号と同様の信号である。

また、エッジ切替部21は、立上りの位相判定を行う場合、立上りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。この場合、エッジ切替部21は、可変遅延制御部175から受信したIH信号をラッチ173へ出力する。

また、エッジ切替部21は、立下りの位相判定を行う場合、立下りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。この場合、エッジ切替部21は、可変遅延制御部175から受信したIH信号を反転させ、実施例1における立下用IH信号と同様のIH信号を生成する。そして、エッジ切替部21は、生成したIH信号をラッチ173へ出力する。

立上用可変遅延設定値保持部18は、立上りの位相判定を行う場合、立上りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。そして、立上用可変遅延設定値保持部18は、立上りの位相判定における可変遅延設定値を可変遅遅延制御部175から受信し、順次上書きしながら格納していく。

そして、立上用可変遅延設定値保持部18は、立上用設定値の算出完了の通知の入力を可変遅延制御部175から受ける。この場合、立上用可変遅延設定値保持部18は、格納する可変遅延設定値を立上用設定値として可変遅延設定値比較部13へ出力する。

立下用可変遅延設定値保持部19は、立下りの位相判定を行う場合、立下りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。そして、立下用可変遅延設定値保持部19は、立下りの位相判定における可変遅延設定値を可変遅遅延制御部175から受信し、順次上書きしながら格納していく。

そして、立下用可変遅延設定値保持部19は、立下用設定値の算出完了の通知の入力を可変遅延制御部175から受ける。この場合、立下用可変遅延設定値保持部19は、格納する可変遅延設定値を立下用設定値として可変遅延設定値比較部13へ出力する。

エッジ切替部22は、立上りの位相判定を行う場合、立上りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。この場合、エッジ切替部22は、現在の立上りの位相判定処理における可変遅延設定値を立上用可変遅延設定値保持部18から取得する。そして、エッジ切替部22は、取得した可変遅延設定値を、可変遅延付加部171へ返す可変遅延設定値として可変遅延制御部175へ出力する。

また、エッジ切替部22は、立下りの位相判定を行う場合、立下りのエッジを用いた位相判定を行うためのエッジ切替の信号をエッジ切替信号発生部20から受ける。この場合、エッジ切替部22は、現在の立下りの位相判定処理における可変遅延設定値を立下用可変遅延設定値保持部19から取得する。そして、エッジ切替部22は、取得した可変遅延設定値を、可変遅延付加部171へ返す可変遅延設定値として可変遅延制御部175へ出力する。

可変遅延設定値比較部13は、立上用設定値の入力を立上用可変遅延設定値保持部18から受ける。また、可変遅延設定値比較部13は、立下用設定値の入力を立下用可変遅延設定値保持部19から受ける。その後、可変遅延設定値比較部13は、実施例1と同様の動作を行い立上り用設定値と立下用設定値の差分を求め、求めた差分をデューティ算出部14へ出力する。

エッジ切替信号発生部20は、位相情報の入力を位相判定部174から受ける。そして、エッジ切替信号発生部20は、位相情報の入力が所定の条件に達すると、位相判定を行うエッジを切り替えるための信号を位相判定部174、可変遅延制御部175、立上用可変遅延設定値保持部18、立下用可変遅延設定値保持部19、エッジ切替部21、及びエッジ切替部22へ出力する。以下に、エッジ切替信号発生部20によるエッジ切替信号の生成の例を説明する。

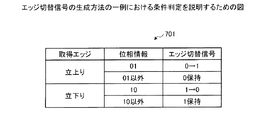

図14Aは、エッジ切替信号の生成方法の一例における条件判定を説明するための図である。また、図14Bは、エッジ切替信号の生成方法の一例のタイミングチャートである。

図14Aの表701におけるエッジ切替信号において値が「0」の場合は、立上りのエッジを位相判定に用いることを示す。また、表701におけるエッジ切替信号において値が「1」の場合は、立下りのエッジを位相判定に用いることを示す。また、表701の位相情報における2つ並んだ数字の組は、末尾bitが先行信号の位相情報を表し、先頭bitが後行信号の位相情報を表す。ここでも、先行信号及び後行信号の位相情報の組みを、単に「位相情報」という場合がある。

エッジ切替信号発生部20は、図14Aの表701に示すように、立上りの位相判定を行っている状態で位相情報が01になると、エッジ切替信号の値を「0」から「1」に変更する。また、エッジ切替信号発生部20は、立上りの位相判定を行っている状態で位相情報が01以外の場合、エッジ切替信号の値を「0」のまま保持する。さらに、エッジ切替信号発生部20は、立下りの位相判定を行っている状態で位相情報が10になると、エッジ切替信号の値を「1」から「0」に変更する。また、エッジ切替信号発生部20は、立下りの位相判定を行っている状態で位相情報が10以外の場合、エッジ切替信号の値を「1」のまま保持する。

この場合の、図14Bを参照して、位相情報の変化によるエッジ切替信号の変化を説明する。図14Bのタイムチャートは、立上りの位相判定を行っている場合から始まる。期間702では、位相情報は「01」以外である。この場合、エッジ切替信号発生部20は、「0」の値のエッジ切替信号を出力する。そして、タイミング703で位相情報が「01」に変化する。この場合、エッジ切替信号発生部20は、タイミング704でエッジ切替信号の値を「0」から「1」に変更する。続いて、期間705では、位相情報は「10」以外である。この場合、エッジ切替信号発生部20は、「1」の値のエッジ切替信号を出力する。そして、タイミング706で位相情報が「10」に変化する。この場合、エッジ切替信号発生部20は、タイミング707でエッジ切替信号の値を「1」から「0」に変更する。

次に、図15を参照して、エッジ切替信号の生成の一例を用いた場合のデューティ算出処理の流れを説明する。図15は、エッジ切替信号の生成の一例を用いた場合のデューティ算出処理のフローチャートである。

エッジ切替信号発生部20は、エッジ切替信号の値を「0」にする(ステップS101)。

位相判定回路17は、立上りを用いて位相判定を行う(ステップS102)。

エッジ切替信号発生部20は、位相情報の入力を位相判定部174から受ける。そして、エッジ切替信号発生部20は、位相情報が「01」となったか否かを判定する(ステップS103)。位相情報が「01」になっていない場合(ステップS103:否定)、エッジ切替信号発生部20は、ステップS102へ戻る。

これに対して、位相情報が「01」になった場合(ステップS103:肯定)、立上用可変遅延設定値保持部18は、立上用設定値を可変遅延設定値比較部13へ出力する(ステップS104)。

そして、エッジ切替信号発生部20は、エッジ切替信号の値を「1」に変更する(ステップS105)。

位相判定回路17は、立下りを用いて位相判定を行う(ステップS106)。

エッジ切替信号発生部20は、位相情報の入力を位相判定部174から受ける。そして、エッジ切替信号発生部20は、位相情報が「10」となったか否かを判定する(ステップS107)。位相情報が「10」になっていない場合(ステップS107:否定)、エッジ切替信号発生部20は、ステップS106へ戻る。

これに対して、位相情報が「10」になった場合(ステップS107:肯定)、立下用可変遅延設定値保持部19は、立下用設定値を可変遅延設定値比較部13へ出力する(ステップS108)。

そして、可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求め、求めた差分をデューティ算出部14へ出力する。デューティ算出部14は、DQS信号のデューティを算出し(ステップS109)、操作者へ通知する。

次に、エッジ切替信号の生成方法の他の例を説明する。この例では、エッジ切替信号発生部20は、位相情報の入力が所定回数行われると、位相判定を行うエッジを切り替える。例えば、エッジ切替信号発生部20は、位相情報が100回入力されると、立上りのエッジを位相判定に用いることを示す「0」の値のエッジ切替信号から、立下りのエッジを位相判定に用いることを示す「1」の値のエッジ切替信号へと切り替える。

図16は、エッジ切替信号の生成方法の他の例のタイミングチャートである。例えば、タイミング711で、エッジ切替信号発生部20が、エッジ切替信号の値を「0」から「1」に変更する。そして、エッジ切替信号発生部20は、位相情報の受信回数をカウントする。そして、エッジ切替信号発生部20は、位相情報の受信回数が100回になるまで値が「1」のエッジ切替信号を出力する。期間712で位相情報の受信回数が100回になったとすると、エッジ切替信号発生部20は、タイミング713で、エッジ切替信号の値を「1」から「0」に変更する。エッジ切替信号発生部20は、この処理を立上りの位相及び立下り信号の位相が一致するまで繰り返す。

次に、図17を参照して、エッジ切替信号の生成の他の例を用いた場合のデューティ算出処理の流れを説明する。図17は、エッジ切替信号の生成の他の例を用いた場合のデューティ算出処理のフローチャートである。

エッジ切替信号発生部20は、エッジ切替信号の値を「0」にする(ステップS201)。

そして、位相判定回路17は、立上りを用いて位相判定を行う(ステップS202)。

次に、エッジ切替信号発生部20は、位相情報の入力回数が100回終了したか否かを判定する(ステップS203)。

位相情報の入力回数が100回終了していない場合(ステップS203:否定)、エッジ切替信号発生部20は、ステップS202へ戻る。

これに対して、位相情報の入力回数が100回終了した場合(ステップS203:肯定)、位相判定回路17は、位相が一致したか否かを判定する(ステップS204)。

位相が一致していない場合(ステップS204:否定)、エッジ切替信号発生部20は、エッジ切替信号の値を「1」にする(ステップS205)。

そして、位相判定回路17は、立下りを用いて位相判定を行う(ステップS206)。

次に、エッジ切替信号発生部20は、位相情報の入力回数が100回終了したか否かを判定する(ステップS207)。

位相情報の入力回数が100回終了していない場合(ステップS207:否定)、エッジ切替信号発生部20は、ステップS206へ戻る。

これに対して、位相情報の入力回数が100回終了した場合(ステップS207:肯定)、位相判定回路17は、位相が一致したか否かを判定する(ステップS208)。

位相が一致していない場合(ステップS208:否定)、位相判定回路17は、ステップS201へ戻る。

一方、立上りの位相判定において位相が一致した場合(ステップS204:肯定)、立上用可変遅延設定値保持部18は、立上用設定値を可変遅延設定値比較部13へ出力する(ステップS209)。

そして、位相判定回路17は、立下りの位相が一致しているか否かを判定する(ステップS210)。立下りの位相が一致していない場合(ステップS210:否定)、メモリインタフェース回路1は、ステップS205へ進む。

これに対して、立下りの位相が一致している場合(ステップS210:肯定)、可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求め、求めた差分をデューティ算出部14へ出力する。デューティ算出部14は、DQS信号のデューティを算出し(ステップS213)、操作者へ通知する。

また、一方、立下りの位相判定において位相が一致した場合(ステップS208:肯定)、立下用可変遅延設定値保持部19は、立下用設定値を可変遅延設定値比較部13へ出力する(ステップS211)。これにより、立下りの位相判定は完了する。

そして、位相判定回路17は、立上りの位相が一致しているか否かを判定する(ステップS212)。立上りの位相が一致していない場合(ステップS212:否定)、メモリインタフェース回路1は、ステップS201へ進む。

これに対して、立上りの位相が一致している場合(ステップS212:肯定)、可変遅延設定値比較部13は、立上用設定値と立下用設定値との差分を求め、求めた差分をデューティ算出部14へ出力する。デューティ算出部14は、DQS信号のデューティを算出し(ステップS213)、操作者へ通知する。

ここでは、2つのエッジ切替信号の生成方法を説明したが、最終的に立上用設定値と立下用設定値が求まるのであれば方法はこれに限らない。

以上に説明した、位相判定回路17が、「遅延量取得部」の一例にあたる。

以上に説明したように、本実施例に係るメモリインタフェース回路は、1つの位相判定回路を用いて、立上用設定値及び立下用設定値を求める。すなわち、実施例1に比べて位相比較回路1つ分程度実装規模を縮小することができる。

また、以上の説明では、図1に示すように、メモリコントローラ10が、CPU3とは異なるチップセット100上に配置されている構成で説明したが、ハードウェア構成はこれに限らない。

図18は、ハードウェア構成の他の例の図である。各実施例に係るメモリインタフェース回路1を搭載したメモリコントローラ10は、図18に示すように、CPU3上に搭載されていてもよい。この場合、CPU3には、演算処理部31及びメモリコントローラ10が搭載される。

また、以上の説明では、デューティ算出部14がCPU3に含まれる場合を例に説明したが、デューティ算出部14の配置はこれに限らず、可変遅延設定値比較部13からのデータを受信できればどこに配置されてもよい。