JP6040035B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP6040035B2 JP6040035B2 JP2013007115A JP2013007115A JP6040035B2 JP 6040035 B2 JP6040035 B2 JP 6040035B2 JP 2013007115 A JP2013007115 A JP 2013007115A JP 2013007115 A JP2013007115 A JP 2013007115A JP 6040035 B2 JP6040035 B2 JP 6040035B2

- Authority

- JP

- Japan

- Prior art keywords

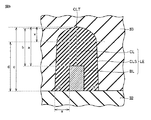

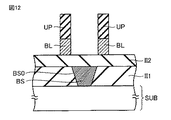

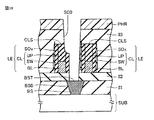

- insulating film

- bit line

- interlayer insulating

- semiconductor device

- conductive layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76832—Multiple layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76834—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers formation of thin insulating films on the sidewalls or on top of conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

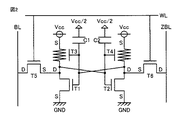

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

- H01L23/5223—Capacitor integral with wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Memories (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Thin Film Transistor (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013007115A JP6040035B2 (ja) | 2013-01-18 | 2013-01-18 | 半導体装置およびその製造方法 |

| US14/156,026 US9472495B2 (en) | 2013-01-18 | 2014-01-15 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013007115A JP6040035B2 (ja) | 2013-01-18 | 2013-01-18 | 半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014138141A JP2014138141A (ja) | 2014-07-28 |

| JP2014138141A5 JP2014138141A5 (enExample) | 2015-10-15 |

| JP6040035B2 true JP6040035B2 (ja) | 2016-12-07 |

Family

ID=51207098

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013007115A Active JP6040035B2 (ja) | 2013-01-18 | 2013-01-18 | 半導体装置およびその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9472495B2 (enExample) |

| JP (1) | JP6040035B2 (enExample) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6448424B2 (ja) * | 2015-03-17 | 2019-01-09 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| US10896873B2 (en) * | 2018-11-16 | 2021-01-19 | Google Llc | Massive deep trench capacitor die fill for high performance application specific integrated circuit (ASIC) applications |

| KR102890492B1 (ko) * | 2020-12-17 | 2025-11-26 | 삼성전자주식회사 | 반도체 소자 및 그의 제조 방법 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100258576B1 (ko) * | 1997-11-04 | 2000-06-15 | 윤종용 | 반도체 장치의 마이크로 콘택 형성 방법 |

| JP2001102550A (ja) * | 1999-09-02 | 2001-04-13 | Samsung Electronics Co Ltd | 自己整合コンタクトを有する半導体メモリ装置及びその製造方法 |

| KR100331568B1 (ko) * | 2000-05-26 | 2002-04-06 | 윤종용 | 반도체 메모리 소자 및 그 제조방법 |

| US6563162B2 (en) * | 2001-03-21 | 2003-05-13 | Samsung Electronics Co., Ltd. | Semiconductor memory device for reducing parasitic bit line capacitance and method of fabricating the same |

| KR100408411B1 (ko) * | 2001-06-01 | 2003-12-06 | 삼성전자주식회사 | 반도체 메모리 소자 및 그 제조방법 |

| JP2011077539A (ja) | 2003-06-30 | 2011-04-14 | Renesas Electronics Corp | 半導体装置とその製造方法 |

| JP4658486B2 (ja) | 2003-06-30 | 2011-03-23 | ルネサスエレクトロニクス株式会社 | 半導体装置とその製造方法 |

| US7247537B2 (en) * | 2003-08-18 | 2007-07-24 | Samsung Electronics Co., Ltd. | Semiconductor device including an improved capacitor and method for manufacturing the same |

| JP2009016596A (ja) * | 2007-07-05 | 2009-01-22 | Elpida Memory Inc | 半導体装置及び半導体装置の製造方法 |

| KR101283574B1 (ko) * | 2007-08-09 | 2013-07-08 | 삼성전자주식회사 | 질소를 함유하는 절연막 형성 방법 및 그것을 포함하는플래시 메모리 소자의 제조 방법 |

| JP2010040538A (ja) | 2008-07-31 | 2010-02-18 | Toshiba Corp | 半導体装置の製造方法 |

| JP2012054342A (ja) | 2010-08-31 | 2012-03-15 | Toshiba Corp | 半導体装置およびその製造方法 |

-

2013

- 2013-01-18 JP JP2013007115A patent/JP6040035B2/ja active Active

-

2014

- 2014-01-15 US US14/156,026 patent/US9472495B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US9472495B2 (en) | 2016-10-18 |

| US20140203441A1 (en) | 2014-07-24 |

| JP2014138141A (ja) | 2014-07-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11871559B2 (en) | Semiconductor device and method of manufacturing the same | |

| KR102471722B1 (ko) | 반도체 메모리 장치 | |

| KR100650468B1 (ko) | 반도체 집적 회로 장치 및 그 제조 방법 | |

| US6693008B1 (en) | Method of manufacturing a semiconductor integrated circuit device and a semiconductor integrated circuit device | |

| US8941162B2 (en) | Semiconductor device, method for forming the same, and data processing system | |

| KR102796606B1 (ko) | 반도체 장치 | |

| US10553593B2 (en) | Semiconductor devices | |

| KR20200061871A (ko) | 반도체 소자 및 그의 제조 방법 | |

| CN110071108A (zh) | 半导体存储器元件及其制作方法 | |

| JP5596260B2 (ja) | 半導体装置およびその製造方法 | |

| JP2012221965A (ja) | 半導体記憶装置及びその製造方法 | |

| US11665888B2 (en) | Semiconductor device and method for fabricating the same | |

| JP6040035B2 (ja) | 半導体装置およびその製造方法 | |

| JP5923334B2 (ja) | 半導体装置 | |

| US10062700B2 (en) | Semiconductor storage device and manufacturing method thereof | |

| US20240324188A1 (en) | Integrated circuit device and method of manufacturing the same | |

| EP4429434A1 (en) | Integrated circuit devices and methods of manufacturing the same | |

| US10991620B2 (en) | Semiconductor device | |

| TWI531025B (zh) | 記憶體單元、記憶體單元陣列及其製造方法 | |

| TWI722546B (zh) | 半導體元件及其製造方法 | |

| JP2014175647A (ja) | 半導体装置およびその製造方法 | |

| JP2015060864A (ja) | 半導体記憶装置およびその製造方法 | |

| KR20250121783A (ko) | 반도체 장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150827 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150827 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20160722 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160802 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160928 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20161018 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20161107 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6040035 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |