JP5806600B2 - 炭化珪素半導体装置の製造方法 - Google Patents

炭化珪素半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5806600B2 JP5806600B2 JP2011253556A JP2011253556A JP5806600B2 JP 5806600 B2 JP5806600 B2 JP 5806600B2 JP 2011253556 A JP2011253556 A JP 2011253556A JP 2011253556 A JP2011253556 A JP 2011253556A JP 5806600 B2 JP5806600 B2 JP 5806600B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon carbide

- region

- side wall

- trench

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 title claims description 69

- 229910010271 silicon carbide Inorganic materials 0.000 title claims description 68

- 238000000034 method Methods 0.000 title claims description 36

- 239000004065 semiconductor Substances 0.000 title claims description 33

- 238000004519 manufacturing process Methods 0.000 title claims description 27

- 238000005530 etching Methods 0.000 claims description 57

- 150000002500 ions Chemical class 0.000 claims description 7

- 230000000149 penetrating effect Effects 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 85

- 238000005452 bending Methods 0.000 description 19

- 239000013078 crystal Substances 0.000 description 12

- 239000007789 gas Substances 0.000 description 11

- 238000005468 ion implantation Methods 0.000 description 10

- 239000000758 substrate Substances 0.000 description 8

- 238000000151 deposition Methods 0.000 description 5

- 238000010884 ion-beam technique Methods 0.000 description 5

- 239000000463 material Substances 0.000 description 5

- 230000004048 modification Effects 0.000 description 5

- 238000012986 modification Methods 0.000 description 5

- 238000010438 heat treatment Methods 0.000 description 4

- 239000012535 impurity Substances 0.000 description 4

- 239000011229 interlayer Substances 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 3

- 241000526657 Microchloa Species 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 230000002349 favourable effect Effects 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- KZBUYRJDOAKODT-UHFFFAOYSA-N Chlorine Chemical compound ClCl KZBUYRJDOAKODT-UHFFFAOYSA-N 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- MYMOFIZGZYHOMD-UHFFFAOYSA-N Dioxygen Chemical compound O=O MYMOFIZGZYHOMD-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000000460 chlorine Substances 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 238000002050 diffraction method Methods 0.000 description 1

- 229910001873 dinitrogen Inorganic materials 0.000 description 1

- 229910001882 dioxygen Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 239000001307 helium Substances 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 239000001294 propane Substances 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7801—DMOS transistors, i.e. MISFETs with a channel accommodating body or base region adjoining a drain drift region

- H01L29/7802—Vertical DMOS transistors, i.e. VDMOS transistors

- H01L29/7813—Vertical DMOS transistors, i.e. VDMOS transistors with trench gate electrode, e.g. UMOS transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/3065—Plasma etching; Reactive-ion etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42356—Disposition, e.g. buried gate electrode

- H01L29/4236—Disposition, e.g. buried gate electrode within a trench, e.g. trench gate electrode, groove gate electrode

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66053—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide

- H01L29/66068—Multistep manufacturing processes of devices having a semiconductor body comprising crystalline silicon carbide the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/04—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes

- H01L29/045—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their crystalline structure, e.g. polycrystalline, cubic or particular orientation of crystalline planes by their particular orientation of crystalline planes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/12—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/16—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by the materials of which they are formed including, apart from doping materials or other impurities, only elements of Group IV of the Periodic System

- H01L29/1608—Silicon carbide

Description

Effect Transistor)が開示されている。また高いチャネル移動度を有するMOSFETを得るためには、トレンチ側壁の角度を特定の角度に制御する必要があることが開示されている。

これにより、常温下でイオン注入が行われるので、高温下でイオン注入が行われる場合に比して、イオン注入の際に生じる結晶欠陥の程度がより大きくなる。この結果、変質層に対する熱エッチングのエッチングレートがより高まるので、炭化珪素層中の変質層とそれ以外の部分とのエッチングレートの差異がより大きくなる。よって、互いに傾斜の程度が異なる第1および第2の側壁がより確実に形成される。

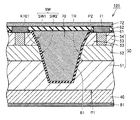

図1に示すように、本実施の形態の炭化珪素半導体装置としてのMOSFET(Metal Oxide Semiconductor Field Effect Transistor)101は、基板40と、エピタキシャル層(炭化珪素層)50と、ゲート絶縁膜61と、層間絶縁膜62と、ゲート電極70と、ソース電極71と、ソース配線電極72と、ドレイン電極81とを有する。

図2に示すように、基板40上にn型のエピタキシャル層50が形成される。このためのエピタキシャル成長は、たとえば原料ガスとしてシラン(SiH4)とプロパン(C3H8)との混合ガスを用い、キャリアガスとしてたとえば水素ガス(H2)を用いたCVD法により実施することができる。またエピタキシャル成長の際に、n型を付与するための導電型不純物としてたとえば窒素(N)またはリン(P)を導入することが好ましい。エピタキシャル層50のこのn型不純物の濃度は、たとえば5×1015cm-3以上5×1016cm-3以下である。

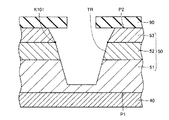

図9に示すように、MOSFET102においては、トレンチTRの内面上における上部側壁SW1および下部側壁SW2の間の屈曲点K102は、第2および第3の領域52、53の境界から離れて第3の領域53上に位置している。この変形例によれば、工程ばらつきによって屈曲点K102の位置がばらついても、下部側壁SW2が、第1および第2の領域51、52の境界と、第2および第3の領域52、53の境界とをより確実につなぐことができる。

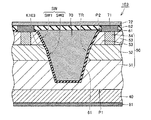

本実施の形態においては、まず実施の形態1における図5までと同様の工程が行われる。次に図11に示すように、エピタキシャル層50中にマスク90を用いてイオンを注入することにより、エピタキシャル層50中に変質層99が形成される。好ましくは、変質層99を形成する工程は、変質層99が第2の領域52よりも浅くに位置するように行われる。好ましくは、変質層99を形成する工程は常温下で行われる。次に実施の形態1と同様の熱エッチングが行われる。この場合、熱エッチングの前半過程において、図12に示すように、エピタキシャル層50のうち変質層99を含む領域が除去される。これにより形成される凹部は、屈曲点K2を有する。なおこれ以外の工程は実施の形態1とほぼ同様であるためその説明を省略する。

本実施の形態においては、実施の形態1における第3の領域53を形成するためのイオン注入(図3)において、結晶欠陥が特に生じやすいような方法が選択される。たとえば、第3の領域53を形成するためのイオン注入が常温下で行われる。この結果、第3の領域53の結晶性は、第2の領域52の結晶性に比して十分に低くなる。その後、実施の形態1における図5までと同様の工程が行われる。次に実施の形態1と同様の熱エッチングが行われる。この場合、熱エッチングの前半過程において、図13に示すように、エピタキシャル層50のうち第3の領域53が除去される。これにより形成される凹部は、屈曲点K3を有する。そして熱エッチングの後半工程を経て、たとえば図14に示すように、トレンチTRが形成される。なおこれ以外の工程は実施の形態1とほぼ同様であるためその説明を省略する。

Claims (7)

- 厚さ方向を有し、第1の主面と前記第1の主面に対して前記厚さ方向において対向する第2の主面とを有する炭化珪素層を準備する工程を備え、

前記炭化珪素層は、前記第1の主面をなし第1の導電型を有する第1の領域と、前記第1の領域上に設けられ、前記第1の導電型と異なる第2の導電型を有する第2の領域と、前記第2の領域の上に設けられ、前記第1の導電型を有する第3の領域とを含み、さらに

前記炭化珪素層の前記第2の主面上に、開口部を有するマスクを形成する工程と、

前記マスクを用いて前記炭化珪素層をエッチングすることにより、前記炭化珪素層の前記第2の主面に、内面を有し、前記第2および第3の領域を貫通するトレンチを形成する工程とを備え、

前記トレンチを形成する工程は、前記炭化珪素層を物理的にエッチングすることにより、前記炭化珪素層の前記第2の主面に凹部を形成する工程と、前記凹部の内面に対して熱エッチングを行うことで、前記トレンチの前記内面に、前記第2の主面に対して傾斜する第1の側壁と、前記第1の側壁よりも深くに位置し前記第2の主面に対して傾斜しかつ前記第2の領域からなる部分を有する第2の側壁とを設け、かつ、前記第2の主面に対する前記第1の側壁の傾斜を、前記第2の主面に対する前記第2の側壁の傾斜に比して小さくする工程とを含み、さらに

前記トレンチの前記内面を覆うゲート絶縁膜を形成する工程と、

前記トレンチの少なくとも一部を埋めるゲート電極を形成する工程とを備える、炭化珪素半導体装置の製造方法。 - 前記凹部を形成する工程は、前記凹部が前記第2の領域よりも浅くに位置するように行われる、請求項1に記載の炭化珪素半導体装置の製造方法。

- 前記凹部を形成する工程は、前記凹部の内面が、第1の側面と、前記第1の側面よりも深くに位置し、かつ前記第1の側面に対して傾斜した第2の側面とを含むように行われる、請求項2に記載の炭化珪素半導体装置の製造方法。

- 前記トレンチを形成する工程の前に、前記炭化珪素層中に前記マスクを用いてイオンを注入することにより、前記炭化珪素層中に変質層を形成する工程をさらに備え、

前記トレンチを形成する工程は、前記炭化珪素層のうち前記変質層を含む領域を熱エッチングにより除去する工程を含む、請求項1に記載の炭化珪素半導体装置の製造方法。 - 前記変質層を形成する工程は、前記変質層が前記第2の領域よりも浅くに位置するように行われる、請求項4に記載の炭化珪素半導体装置の製造方法。

- 前記変質層を形成する工程は常温下で行われる、請求項4または請求項5に記載の炭化珪素半導体装置の製造方法。

- 前記炭化珪素層を準備する工程は、前記第3の領域の結晶性が前記第2の領域の結晶性よりも低くなるように行われる、請求項1に記載の炭化珪素半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011253556A JP5806600B2 (ja) | 2011-11-21 | 2011-11-21 | 炭化珪素半導体装置の製造方法 |

| CN201280051725.2A CN103890952B (zh) | 2011-11-21 | 2012-09-12 | 碳化硅半导体器件及其制造方法 |

| EP12851689.5A EP2784821B1 (en) | 2011-11-21 | 2012-09-12 | Silicon carbide semiconductor device and method for manufacturing the same |

| PCT/JP2012/073284 WO2013077064A1 (ja) | 2011-11-21 | 2012-09-12 | 炭化珪素半導体装置およびその製造方法 |

| US13/658,672 US9293549B2 (en) | 2011-11-21 | 2012-10-23 | Silicon carbide semiconductor device and method for manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011253556A JP5806600B2 (ja) | 2011-11-21 | 2011-11-21 | 炭化珪素半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013110238A JP2013110238A (ja) | 2013-06-06 |

| JP2013110238A5 JP2013110238A5 (ja) | 2014-08-28 |

| JP5806600B2 true JP5806600B2 (ja) | 2015-11-10 |

Family

ID=48425954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011253556A Active JP5806600B2 (ja) | 2011-11-21 | 2011-11-21 | 炭化珪素半導体装置の製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US9293549B2 (ja) |

| EP (1) | EP2784821B1 (ja) |

| JP (1) | JP5806600B2 (ja) |

| CN (1) | CN103890952B (ja) |

| WO (1) | WO2013077064A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPWO2013031172A1 (ja) | 2011-08-26 | 2015-03-23 | 国立大学法人 奈良先端科学技術大学院大学 | SiC半導体素子およびその製造方法 |

| JP6065303B2 (ja) | 2012-06-15 | 2017-01-25 | ローム株式会社 | スイッチングデバイス |

| KR101723780B1 (ko) * | 2013-12-20 | 2017-04-05 | 엔지케이 인슐레이터 엘티디 | 질화갈륨층을 포함하는 기판 및 그 제조 방법 |

| JP6183224B2 (ja) * | 2014-01-16 | 2017-08-23 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2015220408A (ja) * | 2014-05-20 | 2015-12-07 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| JP6357869B2 (ja) * | 2014-05-20 | 2018-07-18 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2016048747A (ja) * | 2014-08-28 | 2016-04-07 | 株式会社豊田中央研究所 | トレンチゲート電極を備えている半導体装置 |

| JP6766512B2 (ja) * | 2016-08-05 | 2020-10-14 | 富士電機株式会社 | 半導体装置および半導体装置の製造方法 |

| JP2021190647A (ja) * | 2020-06-04 | 2021-12-13 | 豊田合成株式会社 | 半導体装置とその製造方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5436174A (en) * | 1993-01-25 | 1995-07-25 | North Carolina State University | Method of forming trenches in monocrystalline silicon carbide |

| JP3490857B2 (ja) * | 1996-11-25 | 2004-01-26 | 三洋電機株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP3976374B2 (ja) * | 1997-07-11 | 2007-09-19 | 三菱電機株式会社 | トレンチmosゲート構造を有する半導体装置及びその製造方法 |

| JP2000068505A (ja) * | 1998-08-20 | 2000-03-03 | Toshiba Corp | 半導体装置およびその製造方法 |

| JP5058406B2 (ja) * | 2000-10-31 | 2012-10-24 | ローム株式会社 | 半導体装置の製造方法 |

| JP2004520718A (ja) * | 2001-04-28 | 2004-07-08 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | トレンチ−ゲート構造半導体装置及びその製造方法 |

| JP4961668B2 (ja) * | 2005-01-11 | 2012-06-27 | 富士電機株式会社 | 半導体装置の製造方法 |

| JP2006351744A (ja) * | 2005-06-15 | 2006-12-28 | Fuji Electric Holdings Co Ltd | 炭化珪素半導体装置の製造方法 |

| JP5017823B2 (ja) * | 2005-09-12 | 2012-09-05 | 富士電機株式会社 | 半導体素子の製造方法 |

| JP5017855B2 (ja) * | 2005-12-14 | 2012-09-05 | 富士電機株式会社 | 半導体装置の製造方法 |

| JP2007227649A (ja) * | 2006-02-23 | 2007-09-06 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP5167593B2 (ja) * | 2006-03-23 | 2013-03-21 | 富士電機株式会社 | 半導体装置 |

| JP4450241B2 (ja) * | 2007-03-20 | 2010-04-14 | 株式会社デンソー | 炭化珪素半導体装置の製造方法 |

| JP5309587B2 (ja) | 2008-02-07 | 2013-10-09 | 富士電機株式会社 | 炭化珪素半導体基板のトレンチエッチング方法 |

| JP4877286B2 (ja) * | 2008-07-08 | 2012-02-15 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| JP2010182857A (ja) * | 2009-02-05 | 2010-08-19 | Renesas Electronics Corp | 半導体装置およびその製造方法 |

| CN102576723B (zh) * | 2009-10-23 | 2014-09-24 | 松下电器产业株式会社 | 半导体装置及其制造方法 |

| JP5699878B2 (ja) * | 2011-09-14 | 2015-04-15 | 住友電気工業株式会社 | 炭化珪素半導体装置およびその製造方法 |

| JP5834801B2 (ja) * | 2011-11-16 | 2015-12-24 | 住友電気工業株式会社 | 半導体装置の製造方法および半導体装置 |

-

2011

- 2011-11-21 JP JP2011253556A patent/JP5806600B2/ja active Active

-

2012

- 2012-09-12 EP EP12851689.5A patent/EP2784821B1/en active Active

- 2012-09-12 CN CN201280051725.2A patent/CN103890952B/zh active Active

- 2012-09-12 WO PCT/JP2012/073284 patent/WO2013077064A1/ja active Application Filing

- 2012-10-23 US US13/658,672 patent/US9293549B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN103890952B (zh) | 2016-12-07 |

| JP2013110238A (ja) | 2013-06-06 |

| US20130126904A1 (en) | 2013-05-23 |

| EP2784821A1 (en) | 2014-10-01 |

| US9293549B2 (en) | 2016-03-22 |

| CN103890952A (zh) | 2014-06-25 |

| EP2784821A4 (en) | 2015-07-15 |

| EP2784821B1 (en) | 2019-12-04 |

| WO2013077064A1 (ja) | 2013-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5806600B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP5741583B2 (ja) | 半導体装置およびその製造方法 | |

| JP2013110238A5 (ja) | ||

| JP5699878B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| US8999854B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| US9000447B2 (en) | Silicon carbide semiconductor device | |

| US10014376B2 (en) | Silicon carbide semiconductor device having a trench with side walls and method for manufacturing same | |

| TW201304146A (zh) | 半導體裝置及其製造方法 | |

| JP2012038771A (ja) | 半導体装置およびその製造方法 | |

| US9543412B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| JP6135383B2 (ja) | 炭化珪素半導体装置 | |

| US8927368B2 (en) | Method for manufacturing silicon carbide semiconductor device | |

| JP6233211B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP2015026723A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| US9299790B2 (en) | Silicon carbide semiconductor device | |

| JP6233210B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| US9679986B2 (en) | Silicon carbide semiconductor device | |

| JP6287642B2 (ja) | 炭化珪素半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140702 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140702 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20140702 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150204 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150526 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150625 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20150818 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20150904 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5806600 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |