JP5660076B2 - 半導体装置とその製造方法 - Google Patents

半導体装置とその製造方法 Download PDFInfo

- Publication number

- JP5660076B2 JP5660076B2 JP2012101297A JP2012101297A JP5660076B2 JP 5660076 B2 JP5660076 B2 JP 5660076B2 JP 2012101297 A JP2012101297 A JP 2012101297A JP 2012101297 A JP2012101297 A JP 2012101297A JP 5660076 B2 JP5660076 B2 JP 5660076B2

- Authority

- JP

- Japan

- Prior art keywords

- printed circuit

- circuit board

- flat cable

- flat

- wire

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 51

- 238000004519 manufacturing process Methods 0.000 title claims description 18

- 239000000758 substrate Substances 0.000 claims description 23

- 238000000576 coating method Methods 0.000 claims description 20

- 239000011248 coating agent Substances 0.000 claims description 19

- 238000005452 bending Methods 0.000 claims description 5

- 229920005992 thermoplastic resin Polymers 0.000 claims description 3

- 238000000034 method Methods 0.000 description 13

- 239000000919 ceramic Substances 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 229910000679 solder Inorganic materials 0.000 description 3

- 238000005476 soldering Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 238000001179 sorption measurement Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0296—Conductive pattern lay-out details not covered by sub groups H05K1/02 - H05K1/0295

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/36—Assembling printed circuits with other printed circuits

- H05K3/368—Assembling printed circuits with other printed circuits parallel to each other

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/4554—Coating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/4554—Coating

- H01L2224/45565—Single coating layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/04—Assemblies of printed circuits

- H05K2201/042—Stacked spaced PCBs; Planar parts of folded flexible circuits having mounted components in between or spaced from each other

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10227—Other objects, e.g. metallic pieces

- H05K2201/10356—Cables

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/49—Method of mechanical manufacture

- Y10T29/49002—Electrical device making

- Y10T29/49117—Conductor or circuit manufacturing

- Y10T29/49124—On flat or curved insulated base, e.g., printed circuit, etc.

- Y10T29/49126—Assembling bases

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Combinations Of Printed Boards (AREA)

- Wire Bonding (AREA)

- Pressure Sensors (AREA)

Description

図1は、本発明の実施の形態1に係る半導体装置の断面図である。半導体装置10は、絶縁基板12を備えている。絶縁基板12の表面には、配線パターン14、16、18が形成されている。絶縁基板12の裏面には裏面パターン20が形成されている。

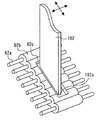

本発明の実施の形態2に係る半導体装置とその製造方法は、実施の形態1との一致点が多い。そのため実施の形態1との相違点を中心に説明する。図8は、本発明の実施の形態2に係る半導体装置の断面図である。この半導体装置は、中継端子150を有している。中継端子150の下部はケース70に固定されている。

本発明の実施の形態3に係る半導体装置とその製造方法は、実施の形態1との一致点が多い。そのため実施の形態1との相違点を中心に説明する。図9は、本発明の実施の形態3に係る半導体装置の断面図である。この半導体装置は、フラットケーブル200を有している。フラットケーブル200の一端は第1プリント基板50に接続され、他端は半導体素子30に接続されている。なお、フラットケーブル200はフラットケーブル62と同じものである。

Claims (9)

- 第1プリント基板と、

電線と、前記電線の両端を露出させつつ前記電線を覆う被膜を有し、前記電線の一端が前記第1プリント基板に接続されたフラットケーブルと、

前記電線の他端と接続された第2プリント基板と、を備え、

前記フラットケーブルは、前記第1プリント基板と前記第2プリント基板を対向させるように屈曲しており、

前記被膜の上面又は下面の一部には平坦面が形成され、前記被膜の上面と下面のうち前記平坦面が形成されていない部分は曲面であることを特徴とする半導体装置。 - 前記被膜は熱可塑性樹脂で形成されたことを特徴とする請求項1に記載の半導体装置。

- 前記平坦面は前記電線と略直交する方向に伸びる細長い形状であり、

前記フラットケーブルは、前記平坦面が形成された部分に沿って屈曲することを特徴とする請求項1に記載の半導体装置。 - 絶縁基板と、

前記絶縁基板の上に形成された半導体素子と、

一端が前記半導体素子と電気的に接続され、他端が前記第1プリント基板に電気的に接続された導線を備えたことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。 - 前記半導体素子と接続されたワイヤと、

前記ワイヤと接続された中継端子と、を備え、

前記導線の一端は前記中継端子と接続されたことを特徴とする請求項4に記載の半導体装置。 - 前記導線の一端は前記半導体素子と接続されたことを特徴とする請求項4に記載の半導体装置。

- 前記導線は、フラットケーブル又はボンディングワイヤであることを特徴とする請求項4乃至6のいずれか1項に記載の半導体装置。

- 電線の両端を露出させつつ前記電線を覆い上面と下面は曲面である被膜を有するフラットケーブルの前記上面又は前記下面の一部に、平坦面を形成する工程と、

平坦な吸着面を有する吸着器の前記吸着面を前記平坦面に当てて、前記吸着器で前記フラットケーブルを保持しつつ移動させ、前記フラットケーブルの一端を第1プリント基板に接続し他端を第2プリント基板に接続する工程と、

前記フラットケーブルを折り曲げて前記第1プリント基板と前記第2プリント基板を対向させる工程と、を備えたことを特徴とする半導体装置の製造方法。 - 前記平坦面は前記電線と略直交する方向に伸びる細長い形状であり、

前記フラットケーブルを折り曲げる際は、前記平坦面が形成された部分に沿って前記フラットケーブルを折り曲げることを特徴とする請求項8に記載の半導体装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012101297A JP5660076B2 (ja) | 2012-04-26 | 2012-04-26 | 半導体装置とその製造方法 |

| US13/828,142 US9125308B2 (en) | 2012-04-26 | 2013-03-14 | Semiconductor device and method of manufacturing thereof |

| DE102013204565.4A DE102013204565B4 (de) | 2012-04-26 | 2013-03-15 | Halbleitervorrichtung und Verfahren zum Herstellen derselben |

| CN201310147145.XA CN103379735B (zh) | 2012-04-26 | 2013-04-25 | 半导体装置及其制造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2012101297A JP5660076B2 (ja) | 2012-04-26 | 2012-04-26 | 半導体装置とその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2013229489A JP2013229489A (ja) | 2013-11-07 |

| JP2013229489A5 JP2013229489A5 (ja) | 2014-10-09 |

| JP5660076B2 true JP5660076B2 (ja) | 2015-01-28 |

Family

ID=49323389

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012101297A Active JP5660076B2 (ja) | 2012-04-26 | 2012-04-26 | 半導体装置とその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US9125308B2 (ja) |

| JP (1) | JP5660076B2 (ja) |

| CN (1) | CN103379735B (ja) |

| DE (1) | DE102013204565B4 (ja) |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS4860075U (ja) * | 1971-11-12 | 1973-07-31 | ||

| JPS5340476U (ja) * | 1976-09-10 | 1978-04-07 | ||

| JPS5943593A (ja) | 1982-09-06 | 1984-03-10 | 富士通株式会社 | 電子回路モジユ−ルの製造方法 |

| DE8413336U1 (de) | 1984-05-02 | 1984-08-23 | Gossen Gmbh, 8520 Erlangen | Flachbandkabel |

| JP2678327B2 (ja) * | 1991-02-15 | 1997-11-17 | 住友金属鉱山株式会社 | フレキシブル配線基板およびその製造方法 |

| US5428190A (en) * | 1993-07-02 | 1995-06-27 | Sheldahl, Inc. | Rigid-flex board with anisotropic interconnect and method of manufacture |

| JP3286104B2 (ja) * | 1995-01-24 | 2002-05-27 | ヒロセ電機株式会社 | 保持体付同軸セミリジッドケーブル組立体 |

| JP3430192B2 (ja) * | 1996-11-12 | 2003-07-28 | 株式会社日立産機システム | インバータ装置 |

| JPH10209594A (ja) * | 1997-01-17 | 1998-08-07 | Fuji Photo Optical Co Ltd | フレキシブルプリント回路基板と硬質プリント回路基板との接続構造 |

| CN1186971C (zh) * | 1999-04-22 | 2005-01-26 | 罗姆股份有限公司 | 印刷电路板、电池组件和印刷电路板的制造方法 |

| JP3667176B2 (ja) * | 1999-11-12 | 2005-07-06 | 平河ヒューテック株式会社 | フラットケーブルおよびその製造方法 |

| JP4667652B2 (ja) | 2001-06-12 | 2011-04-13 | ローム株式会社 | 電池パック、およびその製造方法 |

| JP4330294B2 (ja) | 2001-08-10 | 2009-09-16 | 三菱電機株式会社 | 電力用半導体装置 |

| JP2003100156A (ja) | 2001-09-26 | 2003-04-04 | Canon Inc | ケーブル及び電子機器 |

| JP2004297972A (ja) * | 2003-03-28 | 2004-10-21 | Toyota Industries Corp | 半導体装置 |

| JP4265394B2 (ja) * | 2003-12-17 | 2009-05-20 | 株式会社日立製作所 | 電力変換装置 |

| US7148428B2 (en) | 2004-09-27 | 2006-12-12 | Intel Corporation | Flexible cable for high-speed interconnect |

| JP4673211B2 (ja) * | 2005-12-27 | 2011-04-20 | 日立オートモティブシステムズ株式会社 | 電力変換装置 |

| DE112008002140B4 (de) | 2007-09-21 | 2014-01-30 | Mitsubishi Electric Corp. | Befestigungsstruktur und Befestigungsanordnung mit einer flexiblen Leiterplatte |

| JP2010105640A (ja) | 2008-10-31 | 2010-05-13 | Nsk Ltd | 電動パワーステアリング装置 |

| JP2010165914A (ja) | 2009-01-16 | 2010-07-29 | Toshiba Carrier Corp | インバータ装置及びインバータ装置の製造方法 |

| JP5153706B2 (ja) | 2009-03-26 | 2013-02-27 | 京セラ株式会社 | Ecu用混成集積回路装置 |

| JP5375408B2 (ja) * | 2009-07-24 | 2013-12-25 | 住友電気工業株式会社 | 同軸線ハーネス |

| WO2012039114A1 (ja) * | 2010-09-24 | 2012-03-29 | オンセミコンダクター・トレーディング・リミテッド | 回路装置 |

| JP5579576B2 (ja) | 2010-11-08 | 2014-08-27 | サンドビック株式会社 | 無端ベルトの製造方法及び装着方法 |

-

2012

- 2012-04-26 JP JP2012101297A patent/JP5660076B2/ja active Active

-

2013

- 2013-03-14 US US13/828,142 patent/US9125308B2/en active Active

- 2013-03-15 DE DE102013204565.4A patent/DE102013204565B4/de active Active

- 2013-04-25 CN CN201310147145.XA patent/CN103379735B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20130286622A1 (en) | 2013-10-31 |

| DE102013204565B4 (de) | 2023-04-20 |

| JP2013229489A (ja) | 2013-11-07 |

| CN103379735B (zh) | 2016-06-08 |

| US9125308B2 (en) | 2015-09-01 |

| DE102013204565A1 (de) | 2013-10-31 |

| CN103379735A (zh) | 2013-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6305302B2 (ja) | 半導体装置およびその製造方法 | |

| KR100935854B1 (ko) | 와이어 본딩 및 기준 와이어 본딩에 의해 제어되는 임피던스를 가진 마이크로전자 어셈블리 | |

| KR20090009737A (ko) | 반도체장치 및 그 제조방법 | |

| US7071543B2 (en) | Semiconductor device and manufacturing method thereof | |

| US20190254164A1 (en) | Circuit board, method of manufacturing circuit board, and electronic device | |

| JP2010027996A (ja) | 高周波モジュール及びその製造方法 | |

| KR102047775B1 (ko) | 칩 패키징 구조 및 관련된 인너 리드 본딩 방법 | |

| JP5415525B2 (ja) | 電気的なボンディング接続構造 | |

| JP2011159933A (ja) | 電力用半導体装置およびその製造方法 | |

| JP2011151103A (ja) | 電子部品相互の接続構造及び接続方法 | |

| JP2012222124A (ja) | 絶縁被膜付きコンデンサ及びその製造方法 | |

| JP5660076B2 (ja) | 半導体装置とその製造方法 | |

| JP2001102712A (ja) | コネクタ付きの配線基板、およびその製造方法 | |

| JP2010182828A (ja) | 電力用半導体モジュールとその製造方法 | |

| JP6312527B2 (ja) | 放熱板を備えた電子部品の実装構造 | |

| KR102004777B1 (ko) | 패키지 제조 방법 및 그를 이용한 패키지 | |

| JP5835166B2 (ja) | 半導体装置、半導体装置の製造方法 | |

| JP5229200B2 (ja) | 半導体装置の製造方法 | |

| US20150016069A1 (en) | Printed circuit board | |

| TWI571995B (zh) | 具有多連接導線之設備、具有多連接導線之晶片封裝以及用於保留導線框次結構之外部針腳的方法 | |

| JP4571012B2 (ja) | 台座付水晶振動子 | |

| US20130069217A1 (en) | Semiconductor device and electrode terminal | |

| JP7373703B2 (ja) | ケーブルの接合方法 | |

| JP4954778B2 (ja) | 三次元電子回路装置および連結部材 | |

| TW201724430A (zh) | 半導體裝置、導線架以及導線架的製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140516 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140516 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140821 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140827 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140924 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141007 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141104 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141117 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5660076 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |