JP5438358B2 - データ処理装置及びその制御方法 - Google Patents

データ処理装置及びその制御方法 Download PDFInfo

- Publication number

- JP5438358B2 JP5438358B2 JP2009097391A JP2009097391A JP5438358B2 JP 5438358 B2 JP5438358 B2 JP 5438358B2 JP 2009097391 A JP2009097391 A JP 2009097391A JP 2009097391 A JP2009097391 A JP 2009097391A JP 5438358 B2 JP5438358 B2 JP 5438358B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- programmable logic

- job

- cpu

- image processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N1/00—Scanning, transmission or reproduction of documents or the like, e.g. facsimile transmission; Details thereof

- H04N1/00962—Input arrangements for operating instructions or parameters, e.g. updating internal software

- H04N1/0097—Storage of instructions or parameters, e.g. customised instructions or different parameters for different user IDs

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F15/00—Digital computers in general; Data processing equipment in general

- G06F15/76—Architectures of general purpose stored program computers

- G06F15/78—Architectures of general purpose stored program computers comprising a single central processing unit

- G06F15/7867—Architectures of general purpose stored program computers comprising a single central processing unit with reconfigurable architecture

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/12—Digital output to print unit, e.g. line printer, chain printer

- G06F3/1201—Dedicated interfaces to print systems

- G06F3/1223—Dedicated interfaces to print systems specifically adapted to use a particular technique

- G06F3/1237—Print job management

- G06F3/1253—Configuration of print job parameters, e.g. using UI at the client

- G06F3/1258—Configuration of print job parameters, e.g. using UI at the client by updating job settings at the printer

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N2201/00—Indexing scheme relating to scanning, transmission or reproduction of documents or the like, and to details thereof

- H04N2201/0077—Types of the still picture apparatus

- H04N2201/0094—Multifunctional device, i.e. a device capable of all of reading, reproducing, copying, facsimile transception, file transception

Description

CPUと、前記CPUとは異なる画像処理部に含まれるプログラマブルロジックと、前記プログラマブルロジックを書換えるための複数種類の回路情報を記憶するメモリとを含むデータ処理装置であって、

前記CPUは、ジョブを入力した際に、当該ジョブを処理するために必要な種類の回路情報を示す設定データと前記ジョブのデータとを前記プログラマブルロジックに送信し、

前記プログラマブルロジックは、前記CPUから前記設定データを受信した際に、前記画像処理部による処理が完了している場合に、又は当該処理が完了するのを待って当該データにより示される種類の回路情報を前記メモリから読出して、当該回路情報を用いて前記プログラマブルロジックの配線を書換え、

前記画像処理部は、当該プログラマブルロジックの書換えが完了していないときは前記CPUから送信された前記ジョブのデータをバッファに保持し、当該プログラマブルロジックの書換えが完了した後に、当該バッファに保持された前記ジョブのデータに基づいて処理を実行することを特徴とする。

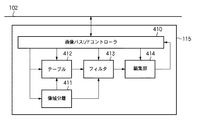

本発明の実施形態1では、MFPのプリンタ画像処理部117がFPGAで構成されていて、そのMFPがコピージョブを処理中にプリントジョブを受信した場合の処理方法について説明をする。

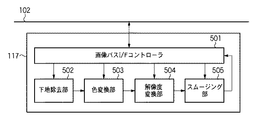

冒頭で述べたように、FPGAを含む回路の規模や動作速度の仕様は、ASICのように開示されない場合がある。その場合、そのような回路を2つ以上のブロックに分割することが行われる。そこで本実施形態2では、プリンタ画像処理部117の内部モジュールを2つに分割し、2つのFPGAをカスケード接続した場合の例を図13に示す。

以上、本発明の実施形態について詳述したが、本発明は、複数の機器から構成されるシステムに適用しても良いし、また一つの機器からなる装置に適用しても良い。

Claims (6)

- CPUと、前記CPUとは異なる画像処理部に含まれるプログラマブルロジックと、前記プログラマブルロジックを書換えるための複数種類の回路情報を記憶するメモリとを含むデータ処理装置であって、

前記CPUは、ジョブを入力した際に、当該ジョブを処理するために必要な種類の回路情報を示す設定データと前記ジョブのデータとを前記プログラマブルロジックに送信し、

前記プログラマブルロジックは、前記CPUから前記設定データを受信した際に、前記画像処理部による処理が完了している場合に、又は当該処理が完了するのを待って当該データにより示される種類の回路情報を前記メモリから読出して、当該回路情報を用いて前記プログラマブルロジックの配線を書換え、

前記画像処理部は、当該プログラマブルロジックの書換えが完了していないときは前記CPUから送信された前記ジョブのデータをバッファに保持し、当該プログラマブルロジックの書換えが完了した後に、当該バッファに保持された前記ジョブのデータに基づいて処理を実行することを特徴とするデータ処理装置。 - 前記プログラマブルロジックの配線の書換中に、前記バッファから前記プログラマブルロジックへの前記ジョブのデータの入力を禁止する第1の制御手段を更に有することを特徴とする請求項1に記載のデータ処理装置。

- 前記プログラマブルロジックの書換え中、又は前記プログラマブルロジックが処理を実行中に、前記CPUから前記プログラマブルロジックへの前記ジョブのデータの入力を禁止する第2の制御手段を更に有することを特徴とする請求項1又は2に記載のデータ処理装置。

- 前記プログラマブルロジックは、FPGAであることを特徴とする請求項1乃至3のいずれか1項に記載のデータ処理装置。

- 前記プログラマブルロジックは、リコンフィグアブルプロセッサであることを特徴とする請求項1乃至3のいずれか1項に記載のデータ処理装置。

- CPUと、前記CPUとは異なる画像処理部に含まれるプログラマブルロジックと、前記プログラマブルロジックを書換えるための複数種類の回路情報を記憶するメモリとを含むデータ処理装置の制御方法であって、

前記CPUが、ジョブを入力した際に、当該ジョブを処理するために必要な種類の回路情報を示す設定データと前記ジョブのデータとを前記プログラマブルロジックに送信する工程と、

前記プログラマブルロジックが、前記CPUから前記設定データを受信した際に、前記画像処理部による処理が完了している場合に、又は当該処理が完了するのを待って当該データにより示される種類の回路情報を前記メモリから読出して、当該回路情報を用いて前記プログラマブルロジックの配線を書換える書換え工程と、

前記画像処理部は、当該プログラマブルロジックの書換えが完了していないときは前記CPUから送信された前記ジョブのデータをバッファに保持し、当該プログラマブルロジックの書換えが完了した後に、当該バッファに保持された前記ジョブのデータに基づいて処理を実行する工程と、

を有することを特徴とするデータ処理装置の制御方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009097391A JP5438358B2 (ja) | 2009-04-13 | 2009-04-13 | データ処理装置及びその制御方法 |

| PCT/JP2010/053719 WO2010119736A1 (en) | 2009-04-13 | 2010-03-02 | Data processing apparatus and method for controlling the apparatus |

| US13/003,272 US8745564B2 (en) | 2009-04-13 | 2010-03-02 | Data processing apparatus and method for controlling the apparatus |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009097391A JP5438358B2 (ja) | 2009-04-13 | 2009-04-13 | データ処理装置及びその制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010251925A JP2010251925A (ja) | 2010-11-04 |

| JP2010251925A5 JP2010251925A5 (ja) | 2012-06-07 |

| JP5438358B2 true JP5438358B2 (ja) | 2014-03-12 |

Family

ID=42982404

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009097391A Expired - Fee Related JP5438358B2 (ja) | 2009-04-13 | 2009-04-13 | データ処理装置及びその制御方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8745564B2 (ja) |

| JP (1) | JP5438358B2 (ja) |

| WO (1) | WO2010119736A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5852320B2 (ja) * | 2011-04-13 | 2016-02-03 | キヤノン株式会社 | 画像形成装置及びその制御方法 |

| JP5546500B2 (ja) * | 2011-04-26 | 2014-07-09 | 三菱電機株式会社 | Fpga搭載装置の遠隔保守システム |

| KR20130057310A (ko) * | 2011-11-23 | 2013-05-31 | 삼성전자주식회사 | 화상독취장치 및 화상독취방법 |

| JP5943736B2 (ja) | 2012-06-28 | 2016-07-05 | キヤノン株式会社 | 情報処理装置、情報処理装置の制御方法及びプログラム |

| JP6036719B2 (ja) * | 2014-01-30 | 2016-11-30 | コニカミノルタ株式会社 | プログラム可能な論理回路デバイスを備えた電子装置および書き換え方法 |

| JP2015149025A (ja) * | 2014-02-07 | 2015-08-20 | キヤノン株式会社 | 画像処理装置およびその制御方法、並びにプログラム |

| JP6370063B2 (ja) * | 2014-03-04 | 2018-08-08 | キヤノン株式会社 | 画像処理装置及びその制御方法、並びにプログラム |

| JP6308821B2 (ja) * | 2014-03-13 | 2018-04-11 | キヤノン株式会社 | 画像処理装置 |

| JP2016035692A (ja) * | 2014-08-04 | 2016-03-17 | キヤノン株式会社 | 画像処理装置、システム、情報処理方法及びプログラム |

| JP2016042296A (ja) * | 2014-08-18 | 2016-03-31 | キヤノン株式会社 | 画像処理装置、情報処理方法及びプログラム |

| JP2016111633A (ja) * | 2014-12-09 | 2016-06-20 | キヤノン株式会社 | 回路情報に従って論理回路を構成可能な回路を持つデバイスと、複数の制御手段とを有する情報処理システム |

| US20180143860A1 (en) * | 2016-11-22 | 2018-05-24 | Intel Corporation | Methods and apparatus for programmable integrated circuit coprocessor sector management |

| JP6911600B2 (ja) * | 2017-07-18 | 2021-07-28 | 富士通株式会社 | 情報処理装置、情報処理方法および情報処理プログラム |

| WO2022219727A1 (ja) | 2021-04-13 | 2022-10-20 | Chiptip Technology株式会社 | 情報処理システム、情報処理装置、サーバ装置、プログラム、リコンフィグラブルデバイス、又は方法 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5684980A (en) * | 1992-07-29 | 1997-11-04 | Virtual Computer Corporation | FPGA virtual computer for executing a sequence of program instructions by successively reconfiguring a group of FPGA in response to those instructions |

| JP3351452B2 (ja) * | 1995-03-08 | 2002-11-25 | 日本電信電話株式会社 | プログラマブルゲートアレイ |

| JP3834935B2 (ja) | 1997-06-05 | 2006-10-18 | 富士ゼロックス株式会社 | 印刷処理装置 |

| JP3489608B2 (ja) * | 1997-06-20 | 2004-01-26 | 富士ゼロックス株式会社 | プログラマブル論理回路システムおよびプログラマブル論理回路装置の再構成方法 |

| JP2891979B1 (ja) * | 1998-02-06 | 1999-05-17 | 日本電気アイシーマイコンシステム株式会社 | 部分書き換え可能なpld |

| JPH11274915A (ja) * | 1998-03-25 | 1999-10-08 | Victor Co Of Japan Ltd | Fpgaの書換処理装置 |

| JP3587095B2 (ja) * | 1999-08-25 | 2004-11-10 | 富士ゼロックス株式会社 | 情報処理装置 |

| EP1630685B1 (en) * | 2000-01-07 | 2008-04-09 | Nippon Telegraph and Telephone Corporation | Function reconfigurable semiconductor device and integrated circuit configuring the semiconductor device |

| US8058899B2 (en) * | 2000-10-06 | 2011-11-15 | Martin Vorbach | Logic cell array and bus system |

| US7152151B2 (en) * | 2002-07-18 | 2006-12-19 | Ge Fanuc Embedded Systems, Inc. | Signal processing resource for selective series processing of data in transit on communications paths in multi-processor arrangements |

| JP4258137B2 (ja) * | 2001-05-30 | 2009-04-30 | 横河電機株式会社 | 監視装置 |

| JP3944639B2 (ja) * | 2002-06-17 | 2007-07-11 | コニカミノルタホールディングス株式会社 | プログラマブル論理装置 |

| JP3904072B2 (ja) | 2002-07-10 | 2007-04-11 | コニカミノルタホールディングス株式会社 | プログラマブル論理回路及びコンピュータシステム並びに回路の初期化方法 |

| JP3837136B2 (ja) * | 2004-02-12 | 2006-10-25 | 松下電器産業株式会社 | プログラマブル論理回路 |

| US7328335B1 (en) * | 2004-10-01 | 2008-02-05 | Xilinx, Inc. | Bootable programmable logic device for internal decoding of encoded configuration data |

| US7689726B1 (en) * | 2004-10-01 | 2010-03-30 | Xilinx, Inc. | Bootable integrated circuit device for readback encoding of configuration data |

| JP2006260654A (ja) * | 2005-03-16 | 2006-09-28 | Mitsubishi Electric Engineering Co Ltd | 論理処理装置 |

| JP2006352256A (ja) * | 2005-06-13 | 2006-12-28 | Canon Inc | プログラマブル論理回路及びその論理回路構成の再構築方法、並びにプログラム |

| JP2007251329A (ja) | 2006-03-14 | 2007-09-27 | Matsushita Electric Ind Co Ltd | プログラマブルロジックデバイス |

| JP5045036B2 (ja) * | 2006-09-05 | 2012-10-10 | 富士ゼロックス株式会社 | データ処理装置 |

-

2009

- 2009-04-13 JP JP2009097391A patent/JP5438358B2/ja not_active Expired - Fee Related

-

2010

- 2010-03-02 WO PCT/JP2010/053719 patent/WO2010119736A1/en active Application Filing

- 2010-03-02 US US13/003,272 patent/US8745564B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| WO2010119736A1 (en) | 2010-10-21 |

| JP2010251925A (ja) | 2010-11-04 |

| US8745564B2 (en) | 2014-06-03 |

| US20110109931A1 (en) | 2011-05-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5438358B2 (ja) | データ処理装置及びその制御方法 | |

| JP5247542B2 (ja) | 画像処理装置、画像処理装置の制御方法、及び、プログラム | |

| JP6308821B2 (ja) | 画像処理装置 | |

| JP4399490B2 (ja) | 画像出力装置 | |

| JP2007025882A (ja) | 省電力モードからの高速復帰手段 | |

| US8724161B2 (en) | Method, apparatus, and computer program product for processing image data of plural images to combine for output to a recording medium | |

| JP2010011468A (ja) | 画像処理装置及びその制御方法 | |

| JP5325902B2 (ja) | 画像形成装置 | |

| JP2006325260A (ja) | 画像形成システム | |

| JP5269044B2 (ja) | 画像処理装置及び画像形成装置 | |

| JP5563265B2 (ja) | 印刷装置及びその制御方法、並びにプログラム | |

| JP4078041B2 (ja) | 画像入出力装置、画像入出力方法、画像入出力システム、及び記憶媒体 | |

| JP2011103635A (ja) | 画像形成システム | |

| JP2007025881A (ja) | 省電力モードからの高速復帰手段 | |

| JP2006224595A (ja) | プリンティングシステム | |

| JP2006352256A (ja) | プログラマブル論理回路及びその論理回路構成の再構築方法、並びにプログラム | |

| EP3122028B1 (en) | Image processing apparatus and processing method | |

| JP2006171866A (ja) | 画像形成装置 | |

| JP2006236039A (ja) | マルチファンクションシステム | |

| JP2007004247A (ja) | 画像処理装置 | |

| JP2000172823A (ja) | 画像処理方法及び装置 | |

| JP2018086751A (ja) | 情報処理装置、情報処理装置の制御法及びプログラム | |

| JP2006015610A (ja) | 印刷システム及びその制御方法、プログラム | |

| JP2019175431A (ja) | 情報処理装置およびその制御方法 | |

| JP2004032048A (ja) | マルチファンクションシステム |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120413 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130513 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130809 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131007 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131213 |

|

| LAPS | Cancellation because of no payment of annual fees |