JP5404991B2 - Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 - Google Patents

Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 Download PDFInfo

- Publication number

- JP5404991B2 JP5404991B2 JP2006030036A JP2006030036A JP5404991B2 JP 5404991 B2 JP5404991 B2 JP 5404991B2 JP 2006030036 A JP2006030036 A JP 2006030036A JP 2006030036 A JP2006030036 A JP 2006030036A JP 5404991 B2 JP5404991 B2 JP 5404991B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- control

- converter

- voltage value

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 23

- 230000010355 oscillation Effects 0.000 claims description 143

- 239000003990 capacitor Substances 0.000 claims description 46

- 230000007423 decrease Effects 0.000 claims description 40

- 230000004044 response Effects 0.000 claims description 29

- 230000000737 periodic effect Effects 0.000 claims description 14

- 230000008569 process Effects 0.000 claims description 12

- 230000004913 activation Effects 0.000 claims description 7

- 230000003247 decreasing effect Effects 0.000 claims description 6

- 230000007704 transition Effects 0.000 description 21

- 208000028659 discharge Diseases 0.000 description 20

- 101100484930 Saccharomyces cerevisiae (strain ATCC 204508 / S288c) VPS41 gene Proteins 0.000 description 17

- 101100225969 Aquifex aeolicus (strain VF5) era gene Proteins 0.000 description 15

- 101100120423 Arabidopsis thaliana FTB gene Proteins 0.000 description 15

- 101100065508 Zea mays ERA1 gene Proteins 0.000 description 15

- 238000007599 discharging Methods 0.000 description 13

- 230000001360 synchronised effect Effects 0.000 description 12

- 238000009499 grossing Methods 0.000 description 11

- 101710170231 Antimicrobial peptide 2 Proteins 0.000 description 10

- 238000010586 diagram Methods 0.000 description 8

- 101710170230 Antimicrobial peptide 1 Proteins 0.000 description 6

- 102100029469 WD repeat and HMG-box DNA-binding protein 1 Human genes 0.000 description 3

- 101710097421 WD repeat and HMG-box DNA-binding protein 1 Proteins 0.000 description 3

- 238000001514 detection method Methods 0.000 description 3

- 238000005259 measurement Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000002441 reversible effect Effects 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 2

- 230000001960 triggered effect Effects 0.000 description 2

- 230000003321 amplification Effects 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

- H02M3/1563—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators without using an external clock

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

Description

例えば、本実施形態においては、容量素子CS1を備えて発振回路OSCが構成される場合について説明したが、制御端子を備えておき、容量素子を外付けとすることもできる。容量素子を外付けとすれば、発振信号CKにおける発振周波数の漸次な増減を自在に調整することができる。この場合、容量素子を外付けすることに代えて、外部の制御回路などから制御電圧を直接入力する構成とすることも可能である。

また、容量素子CS1を充放電する充電電流部として定電流回路I1を備え、放電電流部として放電用抵抗素子RD1を備える場合について説明したが、本発明はこれに限定されるものではない。定電流回路I1に代え、また定電流回路I1と共に、抵抗素子を備え、放電用抵抗素子RD1に代え、また放電用抵抗素子RD1と共に、停電流回路を備える構成とすることもできる。

(付記1)DC−DCコンバータの周期的なスイッチング制御のタイミングを指令する発振回路を備え、

前記発振回路は、前記スイッチング制御が停止状態と定常動作状態との間の遷移状態であって、時間経過に伴い前記DC−DCコンバータの出力電圧値が上昇していく遷移状態にあっては発振周波数を漸次増大し、時間経過に伴い前記DC−DCコンバータの出力電圧値が下降していく遷移状態にあっては発振周波数を漸次減少することを特徴とする電流制御型DC−DCコンバータの制御回路。

(付記2)前記DC−DCコンバータの主スイッチ素子をスイッチング制御するフリップフロップ回路を備え、

前記発振回路から出力される発振信号は、前記フリップフロップ回路のセット端子に入力されることを特徴とする付記1に記載の電流制御型DC−DCコンバータの制御回路。

(付記3) 起動指令に応じて端子電圧が漸次上昇し、停止指令に応じて端子電圧が漸次下降する電圧信号が入力される制御端子と、

前記制御端子の端子電圧に応じて、前記発振回路の発振周波数を設定する周波数設定部と

を備えることを特徴とする付記1に記載の電流制御型DC−DCコンバータの制御回路。

(付記4) 前記制御端子に対して電流出力を行なう第1電流部と、

前記起動指令に応じて、前記第1電流部を介して前記制御端子までの電流経路を確立する第1スイッチ回路と、

前記制御端子に対して電流引き込みを行なう第2電流部と、

前記停止指令に応じて、前記第2電流部を介して前記制御端子までの電流経路を確立する第2スイッチ回路と

を備えることを特徴とする付記3に記載の電流制御型DC−DCコンバータの制御回路。

(付記5) 前記第1電流部または/および前記第2電流部は、定電流源回路または/および抵抗素子を備えることを特徴とする付記4に記載の電流制御型DC−DCコンバータの制御回路。

(付記6) 前記周波数設定部は、

前記制御端子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記3に記載の電流制御型DC−DCコンバータの制御回路。

(付記7) 前記バッファ部は、

前記制御端子の端子電圧が入力される第1の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第2の非反転入力端子と

を備え、

前記バッファ部は、前記第1および第2の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記6に記載の電流制御型DC−DCコンバータの制御回路。

(付記8) 前記発振回路は、

起動指令に応じて漸次充電されて端子電圧が漸次上昇し、停止指令に応じて漸次放電されて前記端子電圧が漸次下降する第1容量素子と、

前記第1容量素子の端子電圧に応じて、発振周波数を設定する周波数設定部と

を備えることを特徴とする付記1に記載の電流制御型DC−DCコンバータの制御回路。

(付記9) 前記第1容量素子に対して充電を行なう充電電流部と、

前記起動指令に応じて、前記充電電流部を介して前記第1容量素子への充電経路を確立する第1スイッチ回路と、

前記第1容量素子に対して放電を行なう放電電流部と、

前記停止指令に応じて、前記放電電流部を介して前記第1容量素子からの放電経路を確立する第2スイッチ回路と

を備えることを特徴とする付記8に記載の電流制御型DC−DCコンバータの制御回路。

(付記10) 前記充電電流部または/および前記放電電流部は、定電流源回路または/および抵抗素子を備えることを特徴とする付記9に記載の電流制御型DC−DCコンバータの制御回路。

(付記11) 前記周波数設定部は、

前記第1容量素子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記8に記載の電流制御型DC−DCコンバータの制御回路。

(付記12) 前記バッファ部は、

前記第1容量素子の端子電圧が入力される第1の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第2の非反転入力端子と

を備え、

前記バッファ部は、前記第1および第2の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記11に記載の電流制御型DC−DCコンバータの制御回路。

(付記13)

周期的なスイッチング制御のタイミングを指令する発振回路を備え、

前記発振回路は、前記スイッチング制御が停止状態と定常動作状態との間の遷移状態であって、時間経過に伴い出力電圧値が上昇していく遷移状態にあっては発振周波数を漸次増大し、時間経過に伴い出力電圧値が下降していく遷移状態にあっては発振周波数を漸次減少することを特徴とする電流制御型DC−DCコンバータ。

(付記14)主スイッチ素子と、

前記主スイッチング素子をスイッチング制御するフリップフロップ回路とを備え、

前記発振回路から出力される発振信号は、前記フリップフロップ回路のセット端子に入力されることを特徴とする付記13に記載の電流制御型DC−DCコンバータ。

(付記15) 前記発振回路は、

起動指令に応じて漸次充電されて端子電圧が漸次上昇し、停止指令に応じて漸次放電されて前記端子電圧が漸次下降する第1容量素子と、

前記第1容量素子の端子電圧に応じて、前記発振回路の発振周波数を設定する周波数設定部と

を備えることを特徴とする付記13に記載の電流制御型DC−DCコンバータ。

(付記16) 前記第1容量素子に対して充電を行なう充電電流部と、

前記起動指令に応じて、前記充電電流部を介して前記第1容量素子への充電経路を確立する第1スイッチ回路と、

前記第1容量素子に対して放電を行なう放電電流部と、

前記停止指令に応じて、前記放電電流部を介して前記第1容量素子からの放電経路を確立する第2スイッチ回路と

を備えることを特徴とする付記13に記載の電流制御型DC−DCコンバータ。

(付記17) 前記充電電流部または/および前記放電電流部は、定電流源回路または/および抵抗素子を備えることを特徴とする付記16に記載の電流制御型DC−DCコンバータ。

(付記18) 前記周波数設定部は、

前記第1容量素子の端子電圧に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と

を備えることを特徴とする付記15に記載の電流制御型DC−DCコンバータ。

(付記19) 前記バッファ部は、

前記第1容量素子の端子電圧が入力される第1の非反転入力端子と、

前記定常動作状態における発振周波数を設定する定常設定電圧が入力される第2の非反転入力端子と

を備え、

前記バッファ部は、前記第1および第2の非反転入力端子に入力される電圧のうち低い電圧値を出力することを特徴とする付記18に記載の電流制御型DC−DCコンバータ。

(付記20) 周期的なスイッチング制御が行なわれる電流制御型DC−DCコンバータの制御方法であって、

定常動作状態において、第1周期でスイッチング制御を行なうステップと、

前記スイッチング制御が停止状態と定常動作状態との間の遷移状態であって、時間経過に伴い出力電圧値が上昇していく遷移状態にあっては、前記第1周期を最短周期として、発振周期を漸次増大し、時間経過に伴い出力電圧値が下降していく遷移状態にあっては、前記第1周期を最短周期として、発振周期を漸次減少するステップと

を有することを特徴とする電流制御型DC−DCコンバータの制御方法。

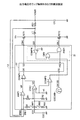

21 同期整流制御回路

(C2) ソフトスタート端子

(DH)、(DL) 出力端子

(FB0)、(FB1) 入力端子

(ID) 電流検出端子

AMP1、AMP2 電圧増幅器

C1 平滑コンデンサ

COMP1、COMP2、COMP3 電圧比較器

CS1 容量素子

CS2 ソフトスタート用容量素子

CT 周波数設定用容量素子

ERA1 誤差増幅器

FET1、FET2 MOSトランジスタ

FF フリップフロップ回路

FSET 周波数設定部

I1、I2 定電流回路

L1 チョークコイル

OSC 発振回路

RD1、RD2 放電用抵抗素子

RS1 電流測定抵抗

RT 電流設定用抵抗素子

SW11、SW12、SW21、SW22 スイッチ回路

VOUT 出力端子

e1 基準電圧

e11 定常設定電圧

CK 発振信号

VCS 容量素子CS1の端子電圧VCS

VH ピーク電圧

VIN 入力電圧

Claims (10)

- 電源電圧が供給され、DC−DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC−DCコンバータの出力電圧を漸次増加するように制御するランプ制御部とを備え、

前記発振回路は、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC−DCコンバータの制御回路。 - 前記制御電圧値は第一容量の端子電圧値であり、前記第一容量が前記起動信号に応じて充電されることにより前記制御電圧値が漸次増加することを特徴とする請求項1に記載のDC−DCコンバータの制御回路。

- 前記発振回路は、

前記漸次増加する制御電圧値に応じて前記発振周波数を設定する周波数設定部を備えることを特徴とする請求項2に記載のDC−DCコンバータの制御回路。 - 前記周波数設定部は、

前記漸次増加する制御電圧値に応じた電圧を出力するバッファ部と、

前記バッファ部の出力電圧に応じたバイアス電流を設定する電流設定部と、

前記バイアス電流により充電され、所定電圧に到達することに応じて放電される第二容量とを備えることを特徴とする請求項3に記載のDC−DCコンバータの制御回路。 - 電源電圧が供給され、DC−DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて増加し停止指令に応じて減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC−DCコンバータの出力電圧を増加または減少するように制御するランプ制御部とを備え、

前記発振回路は、前記増加または減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で増加または減少させることを特徴とするDC−DCコンバータの制御回路。 - 電源電圧が供給され、周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて出力電圧を漸次増加するように制御するランプ制御部とを備え、

前記発振回路は、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC−DCコンバータ。 - 前記制御電圧値は第一容量の端子電圧値であり、前記第一容量が前記起動信号に応じて充電されることにより前記制御電圧値が漸次増加することを特徴とする請求項6に記載のDC−DCコンバータ。

- 電源電圧が供給され、周期的なスイッチング制御のタイミングを制御する発振信号を出力する発振回路と、

起動指令に応じて増加し停止指令に応じて減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて出力電圧を増加または減少するように制御するランプ制御部とを備え、

前記発振回路は、前記増加または減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で増加または減少させることを特徴とするDC−DCコンバータ。 - DC−DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力するステップと、

起動指令に応じて漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて前記DC−DCコンバータの出力電圧を漸次増加するように制御するステップとを備え、

前記発振信号を出力するステップは、前記漸次増加する、前記電源電圧に基づく電圧値とは異なる制御電圧値に応じて、前記発振信号の周波数を前記出力電圧が漸次増加する過程で漸次増加させることを特徴とするDC−DCコンバータの制御方法。 - DC−DCコンバータの周期的なスイッチング制御のタイミングを制御する発振信号を出力するステップと、

起動指令に応じて増加し停止指令に応じて減少する制御電圧値に基づいて前記DC−DCコンバータの出力電圧を増加または減少するように、前記電源電圧に基づく電圧値とは異なる制御するステップとを備え、

前記発振信号を出力するステップは、前記増加または減少する、前記電源電圧に基づく電圧値とは異なる制御電圧値に基づいて、前記発振信号の周波数を前記出力電圧が増加または減少する過程で増加または減少させることを特徴とするDC−DCコンバータの制御方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006030036A JP5404991B2 (ja) | 2006-02-07 | 2006-02-07 | Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 |

| TW095118451A TWI312609B (en) | 2006-02-07 | 2006-05-24 | Current-controlled dc-dc converter control circuit, current-controlled dc-dc converter, and method for controlling current-controlled dc-dc converter |

| US11/447,853 US7663356B2 (en) | 2006-02-07 | 2006-06-07 | Current-controlled DC-DC converter control circuit, current-controlled DC-DC converter, and method for controlling current-controlled DC-DC converter |

| KR1020060053749A KR100793677B1 (ko) | 2006-02-07 | 2006-06-15 | 전류 제어형 dc―dc 컨버터 제어회로, 전류 제어형dc―dc 컨버터 및 전류 제어형 dc―dc 컨버터의제어 방법 |

| CN2006100829212A CN101018013B (zh) | 2006-02-07 | 2006-06-19 | 电流控制直流-直流变换器及其控制电路和控制方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006030036A JP5404991B2 (ja) | 2006-02-07 | 2006-02-07 | Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007215268A JP2007215268A (ja) | 2007-08-23 |

| JP2007215268A5 JP2007215268A5 (ja) | 2011-01-13 |

| JP5404991B2 true JP5404991B2 (ja) | 2014-02-05 |

Family

ID=38333396

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006030036A Active JP5404991B2 (ja) | 2006-02-07 | 2006-02-07 | Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7663356B2 (ja) |

| JP (1) | JP5404991B2 (ja) |

| KR (1) | KR100793677B1 (ja) |

| CN (1) | CN101018013B (ja) |

| TW (1) | TWI312609B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5071138B2 (ja) * | 2008-02-13 | 2012-11-14 | 富士電機株式会社 | 電流負帰還回路およびそれを用いるdc−dcコンバータ |

| US8076913B2 (en) * | 2008-12-22 | 2011-12-13 | Mediatek Inc. | Voltage converters and voltage generating methods for generating output voltage signals according to a pulse width modulation signal |

| US8963528B2 (en) * | 2010-04-30 | 2015-02-24 | Lockheed Martin Corporation | Method and means to implement fixed frequency operation of buck mode switching |

| JP2011258033A (ja) | 2010-06-10 | 2011-12-22 | Panasonic Corp | 定電圧回路 |

| KR101105681B1 (ko) | 2010-06-25 | 2012-01-18 | (주)실리콘인사이드 | 전류 구동 방식 스위치 모드 dc―dc 컨버터의 제어회로 |

| JP2012090387A (ja) * | 2010-10-18 | 2012-05-10 | Panasonic Corp | Dc−dcコンバータ |

| JP2012114987A (ja) * | 2010-11-22 | 2012-06-14 | Rohm Co Ltd | 電流モード同期整流dc/dcコンバータ |

| JP2012257408A (ja) * | 2011-06-09 | 2012-12-27 | Seiko Instruments Inc | スイッチングレギュレータ |

| JP5964125B2 (ja) * | 2012-04-24 | 2016-08-03 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 充電制御回路 |

| US9559592B2 (en) * | 2012-06-18 | 2017-01-31 | Nxp Usa, Inc. | Synchronous rectifier timer for discontinuous mode DC/DC converter |

| JP6422214B2 (ja) * | 2014-01-16 | 2018-11-14 | 矢崎総業株式会社 | スイッチング電源 |

| JP6403954B2 (ja) * | 2014-01-24 | 2018-10-10 | 矢崎総業株式会社 | スイッチング電源 |

| CN105553261B (zh) * | 2016-02-19 | 2018-09-25 | 京东方科技集团股份有限公司 | Dc-dc转换控制模块、dc-dc转换器及显示装置 |

| CN111725995A (zh) * | 2019-03-21 | 2020-09-29 | 深圳卓运半导体有限公司 | 用于直流-直流转换器的定时调整装置 |

| FR3102621B1 (fr) | 2019-10-24 | 2022-01-14 | St Microelectronics Grenoble 2 | Comparateur de tension |

| CN112290788B (zh) * | 2020-09-30 | 2022-04-26 | 昂宝电子(上海)有限公司 | 开关电源及其启动控制电路和方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4238708A (en) * | 1975-01-09 | 1980-12-09 | New Nippon Electric Company, Ltd. | Discharge lamp operating system |

| US4679131A (en) * | 1985-05-10 | 1987-07-07 | Rca Corporation | Regulating power supply for video display apparatus |

| JP3405871B2 (ja) | 1995-11-28 | 2003-05-12 | 富士通株式会社 | 直流−直流変換制御回路および直流−直流変換装置 |

| JPH11356053A (ja) * | 1998-04-09 | 1999-12-24 | Nagano Japan Radio Co | 電源装置 |

| JP2000324826A (ja) * | 1999-05-07 | 2000-11-24 | Sony Corp | スイッチング電源回路 |

| JP2001103734A (ja) * | 1999-09-28 | 2001-04-13 | Sony Corp | スイッチングコンバータ |

| JP4314709B2 (ja) * | 1999-12-28 | 2009-08-19 | ソニー株式会社 | スイッチング電源装置 |

| JP2002171750A (ja) * | 2000-12-04 | 2002-06-14 | Canon Inc | 電源装置 |

| JP2002354801A (ja) * | 2001-05-28 | 2002-12-06 | Sanken Electric Co Ltd | スイッチング電源装置 |

| JP3963258B2 (ja) * | 2001-11-27 | 2007-08-22 | 富士通株式会社 | Dc/dcコンバータ制御回路、及びdc/dcコンバータシステム |

| JP2003274643A (ja) * | 2002-03-13 | 2003-09-26 | Auto Network Gijutsu Kenkyusho:Kk | 直流電圧変換器 |

| US6879115B2 (en) * | 2002-07-09 | 2005-04-12 | International Rectifier Corporation | Adaptive ballast control IC |

| JP2005045993A (ja) * | 2003-07-10 | 2005-02-17 | Seiko Instruments Inc | Pwmスイッチングレギュレータ制御回路 |

| JP2005045856A (ja) * | 2003-07-22 | 2005-02-17 | Toshiba Corp | 無停電電源装置 |

| JP4651977B2 (ja) * | 2004-06-25 | 2011-03-16 | 富士通セミコンダクター株式会社 | Dc−dcコンバータの制御回路、およびその制御方法 |

| JP4347231B2 (ja) * | 2005-01-27 | 2009-10-21 | 富士通マイクロエレクトロニクス株式会社 | マルチフェーズdc−dcコンバータ及びマルチフェーズdc−dcコンバータの制御回路 |

| JP2006304512A (ja) * | 2005-04-21 | 2006-11-02 | Fujitsu Ltd | 昇降圧型dc−dcコンバータ、昇降圧型dc−dcコンバータの制御回路、昇降圧型dc−dcコンバータの制御方法 |

| JP2007116823A (ja) * | 2005-10-20 | 2007-05-10 | Fujitsu Ltd | Dc−dcコンバータの制御回路および制御方法 |

| JP4640985B2 (ja) * | 2005-12-20 | 2011-03-02 | 富士通セミコンダクター株式会社 | Dc−dcコンバータの制御回路および制御方法 |

-

2006

- 2006-02-07 JP JP2006030036A patent/JP5404991B2/ja active Active

- 2006-05-24 TW TW095118451A patent/TWI312609B/zh not_active IP Right Cessation

- 2006-06-07 US US11/447,853 patent/US7663356B2/en active Active

- 2006-06-15 KR KR1020060053749A patent/KR100793677B1/ko not_active IP Right Cessation

- 2006-06-19 CN CN2006100829212A patent/CN101018013B/zh active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US7663356B2 (en) | 2010-02-16 |

| JP2007215268A (ja) | 2007-08-23 |

| KR100793677B1 (ko) | 2008-01-10 |

| CN101018013B (zh) | 2011-08-10 |

| KR20070080539A (ko) | 2007-08-10 |

| CN101018013A (zh) | 2007-08-15 |

| TW200731649A (en) | 2007-08-16 |

| US20070182396A1 (en) | 2007-08-09 |

| TWI312609B (en) | 2009-07-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5404991B2 (ja) | Dc−dcコンバータの制御回路、dc−dcコンバータ、およびdc−dcコンバータの制御方法 | |

| JP2007215268A5 (ja) | ||

| TWI496394B (zh) | Switch regulator | |

| TWI290414B (en) | DC to DC converter, voltage converting device, method for controlling a converter and boost DC to DC converter | |

| TWI593224B (zh) | 升壓降壓型開關功率變換器及其控制電路 | |

| US9425688B2 (en) | Converter circuit and associated method | |

| US9431906B2 (en) | Voltage converter circuit and associated control method to improve transient performance | |

| US7957165B2 (en) | DC-DC converter with a plurality of soft-start control circuits | |

| US8773099B2 (en) | Methods to reduce output voltage ripple in constant on-time DC-DC converters | |

| EP1519473B1 (en) | Synchronization of multiphase synthetic ripple voltage regulator | |

| KR101411000B1 (ko) | 컨버터 및 그 구동방법 | |

| CN112994455A (zh) | 降压-升压式转换器及其控制方法 | |

| JP2010259257A (ja) | スイッチングレギュレータ及びその動作制御方法 | |

| CN111049375A (zh) | 开关转换器的节电模式脉冲选通控制 | |

| JP2007074190A (ja) | 三角波発生回路ならびにそれを用いたパルス幅変調器およびスイッチングレギュレータ | |

| KR102641551B1 (ko) | 강압형 dc-dc 컨버터 | |

| TW201010258A (en) | Apparatus and method for zero-voltage region detection, and control apparatus and control method for a power factor correction power converter | |

| CN110875686A (zh) | 电子转换器和操作电子转换器的方法 | |

| JP5951358B2 (ja) | 充電制御回路および充電回路 | |

| CN113098267B (zh) | 一种开关变换器、开关集成电路及其控制电路 | |

| CN111953209B (zh) | 开关型变换器及其控制电路和控制方法 | |

| JP2009124877A (ja) | 電源出力制御装置 | |

| CN112467976B (zh) | 开关变换器及其控制电路和控制方法 | |

| JP5563997B2 (ja) | 制御回路 | |

| JP4422583B2 (ja) | Dc−dc変換器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20070517 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070521 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080728 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081008 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101123 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110113 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120705 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130402 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130621 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20130621 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130628 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130822 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131002 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131030 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5404991 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |