JP5384038B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5384038B2 JP5384038B2 JP2008156353A JP2008156353A JP5384038B2 JP 5384038 B2 JP5384038 B2 JP 5384038B2 JP 2008156353 A JP2008156353 A JP 2008156353A JP 2008156353 A JP2008156353 A JP 2008156353A JP 5384038 B2 JP5384038 B2 JP 5384038B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- insulating film

- film

- substrate

- heat treatment

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 120

- 238000007667 floating Methods 0.000 claims description 54

- 239000012535 impurity Substances 0.000 claims description 28

- 239000000463 material Substances 0.000 claims description 22

- 239000010936 titanium Substances 0.000 claims description 12

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 claims description 11

- 239000013078 crystal Substances 0.000 claims description 10

- 230000015572 biosynthetic process Effects 0.000 claims description 9

- 229910052719 titanium Inorganic materials 0.000 claims description 9

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims description 8

- 229910052715 tantalum Inorganic materials 0.000 claims description 8

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims description 8

- 229910052721 tungsten Inorganic materials 0.000 claims description 8

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 7

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 7

- 239000010937 tungsten Substances 0.000 claims description 7

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 claims description 5

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 claims description 5

- 229910001936 tantalum oxide Inorganic materials 0.000 claims description 5

- 229910001930 tungsten oxide Inorganic materials 0.000 claims description 5

- 239000010410 layer Substances 0.000 description 206

- 239000000758 substrate Substances 0.000 description 176

- 238000010438 heat treatment Methods 0.000 description 93

- 230000015654 memory Effects 0.000 description 88

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 41

- 229910052814 silicon oxide Inorganic materials 0.000 description 39

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 32

- 150000002500 ions Chemical class 0.000 description 32

- 238000000034 method Methods 0.000 description 26

- 238000000926 separation method Methods 0.000 description 25

- 229910052581 Si3N4 Inorganic materials 0.000 description 19

- 230000004888 barrier function Effects 0.000 description 19

- 238000004519 manufacturing process Methods 0.000 description 19

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 19

- 239000001301 oxygen Substances 0.000 description 17

- 229910052760 oxygen Inorganic materials 0.000 description 17

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 16

- 229910052757 nitrogen Inorganic materials 0.000 description 16

- 239000001257 hydrogen Substances 0.000 description 14

- 229910052739 hydrogen Inorganic materials 0.000 description 14

- 239000011521 glass Substances 0.000 description 13

- 238000004891 communication Methods 0.000 description 10

- 239000000126 substance Substances 0.000 description 10

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 9

- 230000006870 function Effects 0.000 description 8

- 238000005468 ion implantation Methods 0.000 description 8

- 239000007789 gas Substances 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 6

- MWUXSHHQAYIFBG-UHFFFAOYSA-N Nitric oxide Chemical compound O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 6

- 230000008859 change Effects 0.000 description 6

- 238000000151 deposition Methods 0.000 description 6

- 238000010884 ion-beam technique Methods 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 230000001133 acceleration Effects 0.000 description 5

- 125000004429 atom Chemical group 0.000 description 5

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 230000008021 deposition Effects 0.000 description 5

- 239000011261 inert gas Substances 0.000 description 5

- 239000011229 interlayer Substances 0.000 description 5

- 230000001590 oxidative effect Effects 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 230000005855 radiation Effects 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000009792 diffusion process Methods 0.000 description 4

- 230000005684 electric field Effects 0.000 description 4

- 230000001771 impaired effect Effects 0.000 description 4

- 230000001681 protective effect Effects 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 229910052783 alkali metal Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 3

- 150000001342 alkaline earth metals Chemical class 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 239000002585 base Substances 0.000 description 3

- 238000002425 crystallisation Methods 0.000 description 3

- 230000008025 crystallization Effects 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 230000005660 hydrophilic surface Effects 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 229910021426 porous silicon Inorganic materials 0.000 description 3

- 238000004151 rapid thermal annealing Methods 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 239000005407 aluminoborosilicate glass Substances 0.000 description 2

- 239000005354 aluminosilicate glass Substances 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000000903 blocking effect Effects 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 150000002431 hydrogen Chemical class 0.000 description 2

- -1 hydrogen ions Chemical class 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 2

- 150000001282 organosilanes Chemical class 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 229910052708 sodium Inorganic materials 0.000 description 2

- 239000011734 sodium Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- YZCKVEUIGOORGS-OUBTZVSYSA-N Deuterium Chemical compound [2H] YZCKVEUIGOORGS-OUBTZVSYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 238000005411 Van der Waals force Methods 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 229910052805 deuterium Inorganic materials 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000005485 electric heating Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 235000013305 food Nutrition 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 1

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 1

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

- H01L29/7881—Programmable transistors with only two possible levels of programmation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/4234—Gate electrodes for transistors with charge trapping gate insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/511—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures

- H01L29/513—Insulating materials associated therewith with a compositional variation, e.g. multilayer structures the variation being perpendicular to the channel plane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66825—Unipolar field-effect transistors with an insulated gate, i.e. MISFET with a floating gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thin Film Transistor (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

- Recrystallisation Techniques (AREA)

Description

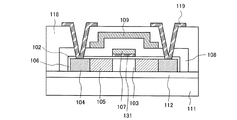

本実施の形態を、図1、図2(A)〜図2(C)、図3(A)〜図3(D)、図4(A)〜図4(C)、図5を用いて説明する。

本実施の形態では、無線交信可能な半導体装置において、本発明の記憶素子を用いた場合について、図6、図7(A)〜図7(B)を用いて説明する。

実施の形態2に基づいて作製された、無線交信可能な半導体装置200は、電磁波の送信と受信ができるという機能を活用して、様々な物品やシステムに用いることができる。物品とは、例えば、鍵(図8(A)参照)、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等、図8(B)参照)、書籍類、容器類(シャーレ等、図8(C)参照)、包装用容器類(包装紙やボトル等、図8(E)(F)参照)、記録媒体(ディスクやビデオテープ等)、乗物類(自転車等)、装身具(鞄や眼鏡等、図8(D)参照)、食品類、衣類、生活用品類、電子機器(液晶表示装置、EL表示装置、テレビジョン装置、携帯端末等)等である。

本実施の形態では、実施の形態1の島状半導体膜102を、SOI構造を有する基板を用いて形成する方法について、図9(A)〜図9(B)、図10(A)〜図10(C)、図11(A)〜図11(C)、図12(A)〜図12(B)、図13(A)〜図13(C)、図14(A)〜図14(C)、図15(A)〜図15(B)、図16(A)〜図16(C)を用いて説明する。

102 島状半導体膜

103 チャネル形成領域

104 高濃度不純物領域

105 低濃度不純物領域

106 トンネル絶縁膜

107 フローティングゲート

108 ゲート絶縁膜

109 コントロールゲート

111 基板

112 下地膜

113 非晶質半導体膜

114 結晶性半導体膜

115 レーザ光

118 層間絶縁膜

119 配線

121 低濃度不純物領域

131 絶縁膜

132 絶縁膜

200 半導体装置

201 演算処理回路

202 記憶回路

203 アンテナ

204 電源回路

205 復調回路

206 変調回路

207 リーダ/ライタ

300 支持基板

301 LTSS層

302 接合層

303 バリア層

304 絶縁層

305 酸化シリコン層

306 半導体基板

307 分離層

502 TFT

503 TFT

504 TFT

506 記憶素子

507 記憶素子

508 記憶素子

1021 メモリセル

1023 メモリセルアレイ

1024 ビット線駆動回路

1025 カラムデコーダ

1026 読み出し回路

1027 セレクタ

1028 インターフェース

1029 ワード線駆動回路

1030 ロウデコーダ

1031 レベルシフタ

1032 TFT

1033 記憶素子

Claims (5)

- 絶縁表面上に、

チャネル形成領域と高濃度不純物領域を有する島状半導体膜と、

前記島状半導体膜上に、トンネル絶縁膜と、

前記トンネル絶縁膜上に、フローティングゲートと、

前記フローティングゲート上に、ゲート絶縁膜と、

前記ゲート絶縁膜上に、コントロールゲートと、

前記トンネル絶縁膜と前記フローティングゲートとの間に、第1の絶縁膜と、

を有し、

前記フローティングゲートの材料は、チタン、タンタル、タングステンのいずれか1つであり、

前記第1の絶縁膜は、前記フローティングゲートの材料の酸化膜で形成されており、前記フローティングゲートの材料が、前記トンネル絶縁膜に拡散するのを防ぐことを特徴とする半導体装置。 - 請求項1において、

前記フローティングゲートと前記ゲート絶縁膜との間に、第2の絶縁膜と、

を有し、

前記第2の絶縁膜は、前記フローティングゲートの材料の酸化膜で形成されており、前記フローティングゲートの材料が、前記ゲート絶縁膜に拡散するのを防ぐことを特徴とする半導体装置。 - 請求項1または請求項2において、

前記第1の絶縁膜は、酸化チタン、酸化タンタル、酸化タングステンのいずれか1つであることを特徴とする半導体装置。 - 請求項2において、

前記第2の絶縁膜は、酸化チタン、酸化タンタル、酸化タングステンのいずれか1つであることを特徴とする半導体装置。 - 請求項1乃至請求項4のいずれか1項において、

前記島状半導体膜は、単結晶半導体層により形成されていることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008156353A JP5384038B2 (ja) | 2007-06-25 | 2008-06-16 | 半導体装置 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007166495 | 2007-06-25 | ||

| JP2007166495 | 2007-06-25 | ||

| JP2008156353A JP5384038B2 (ja) | 2007-06-25 | 2008-06-16 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009033118A JP2009033118A (ja) | 2009-02-12 |

| JP2009033118A5 JP2009033118A5 (ja) | 2011-07-07 |

| JP5384038B2 true JP5384038B2 (ja) | 2014-01-08 |

Family

ID=40135566

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008156353A Active JP5384038B2 (ja) | 2007-06-25 | 2008-06-16 | 半導体装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8319269B2 (ja) |

| JP (1) | JP5384038B2 (ja) |

| KR (1) | KR101520284B1 (ja) |

| CN (1) | CN101681885B (ja) |

| WO (1) | WO2009001733A1 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009001733A1 (en) * | 2007-06-25 | 2008-12-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| JP5576400B2 (ja) * | 2009-01-29 | 2014-08-20 | インターナショナル・ビジネス・マシーンズ・コーポレーション | フラッシュ・メモリ・デバイスおよびその製造方法 |

| US9202822B2 (en) * | 2010-12-17 | 2015-12-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| CN103597545B (zh) | 2011-06-09 | 2016-10-19 | 株式会社半导体能源研究所 | 高速缓冲存储器及其驱动方法 |

| JP6012263B2 (ja) | 2011-06-09 | 2016-10-25 | 株式会社半導体エネルギー研究所 | 半導体記憶装置 |

| JP6013685B2 (ja) | 2011-07-22 | 2016-10-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US8994019B2 (en) * | 2011-08-05 | 2015-03-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

| US9135182B2 (en) | 2012-06-01 | 2015-09-15 | Semiconductor Energy Laboratory Co., Ltd. | Central processing unit and driving method thereof |

| CN105140299B (zh) * | 2015-10-14 | 2017-12-15 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制备方法 |

| TWI686929B (zh) | 2016-05-20 | 2020-03-01 | 聯華電子股份有限公司 | 半導體元件 |

| CN105932032A (zh) * | 2016-06-16 | 2016-09-07 | 深圳市华星光电技术有限公司 | 一种阵列基板及其制备方法 |

| KR102684115B1 (ko) * | 2019-07-19 | 2024-07-12 | 에스케이하이닉스 주식회사 | 반도체 메모리 소자 |

| WO2021046734A1 (zh) * | 2019-09-11 | 2021-03-18 | 咸阳彩虹光电科技有限公司 | 开关元件和显示面板 |

| US11335775B2 (en) * | 2020-08-27 | 2022-05-17 | Micron Technology, Inc. | Integrated assemblies and methods of forming integrated assemblies |

Family Cites Families (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3996657A (en) | 1974-12-30 | 1976-12-14 | Intel Corporation | Double polycrystalline silicon gate memory device |

| JPH0758225A (ja) * | 1993-08-10 | 1995-03-03 | Oki Electric Ind Co Ltd | 不揮発性半導体記憶装置及びその形成方法 |

| JPH10233505A (ja) * | 1997-02-21 | 1998-09-02 | Hitachi Ltd | 半導体装置の製造方法 |

| JP3943245B2 (ja) * | 1997-09-20 | 2007-07-11 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| TW518650B (en) * | 1999-04-15 | 2003-01-21 | Semiconductor Energy Lab | Electro-optical device and electronic equipment |

| EP1220318A4 (en) * | 1999-09-30 | 2007-06-06 | Rohm Co Ltd | NON-VOLATILE MEMORY |

| JP2001326289A (ja) | 2000-03-08 | 2001-11-22 | Semiconductor Energy Lab Co Ltd | 不揮発性メモリおよび半導体装置 |

| JP2002198446A (ja) * | 2000-12-27 | 2002-07-12 | Fujitsu Ltd | 半導体記憶装置とその製造方法 |

| US6784480B2 (en) * | 2002-02-12 | 2004-08-31 | Micron Technology, Inc. | Asymmetric band-gap engineered nonvolatile memory device |

| US6586349B1 (en) * | 2002-02-21 | 2003-07-01 | Advanced Micro Devices, Inc. | Integrated process for fabrication of graded composite dielectric material layers for semiconductor devices |

| JP5046464B2 (ja) * | 2002-12-18 | 2012-10-10 | 株式会社半導体エネルギー研究所 | 半導体記憶素子の作製方法 |

| JP4860160B2 (ja) * | 2004-02-10 | 2012-01-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US7102191B2 (en) * | 2004-03-24 | 2006-09-05 | Micron Technologies, Inc. | Memory device with high dielectric constant gate dielectrics and metal floating gates |

| JP4942950B2 (ja) | 2004-05-28 | 2012-05-30 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US7504663B2 (en) * | 2004-05-28 | 2009-03-17 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device with a floating gate electrode that includes a plurality of particles |

| US7335556B2 (en) * | 2004-06-14 | 2008-02-26 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| US20070063147A1 (en) * | 2004-06-14 | 2007-03-22 | Semiconductor Energy Laboratory Co., Ltd. | Doping device |

| KR100688575B1 (ko) * | 2004-10-08 | 2007-03-02 | 삼성전자주식회사 | 비휘발성 반도체 메모리 소자 |

| US20090189215A1 (en) * | 2005-04-20 | 2009-07-30 | National University Of Singapore | Nonvolatile flash memory device and method for producing the same |

| JP4851740B2 (ja) * | 2005-06-30 | 2012-01-11 | 株式会社東芝 | 半導体装置およびその製造方法 |

| JP2007053171A (ja) * | 2005-08-16 | 2007-03-01 | Toshiba Corp | 不揮発性半導体メモリ装置 |

| JP4909552B2 (ja) * | 2005-09-12 | 2012-04-04 | 旭硝子株式会社 | 電荷保持特性に優れた不揮発性半導体記憶素子の製造方法 |

| JP4928890B2 (ja) * | 2005-10-14 | 2012-05-09 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP4575320B2 (ja) * | 2006-03-15 | 2010-11-04 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| TWI416738B (zh) * | 2006-03-21 | 2013-11-21 | Semiconductor Energy Lab | 非揮發性半導體記憶體裝置 |

| EP1837917A1 (en) * | 2006-03-21 | 2007-09-26 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device |

| EP1837900A3 (en) * | 2006-03-21 | 2008-10-15 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device |

| JP2007294911A (ja) | 2006-03-31 | 2007-11-08 | Semiconductor Energy Lab Co Ltd | 不揮発性半導体記憶装置 |

| EP1840947A3 (en) * | 2006-03-31 | 2008-08-13 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device |

| US8022460B2 (en) | 2006-03-31 | 2011-09-20 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device |

| WO2007138937A1 (en) * | 2006-05-26 | 2007-12-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US7994000B2 (en) * | 2007-02-27 | 2011-08-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method of manufacturing the same |

| US7791172B2 (en) * | 2007-03-19 | 2010-09-07 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile semiconductor memory device |

| WO2009001733A1 (en) * | 2007-06-25 | 2008-12-31 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device |

-

2008

- 2008-06-12 WO PCT/JP2008/061167 patent/WO2009001733A1/en active Application Filing

- 2008-06-12 KR KR1020107001655A patent/KR101520284B1/ko active IP Right Grant

- 2008-06-12 CN CN200880021052XA patent/CN101681885B/zh not_active Expired - Fee Related

- 2008-06-16 JP JP2008156353A patent/JP5384038B2/ja active Active

- 2008-06-20 US US12/143,472 patent/US8319269B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009033118A (ja) | 2009-02-12 |

| WO2009001733A1 (en) | 2008-12-31 |

| US8319269B2 (en) | 2012-11-27 |

| CN101681885A (zh) | 2010-03-24 |

| US20080315286A1 (en) | 2008-12-25 |

| KR20100033521A (ko) | 2010-03-30 |

| KR101520284B1 (ko) | 2015-05-14 |

| CN101681885B (zh) | 2013-09-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5384038B2 (ja) | 半導体装置 | |

| CN101669193B (zh) | Soi衬底及其制造方法和半导体器件 | |

| US8093135B2 (en) | Method of manufacturing semiconductor device | |

| US7528463B2 (en) | Semiconductor on insulator structure | |

| CN101393859B (zh) | 设置有半导体膜的衬底及其制造方法 | |

| US8765535B2 (en) | Method for manufacturing a capacitor having a yttrium oxide layer | |

| CN102593153A (zh) | 半导体衬底、半导体装置、以及其制造方法 | |

| KR20090037363A (ko) | Soi기판의 제작방법 | |

| KR20000011051A (ko) | 고체 물질의 박막을 얻는 방법 및 이 방법의 적용 | |

| JP2009076886A (ja) | 半導体装置の作製方法 | |

| TW200903709A (en) | Method for manufacturing semiconductor device | |

| US8072017B2 (en) | Nonvolatile semiconductor memory device | |

| US8198165B2 (en) | Method for manufacturing semiconductor device | |

| JP2009076729A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110519 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110519 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130821 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130827 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130903 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130924 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131002 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5384038 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |