JP5348939B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP5348939B2 JP5348939B2 JP2008123316A JP2008123316A JP5348939B2 JP 5348939 B2 JP5348939 B2 JP 5348939B2 JP 2008123316 A JP2008123316 A JP 2008123316A JP 2008123316 A JP2008123316 A JP 2008123316A JP 5348939 B2 JP5348939 B2 JP 5348939B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- substrate

- semiconductor

- semiconductor substrate

- support substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0214—Manufacture or treatment of multiple TFTs using temporary substrates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P50/00—Etching of wafers, substrates or parts of devices

- H10P50/69—Etching of wafers, substrates or parts of devices using masks for semiconductor materials

- H10P50/691—Etching of wafers, substrates or parts of devices using masks for semiconductor materials for Group V materials or Group III-V materials

- H10P50/692—Etching of wafers, substrates or parts of devices using masks for semiconductor materials for Group V materials or Group III-V materials characterised by their composition, e.g. multilayer masks or materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/19—Preparing inhomogeneous wafers

- H10P90/1904—Preparing vertically inhomogeneous wafers

- H10P90/1906—Preparing SOI wafers

- H10P90/1914—Preparing SOI wafers using bonding

- H10P90/1916—Preparing SOI wafers using bonding with separation or delamination along an ion implanted layer, e.g. Smart-cut

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/19—Preparing inhomogeneous wafers

- H10P90/1904—Preparing vertically inhomogeneous wafers

- H10P90/1906—Preparing SOI wafers

- H10P90/1924—Preparing SOI wafers with separation/delamination along a porous layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W10/00—Isolation regions in semiconductor bodies between components of integrated devices

- H10W10/10—Isolation regions comprising dielectric materials

- H10W10/181—Semiconductor-on-insulator [SOI] isolation regions, e.g. buried oxide regions of SOI wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

- H10D30/0323—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon comprising monocrystalline silicon

Landscapes

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Recrystallisation Techniques (AREA)

Description

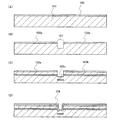

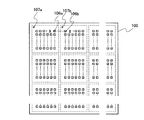

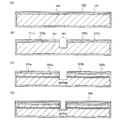

本実施の形態では、支持基板に半導体基板を接合し、熱処理して、半導体基板の一部を剥離(分離)する際において、支持基板の収縮を考慮して、歩留まり高く半導体装置を作製する方法について、図1乃至図7を参照して説明する。図1乃至図4は図5乃至図7のA−Bの断面図を示す。また、図5は半導体基板の上面図を示し、図6及び図7は支持基板の上面図を示す。

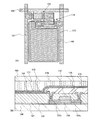

上記形態とは異なる半導体装置の作製方法について、図8乃至10を用いて説明する。ここでは、歩留まり高く半導体基板を支持基板に接合することが可能な半導体装置の作製について示す。

上記形態とは異なる半導体装置の作製方法について、図21を用いて説明する。ここでは、歩留まり高く半導体基板を支持基板に接合することが可能な半導体装置の作製について示す。

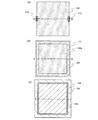

本実施の形態では、可撓性を有する半導体装置の作製方法について、図11乃至図14を用いて説明する。

本実施の形態では、実施の形態4とは異なる半導体装置の作製方法について、図22を用いて説明する。本実施の形態では、可撓性を有する半導体装置の作製方法について示す。

本実施の形態は、半導体装置の一形態を図15を用いて示す。図15は半導体装置の一例として、SOI基板により得られるマイクロプロセッサ200の構成を示す。マイクロプロセッサ200は、上記したように本発明に係る半導体基板により製造されるものである。このマイクロプロセッサ200は、演算回路201(Arithmetic logic unit;ALUともいう。)、演算回路制御部202(ALU Controller)、命令解析部203(Instruction Decoder)、割り込み制御部204(Interrupt Controller)、タイミング制御部205(Timing Controller)、レジスタ206(Register)、レジスタ制御部207(Register Controller)、バスインターフェース208(Bus I/F)、読み出し専用メモリ209(ROM)、及びメモリインターフェース210(ROM I/F)を有している。

本実施の形態は、非接触でデータの送受信を行うことのできる演算機能を備えた半導体装置の一形態を図16を用いて示す。ここでは、SOI基板により得られるRFCPUの構成について図16を参照して説明する。図16は無線通信により外部装置と信号の送受信を行って動作するコンピュータ(以下、「RFCPU」という)の一例を示す。RFCPU211は、アナログ回路部212とデジタル回路部213を有している。アナログ回路部212として、共振容量を有する共振回路214、整流回路215、定電圧回路216、リセット回路217、発振回路218、復調回路219、変調回路220、電源管理回路230を有している。デジタル回路部213は、RFインターフェース221、制御レジスタ222、クロックコントローラ223、インターフェース224(CPUインターフェース)、中央処理ユニット225(CPU)、ランダムアクセスメモリ226(RAM)、読み出し専用メモリ227(ROM)を有している。

上記実施の形態に示すようなSOI層は表示パネルを製造するマザーガラスと呼ばれる大型のガラス基板に接合することもできる。図17は支持基板100としてマザーガラスにSOI層105を接合する場合を示す。マザーガラスからは複数の表示パネルを切り出すが、SOI層105は、表示パネル162の形成領域に合わせて接合することが好ましい。半導体基板に比べて、マザーガラス基板は面積が大きいので、図17で示すように、表示パネル162の形成領域の内側にSOI層105を複数個配置することが好ましい。これによって、SOI層105を支持基板100上に複数個並べて配置する場合にも、隣接間隔に余裕を持たせることができる。表示パネル162には、走査線駆動回路領域163、信号線駆動回路領域164、画素形成領域165があり、これらの領域が含まれるようにSOI層105を支持基板100に接合する。

本発明によれば様々な電気器具を構成することができる。電気器具としては、ビデオカメラ、デジタルカメラ、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDVD(digital versatile disc)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが含まれる。

以下において、本発明の特徴の一であるイオンの照射方法について考察する。

上記のような水素プラズマ中には、H+、H2 +、H3 +といった水素イオン種が存在する。ここで、各水素イオン種の反応過程(生成過程、消滅過程)について、以下に反応式を列挙する。

e+H→e+H++e ・・・・・ (1)

e+H2→e+H2 ++e ・・・・・ (2)

e+H2→e+(H2)*→e+H+H ・・・・・ (3)

e+H2 +→e+(H2 +)*→e+H++H ・・・・・ (4)

H2 ++H2→H3 ++H ・・・・・ (5)

H2 ++H2→H++H+H2 ・・・・・ (6)

e+H3 +→e+H++H+H ・・・・・ (7)

e+H3 +→H2+H ・・・・・ (8)

e+H3 +→H+H+H ・・・・・ (9)

上記のように、H3 +は、主として反応式(5)により表される反応過程により生成される。一方で、反応式(5)と競合する反応として、反応式(6)により表される反応過程が存在する。H3 +が増加するためには、少なくとも、反応式(5)の反応が、反応式(6)の反応より多く起こる必要がある(なお、H3 +が減少する反応としては他にも(7)、(8)、(9)が存在するため、(5)の反応が(6)の反応より多いからといって、必ずしもH3 +が増加するとは限らない。)。反対に、反応式(5)の反応が、反応式(6)の反応より少ない場合には、プラズマ中におけるH3 +の割合は減少する。

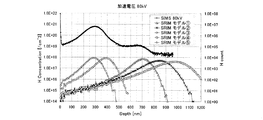

ここで、イオン種の割合(特にH3 +の割合)が異なる例を示す。図24は、100%水素ガス(イオン源の圧力:4.7×10−2Pa)から生成されるイオンの質量分析結果を示すグラフである。なお、上記質量分析は、イオン源から引き出されたイオンを測定することにより行った。横軸はイオンの質量である。スペクトル中、質量1、2、3のピークは、それぞれ、H+、H2 +、H3 +に対応する。縦軸は、スペクトルの強度であり、イオンの数に対応する。図24では、質量が異なるイオンの数量を、質量3のイオンを100とした場合の相対比で表している。図24から、上記イオン源により生成されるイオンの割合は、H+:H2 +:H3 +=1:1:8程度となることが分かる。なお、このような割合のイオンは、プラズマを生成するプラズマソース部(イオン源)と、当該プラズマからイオンビームを引き出すための引出電極などから構成されるイオンドーピング装置によっても得ることが出来る。

図24のような複数のイオン種を含むプラズマを生成し、生成されたイオン種を質量分離しないで単結晶半導体基板に照射する場合、単結晶半導体基板の表面には、H+、H2 +、H3 +の各イオンが照射される。イオンの照射からイオン導入領域形成にかけてのメカニズムを再現するために、以下の5種類のモデルを考える。

1.照射されるイオン種がH+で、照射後もH+(H)である場合

2.照射されるイオン種がH2 +で、照射後もH2 +(H2)のままである場合

3.照射されるイオン種がH2 +で、照射後に2個のH(H+)に分裂する場合

4.照射されるイオン種がH3 +で、照射後もH3 +(H3)のままである場合

5.照射されるイオン種がH3 +で、照射後に3個のH(H+)に分裂する場合

上記のモデルを基にして、水素イオン種をSi基板に照射する場合のシミュレーションを行った。シミュレーション用のソフトウェアとしては、SRIM(the Stopping and Range of Ions in Matter:モンテカルロ法によるイオン導入過程のシミュレーションソフトウェア、TRIM(the Transport of Ions in Matter)の改良版)を用いている。なお、計算の関係上、モデル2ではH2 +を質量2倍のH+に置き換えて計算した。また、モデル4ではH3 +を質量3倍のH+に置き換えて計算した。さらに、モデル3ではH2 +を運動エネルギー1/2のH+に置き換え、モデル5ではH3 +を運動エネルギー1/3のH+に置き換えて計算を行った。

[フィッティング関数]

=X/V×[モデル1のデータ]+Y/V×[モデル5のデータ]

・モデル3に示される照射過程により導入される水素は、モデル5の照射過程と比較して僅かであるため、除外して考えても大きな影響はない(SIMSデータにおいても、ピークが現れていない)。

・モデル5とピーク位置の近いモデル3は、モデル5において生じるチャネリング(結晶の格子構造に起因する元素の移動)により隠れてしまう可能性が高い。すなわち、モデル3のフィッティングパラメータを見積もるのは困難である。これは、本シミュレーションが非晶質Siを前提としており、結晶性に起因する影響を考慮していないことによるものである。

図24に示すようなH3 +の割合を高めた水素イオン種を基板に照射することで、H3 +に起因する複数のメリットを享受することができる。例えば、H3 +はH+やHなどに分離して基板内に導入されるため、主にH+やH2 +を照射する場合と比較して、イオンの導入効率を向上させることができる。これにより、半導体基板の生産性向上を図ることができる。また、同様に、H3 +が分離した後のH+やHの運動エネルギーは小さくなる傾向にあるから、薄い半導体層の製造に向いている。

Claims (8)

- ハロゲンを含む酸化雰囲気中で熱処理を行い半導体基板の表面に第1の酸化層を形成し、

前記第1の酸化層の一部及び前記半導体基板の一部をエッチングして、凸部及び溝を有する半導体基板と前記凸部の表面上の第2の酸化層とを形成し、

前記凸部側から前記凸部及び溝を有する半導体基板に一又は複数の原子からなる質量の異なるイオンを照射して、前記凸部表面から一定の深さを有する第1の領域及び前記溝底面から一定の深さを有する第2の領域に、脆弱領域を形成し、

支持基板と前記凸部及び溝を有する半導体基板とを前記第2の酸化層を挟んで重ね合わせて接合し、

熱処理により、前記第1の領域の前記脆弱領域において前記凸部及び溝を有する半導体基板を分離することで、前記支持基板上に半導体層を残し、

前記半導体層を用いて半導体素子を形成することを特徴とする半導体装置の作製方法。 - ハロゲンを含む酸化雰囲気中で熱処理を行い半導体基板の表面に第1の酸化層を形成し、

前記第1の酸化層の一部及び前記半導体基板の一部をエッチングして、凸部を及び溝を有する半導体基板と前記凸部の表面上の第2の酸化層とを形成し、

前記凸部側から前記凸部及び溝を有する半導体基板に一又は複数の原子からなる質量の異なるイオンを照射して、前記凸部表面から一定の深さを有する第1の領域及び前記溝底面から一定の深さを有する第2の領域に、脆弱領域を形成し、

接合層を有する支持基板を用意し、

前記支持基板と前記凸部及び溝を有する半導体基板とを前記第2の酸化層及び前記接合層を挟んで重ね合わせて接合し、

熱処理により、前記第1の領域の前記脆弱領域において前記凸部及び溝を有する半導体基板を分離することで、前記支持基板上に半導体層を残し、

前記半導体層を用いて半導体素子を形成することを特徴とする半導体装置の作製方法。 - ハロゲンを含む酸化雰囲気中で熱処理を行い半導体基板の表面に第1の酸化層を形成し、

前記第1の酸化層の一部及び前記半導体基板の一部をエッチングして、凸部を有する半導体基板と前記凸部の表面上の第2の酸化層とを形成し、

前記凸部側から前記凸部を有する半導体基板に一又は複数の原子からなる質量の異なるイオンを照射して、前記凸部を有する半導体基板の表面から一定の深さを有する領域に、脆弱領域を形成し、

剥離層を有する支持基板を用意し、

前記支持基板と前記凸部を有する半導体基板とを前記第2の酸化層及び前記剥離層を挟んで重ね合わせて接合し、

熱処理により、前記脆弱領域において前記凸部を有する半導体基板を分離することで、前記支持基板上に半導体層を残し、

前記半導体層を用いて形成した半導体素子を有する素子層を形成し、

前記素子層上に可撓性基板を設け、

前記可撓性基板及び前記素子層から、前記支持基板を前記剥離層で剥離することを特徴とする半導体装置の作製方法。 - ハロゲンを含む酸化雰囲気中で熱処理を行い半導体基板の表面に第1の酸化層を形成し、

前記第1の酸化層の一部及び前記半導体基板の一部をエッチングして、凸部を有する半導体基板と前記凸部の表面上の第2の酸化層とを形成し、

前記凸部側から前記凸部を有する半導体基板に一又は複数の原子からなる質量の異なるイオンを照射して、前記凸部を有する半導体基板の表面から一定の深さを有する領域に、脆弱領域を形成し、

剥離層及び前記剥離層上の接合層を有する、支持基板を用意し、

前記支持基板と前記凸部を有する半導体基板とを、前記第2の酸化層、前記剥離層及び前記接合層を挟んで重ね合わせて接合し、

熱処理により、前記脆弱領域において前記凸部を有する半導体基板を分離することで、前記支持基板上に半導体層を残し、

前記半導体層を用いて形成した半導体素子を有する素子層を形成し、

前記素子層上に可撓性基板を設け、

前記可撓性基板及び前記素子層から、前記支持基板を前記剥離層で剥離することを特徴とする半導体装置の作製方法。 - 請求項1において、前記支持基板上にブロッキング層が設けられた状態で、前記支持基板と前記凸部及び溝を有する半導体基板とを、前記ブロッキング層を挟んで重ね合わせて接合することを特徴とする半導体装置の作製方法。

- 請求項2において、前記支持基板と前記接合層との間にブロッキング層が設けられた状態で、前記支持基板と前記凸部及び溝を有する半導体基板とを、前記ブロッキング層を挟んで重ね合わせて接合することを特徴とする半導体装置の作製方法。

- 請求項3において、前記剥離層上にブロッキング層が設けられた状態で、前記支持基板と前記凸部を有する半導体基板とを、前記ブロッキング層を挟んで重ね合わせて接合することを特徴とする半導体装置の作製方法。

- 請求項4において、前記剥離層と前記接合層との間にブロッキング層が設けられた状態で、前記支持基板と前記凸部を有する半導体基板とを、前記ブロッキング層を挟んで重ね合わせて接合することを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008123316A JP5348939B2 (ja) | 2007-05-11 | 2008-05-09 | 半導体装置の作製方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007127270 | 2007-05-11 | ||

| JP2007127270 | 2007-05-11 | ||

| JP2008123316A JP5348939B2 (ja) | 2007-05-11 | 2008-05-09 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008311635A JP2008311635A (ja) | 2008-12-25 |

| JP2008311635A5 JP2008311635A5 (ja) | 2011-05-26 |

| JP5348939B2 true JP5348939B2 (ja) | 2013-11-20 |

Family

ID=39969907

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008123316A Expired - Fee Related JP5348939B2 (ja) | 2007-05-11 | 2008-05-09 | 半導体装置の作製方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US7601601B2 (ja) |

| JP (1) | JP5348939B2 (ja) |

| KR (1) | KR101443580B1 (ja) |

| CN (1) | CN101303967B (ja) |

| TW (1) | TWI455245B (ja) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5507063B2 (ja) | 2007-07-09 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8101501B2 (en) * | 2007-10-10 | 2012-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing semiconductor device |

| JP2010114409A (ja) * | 2008-10-10 | 2010-05-20 | Sony Corp | Soi基板とその製造方法、固体撮像装置とその製造方法、および撮像装置 |

| JP5618521B2 (ja) * | 2008-11-28 | 2014-11-05 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI607670B (zh) * | 2009-01-08 | 2017-12-01 | 半導體能源研究所股份有限公司 | 發光裝置及電子裝置 |

| JP2010161671A (ja) * | 2009-01-09 | 2010-07-22 | Murata Mfg Co Ltd | 圧電デバイスの製造方法 |

| JP5607399B2 (ja) * | 2009-03-24 | 2014-10-15 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| US8043938B2 (en) * | 2009-05-14 | 2011-10-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate and SOI substrate |

| GB0914251D0 (en) | 2009-08-14 | 2009-09-30 | Nat Univ Ireland Cork | A hybrid substrate |

| JP5866088B2 (ja) * | 2009-11-24 | 2016-02-17 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| US8476147B2 (en) * | 2010-02-03 | 2013-07-02 | Semiconductor Energy Laboratory Co., Ltd. | SOI substrate and manufacturing method thereof |

| JP5355618B2 (ja) * | 2011-03-10 | 2013-11-27 | 三星ディスプレイ株式會社 | 可撓性表示装置及びこの製造方法 |

| JP6040609B2 (ja) * | 2012-07-20 | 2016-12-07 | 東京エレクトロン株式会社 | 成膜装置及び成膜方法 |

| KR102007834B1 (ko) * | 2013-06-27 | 2019-08-07 | 엘지디스플레이 주식회사 | 가요성 표시장치의 제조방법 |

| JP6887992B2 (ja) * | 2015-09-04 | 2021-06-16 | ナンヤン テクノロジカル ユニヴァーシティー | 基板を被膜する方法 |

| CN108417523B (zh) * | 2018-04-16 | 2020-08-04 | 歌尔股份有限公司 | Led衬底的剥离方法 |

| CN108493106B (zh) * | 2018-05-15 | 2020-10-02 | 浙江蓝晶芯微电子有限公司 | 一种半导体晶圆刻蚀方法 |

| US11050012B2 (en) * | 2019-04-01 | 2021-06-29 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method to protect electrodes from oxidation in a MEMS device |

| US11728199B2 (en) * | 2019-12-23 | 2023-08-15 | Asmpt Nexx, Inc. | Substrate support features and method of application |

| CN111106029B (zh) * | 2019-12-31 | 2023-02-10 | 深圳市锐骏半导体股份有限公司 | 一种晶圆快速热处理机台的监控方法 |

| CN111366618B (zh) * | 2020-04-01 | 2022-07-29 | 上海华虹宏力半导体制造有限公司 | 一种温湿度传感器及其制造方法 |

| JP7674068B2 (ja) * | 2021-03-09 | 2025-05-09 | 東京エレクトロン株式会社 | 半導体チップの製造方法、及び基板処理装置 |

| US20230200040A1 (en) * | 2021-12-16 | 2023-06-22 | Invention And Collaboration Laboratory Pte. Ltd. | Homogeneous/ heterogeneous integration system with high performance computing and high storage volume |

| US20240258118A1 (en) * | 2023-01-27 | 2024-08-01 | Destination 2D Inc. | Large-area wafer-scale cmos-compatible 2d-material intercalation doping tools, processes, and methods, including doping of synthesized graphene |

Family Cites Families (46)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0254532A (ja) * | 1988-08-17 | 1990-02-23 | Sony Corp | Soi基板の製造方法 |

| US5347154A (en) * | 1990-11-15 | 1994-09-13 | Seiko Instruments Inc. | Light valve device using semiconductive composite substrate |

| TW211621B (ja) * | 1991-07-31 | 1993-08-21 | Canon Kk | |

| FR2681472B1 (fr) | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| DE69334324D1 (de) * | 1992-01-30 | 2010-05-06 | Canon Kk | Herstellungsverfahren für Halbleitersubstrat |

| JP3237888B2 (ja) * | 1992-01-31 | 2001-12-10 | キヤノン株式会社 | 半導体基体及びその作製方法 |

| TW330313B (en) * | 1993-12-28 | 1998-04-21 | Canon Kk | A semiconductor substrate and process for producing same |

| US6107213A (en) * | 1996-02-01 | 2000-08-22 | Sony Corporation | Method for making thin film semiconductor |

| US5831276A (en) * | 1995-06-07 | 1998-11-03 | Micron Technology, Inc. | Three-dimensional container diode for use with multi-state material in a non-volatile memory cell |

| ATE275761T1 (de) | 1997-03-26 | 2004-09-15 | Canon Kk | Halbleitersubstrat und verfahren zu dessen herstellung |

| JPH10284431A (ja) | 1997-04-11 | 1998-10-23 | Sharp Corp | Soi基板の製造方法 |

| US6191007B1 (en) * | 1997-04-28 | 2001-02-20 | Denso Corporation | Method for manufacturing a semiconductor substrate |

| US6534380B1 (en) * | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JPH1145862A (ja) * | 1997-07-24 | 1999-02-16 | Denso Corp | 半導体基板の製造方法 |

| JPH1174208A (ja) * | 1997-08-27 | 1999-03-16 | Denso Corp | 半導体基板の製造方法 |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000012864A (ja) | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US6093623A (en) * | 1998-08-04 | 2000-07-25 | Micron Technology, Inc. | Methods for making silicon-on-insulator structures |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| JP4476390B2 (ja) * | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000124092A (ja) | 1998-10-16 | 2000-04-28 | Shin Etsu Handotai Co Ltd | 水素イオン注入剥離法によってsoiウエーハを製造する方法およびこの方法で製造されたsoiウエーハ |

| US6380019B1 (en) | 1998-11-06 | 2002-04-30 | Advanced Micro Devices, Inc. | Method of manufacturing a transistor with local insulator structure |

| JP4313874B2 (ja) * | 1999-02-02 | 2009-08-12 | キヤノン株式会社 | 基板の製造方法 |

| US6375738B1 (en) * | 1999-03-26 | 2002-04-23 | Canon Kabushiki Kaisha | Process of producing semiconductor article |

| JP2001015721A (ja) * | 1999-04-30 | 2001-01-19 | Canon Inc | 複合部材の分離方法及び薄膜の製造方法 |

| US20010053559A1 (en) * | 2000-01-25 | 2001-12-20 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating display device |

| JP4507395B2 (ja) * | 2000-11-30 | 2010-07-21 | セイコーエプソン株式会社 | 電気光学装置用素子基板の製造方法 |

| US6583440B2 (en) | 2000-11-30 | 2003-06-24 | Seiko Epson Corporation | Soi substrate, element substrate, semiconductor device, electro-optical apparatus, electronic equipment, method of manufacturing the soi substrate, method of manufacturing the element substrate, and method of manufacturing the electro-optical apparatus |

| US6601783B2 (en) * | 2001-04-25 | 2003-08-05 | Dennis Chisum | Abrasivejet nozzle and insert therefor |

| US6566158B2 (en) * | 2001-08-17 | 2003-05-20 | Rosemount Aerospace Inc. | Method of preparing a semiconductor using ion implantation in a SiC layer |

| US6818529B2 (en) * | 2002-09-12 | 2004-11-16 | Applied Materials, Inc. | Apparatus and method for forming a silicon film across the surface of a glass substrate |

| US6750117B1 (en) * | 2002-12-23 | 2004-06-15 | Macronix International Co., Ltd. | Shallow trench isolation process |

| JP4581348B2 (ja) * | 2003-08-26 | 2010-11-17 | 信越半導体株式会社 | 貼り合わせウエーハの製造方法およびsoiウエーハ |

| US20050048736A1 (en) * | 2003-09-02 | 2005-03-03 | Sebastien Kerdiles | Methods for adhesive transfer of a layer |

| JP5110772B2 (ja) | 2004-02-03 | 2012-12-26 | 株式会社半導体エネルギー研究所 | 半導体薄膜層を有する基板の製造方法 |

| US7410882B2 (en) * | 2004-09-28 | 2008-08-12 | Palo Alto Research Center Incorporated | Method of manufacturing and structure of polycrystalline semiconductor thin-film heterostructures on dissimilar substrates |

| US7148124B1 (en) * | 2004-11-18 | 2006-12-12 | Alexander Yuri Usenko | Method for forming a fragile layer inside of a single crystalline substrate preferably for making silicon-on-insulator wafers |

| US8153511B2 (en) * | 2005-05-30 | 2012-04-10 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing semiconductor device |

| US7638381B2 (en) * | 2005-10-07 | 2009-12-29 | International Business Machines Corporation | Methods for fabricating a semiconductor structure using a mandrel and semiconductor structures formed thereby |

| US7288458B2 (en) | 2005-12-14 | 2007-10-30 | Freescale Semiconductor, Inc. | SOI active layer with different surface orientation |

| JP4610515B2 (ja) * | 2006-04-21 | 2011-01-12 | 株式会社半導体エネルギー研究所 | 剥離方法 |

| US20070281440A1 (en) * | 2006-05-31 | 2007-12-06 | Jeffrey Scott Cites | Producing SOI structure using ion shower |

| EP1975998A3 (en) | 2007-03-26 | 2013-12-04 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a plurality of island-shaped SOI structures |

| CN101281912B (zh) * | 2007-04-03 | 2013-01-23 | 株式会社半导体能源研究所 | Soi衬底及其制造方法以及半导体装置 |

| KR101400699B1 (ko) * | 2007-05-18 | 2014-05-29 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기판 및 반도체 장치 및 그 제조 방법 |

| SG160295A1 (en) * | 2008-09-29 | 2010-04-29 | Semiconductor Energy Lab | Method for manufacturing semiconductor device |

-

2008

- 2008-03-21 KR KR1020080026203A patent/KR101443580B1/ko not_active Expired - Fee Related

- 2008-03-27 TW TW097111074A patent/TWI455245B/zh not_active IP Right Cessation

- 2008-03-28 US US12/078,214 patent/US7601601B2/en not_active Expired - Fee Related

- 2008-03-31 CN CN2008100907193A patent/CN101303967B/zh not_active Expired - Fee Related

- 2008-05-09 JP JP2008123316A patent/JP5348939B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-25 US US12/546,719 patent/US7902041B2/en not_active Expired - Fee Related

-

2011

- 2011-01-25 US US13/012,844 patent/US8629433B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TWI455245B (zh) | 2014-10-01 |

| KR101443580B1 (ko) | 2014-10-30 |

| JP2008311635A (ja) | 2008-12-25 |

| US7902041B2 (en) | 2011-03-08 |

| US20080280417A1 (en) | 2008-11-13 |

| US20110114948A1 (en) | 2011-05-19 |

| US8629433B2 (en) | 2014-01-14 |

| KR20080100120A (ko) | 2008-11-14 |

| TW200908209A (en) | 2009-02-16 |

| US7601601B2 (en) | 2009-10-13 |

| CN101303967A (zh) | 2008-11-12 |

| CN101303967B (zh) | 2012-05-30 |

| US20090309183A1 (en) | 2009-12-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5348939B2 (ja) | 半導体装置の作製方法 | |

| JP5394653B2 (ja) | Soi基板の製造方法 | |

| US8552499B2 (en) | Semiconductor substrate, semiconductor device and manufacturing method thereof | |

| JP5500781B2 (ja) | Soi基板の製造方法 | |

| JP5542256B2 (ja) | Soi基板の作製方法 | |

| JP5459899B2 (ja) | 半導体装置の作製方法 | |

| JP5490371B2 (ja) | 半導体装置の作製方法 | |

| KR101561855B1 (ko) | Soi기판의 제작방법 | |

| JP5661990B2 (ja) | Soi基板の製造方法 | |

| JP5460972B2 (ja) | Soi基板の作製方法、及び半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110413 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110413 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130409 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130411 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130520 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130806 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130820 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |