CN101303967B - 半导体装置的制造方法 - Google Patents

半导体装置的制造方法 Download PDFInfo

- Publication number

- CN101303967B CN101303967B CN2008100907193A CN200810090719A CN101303967B CN 101303967 B CN101303967 B CN 101303967B CN 2008100907193 A CN2008100907193 A CN 2008100907193A CN 200810090719 A CN200810090719 A CN 200810090719A CN 101303967 B CN101303967 B CN 101303967B

- Authority

- CN

- China

- Prior art keywords

- layer

- semiconductor substrate

- single crystal

- crystal semiconductor

- support substrates

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 382

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 39

- 239000000758 substrate Substances 0.000 claims abstract description 505

- 238000000034 method Methods 0.000 claims abstract description 56

- 230000004888 barrier function Effects 0.000 claims description 94

- 238000009940 knitting Methods 0.000 claims description 91

- 239000013078 crystal Substances 0.000 claims description 66

- 229910052710 silicon Inorganic materials 0.000 claims description 32

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 31

- 239000010703 silicon Substances 0.000 claims description 31

- 230000015572 biosynthetic process Effects 0.000 claims description 24

- 229910052782 aluminium Inorganic materials 0.000 claims description 13

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 13

- 239000000463 material Substances 0.000 claims description 12

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical group N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 9

- 229910017083 AlN Inorganic materials 0.000 claims 2

- PIGFYZPCRLYGLF-UHFFFAOYSA-N Aluminum nitride Chemical compound [Al]#N PIGFYZPCRLYGLF-UHFFFAOYSA-N 0.000 claims 2

- 239000011230 binding agent Substances 0.000 claims 1

- 150000002500 ions Chemical class 0.000 abstract description 88

- 238000010438 heat treatment Methods 0.000 abstract description 28

- 238000000926 separation method Methods 0.000 abstract description 17

- 239000010410 layer Substances 0.000 description 478

- 238000006243 chemical reaction Methods 0.000 description 56

- 229910052739 hydrogen Inorganic materials 0.000 description 50

- 239000001257 hydrogen Substances 0.000 description 48

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 34

- 239000011521 glass Substances 0.000 description 25

- 229910052721 tungsten Inorganic materials 0.000 description 23

- 239000010937 tungsten Substances 0.000 description 23

- GPRLSGONYQIRFK-UHFFFAOYSA-N hydron Chemical compound [H+] GPRLSGONYQIRFK-UHFFFAOYSA-N 0.000 description 22

- 239000012535 impurity Substances 0.000 description 22

- 229910052751 metal Inorganic materials 0.000 description 22

- 239000002184 metal Substances 0.000 description 22

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 22

- 239000007789 gas Substances 0.000 description 21

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 20

- 238000005755 formation reaction Methods 0.000 description 20

- 230000005669 field effect Effects 0.000 description 19

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 18

- 229910052736 halogen Inorganic materials 0.000 description 18

- 150000002367 halogens Chemical class 0.000 description 18

- 239000000203 mixture Substances 0.000 description 18

- 239000011733 molybdenum Substances 0.000 description 18

- 238000005530 etching Methods 0.000 description 17

- 229910052750 molybdenum Inorganic materials 0.000 description 17

- 230000000694 effects Effects 0.000 description 16

- 230000008569 process Effects 0.000 description 16

- 230000006870 function Effects 0.000 description 15

- -1 halide ion Chemical class 0.000 description 13

- 241000894007 species Species 0.000 description 13

- 206010040844 Skin exfoliation Diseases 0.000 description 12

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 12

- 230000003647 oxidation Effects 0.000 description 12

- 238000007254 oxidation reaction Methods 0.000 description 12

- 229910052760 oxygen Inorganic materials 0.000 description 12

- 238000012545 processing Methods 0.000 description 12

- 239000000047 product Substances 0.000 description 12

- 125000004429 atom Chemical group 0.000 description 11

- 230000005684 electric field Effects 0.000 description 11

- 230000015654 memory Effects 0.000 description 11

- 239000001301 oxygen Substances 0.000 description 11

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 11

- 229910052757 nitrogen Inorganic materials 0.000 description 10

- 239000002245 particle Substances 0.000 description 10

- 238000004458 analytical method Methods 0.000 description 9

- 230000008859 change Effects 0.000 description 9

- 239000011229 interlayer Substances 0.000 description 9

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 8

- 238000013459 approach Methods 0.000 description 8

- 238000011282 treatment Methods 0.000 description 8

- 208000034699 Vitreous floaters Diseases 0.000 description 7

- 239000004973 liquid crystal related substance Substances 0.000 description 7

- 230000001590 oxidative effect Effects 0.000 description 7

- 239000011241 protective layer Substances 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- 230000002950 deficient Effects 0.000 description 6

- 238000009792 diffusion process Methods 0.000 description 6

- 239000012467 final product Substances 0.000 description 6

- 238000010884 ion-beam technique Methods 0.000 description 6

- 238000001459 lithography Methods 0.000 description 6

- 239000004411 aluminium Substances 0.000 description 5

- 238000010276 construction Methods 0.000 description 5

- 230000007547 defect Effects 0.000 description 5

- 238000010586 diagram Methods 0.000 description 5

- 238000005247 gettering Methods 0.000 description 5

- 150000002431 hydrogen Chemical class 0.000 description 5

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- PQLAYKMGZDUDLQ-UHFFFAOYSA-K aluminium bromide Chemical compound Br[Al](Br)Br PQLAYKMGZDUDLQ-UHFFFAOYSA-K 0.000 description 4

- VSCWAEJMTAWNJL-UHFFFAOYSA-K aluminium trichloride Chemical compound Cl[Al](Cl)Cl VSCWAEJMTAWNJL-UHFFFAOYSA-K 0.000 description 4

- 239000005388 borosilicate glass Substances 0.000 description 4

- 239000000835 fiber Substances 0.000 description 4

- FFUAGWLWBBFQJT-UHFFFAOYSA-N hexamethyldisilazane Chemical compound C[Si](C)(C)N[Si](C)(C)C FFUAGWLWBBFQJT-UHFFFAOYSA-N 0.000 description 4

- VEXZGXHMUGYJMC-UHFFFAOYSA-N hydrochloric acid Substances Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 4

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 4

- 239000007788 liquid Substances 0.000 description 4

- 239000011159 matrix material Substances 0.000 description 4

- 229910044991 metal oxide Inorganic materials 0.000 description 4

- 150000004706 metal oxides Chemical class 0.000 description 4

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 4

- HMMGMWAXVFQUOA-UHFFFAOYSA-N octamethylcyclotetrasiloxane Chemical compound C[Si]1(C)O[Si](C)(C)O[Si](C)(C)O[Si](C)(C)O1 HMMGMWAXVFQUOA-UHFFFAOYSA-N 0.000 description 4

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 4

- 229920005989 resin Polymers 0.000 description 4

- 239000011347 resin Substances 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 239000011734 sodium Substances 0.000 description 4

- 229910052708 sodium Inorganic materials 0.000 description 4

- 238000003860 storage Methods 0.000 description 4

- 208000005189 Embolism Diseases 0.000 description 3

- GQPLMRYTRLFLPF-UHFFFAOYSA-N Nitrous Oxide Chemical compound [O-][N+]#N GQPLMRYTRLFLPF-UHFFFAOYSA-N 0.000 description 3

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 238000000137 annealing Methods 0.000 description 3

- 238000004364 calculation method Methods 0.000 description 3

- 239000000460 chlorine Substances 0.000 description 3

- GPTXWRGISTZRIO-UHFFFAOYSA-N chlorquinaldol Chemical compound ClC1=CC(Cl)=C(O)C2=NC(C)=CC=C21 GPTXWRGISTZRIO-UHFFFAOYSA-N 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 230000008602 contraction Effects 0.000 description 3

- 230000006378 damage Effects 0.000 description 3

- 238000001678 elastic recoil detection analysis Methods 0.000 description 3

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- 238000005304 joining Methods 0.000 description 3

- 238000003475 lamination Methods 0.000 description 3

- 150000001282 organosilanes Chemical class 0.000 description 3

- 238000000053 physical method Methods 0.000 description 3

- 238000005381 potential energy Methods 0.000 description 3

- 238000004151 rapid thermal annealing Methods 0.000 description 3

- 239000002994 raw material Substances 0.000 description 3

- 230000008439 repair process Effects 0.000 description 3

- 238000004088 simulation Methods 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- WZJUBBHODHNQPW-UHFFFAOYSA-N 2,4,6,8-tetramethyl-1,3,5,7,2$l^{3},4$l^{3},6$l^{3},8$l^{3}-tetraoxatetrasilocane Chemical compound C[Si]1O[Si](C)O[Si](C)O[Si](C)O1 WZJUBBHODHNQPW-UHFFFAOYSA-N 0.000 description 2

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 239000004695 Polyether sulfone Substances 0.000 description 2

- 239000004743 Polypropylene Substances 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 229910052801 chlorine Inorganic materials 0.000 description 2

- 238000000576 coating method Methods 0.000 description 2

- 238000005238 degreasing Methods 0.000 description 2

- 238000006356 dehydrogenation reaction Methods 0.000 description 2

- AWFPGKLDLMAPMK-UHFFFAOYSA-N dimethylaminosilicon Chemical compound CN(C)[Si] AWFPGKLDLMAPMK-UHFFFAOYSA-N 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 238000009499 grossing Methods 0.000 description 2

- 230000003760 hair shine Effects 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- MWUXSHHQAYIFBG-UHFFFAOYSA-N nitrogen oxide Inorganic materials O=[N] MWUXSHHQAYIFBG-UHFFFAOYSA-N 0.000 description 2

- 239000003960 organic solvent Substances 0.000 description 2

- 238000009832 plasma treatment Methods 0.000 description 2

- 229920006393 polyether sulfone Polymers 0.000 description 2

- 229920005644 polyethylene terephthalate glycol copolymer Polymers 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 229920001155 polypropylene Polymers 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 238000005546 reactive sputtering Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000000630 rising effect Effects 0.000 description 2

- 238000005001 rutherford backscattering spectroscopy Methods 0.000 description 2

- 239000005368 silicate glass Substances 0.000 description 2

- 239000002210 silicon-based material Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 125000006850 spacer group Chemical group 0.000 description 2

- 230000006641 stabilisation Effects 0.000 description 2

- CZDYPVPMEAXLPK-UHFFFAOYSA-N tetramethylsilane Chemical compound C[Si](C)(C)C CZDYPVPMEAXLPK-UHFFFAOYSA-N 0.000 description 2

- RSNQKPMXXVDJFG-UHFFFAOYSA-N tetrasiloxane Chemical compound [SiH3]O[SiH2]O[SiH2]O[SiH3] RSNQKPMXXVDJFG-UHFFFAOYSA-N 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- QQQSFSZALRVCSZ-UHFFFAOYSA-N triethoxysilane Chemical compound CCO[SiH](OCC)OCC QQQSFSZALRVCSZ-UHFFFAOYSA-N 0.000 description 2

- PQDJYEQOELDLCP-UHFFFAOYSA-N trimethylsilane Chemical compound C[SiH](C)C PQDJYEQOELDLCP-UHFFFAOYSA-N 0.000 description 2

- 229940094989 trimethylsilane Drugs 0.000 description 2

- PEPBFCOIJRULGJ-UHFFFAOYSA-N 3h-1,2,3-benzodioxazole Chemical compound C1=CC=C2NOOC2=C1 PEPBFCOIJRULGJ-UHFFFAOYSA-N 0.000 description 1

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 101100113692 Caenorhabditis elegans clk-2 gene Proteins 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- YZCKVEUIGOORGS-OUBTZVSYSA-N Deuterium Chemical compound [2H] YZCKVEUIGOORGS-OUBTZVSYSA-N 0.000 description 1

- 208000033999 Device damage Diseases 0.000 description 1

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 description 1

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 description 1

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 229910001182 Mo alloy Inorganic materials 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229920000265 Polyparaphenylene Polymers 0.000 description 1

- 239000004721 Polyphenylene oxide Substances 0.000 description 1

- 239000004734 Polyphenylene sulfide Substances 0.000 description 1

- 239000004954 Polyphthalamide Substances 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- YZCKVEUIGOORGS-IGMARMGPSA-N Protium Chemical compound [1H] YZCKVEUIGOORGS-IGMARMGPSA-N 0.000 description 1

- 241000720974 Protium Species 0.000 description 1

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- 229910001080 W alloy Inorganic materials 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- MXSJNBRAMXILSE-UHFFFAOYSA-N [Si].[P].[B] Chemical compound [Si].[P].[B] MXSJNBRAMXILSE-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000001133 acceleration Effects 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 239000004760 aramid Substances 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 229920003235 aromatic polyamide Polymers 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000003985 ceramic capacitor Substances 0.000 description 1

- 230000005465 channeling Effects 0.000 description 1

- 230000000739 chaotic effect Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 238000002788 crimping Methods 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 230000035618 desquamation Effects 0.000 description 1

- 229910052805 deuterium Inorganic materials 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000000605 extraction Methods 0.000 description 1

- 239000002657 fibrous material Substances 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 239000003365 glass fiber Substances 0.000 description 1

- 239000002241 glass-ceramic Substances 0.000 description 1

- 238000007731 hot pressing Methods 0.000 description 1

- 230000005660 hydrophilic surface Effects 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- 238000011835 investigation Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 230000006386 memory function Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 239000010955 niobium Substances 0.000 description 1

- GUCVJGMIXFAOAE-UHFFFAOYSA-N niobium atom Chemical compound [Nb] GUCVJGMIXFAOAE-UHFFFAOYSA-N 0.000 description 1

- 239000001272 nitrous oxide Substances 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- SYQBFIAQOQZEGI-UHFFFAOYSA-N osmium atom Chemical compound [Os] SYQBFIAQOQZEGI-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000001936 parietal effect Effects 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 229920003023 plastic Polymers 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 229920002492 poly(sulfone) Polymers 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920006380 polyphenylene oxide Polymers 0.000 description 1

- 229920000069 polyphenylene sulfide Polymers 0.000 description 1

- 229920006375 polyphtalamide Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 238000002360 preparation method Methods 0.000 description 1

- 230000007115 recruitment Effects 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 150000003568 thioethers Chemical class 0.000 description 1

- 238000010023 transfer printing Methods 0.000 description 1

- 230000017105 transposition Effects 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 229920006337 unsaturated polyester resin Polymers 0.000 description 1

- 239000002966 varnish Substances 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

- H01L21/308—Chemical or electrical treatment, e.g. electrolytic etching using masks

- H01L21/3081—Chemical or electrical treatment, e.g. electrolytic etching using masks characterised by their composition, e.g. multilayer masks, materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76259—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along a porous layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1262—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate

- H01L27/1266—Multistep manufacturing methods with a particular formation, treatment or coating of the substrate the substrate on which the devices are formed not being the final device substrate, e.g. using a temporary substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/66772—Monocristalline silicon transistors on insulating substrates, e.g. quartz substrates

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Recrystallisation Techniques (AREA)

Abstract

本发明的目的在于提供一种半导体装置的方法,即使使用耐热温度低的衬底也高成品率地制造具有结晶半导体层的半导体装置。通过在半导体衬底的一部分中形成槽,形成具有凸部的半导体衬底,而且覆盖该凸部地形成接合层。另外,在形成接合层之前,通过对成为凸部的半导体衬底照射加速了的离子,形成脆弱层。将接合层和支撑衬底接合,然后进行分离半导体衬底的热处理,以在支撑衬底上提供半导体层。通过选择性地蚀刻该半导体层,形成半导体元件,以制造半导体装置。

Description

技术领域

本发明涉及使用具有SOI结构的衬底的半导体装置的制造方法。

背景技术

正在开发在绝缘层上设置有薄单晶半导体层的称为绝缘体上硅(Silicon on Insulator)的半导体衬底(SOI衬底),而代替将单晶半导体的锭(ingot)切成薄片而形成的硅片。通过使用SOI衬底设置构成集成电路的晶体管,可以减少晶体管的漏极和衬底之间的寄生电容,从而被认为对提高工作速度及降低耗电量有效。因此,SOI衬底被期待着应用于高性能半导体装置如微处理器等。

作为制造SOI衬底的方法,已知氢离子注入剥离法(例如参照专利文件1)。在氢离子注入剥离法中,通过将氢离子注入到硅片,在离表面有预定深度处形成微小气泡层,将氢离子注入面重叠于另一硅片,进行热处理,并以该微小气泡层为劈开面进行剥离,来将薄硅层(SOI层)接合到另一硅片。除了进行用来剥离SOI层的热处理以外,还需要通过在氧化性气氛下进行热处理而在SOI层上形成氧化层,然后去除该氧化层,并在1000℃至1300℃的还原性气氛下进行热处理,以提高接合面的接合强度并改善SOI层表面的损伤层。

另一方面,公开了在绝缘衬底如高耐热性玻璃等上设置有单晶硅层的半导体装置(参照专利文件2)。在该半导体装置中,使用绝缘性硅层保护应变点为750℃以上的结晶玻璃的整个表面,并将通过氢离子注入剥离法而获得的单晶硅层固定于该绝缘性硅层上。

专利文件1日本专利申请特开2000-124092号公报

专利文件2日本专利申请特开平11-163363号公报

在氢离子注入剥离法中,需要在1000℃以上的高温下进行热处理,以提高SOI层和另一衬底的接合强度并改善SOI层表面的损伤层。因此,在为了降低衬底的成本而将单晶硅层接合到用于液晶面板等的耐热温度为700℃左右的玻璃衬底来形成SOI衬底的情况下,发生玻璃衬底因所述高温下进行热处理而收缩的问题。若玻璃衬底收缩,则单晶硅层和玻璃衬底的接合强度降低,因此成品率降低。

发明内容

鉴于上述问题,本发明的目的在于提供一种高成品率地制造具有结晶半导体层的半导体装置的方法,该结晶半导体层即使使用耐热温度低的衬底如玻璃衬底等也可以实用。

通过在作为半导体层的基体的半导体衬底的一部分中形成槽,形成具有凸部的半导体衬底,而且覆盖该凸部地形成接合层。另外,在形成接合层之前,通过至少对成为凸部的半导体衬底照射加速了的离子,将半导体衬底的一部分多孔化而形成脆弱层。在清洗接合层的表面及支撑衬底的表面之后,将接合层和支撑衬底接合,并进行分离半导体衬底的热处理,以在支撑衬底上提供半导体层。通过选择性地蚀刻该半导体层,制造场效应晶体管、二极管、电容元件、非易失存储元件等的半导体元件,以制造半导体装置。

在进行分离半导体衬底的热处理之前,在半导体衬底的一部分形成槽,来形成分离的凸部。然后,将该凸部接合到支撑衬底,并进行分离半导体衬底的热处理。通过进行分离半导体衬底的热处理,支撑衬底收缩,因而接合到支撑衬底上的SOI层的位置也变化,并且产生畸变应力。但是,由于凸部是被槽分离而不是连续接合到支撑衬底上,所以可以抑制由支撑衬底收缩产生的半导体层的畸变应力,并可以抑制膜剥离或接合面的接合力降低。另外,因为在后续的加热步骤中不容易发生支撑衬底的收缩,所以可以抑制在多个光刻步骤中的光掩模的偏离。

当通过向半导体衬底照射加速了的离子将半导体衬底的一部分多孔化来形成脆弱区域时,存在着如下区域:加速了的离子即使被照射到半导体衬底,在该区域在半导体衬底中也不适当地包含该离子。通过去除半导体衬底中的该区域形成槽,来形成凸部,以在凸部中形成连续的脆弱区域。然后,将所述被分割的半导体衬底接合到支撑衬底,并进行分离半导体衬底的热处理。通过进行分离半导体衬底的热处理,在连续的脆弱区域中半导体衬底的整个凸部被分离,来可以在支撑衬底上设置具有预定厚度的半导体层。

接合层是形成平滑面且具有亲水性表面的层。作为可形成这种表面的层,优选使用通过化学反应形成的绝缘层。例如,优选使用通过热反应或化学反应形成的氧化层。这是因为主要通过化学反应形成的膜能够确保表面平滑性的缘故。作为接合层的代表例子,使用以有机硅烷为原料而形成的氧化硅层。作为有机硅烷气体,可以使用硅酸乙酯(四乙氧基硅烷,TEOS;Si(OC2H5)4)、四甲基硅烷(Si(CH3)4)、三甲基硅烷((CH3)3SiH)、四甲基环四硅氧烷(TMCTS)、八甲基环四硅氧烷(OMCTS)、六甲基二硅氮烷(HMDS)、三乙氧基硅烷(SiH(OC2H5)3)、三二甲氨基硅烷(SiH(N(CH3)2)3)等的含硅化合物。

另外,可以先在支撑衬底上以支撑衬底的应变点以下的温度形成防止杂质扩散的阻挡层,然后接合支撑衬底的阻挡层和半导体衬底的接合层,并进行分离半导体衬底的热处理,以在支撑衬底上设置半导体层。

另外,可以在将槽形成于半导体衬底的一部分之前或之后,在半导体衬底的表面上形成阻挡层,并在该阻挡层上形成接合层,然后接合支撑衬底和半导体衬底的接合层,并进行分离半导体衬底的热处理,以在支撑衬底上设置半导体层。

作为形成在支撑衬底或半导体衬底上的防止杂质元素扩散的阻挡层,可以设置氮化硅层、氮氧化硅层、氮化铝层、或氮氧化铝层。再者,可以组合氧氮化硅层作为具有应力缓和效果的绝缘层。这里,氧氮化硅层指的是在其组成上氧含量多于氮含量的物质,在通过卢瑟福背散射分析(RBS;Rutherford Backscattering Spectrometry)及氢正散射分析(HFS;Hydrogen Forward Scattering)测量的情况下包含氧、氮、Si及氢,其浓度如下:50至70原子%的氧;0.5至15原子%的氮;25至35原子%的Si;以及0.1至10原子%的氢。另一方面,氮氧化硅层指的是在其组成上氮含量多于氧含量的物质,在通过RBS及HFS测量的情况下包含氧、氮、Si及氢,其浓度如下:5至30原子%的氧;20至50原子%的氮;25至35原子%的Si;以及10至30原子%的氢。注意,当将构成氧氮化硅或氮氧化硅的原子总量设定为100原子%时,氮、氧、Si及氢的含量比率在上述范围内。

再者,在将槽形成于半导体衬底的一部分之前或之后,优选在氧化性气氛下对半导体衬底进行加热处理。尤其是,优选在包含卤素的氧化性气氛下进行热处理。例如,将微量盐酸添加到氧来进行热处理,以在半导体衬底上形成氧化层。由此,半导体衬底和氧化层的界面的悬空键以氢为终端,从而可以使界面不激活并实现电特性的稳定化。另外,氯有与包含在半导体衬底中的金属反应来去除它(吸杂)的作用。

在通过将槽形成于半导体衬底的一部分而形成具有凸部的半导体衬底之后,将该凸部接合到支撑衬底,而且通过进行热处理,可以在脆弱区域中分离半导体衬底,并在支撑衬底上提供SOI层。由于半导体衬底中的凸部被分离,所以可以防止SOI层的剥离,该剥离是伴随由加热导致的所述支撑衬底的收缩而发生的。

另外,由于在半导体衬底的凸部中形成有连续的脆弱层,所以可以在支撑衬底上设置具有预定厚度的SOI层。

因此,可以通过使用上述SOI层高成品率地制造半导体装置。

附图说明

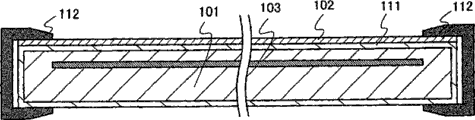

图1A至1D是表示本发明的半导体装置的制造步骤的截面图;

图2A和2B是表示本发明的半导体装置的制造步骤的截面图;

图3A至3C是表示本发明的半导体装置的制造步骤的截面图;

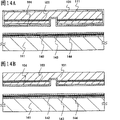

图4A和4B是表示本发明的半导体装置的制造步骤的截面图;

图5是表示本发明的半导体装置的制造步骤的俯视图;

图6是表示本发明的半导体装置的制造步骤的俯视图;

图7是表示本发明的半导体装置的制造步骤的俯视图;

图8A至8D是表示本发明的半导体装置的制造步骤的截面图;

图9A至9C是表示本发明的半导体装置的制造步骤的截面图;

图10A至10C是表示本发明的半导体装置的制造步骤的俯视图;

图11A至11D是表示本发明的半导体装置的制造步骤的截面图;

图12A至12C是表示本发明的半导体装置的制造步骤的截面图;

图13A和13B是表示本发明的半导体装置的制造步骤的截面图;

图14A和14B是表示本发明的半导体装置的制造步骤的截面图;

图15是表示作为半导体装置的一个方式的微处理器的结构的框图;

图16是表示作为半导体装置的一个方式的RFCPU的结构的框图;

图17是表示将半导体层接合到显示面板制造用母玻璃的情况的平面图;

图18A和18B是表示像素晶体管由半导体层构成的液晶显示装置的一个例子的图;

图19A和19B是表示像素晶体管由半导体层构成的电致发光显示装置的一个例子的图;

图20A至20C是说明根据本发明的电器的一个例子的图;

图21A至21C是表示本发明的半导体装置的制造步骤的截面图;

图22A至22D是表示本发明的半导体装置的制造步骤的截面图;

图23是示出氢离子种类的能量图的图;

图24是示出离子的质量分析结果的图;

图25是示出离子的质量分析结果的图;

图26是示出当将加速电压设定为80kV时的氢的深度方向的廓线(实测值及计算值)的图;

图27是示出当将加速电压设定为80kV时的氢的深度方向的廓线(实测值、计算值、以及拟合函数)的图;

图28是示出当将加速电压设定为60kV时的氢的深度方向的廓线(实测值、计算值、以及拟合函数)的图;

图29是示出当将加速电压设定为40kV时的氢的深度方向的廓线(实测值、计算值、以及拟合函数)的图;

图30是总结拟合参数的比率(氢元素比及氢离子种类比)的图。

具体实施方式

下面,参照附图说明本发明的实施方式。注意,本发明不局限于下述说明,所属技术领域的普通技术人员可以很容易地理解一个事实就是,其方式和详细内容可以在不脱离本发明的宗旨及其范围的情况下被变换为各种各样的形式。因此,本发明不应该被解释为仅限定在下述实施方式所记载的内容中。在以下所说明的本发明的结构中,在不同附图之间共同使用同一附图标记表示同一部分。

注意,在以下说明中,虽然说明将单晶半导体层设置在具有绝缘表面的衬底上或绝缘衬底上的情况,但是也可以通过改变作为单晶半导体层的基体的半导体衬底的种类将多晶半导体层固定于具有绝缘表面的衬底上或绝缘衬底上。

实施方式1

在本实施方式中,参照图1A至图7说明高成品率地制造半导体装置的方法,其中考虑到当将半导体衬底接合到支撑衬底并进行热处理以剥离(分离)半导体衬底的一部分时发生的支撑衬底的收缩。图1A至图4B是沿图5至图7的A-B线的截面图。图5是半导体衬底的俯视图,而图6及图7是支撑衬底的俯视图。

在图1A中,可以使用结晶半导体衬底或单晶半导体衬底作为半导体衬底101。作为结晶半导体衬底或单晶半导体衬底,可以举出硅衬底、锗衬底,除此以外还可使用硅锗、镓砷或铟磷等化合物半导体的衬底。作为在市场上销售的硅衬底,典型地说,可以举出直径为5英寸(125mm)、6英寸(150mm)、8英寸(200mm)、12英寸(300mm)的衬底,其形状大多是圆形。另外,可以在约1.5mm以下的范围内适当地选择其厚度。这里,使用p型或n型单晶硅衬底(硅片)作为半导体衬底101。

另外,在半导体衬底101的一表面上形成阻挡层102。作为阻挡层102,可以使用选自氮化硅层、氮氧化硅层、氮化铝层或氮氧化铝层的一层或多个膜所构成的叠层结构。通过气相沉积法形成50nm至200nm厚的氮化硅层、氮氧化硅层、氮化铝层或氮氧化铝层。例如,氮化硅层以SiH4及NH3为源气体通过等离子体CVD法而形成,氮氧化硅层使用SiH4、N2O及NH3通过等离子体CVD法而形成,氮化铝层通过使用铝靶并使用氮作为反应气体的反应性溅射法而形成,或者,氮化铝层以氯化铝或溴化铝及氨为源气体通过热CVD法而形成,氮氧化铝层通过使用铝靶并使用氮及氧作为反应气体的反应性溅射法而形成,或者,氮氧化铝层以氯化铝或溴化铝、氨及一氧化二氮为源气体通过热CVD法而形成。

阻挡层102起到防止杂质扩散到由半导体衬底101构成的SOI层的作用。另外,阻挡层102还起到当形成脆弱层(具体地说,指的是被照射加速了的离子的脆弱层,下面称为脆弱区域)时防止被照射离子的半导体衬底101的面因离子照射而损伤使得平整度降低的作用。

在图1B中,去除半导体衬底101的一部分来形成槽107。其结果,被分离的凸部形成在半导体衬底101上。另外,阻挡层102被分开。

图5是形成有槽的半导体衬底101的上表面的示意图。沿图5的A-B线的截面图相当于图1B。

半导体衬底101被选择性地蚀刻,阻挡层102a及102b残留在相当于图1B的凸部的部分中。当从上表面看时,形成于半导体衬底101的凸部大致对应于曝光装置曝光一次的区域。

在制造半导体装置等的技术中,当形成微细图案等时,大多采用光刻步骤。在光刻步骤中,通过使用以步进机为代表的曝光装置,向涂敷在衬底上的抗蚀剂层以所希望的图案曝光并显影,然后通过利用该图案在衬底上形成所希望的图案。曝光装置曝光一次的区域的面积根据各装置而不同,但在利用现有步进机的情况下,曝光一次的区域的面积大约为25mm方形、100mm方形、113mm方形、132mm方形或144mm方形,难以通过一次曝光对一边长超过1米的大面积衬底整体进行曝光。因此,预先将曝光装置曝光一次的区域对应于SOI层,以高效地形成所希望的电路图案。

在图5中,以虚线表示曝光装置曝光一次的区域108a及108b。选择性地蚀刻半导体衬底101,以将通过接合而成为SOI层的区域的大小对应于曝光装置曝光一次的区域的大小。

另外,对准标记107a及107b还残留在曝光装置曝光一次的区域108a及108b中。关于该对准标记107a及107b,当在成为SOI层的半导体衬底的一部分中形成抗蚀剂掩模时,还在成为对准标记的部分中形成抗蚀剂掩模。在图5所示的半导体衬底101中,阻挡层也残留在对准标记上。注意,在图1B的截面图中,未图示对准标记107a及107b。

作为去除半导体衬底101的一部分来形成槽的方法,在以抗蚀剂掩模覆盖去除部分以外的部分之后,通过干蚀刻法或湿蚀刻法蚀刻半导体衬底101的一部分。或者,可通过利用切割机的刀、划线机、激光束等形成槽。槽的深度根据之后转置到支撑衬底上的SOI层的厚度而适当地选择。注意,SOI层的厚度可以根据包含加速了的离子元素的区域的位置而设定。在本实施方式中,半导体衬底101的槽的深度优选深于脆弱区域(即,形成脆弱区域的位置)。通过将半导体衬底101的槽加工为其深度深于脆弱区域,可以在之后将SOI层转置在支撑衬底上时容易只将被分离的半导体衬底101的凸部接合到支撑衬底。

在图1C中,通过将加速了的氢离子或卤素离子照射到半导体衬底101,形成脆弱区域103a至103c。脆弱区域103a至103c指的是通过照射加速了的离子而包含离子元素的区域。例如,它指的是包含氢、卤素的脆弱区域,也称为脆弱层。

脆弱区域103a至103c通过从半导体衬底101的表面照射由电场加速的离子来在预定深度处包含该离子的元素而形成。作为这样的离子照射方法,可以举出离子掺杂法和离子注入法等。形成在半导体衬底101中的脆弱区域103a至103c的深度由离子加速能量和离子入射角控制。在离半导体衬底101的表面的深度接近于离子平均进入深度的区域形成脆弱区域103a至103c。例如,半导体层的厚度为5nm至500nm,优选为10nm至200nm,当将离子照射到半导体衬底时的加速电压根据该厚度而设定。

优选使用离子掺杂装置照射离子。就是说,采用如下掺杂方式:

在不对通过使源气体等离子体化而产生的多个离子种类进行质量分离的状态下,以电场加速该多个离子种类来将它照射到对象物,使得对象物包含被离子化的气体元素。在本实施方式中,优选掺杂氢离子或卤素离子。在离子掺杂步骤中,加速电压为10kV至100kV,优选为30kV至80kV,剂量为1×1016/cm2至4×1016/cm2,射束电流密度为2μA/cm2以上,优选为5μA/cm2以上,更优选为10μA/cm2以上,即可。由此,可以减少在半导体层中产生的缺陷。

在照射氢离子的情况下,优选包含H+、H2 +、H3 +离子,并提高H3 +离子的比例。通过在照射氢离子的情况下包含H+、H2 +、H3 +离子,并提高H3 +离子的比例,与在不提高H3 +离子的比例的情况下照射离子的情况相比可以提高引入效率,而可以缩短掺杂时间。由此,可以在形成在半导体衬底101中的脆弱区域103a至103c中包含1×1020/cm3(优选为5×1020/cm3)以上的氢。通过在半导体衬底101中局部地形成包含高浓度氢的区域,结晶结构混乱且产生微小的空位,因此可以形成具有多孔结构的脆弱区域103a至103c。在此情况下,通过在比较低的温度下进行热处理,引起形成在脆弱区域103a至103c中的微小空洞的体积变化,并沿脆弱区域劈开(分离),可以形成厚度薄的半导体层。

在本说明书中,离子掺杂指的是如下方法:在不对通过使用原料气体而产生的离子化气体进行质量分离的状态下,以电场加速该离子化气体来将它照射到对象物。通过使用离子掺杂装置,可以对大面积衬底高效地进行高剂量离子掺杂。

另外,离子掺杂的加速电压为20kV以上100kV以下,优选为20kV以上70kV以下,剂量为1×1016个离子/cm2以上4×1016个离子/cm2以下,优选为1×1016个离子/cm2以上2.5×1016个离子/cm2以下,即可。在本实施方式中,在加速电压为80kV且剂量为2×1016个离子/cm2的状态下进行离子掺杂。

通过对加速了的离子进行质量分离来将它照射到半导体衬底101,也可以同样地形成脆弱区域103a至103c。还在此情况下,优选选择性地照射其质量大的离子(例如H3 +离子),这是因为能够起到与上述相同的效果的缘故。

除了氢以外,还可以选择氘、氦等的惰性气体作为产生离子的气体。通过以氦为原料气体并使用没有质量分离功能的离子掺杂装置,可以获得He+离子的比例高的离子束。通过将这种离子照射到半导体衬底101,可以形成微小的空位,而可以在半导体衬底101中形成与上述相同的脆弱区域103a至103c。

这里,由于在离半导体衬底101的表面有一定深度处包含加速了的离子元素,所以脆弱区域不仅形成在半导体衬底的凸部中,而且还形成在离槽107的表面有一定深度处。

图1D表示形成接合层104(形成在接合界面中的层)的步骤。接合层104是形成平滑面且具有亲水性表面的层。作为可形成这种表面的层,优选使用通过化学反应形成的绝缘层。例如,优选使用通过热反应或化学反应形成的氧化层。这是因为主要通过化学反应形成的层能够确保表面平滑性的缘故。形成平滑面及亲水性表面的接合层104的厚度被设定为0.2nm至500nm。若采用该厚度,则可以降低被成膜表面的粗糙度并确保该膜的生长表面的平滑性。

作为接合层104的优选例子,可以采用通过化学气相沉积法而淀积的氧化硅。在此情况下,优选采用使用有机硅烷气体通过化学气相沉积法而形成的氧化硅层。作为有机硅烷气体,可以使用硅酸乙酯(四乙氧基硅烷,TEOS;Si(OC2H5)4)、四甲基硅烷(Si(CH3)4)、三甲基硅烷((CH3)3SiH)、四甲基环四硅氧烷(TMCTS)、八甲基环四硅氧烷(OMCTS)、六甲基二硅氮烷(HMDS)、三乙氧基硅烷(SiH(OC2H5)3)、三二甲氨基硅烷(SiH(N(CH3)2)3)等的含硅化合物。在使用化学气相沉积法的成膜步骤中,采用从形成在半导体衬底中的脆弱区域103a至103c不发生脱气的温度如350℃以下的成膜温度。另外,在从单晶半导体衬底或多晶半导体衬底剥离(分离)单晶半导体层或多晶半导体层的热处理步骤中,采用比成膜温度高的热处理温度。

接合层104形成在支撑衬底100一侧及半导体衬底101一侧中的单方或双方,即可。

在图1B和1C所示的步骤中,也可以在形成脆弱区域103a至103c并去除半导体衬底的一部分而形成槽107之后,形成阻挡层102和接合层104。通过进行这一步骤,可以在不暴露于大气的状态下连续形成阻挡层102和接合层104,并可以防止向半导体衬底101的异物混入、半导体衬底101的钾或钠等的污染。另外,由于脆弱区域103c不形成在后续的剥离(分离)步骤中分离的半导体衬底中,所以容易再利用半导体衬底101。

图2A表示接合支撑衬底100和半导体衬底101的步骤。通过将支撑衬底100和半导体衬底101的形成有接合层104的面相对并密接,实现接合。对接合的面进行脱脂处理以使它十分干净。然后,通过将支撑衬底100和接合层104密接,在室温下实现接合。这一接合起因于表面间引力,而且更优选进行将多个亲水基附着在表面上的处理。例如,优选对支撑衬底100的表面进行氧等离子体处理或臭氧处理而使它具有亲水性。在进行使表面具有亲水性的这一处理的情况下,由于表面的羟基而以氢键实现接合。再者,通过对将干净的两个表面密接而实现接合的衬底等在室温以上的温度下进行加热,可以提高接合强度。

为了实现良好接合,进行如下处理是有效的:作为接合层104的表面及与接合层104接触的表面中的单方或双方的预处理,对其表面照射利用惰性气体如氩等的离子束使它干净。通过离子束照射,悬空键露出在接合层104的表面及与接合层104接触的表面中的单方或双方上,而形成具有高活性的表面。将这样激活了的两个表面密接,则可以在低温下实现接合。通过激活表面而实现接合的方法因需要使该表面十分干净而优选在真空中进行。

通过进行上述表面处理,即使在200℃至400℃的温度下也可以提高不同材料之间的接合强度。

支撑衬底100指的是设置SOI层的衬底,它具有绝缘性或绝缘表面,可以使用诸如铝硅酸盐玻璃、铝硼硅酸盐玻璃、钡硼硅酸盐玻璃之类的电子工业用玻璃衬底(也称为无碱玻璃衬底)。就是说,可以使用热膨胀系数为25×10-7/℃至50×10-7/℃(优选为30×10-7/℃至40×10-7/℃)且应变点为580℃至680℃(优选为600℃至680℃)的玻璃衬底。除了上述以外,还可以使用石英衬底、陶瓷衬底、其表面被绝缘层覆盖的金属衬底等。

图2B表示从半导体衬底101剥离(分离)SOI层105a及105b的步骤。在通过将半导体衬底101和支撑衬底100重叠而将接合层104接合到支撑衬底100之后,进行热处理。通过进行热处理,可以以SOI层105a及105b残留在支撑衬底100上的方式分离半导体衬底101,并可以提高接合面的接合强度。热处理优选在接合层104的成膜温度以上的温度下进行,优选在400℃至600℃(包括400℃,不包括600℃)的温度下进行。通过在所述温度下进行热处理,引起形成在脆弱区域103a及103b中的微小空位的体积变化,而可以沿脆弱区域103a及103b分离半导体层。由于接合层104与支撑衬底100接合,所以其结晶性与半导体衬底101相同的SOI层105a及105b接合在支撑衬底100上。

注意,在使用单晶半导体衬底作为半导体衬底101的情况下,SOI层105a及105b成为单晶半导体层。另外,在使用结晶半导体衬底作为半导体衬底101的情况下,SOI层105a及105b成为结晶半导体层。

图6是接合有SOI层的支撑衬底100的上表面的示意图。注意,沿图6的A-B线的截面图相当于图2B。

在支撑衬底100上,以曝光装置曝光一次的区域为一个单元而有规律地排列SOI层105a及105b。另外,还形成有其结晶性与SOI层相同的对准标记107a及107b。

在图6中,在曝光装置曝光一次的区域中设置有一个对准标记和一个SOI层。由于考虑曝光装置曝光一次的区域排列SOI层,而且SOI层对应于曝光装置曝光一次的区域,所以可以高效地进行曝光来形成图案。

另外,通过进行图2B所示的热处理,支撑衬底收缩,而且SOI层105a和SOI层105b的间隔缩小。在图2A中,当将接合层104和支撑衬底100接合时的SOI层的间隔109a与当在半导体衬底101上形成槽时的SOI层的间隔109a相同,但是,在进行所述热处理之后,如图2B和图6所示那样缩小为间隔109b。

然后,优选在SOI层105a及105b固定于支撑衬底100上的状态下进行热处理。该热处理的目的在于将形成脆弱区域110时注入而残留在SOI层105a及105b中的微量氢或卤素从SOI层105a及105b脱离。热处理的温度可以在如下范围:从脆弱区域110释放氢或卤素的温度以上至支撑衬底100的应变点附近的温度。例如,在400℃至730℃的温度下进行热处理。作为热处理装置,可以采用电热炉、灯退火炉等。热处理也可以通过以多阶段改变温度而进行。还可使用快速热退火(RTA)装置。在使用RTA装置进行热处理的情况下,也可以在衬底的应变点附近或比该应变点稍微高的温度下进行加热。

包含在SOI层105a及105b中的过多氢呈现复杂的性质,并有时根据热历史而给半导体元件的特性带来负面影响。例如,包含在硅的晶格之间的氢使为了价电子控制而掺杂的杂质元素不激活,这导致晶体管的阈值电压的变动、源区或漏区的高电阻化。另外,在氢包含在硅的晶格内的情况下,有时硅的配位数变化,从而产生晶格缺陷。当然,氢或卤素起到补偿硅中的悬空键,即修复缺陷的作用,但是优选从SOI层105a及105b去除包含在脆弱区域110中的氢或卤素。

通过进行上述热处理,可以在支撑衬底100和接合层104a及104b的接合面中使氢键变成更坚固的共价键。

接着,优选将能量束照射到SOI层105a及105b以修复结晶缺陷。由于当SOI层105a及105b接合到支撑衬底100时其结晶性因受到热及/或机械损伤而退化,所以优选进行这一步骤以修复缺陷。优选使用选择性地吸收到SOI层105a及105b的能量束,即激光束,以在不过多加热支撑衬底100的状态下修复SOI层105a及105b的缺陷。关于激光束,可以使用以准分子激光器为代表的气体激光器、以YAG激光器为代表的固体激光器作为光源。激光束的波长优选在紫外光区至红外光区。从光源发射的光优选通过使用光学系统而聚光为矩形或线形,在SOI层105a及105b上使用该激光束进行扫描,即可。

除了上述以外,还可以采用利用卤素灯或氙灯等的闪光灯退火,以达到同样的目的。

在这一步骤中,由于已将SOI层105a及105b脱氢化,所以可以在在SOI层105a及105b中不产生孔隙的状态下修复结晶缺陷。另外,通过在氮气氛下进行对SOI层105a及105b的能量束照射处理,可以平整SOI层105a及105b的表面。

另一方面,在SOI层105a及105b所包含的氢很少的情况下,也可以在接合支撑衬底100和SOI层105a及105b之后进行能量束照射处理。通过在修复SOI层105a及105b的结晶缺陷之后进行热处理,可以消除SOI层105a及105b和支撑衬底100的热应变,提高接合面的接合强度。

通过上述步骤,可以形成半导体层的一部分被分离的SOI衬底。

下面,参照图3A至3C及图4A和4B说明根据本实施方式的半导体装置。通过选择性地蚀刻图2B所示的SOI层105a及105b,如图3A所示那样形成半导体层106a及106b。这里,覆盖SOI层105a及105b的一部分地形成通过光刻步骤而形成的抗蚀剂掩模,并选择性地蚀刻SOI层105a及105b,以形成半导体层106a及106b。另外,可以与SOI层105a及105b同样地蚀刻阻挡层102a及102b、以及接合层104a及104b。

半导体层106a及106b设置在支撑衬底100上,其中间夹着阻挡层102c及102d、接合层104c及104d。阻挡层102c及102d也可以设置在支撑衬底100一侧。通过提供阻挡层102c及102d,可以防止SOI层105a及105b的污染。

SOI层105a及105b的厚度为5nm至500nm,优选为10nm至200nm,更优选为10nm至60nm。SOI层105a及105b的厚度可以通过控制图1C所示的脆弱区域103a至103c的深度而适当地设定。优选地,根据n沟道型场效应晶体管及p沟道型场效应晶体管的形成区域,对半导体层106a及106b添加诸如硼、铝和镓之类的p型杂质或诸如磷和砷之类的n型杂质。就是说,通过对应于n沟道型场效应晶体管的形成区域添加p型杂质,并对应于p沟道型场效应晶体管的形成区域添n型杂质,形成所谓的阱区。杂质离子的剂量为约1×1012/cm2至1×1014/cm2,即可。再者,当控制场效应晶体管的阈值电压时,可以对这些阱区添加p型或n型杂质。

图7是形成有半导体层106a及106b的支撑衬底100的上表面的示意图。注意,沿图7的A-B线的截面图相当于图3A。

图7表示使用对准标记107a进行位置对准并选择性地蚀刻SOI层105a以形成所希望的图案的例子。例如,对SOI层105a进行曝光来转印电路图案。此时,通过形成对准标记107a,可以在光刻步骤中容易进行位置对准等。至于蚀刻后的各半导体层106a的图案,构成例如形成在电路部中的晶体管的沟道部。

如图3B所示,形成栅极绝缘层121、栅电极122及侧壁绝缘层123,并形成第一杂质区域124及第二杂质区域125。绝缘层126由氮化硅层构成,并用作在蚀刻栅电极122时的硬掩模。

图3C表示在形成栅电极122等之后形成保护层127的步骤。保护层127优选通过等离子体CVD法在成膜时的衬底温度为350℃以下的状态下形成氮化硅层或氮氧化硅层。就是说,使保护层127包含氢。在形成保护层127之后,通过进行350℃至400℃(优选为400℃至420℃)的热处理将包含在保护层127中的氢扩散到半导体层106a及106b一侧。在元件形成步骤中,对之前的步骤中被脱氢化的半导体层106a及106b提供补偿缺陷的氢,来可以有效地补偿成为俘获中心的缺陷。另外,保护层127具有防止从上层一侧的杂质污染的效果,而阻挡层102c及102d防止从支撑衬底100一侧的杂质扩散。在本实施方式中,通过使用能够防止可动性高的杂质离子如钠等的高效绝缘层覆盖结晶性良好的半导体层106a及106b的下层及上层一侧,对由该半导体层106a及106b构成的半导体元件的特性稳定化发挥巨大的作用。

然后,如图4A所示形成层间绝缘层128。作为层间绝缘层128,形成BPSG(Boron Phosphorus Silicon Glass;硼磷硅玻璃)层,或者,通过涂敷以聚酰亚胺为代表的有机树脂形成层间绝缘层128。而且,在层间绝缘层128中形成接触孔129。

图4B表示形成布线的步骤。在接触孔129中形成接触栓塞130。接触栓塞130通过使用WF6气体和SiH4气体以化学气相沉积法形成硅化钨并将它嵌入接触孔129而形成。也可以对WF6进行氢还原来形成钨并将它嵌入接触孔129。然后,根据接触栓塞130形成布线131。布线131由铝或铝合金构成,其上层及下层由作为阻挡金属的钼、铬及钛等的金属层构成。再在其上形成层间绝缘层132。适当地设置布线,即可,也可以在其上形成另一布线层以实现多层布线化。在此情况下,还可采用金属镶嵌工艺。

如上所述,可以使用与支撑衬底100接合的半导体层106a及106b制造场效应晶体管。半导体层106a及106b是具有一定结晶取向的半导体,因此可以获得均匀且高性能的场效应晶体管。就是说,可以抑制晶体管特性的重要特性值如阈值电压或迁移率等的不均匀性,来实现高迁移率化等的高性能化。

另外,在进行分离半导体衬底的热处理之前,通过在半导体衬底的一部分形成槽形成分离的凸部。然后,将分离的凸部接合到支撑衬底,并进行分离半导体衬底的热处理。通过进行分离半导体衬底的热处理,支撑衬底收缩,因而接合到支撑衬底上的SOI层的位置也变化。但是,由于SOI层是分离而不是连续接合到支撑衬底上,所以可以抑制由支撑衬底收缩产生的SOI层的畸变应力,并可以抑制膜剥离或接合力降低。另外,通过将凸部大致对应于曝光装置的一曝光区域,可以高效地进行曝光步骤。其结果,可以高成品率地制造半导体装置。

实施方式2

参照图8A至10C说明与上述实施方式不相同的半导体装置的制造方法。这里,说明可将半导体衬底高成品率地接合到支撑衬底的半导体装置的制造方法。

如图8A所示,对半导体衬底101的表面进行脱脂清洗,去除表面的氧化层并进行热氧化。虽然可以进行一般的干氧化作为热氧化,但优选进行将卤素添加到氧化气氛中的氧化。例如,在相对于氧包含0.5至10体积%(优选为3体积%)HCl的气氛中以700℃以上的温度进行热处理。优选在950℃至1100℃的温度下进行热氧化。处理时间为0.1至6小时,优选为0.5至1小时。所形成的氧化层的厚度为10nm至1000nm(优选为50nm至200nm),例如100nm。

除了HCl以外,还可以使用选自HF、NF3、HBr、Cl2、ClF3、BCl3、F2、Br2等的一种或多种作为包含卤素的物质。

通过在这种温度范围下进行热处理,可以得到利用卤素的吸杂效果。作为吸杂,尤其具有去除金属杂质的效果。就是说,因为卤素的作用,金属等的杂质成为挥发性卤化物并脱离到气相中而被去除。这对其表面被进行了化学机械抛光(CMP)处理的半导体衬底101有效。另外,氢起到补偿半导体衬底101和氧化层111的界面的缺陷并降低界面的局部能级密度(local level density)的作用。

可以在通过上述热处理而形成的氧化层111中包含卤素。通过以1×1016/cm3至5×1020/cm3的浓度包含卤素,可以发挥捕获金属等的杂质而防止半导体衬底101的污染的保护层功能。

接着,也可以与图1A所示的步骤同样地在氧化层111上形成阻挡层102。通过形成阻挡层102及氧化层111,可以防止来自支撑衬底的杂质元素混入半导体层。

然后,在半导体衬底101中形成脆弱区域103。图10A是被夹具固定的半导体衬底的上表面的示意图。沿图10A的A-B线的截面图相当于图8A。

为了控制脆弱区域103的位置(深度)及加速了的离子的剂量,需要使用夹具112固定半导体衬底101的端部。但是,在被夹具覆盖的区域中,夹具112成为掩模,而不能将离子照射到半导体衬底101。因此,具有如下问题:在被夹具覆盖的区域中,难以剥离(分离),厚度不同的半导体层被接合。

为此,如图8B所示,去除被夹具112覆盖的半导体衬底101来形成槽113。槽113可以与图1A所示的槽107同样地形成。此时,凸部形成在半导体衬底101中。另外,在凸部中形成有连续的脆弱区域103。将其一部分被蚀刻的阻挡层102表示为阻挡层102a。在这里,连续的脆弱区域103指的是形成为横穿整个凸部的脆弱区域。

图10B是形成有槽的半导体衬底的上表面的示意图。沿图10B的A-B线的截面图相当于图8B。

接着,如图8C所示,在阻挡层102a及半导体衬底的凸部上形成接合层104。

然后,如图8D所示,与实施方式1同样地对接合层104的表面及支撑衬底100的表面进行脱脂处理而使它十分干净。接着,进行一种处理,即将多个羟基附着在接合层104的表面及支撑衬底100的表面中的单方或双方上。或者,通过将离子束照射到接合层104的表面及支撑衬底100的表面中的单方或双方,使其表面干净并激活其表面。然后,将支撑衬底100和接合层104贴紧来接合。通过压接支撑衬底100和半导体衬底101,可以将支撑衬底100和半导体衬底101坚固接合。

图9A表示从半导体衬底101剥离(分离)SOI层105的步骤。在将半导体衬底101和支撑衬底100重叠并贴紧而将接合层104接合到支撑衬底100之后,通过进行热处理,可以以SOI层105残留在支撑衬底100上的方式分离半导体衬底101,并可以提高接合面的接合强度。热处理优选在接合层104的成膜温度以上的温度下进行,优选在400℃至600℃(包括400℃,不包括600℃)的温度下进行。通过在所述温度下进行热处理,引起形成在脆弱区域103中的微小空位的体积变化,而可以沿脆弱区域103分离半导体层。由于接合层104与支撑衬底100接合,所以其结晶性与半导体衬底101相同的SOI层105接合在支撑衬底100上。

通过进行上述热处理,可以在支撑衬底100和接合层104a的接合面中使氢键变成更坚固的共价键。另外,优选将能量束照射到SOI层105以修复结晶缺陷。

图10C是接合有SOI层的支撑衬底的上表面的示意图。沿图10C的A-B线的截面图相当于图9A。由于不能将加速了的离子照射到设置有夹具的半导体衬底的区域,所以具有半导体衬底在该区域中不能被分离而残留的问题。但是,根据本实施方式,通过去除设置有夹具的半导体衬底的区域来形成槽,可以将预定厚度的SOI层接合在支撑衬底上。

通过上述步骤,可以制造SO1衬底。

然后,通过选择性地蚀刻SOI层105,如图9B所示那样形成半导体层106a及106b。这里,覆盖SOI层105的一部分地形成通过光刻步骤而形成的抗蚀剂掩模,并选择性地蚀刻SOI层105,以形成半导体层106a及106b。另外,可以与SOI层105同样地蚀刻氧化层111a、阻挡层102a、以及接合层104a。

半导体层106a及106b设置在支撑衬底100上,其中间夹着氧化层111b及111c、阻挡层102b及102c、接合层104b及104c。阻挡层102b及102c也可以设置在支撑衬底100一侧。通过提供阻挡层102b及102c,可以防止半导体层106a及106b的污染。

注意,在本实施方式中,虽然如图8A所示那样在形成脆弱区域103之后在半导体衬底101中形成槽113,但是还可以在将槽113形成于被夹具112覆盖的半导体衬底101的区域之后形成脆弱区域103。

另外,可以在实施方式1中适当地采用本实施方式。

如上所述,可以使用与支撑衬底100接合的半导体层106a及106b制造场效应晶体管。半导体层106a及106b是具有一定结晶取向的半导体层,因此可以获得均匀且高性能的场效应晶体管。就是说,可以抑制晶体管特性的重要特性值如阈值电压或迁移率等的不均匀性,来实现高迁移率化等的高性能化。

根据本实施方式,即使使用耐热温度为700℃以下的支撑衬底100如玻璃衬底等,也可以获得接合部具有高接合强度的半导体层106a及106b。作为支撑衬底100,可以使用诸如铝硅酸盐玻璃、铝硼硅酸盐玻璃、钡硼硅酸盐玻璃之类的称为无碱玻璃的各种电子工业用玻璃衬底。换言之,可以在一边长超过1米的衬底上形成半导体层。通过使用这种大面积衬底,不仅可以制造显示装置如液晶显示器,而且还可以制造半导体集成电路。至于半导体衬底,通过在制造步骤的最初阶段中利用包含卤素的气氛进行热氧化,可以得到吸杂作用,对再利用半导体衬底的情况有效。

另外,在半导体层106a及106b的背沟道(back channel)一侧(与栅电极122相反一侧)设置有包含卤素的氧化层111b及111c,因此局部能级密度降低,而可以抑制阈值电压的变动。再者,除了包含卤素的氧化层111b及111c以外,阻挡层102b及102c还设置在支撑衬底100和半导体层106a及106b之间,由此可以防止金属杂质如钠等从支撑衬底100一侧扩散而污染半导体层106a及106b。

另外,在半导体衬底的凸部中形成有连续的脆弱层,因此可以将预定厚度的SOI层接合到支撑衬底上。为此,可以通过使用该半导体层高成品率地制造半导体装置。

实施方式3

参照图21A至21C说明与上述实施方式不相同的半导体装置的制造方法。这里,说明可将半导体衬底高成品率地接合到支撑衬底的半导体装置的制造方法。

如图21A所示,与实施方式2同样地对半导体衬底101的表面进行脱脂清洗,并去除表面的氧化层,然后进行热氧化,以在半导体衬底101的表面上形成氧化层111。这里,通过进行将卤素引入到氧化气氛中的氧化,进行利用卤素的金属杂质吸杂,补偿半导体衬底101和氧化层111的界面的缺陷并降低界面的局部能级密度。

接着,也可以与实施方式2同样地在氧化层111上形成阻挡层102。

然后,如图21B所示,形成槽113。槽113可以与图1A所示的槽107同样地形成。此时,凸部形成在半导体衬底101中。将其一部分被蚀刻的阻挡层102表示为阻挡层102a,并将其一部分被蚀刻的氧化层111表示为氧化层111a。

接下来,如图21C所示,在半导体衬底101中形成脆弱区域103a至103c。这里,在形成有槽113的区域中用夹具112固定半导体衬底101,然后通过将加速了的离子照射到半导体衬底101,形成脆弱区域103a至103c。在凸部中形成连续的脆弱区域103a。就是说,可以形成横穿整个凸部的脆弱区域103a。

然后,与实施方式2的图8C同样地在阻挡层102a及半导体衬底的凸部上形成接合层104。接着,通过与实施方式2相同的步骤将支撑衬底100和半导体衬底101坚固接合,然后在脆弱区域103中分离半导体衬底101,来可以制造在支撑衬底100上设置有SOI层105的SOI衬底。还可以与实施方式2同样地使用该SOI层105制造场效应晶体管。

在本实施方式中,在半导体衬底的凸部中形成有连续的脆弱层,因此可以将预定厚度的SOI层接合到支撑衬底上。为此,可以通过使用该半导体层高成品率地制造半导体装置。

实施方式4

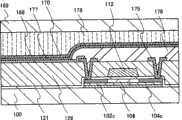

在本实施方式中,参照图11A至14B说明具有柔性的半导体装置的制造方法。

如图11A所示,与实施方式2同样地在去除半导体衬底101的表面的氧化层之后,进行热氧化来形成氧化层。这里,将HCl添加到氧化气氛中并以700℃以上的温度进行热处理,来形成包含氯的氧化层111。接着,在氧化层111上形成阻挡层102。然后,在半导体衬底101中形成脆弱区域103。

接下来,如图11B所示,去除半导体衬底101的一部分来形成槽107。此时,凸部形成在半导体衬底101中。将其一部分被蚀刻的阻挡层102表示为阻挡层102a及102b,并将其一部分被蚀刻的脆弱区域103表示为脆弱区域103a及103b。然后,在阻挡层102a及102b和半导体衬底的凸部上形成接合层104。注意,在将接合层形成在支撑衬底表面上的情况下,不需要一定设置接合层104。

然后,如图11C所示,在支撑衬底141上形成基底层142,在基底层142上形成剥离层143,在剥离层143上形成阻挡层144,并在阻挡层144上形成接合层145。注意,在将接合层形成在半导体衬底表面上的情况下,不需要一定设置接合层145。

这里,优选使用能够耐受在脆弱区域中产生裂缝的加热处理温度(有代表性的为400℃至600℃)的耐热性衬底作为支撑衬底141,典型地可以使用玻璃衬底、石英衬底、陶瓷衬底、金属衬底、硅片等。

基底层142可以与阻挡层102同样地形成。另外,在支撑衬底141和剥离层143的贴紧性高的情况下,也可以不形成基底层142。

剥离层143是通过溅射法、等离子体CVD法、涂敷法、印刷法等使用由如下材料构成的单层或叠层来形成的:选自钨、钼、钛、钽、铌、镍、钴、锆、锌、钌、铑、钯、锇、铱以及硅中的元素;以元素为主要成分的合金材料;或以元素为主要成分的化合物材料。在形成包含硅的层作为剥离层143的情况下,包含硅的层的结晶结构可以为非晶、微晶、多晶中的任何一种。在这里,涂敷法指的是将溶液喷出在被处理物上来形成的方法,例如包括旋涂法及液滴喷射法。另外,液滴喷射法指的是将包含微粒的组成物的液滴从微细的孔喷出而形成具有预定形状的图案的方法。

在剥离层143是单层结构的情况下,优选形成包含钨的层、包含钼的层、或包含钨和钼的混合物的层。或者,形成包含钨的氧化物或氧氮化物的层、包含钼的氧化物或氧氮化物的层、包含钨和钼的混合物的氧化物或氧氮化物的层。注意,钨和钼的混合物例如相当于钨和钼的合金。

在剥离层143是叠层结构的情况下,优选形成金属层作为第一层,形成金属氧化物层作为第二层。典型地,形成包含钨、钼、或钨和钼的混合物的层作为第一层,形成包含如下材料的层作为第二层:钨、钼、或钨和钼的混合物的氧化物;钨、钼、或钨和钼的混合物的氮化物;钨、钼、或钨和钼的混合物的氧氮化物;或者钨、钼、或钨和钼的混合物的氮氧化物。

在形成金属层作为第一层,形成金属氧化物层作为第二层来将它们用作剥离层143时,可以应用如下情况:通过形成金属层如包含钨的层,并在其上层形成由氧化物构成的层间绝缘层132如氧化硅层,来将金属氧化物层如包含钨的氧化物的层形成在包含钨的层和绝缘层的界面。再者,也可以通过对金属层的表面进行热氧化处理、氧等离子体处理、采用氧化力强的溶液如臭氧水等的处理等,形成金属氧化物层。

再者,作为剥离层143,也可以形成金属层作为第一层,形成金属氮化物层、金属氧氮化物层作为第二层。典型地说,在形成包含钨的层作为第一层之后,形成氮化钨层、氧氮化钨层作为第二层。

阻挡层144可以与实施方式1所示的阻挡层102同样地形成。

接合层145可以与实施方式1所示的接合层104同样地形成。

然后,如图11D所示,与实施方式1同样地使接合层104的表面及支撑衬底141的表面十分干净。接着,进行一种处理,即将多个羟基附着在接合层104的表面及支撑衬底141的表面中的单方或双方上。或者,通过将离子束照射到接合层104的表面及支撑衬底141的表面中的单方或双方,使其表面干净并激活其表面。然后,将形成在支撑衬底141上的接合层145和形成在半导体衬底101上的接合层104贴紧来接合。

下面,参照图14A和14B说明半导体衬底表面的叠层结构及支撑衬底的叠层结构。

如图14A所示,可以具有如下结构:在支撑衬底141上形成有基底层142、剥离层143及阻挡层144的三层结构,并在半导体衬底101的表面上层叠有氧化层111及接合层104。通过将具有这种结构的支撑衬底141和半导体衬底101密接,可以接合阻挡层144及接合层104。

虽然未图示,但也可以具有如下结构:在支撑衬底上形成有基底层、剥离层、阻挡层及接合层的四层结构,并在半导体衬底的表面上形成有氧化层。通过将具有这种结构的支撑衬底和半导体衬底密接,可以将接合层及氧化层接合。

就是说,通过将阻挡层设置在支撑衬底141及半导体衬底101中的一方上,可以防止来自外部的杂质混入半导体层。另外,通过将接合层设置在支撑衬底141及半导体衬底101中的一方上,可以接合支撑衬底141及半导体衬底101。再者,可以减少支撑衬底141及半导体衬底101的叠层数,而可以提高产率。

如图14B所示,也可以不是对半导体衬底101进行热氧化来形成氧化层,而是与半导体衬底101接触地形成接合层104。在此情况下,在支撑衬底141上形成有基底层142、剥离层143及阻挡层144的叠层结构。

虽然未图示,但也可以在支撑衬底上形成有基底层、剥离层、阻挡层及接合层的四层结构,并通过将支撑衬底和半导体衬底密接,可以将接合层及氧化层接合。

就是说,即使不设置热氧化层,也可通过将阻挡层设置在支撑衬底141上防止来自外部的杂质混入半导体层。另外,通过将接合层设置在支撑衬底141及半导体衬底101中的一方上,可以接合支撑衬底141及半导体衬底101。再者,可以减少支撑衬底141及半导体衬底101的叠层数,而可以提高产率。

接下来,如图12A所示,通过进行加热处理及加压处理中的单方或双方,可以以脆弱区域103a及103b为劈开面(指的是单晶半导体衬底分离的区域,也称为分离区域)将半导体衬底101从支撑衬底141剥离(分离),并提高接合面的接合强度。加热处理的温度优选为支撑衬底141的耐热温度以下。例如,通过进行400℃至600℃的热处理,引起形成在脆弱区域103a及103b中的微小空洞的体积变化,而可以沿脆弱区域103a及103b分离。

此时,也可以从半导体衬底101照射激光束代替加热处理,以引起形成在脆弱区域103a及103b中的微小空洞的体积变化。作为激光束,优选采用透过半导体衬底且被包含在脆弱区域103a及103b中的元素吸收的波长,典型地可以采用红外光。

在剥离(分离)半导体衬底101之后,优选平整SOI层105a及105b的表面。典型地说,采用CMP或上述激光束照射。另外,也可以为了将所获得的SOI层薄层化而进行CMP等。

接下来,通过选择性地蚀刻SOI层105a及105b,如图12B所示那样形成半导体层106a及106b。此时,也可以蚀刻氧化层111b及111c和接合层104a及104b的一部分。这里,将其一部分被蚀刻的氧化层表示为氧化层111d及111e,并将被蚀刻的接合层表示为接合层104c及104d。另外,也可以选择性地蚀刻阻挡层102c及102d、接合层104a及104b、接合层145。

然后,经过图3A至3C及图4A和4B的步骤,如图12C所示那样使用半导体层106a及106b形成包括场效应晶体管的元件层151。接着,在元件层151上设置柔性衬底152。通过热压合柔性衬底152及元件层151,可以将柔性衬底152固定于元件层151上。还可通过使用粘合材料(未图示)将柔性衬底152固定于元件层151上。作为柔性衬底152,使用具有柔性且具有绝缘表面的衬底,典型地说,可以举出具有柔性的绝缘衬底、在其表面上形成有绝缘层的柔性金属衬底等。作为具有柔性的绝缘衬底,可以举出由PET(聚对苯二甲酸乙二醇酯)、PEN(聚萘二甲酸乙二醇酯)、PES(聚醚砜)、聚丙烯、聚丙烯硫醚、聚碳酸酯、聚醚酰亚胺、聚苯硫醚、聚苯醚、聚砜、聚邻苯二甲酰胺等构成的塑料衬底、或由纤维材料构成的纸。

另外,通过使用预浸料(prepreg)作为具有柔性的绝缘衬底,可以防止之后形成的SOI衬底或半导体装置因点压或线压而损伤。预浸料的代表例子如下:将诸如聚乙烯醇纤维、聚酯纤维、聚酰胺纤维、聚乙烯纤维、芳族聚酰胺纤维、聚对苯撑苯并双噁唑纤维、玻璃纤维或碳素纤维之类的纤维体浸在使用有机溶剂稀释诸如环氧树脂、不饱和聚酯树脂、聚酰亚胺树脂或氟树脂之类的基质树脂而得到的清漆中,然后通过干燥使有机溶剂挥发以将基质树脂半固化。

作为在其表面上形成有绝缘层的柔性金属衬底,可以举出形成有氧化硅层、氮化硅层、氧氮化硅层、氮化铝层、氧化铝层等的绝缘层的金属膜或金属片等。绝缘层不局限于上述绝缘层,可以适当地选择。

接着,如图13A所示,以物理方法从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体。或者,通过将液体渗透到剥离层143和阻挡层144的界面,从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体。

物理方法指的是力学方法或机械方法,就是使某种力学能量(机械能量)变化的方法。该方法典型地是施加机械性力量(例如,用人的手或夹握工具剥下的处理,或者使滚筒转动而进行分离的处理)。此时,若在支撑衬底141及柔性衬底152中的至少一方的表面上设置可通过光或热而剥离的粘结薄片,则更容易进行剥离。

这里,剥离层143和阻挡层144的界面、剥离层143、以及支撑衬底141和剥离层143的界面中的任一处发生剥离,就可以从基底层142剥离包括元件层151及柔性衬底152的叠层体。

在剥离层143处从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体之前,也可以进行某种处理以容易进行剥离。再者,当从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体时,通过在支撑衬底141及柔性衬底152中的至少一方的表面上设置可通过光或热而剥离的粘结薄片,固定支撑衬底141及柔性衬底152中的一方并剥下其另一方,以更容易进行剥离。

接下来,如图13B所示,将柔性衬底153粘合到阻挡层144。作为柔性衬底153,可以使用作为柔性衬底152举出例子的上述材料。

然后,在元件层151包括多个半导体装置的情况下,可以将元件层151、柔性衬底152及153分割成多个半导体装置。通过上述步骤,可以制造薄且具有柔性的多个半导体装置。

在本实施方式中,在通过使用被接合在支撑衬底上的SOI层形成场效应晶体管之后,从支撑衬底剥离具有场效应晶体管的元件层,以制造具有柔性且薄的半导体装置。与柔性衬底相比,支撑衬底容易使用,因此在制造步骤中容易进行处理,可以提高成品率。

根据本实施方式的SOI层105a和105b是具有一定结晶取向的半导体层,因此可以获得均匀且高性能的场效应晶体管。就是说,可以抑制晶体管特性的重要特性值如阈值电压或迁移率等的不均匀性,来实现高迁移率化等的高性能化。再者,在支撑衬底100和SOI层105a、105b之间设置有阻挡层102c和102d,因此可以防止来自支撑衬底的杂质侵入SOI层。由此,可以抑制形成在元件层中的晶体管的特性不均匀。

实施方式5

在本实施方式中,参照图22A至22D说明与实施方式4不相同的半导体装置的制造方法。在本实施方式中,说明具有柔性的半导体装置的制造方法。

如图22A所示,与实施方式2同样地使用单晶半导体衬底作为半导体衬底101,去除其表面的氧化层,然后进行热氧化来形成氧化层111。接着,在氧化层111上形成阻挡层102。

其次,如图22B所示,与实施方式2同样地去除半导体衬底101的一部分来形成槽107。此时,凸部形成在半导体衬底101中。将其一部分被蚀刻的阻挡层102表示为阻挡层102a及102b。

接着,如图22C所示,与实施方式2同样地在半导体衬底101中形成脆弱区域103a至103c。

然后,如图22D所示,与实施方式2同样地在阻挡层102a及102b和半导体衬底的凸部上形成接合层104。注意,在将接合层形成在支撑衬底表面上的情况下,不需要一定设置接合层104。

接着,如图11C所示,与实施方式4同样地在支撑衬底141上依次形成基底层142、剥离层143、阻挡层144及接合层145。

然后,如图11D所示,与实施方式4同样地将形成在支撑衬底141上的接合层145和形成在半导体衬底101上的接合层104贴紧来接合。接着,如图12A所示,以脆弱区域103a及103b为分离面从支撑衬底141剥离(分离)半导体衬底101,来在支撑衬底上设置SOI层105a及105b。然后,如图12C所示,与实施方式1同样地使用SOI层105a及105b形成场效应晶体管,并形成包括场效应晶体管的元件层151。接着,在将柔性衬底152固定于元件层151之后,如图13A所示,通过物理方法从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体。或者,通过将液体渗透到剥离层143和阻挡层144的界面,从支撑衬底141剥离包括柔性衬底152及元件层151的叠层体。然后,如图13B所示,将柔性衬底153粘合到阻挡层144。通过上述步骤,可以制造具有柔性的半导体装置。

然后,在元件层151包括多个半导体装置的情况下,可以将元件层151、柔性衬底152及153分割成多个半导体装置。通过上述步骤,可以制造薄且具有柔性的多个半导体装置。

在本实施方式中,在通过使用被接合在支撑衬底上的SOI层形成场效应晶体管之后,从支撑衬底剥离具有场效应晶体管的元件层,以制造具有柔性且薄的半导体装置。与柔性衬底相比,支撑衬底容易使用,因此在制造步骤中容易进行处理,可以提高成品率。

根据本实施方式的SOI层105a和105b是具有一定结晶取向的半导体层,因此可以获得均匀且高性能的场效应晶体管。就是说,可以抑制晶体管特性的重要特性值如阈值电压或迁移率等的不均匀性,来实现高迁移率化等的高性能化。再者,在支撑衬底100和SOI层105a、105b之间设置有阻挡层102a和102b,因此可以防止来自支撑衬底的杂质侵入SOI层。由此,可以抑制形成在元件层中的晶体管的特性不均匀。

实施方式6

在本实施方式中,参照图15说明半导体装置的一个方式。图15表示通过使用SOI衬底而形成的微处理器200的结构,作为半导体装置的一个例子。微处理器200如上所述那样通过使用根据本发明的半导体衬底而形成。微处理器200包括算术逻辑单元201(Arithmeticlogic unit,也称为ALU)、ALU控制器202(ALU Controller)、指令解码器203(Instruction Decoder)、中断控制器204(interruptcontroller)、时序控制器205(Timing Controller)、寄存器206(Register)、寄存器控制器207(Register Controller)、总线接口208(Bus I/F)、只读存储器209(ROM)、以及ROM接口210(ROMI/F)。

通过总线接口208输入到微处理器200的指令在输入到指令解码器203并被解码之后输入到ALU控制器202、中断控制器204、寄存器控制器207、以及时序控制器205。ALU控制器202、中断控制器204、寄存器控制器207、以及时序控制器205根据被解码了的指令而进行各种控制。具体地说,ALU控制器202产生用来控制算术逻辑单元201的工作的信号。中断控制器204当在执行微处理器200的程序时对来自外部输入输出装置或外围电路的中断要求根据其优先级或掩模状态而进行判断来处理。寄存器控制器207产生寄存器206的地址,并根据微处理器200的状态进行寄存器206的读出或写入。时序控制器205产生控制算术逻辑单元201、ALU控制器202、指令解码器203、中断控制器204及寄存器控制器207的工作时序的信号。例如,时序控制器205包括根据基准时钟信号CLK1产生内部时钟信号CLK2的内部时钟产生部,并将时钟信号CLK2提供给上述各种电路。注意,图15所示的微处理器200只是将其结构简化了的一个例子,在实际上,可以根据其用途具有各种各样的结构。

在上述微处理器200中,通过使用接合在具有绝缘表面的支撑衬底上的具有一定结晶取向的半导体层(单晶半导体层)形成集成电路,因此不仅可以实现处理速度的高速化,而且还可以实现低耗电量化。另外,阻挡层设置在支撑衬底和半导体层之间,由此可以防止金属杂质如钠等从支撑衬底一侧扩散而污染半导体层。

实施方式7

在本实施方式中,参照图16说明说明能够非接触地进行数据收发且具有计算功能的半导体装置的一个方式。这里,参照图16说明通过使用SOI衬底而得到的RFCPU的结构。图16表示以无线通信与外部装置进行信号收发来工作的计算机(以下称为RFCPU)的一个例子。RFCPU211包括模拟电路部212和数字电路部213。模拟电路部212包括具有谐振电容的谐振电路214、整流电路215、恒压电路216、复位电路217、振荡电路218、解调电路219、调制电路220、以及电源管理电路230。数字电路部213包括RF接口221、控制寄存器222、时钟控制器223、接口224(CPU接口)、中央处理单元(CPU)225、随机存取存储器(RAM)226、以及只读存储器(ROM)227。

具有这种结构的RFCPU211的工作概要如下:基于天线228所接收的信号,谐振电路214产生感应电动势。感应电动势经过整流电路215而存储到电容部229。该电容部229优选由电容器如陶瓷电容器或双电层电容器等构成。电容部229不需要与RFCPU211一体形成,而可以作为另一部件安装在构成RFCPU211的具有绝缘表面的衬底上。

复位电路217产生将数字电路部213复位并初始化的信号。例如,产生在电源电压升高之后延迟升高的信号作为复位信号。振荡电路218根据由恒压电路216产生的控制信号改变时钟信号的频率和占空比。由低通滤波器构成的解调电路219例如将调幅(ASK)方式的接收信号的振幅的变动二值化。调制电路220使调幅(ASK)方式的发送信号的振幅变动来发送。调制电路220通过使谐振电路214的谐振点变化来改变通信信号的振幅。时钟控制器223根据电源电压或中央处理单元225的消耗电流,产生用来改变时钟信号的频率和占空比的控制信号。并且,由电源管理电路230监视电源电压。

从天线228输入到RFCPU211的信号被解调电路219解调后,在RF接口221中被分解为控制指令、数据等。控制指令存储在控制寄存器222中。控制指令包括存储在只读存储器227中的数据的读出、向随机存取存储器226的数据写入、向中央处理单元225的计算指令等。中央处理单元225通过接口224对只读存储器227、随机存取存储器226及控制寄存器222进行存取。接口224具有如下功能:根据中央处理单元225所要求的地址,产生对只读存储器227、随机存取存储器226及控制寄存器222中的任何一个的存取信号。

作为中央处理单元225的计算方式,可以采用将OS(操作系统)存储在只读存储器227中并在启动的同时读出并执行程序的方式。另外,也可以采用由专用电路构成计算电路并以硬件方式对计算处理进行处理的方式。作为并用硬件和软件这双方的方式,可以采用如下方式:由专用计算电路进行一部分的处理,使用程序由中央处理单元225进行另一部分的计算。

在上述RFCPU211中,通过使用接合在具有绝缘表面的衬底上或绝缘衬底上的具有一定结晶取向的半导体层(单晶半导体层)形成集成电路,因此不仅可以实现处理速度的高速化,而且还可以实现低耗电量化。由此,即使将提供电力的电容部229小型化,也可以保证长时间工作。图16虽然表示RFCPU的方式,但是只要具有通信功能、计算处理功能、存储功能,就可以采用IC标签。

实施方式8

上述实施方式所示的SOI层可以接合在制造显示面板的称为母玻璃的大型玻璃衬底上。图17表示将SOI层105接合在作为支撑衬底100的母玻璃上的情况。母玻璃被分割成多个显示面板,优选根据显示面板162的形成区域接合SOI层105。母玻璃衬底的面积比半导体衬底大,因此,如图17所示,优选在显示面板162的形成区域的内侧配置多个SOI层105。由此,当将多个SOI层105排列并配置在支撑衬底100上时,可以使相邻间隔十分宽。显示面板162具有扫描线驱动电路区域163、信号线驱动电路区域164及像素形成区域165,以包括这些区域的方式将SOI层105接合到支撑衬底100。

图18A和18B表示液晶显示装置的像素的一个例子,其中像素晶体管由接合在大型玻璃衬底上的半导体层构成。图18A是像素的平面图,在该像素中,半导体层与扫描线166交叉,并与信号线167和像素电极168连接。图18B是沿图18A所示的J-K截断线的截面图。

在图18B中,存在着具有在支撑衬底100上层叠有接合层104c、阻挡层102c及半导体层106的结构的部分,该区域包括在像素晶体管中。在层间绝缘层128上设置有像素电极168。在连接半导体层106和信号线167的接触孔中,由于蚀刻层间绝缘层128而产生凹台阶,因此嵌入该凹部地设置柱状间隔物171。在相对衬底169上形成有相对电极170,并在柱状间隔物171的间隙形成有液晶层172。

图19A表示电致发光显示装置的一个例子,其中像素部的晶体管由接合在大型玻璃衬底上的半导体层构成。图19A是像素的平面图,包括连接到信号线167的选择晶体管173、以及连接到电源线175的显示控制晶体管174。上述显示装置的结构如下:在各像素中设置有其电极之间夹有包含电致发光材料的层(EL层)的发光元件。像素电极168连接到显示控制晶体管174。图19B是表示上述像素的主要部分的截面图。

在图19B中,使用大型玻璃衬底作为支撑衬底100,存在着具有在该支撑衬底100上层叠有接合层104c、阻挡层102c及半导体层106的结构的部分,该区域包括在显示控制晶体管中。接合层104c、阻挡层102c、半导体层106及层间绝缘层128等的结构与图18B同样。第一电极168的周边部被具有绝缘性的隔离壁层176包围。在第一电极168上形成有EL层177。在EL层177上形成有第二电极170。使用密封树脂178填充像素部,并设置有衬底169作为补强板。

本实施方式的电致发光显示装置将上述像素排列为矩阵状来构成显示屏。在此情况下,像素的晶体管的沟道部由接合在支撑衬底100上的半导体层106构成,因此在半导体层106由单晶半导体层构成的情况下,具有各晶体管之间没有特性不均匀性、每个像素的发光亮度均匀的优点。因此,容易使用电流控制发光元件的亮度来驱动,并且不需要用来校正晶体管特性的不均匀的校正电路,而可以减轻驱动电路的负担。再者,可以选择透光衬底作为支撑衬底100,因此可以构成从支撑衬底100一侧发射光的底部发光型电致发光显示装置。

如上所述,还可以在制造显示装置的母玻璃上形成晶体管,该晶体管由使用被接合的半导体衬底的一部分而形成的半导体层构成。关于由该半导体层构成的晶体管,电流驱动能力等的所有工作特性都比非晶硅晶体管优良,因此可以减少晶体管的尺寸。由此,可以提高显示面板中的像素部的开口率。还可以形成图15及16所示的微处理器,因此可以在显示装置内提供计算机的功能。还可以制造能够非接触地进行数据收发的显示器。

实施方式9

根据本发明,可以构成各种各样的电器。作为电器,可以举出摄像机、数字照相机等、导航系统、音频再现装置(汽车音响、音响组件等)、计算机、游戏机、便携式信息终端(移动计算机、移动电话、便携式游戏机或电子书等)、具有记录媒质的图像再现装置(具体地说,能够再现记录媒质例如数字通用盘(DVD)等并且具有能够显示其图像的显示器的装置)等。

图20A示出移动电话301的一个例子。该移动电话301包括显示部302、操作部303等。在显示部302中,可以使用图18A和18B所示的液晶显示装置或图19A和19B所示的电致发光显示装置。通过使用根据实施方式8的显示装置,可以构成显示不均匀性低且图像质量高的显示部。还可将实施方式6及7的半导体装置适用于包括在移动电话301中的微处理器或存储器。

图20B示出数字播放器304作为音响装置的一个典型实例。图20B所示的数字播放器304包括显示部302、操作部303、以及耳机305等。还可以使用头戴式耳机或无线耳机代替耳机305。在数字播放器304中,可以将本发明的半导体装置适用于存储音乐数据的存储部或使数字播放器304工作的微处理器。具有上述结构的数字播放器304可以实现小型轻量化。通过将图18A和18B所示的液晶显示装置或图19A和19B所示的电致发光显示装置适用于显示部302,即使屏幕尺寸为0.3英寸至2英寸左右也能够显示高清晰图像或文字信息。

图20C示出电子书306。该电子书306包括显示部302及操作部303。另外,可以在其内部装有调制解调器,又可以具有以无线方式输出/输入信息的结构。在电子书306中,可以将实施方式6及7的半导体装置适用于存储信息的存储部或使电子书306工作的微处理器。在存储部中,使用存储容量为20至200千兆字节(GB)的NOR型非易失性存储器,来可以存储并再现图像或音频(音乐)。通过将图18A和18B所示的液晶显示装置或图19A和19B所示的电致发光显示装置适用于显示部302,可以进行高图像质量的显示。

实施方式10

下面对作为本发明的特征之一的离子照射方法进行考察。

在本发明中将来源于氢(H)的离子(以下称为氢离子种类)照射到单晶半导体衬底。更具体而言,以氢气体或在其组成中含有氢的气体为原料而使用,来产生氢等离子体,并且将该氢等离子体中的氢离子种类照射到单晶半导体衬底。

(氢等离子体中的离子)

在上述氢等离子体中,存在氢离子种类如H+、H2 +、H3 +。在此,对每个氢离子种类的反应过程(生成过程(formation processes)、消散过程(destruction processes)),下面举出反应式。

e+H→e+H++e ……(1)

e+H2→e+H2 ++e ……(2)

e+H2→e+(H2)*→e+H+H ……(3)

e+H2 +→e+(H2 +)*→e+H++H ……(4)

H2 ++H2→H3 ++H ……(5)

H2 ++H2→H++H+H2 ……(6)

e+H3 +→e+H++H+H ……(7)

e+H3 +→H2+H ……(8)

e+H3 +→H+H+H ……(9)

图23示出示意地表示上述反应的一部分的能量图。要注意的是,图23所示的能量图只不过是示意图,不是严格地规定关于反应的能量的关系。

(H3 +的生成过程)

如上述那样,H3 +主要通过反应式(5)所示的反应过程而生成。另一方面,作为与反应式(5)竞争的反应,有反应式(6)所示的反应过程。为了增加H3 +,至少需要以比反应式(6)的反应多的方式引起反应式(5)的反应(注意,因为作为减少H3 +的反应,也存在有反应式(7)、反应式(8)、反应式(9),所以即使反应式(5)的反应多于反应式(6)的反应,H3 +也不一定增加)。反过来,在反应式(5)的反应比反应式(6)的反应少的情况下,在等离子体中的H3 +的比率减少。

在上述反应式的右边(最右边)的生成物的增加量依赖于反应式的左边(最左边)所示的原料的密度或关于其反应的速度系数等。在此,通过试验已确认到如下事实:当H2 +的动能小于大约11eV时,反应式(5)的反应成为主要反应(即,与关于反应式(6)的速度系数相比,关于反应式(5)的速度系数充分大);当H2 +的动能大于大约11eV时,反应式(6)的反应成为主要反应。

荷电粒子通过从电场受到力而获得动能。该动能对应于电场的势能(potential energy)的减少量。例如,某一个荷电粒子直到与其它粒子碰撞之前获得的动能等于在其期间中经过的电位差的势能。也就是说,有如下趋势:当在电场中能够不与其它粒子碰撞地长距离移动时,与不能不与其它粒子碰撞地长距离移动的情况相比,荷电粒子的动能(的平均)增高。在粒子的平均自由程长的情况下,就是压力低的情况下会发生这种荷电粒子的动能增大的趋势。

另外,即使平均自由程短,也在该平均自由程中可以获得大动能时,荷电粒子的动能会变大。就是,可以说,即使平均自由程短,也在电位差大时,荷电粒子所具有的动能变大。

将上述情况适用于H2 +。在如用于生成等离子体的处理室内那样,以电场的存在为前提的情况下,当在该处理室内的压力低时H2 +的动能变大,当在该处理室内的压力高时H2 +的动能变小。换言之,因为在处理室内的压力低的情况下反应式(6)的反应成为主要反应,所以H3 +有减少的趋势,并且因为在处理室内的压力高的情况下反应式(5)的反应成为主要反应,所以H3 +有增大的趋势。另外,在等离子体生成区域中的电场较强的情况下,即,在某两点之间的电位差大的情况下,H2 +的动能变大。在与此相反的情况下,H2 +的动能变小。换言之,因为在电场较强的情况下反应式(6)的反应成为主要反应,所以H3 +有减少的趋势,并且因为在电场较弱的情况下反应式(5)的反应成为主要反应,所以H3 +有增加的趋势。

(取决于离子源的差异)

在此示出离子种类的比率(尤其是H3 +的比率)不同的一例。图24是表示由100%的氢气体(离子源的压力为4.7×10-2Pa)生成的离子的质量分析结果的图表。注意,上述质量分析通过测量从离子源引出的离子而进行。横轴为离子的质量。在光谱中,质量1的峰值对应于H+、质量2的峰值对应于H2 +、质量3的峰值对应于H3 +。纵轴为光谱的强度,其对应于离子的数量。在图24中,以质量3的离子为100的情形中的相对比来表示质量不同的离子的数量。根据图24可知由上述离子源生成的离子的比率大约为H+∶H2 +∶H3 +=1∶1∶8。注意,也可以由离子掺杂装置获得这种比率的离子,该离子掺杂装置由生成等离子体的等离子体源部(离子源)和用于从该等离子体引出离子束的引出电极等构成。

图25是示出在使用与图24不同的离子源的情况下,当离子源的压力大约为3×10-3Pa时,由PH3生成的离子的质量分析结果的图表。上述质量分析结果是注目于氢离子种类的。此外,质量分析通过测量从离子源引出的离子而进行。与图24相同,横轴表示离子的质量,质量1的峰值对应于H+、质量2的峰值对应于H2 +、质量3的峰值对应于H3 +。纵轴为对应于离子的数量的光谱的强度。根据图25可知在等离子体中的离子的比率大约为H+∶H2 +∶H3 +=37∶56∶7。注意,虽然图25是当源气体为PH3时的数据,但是当将100%的氢气体用作源气体时,氢离子种类的比率也成为相同程度。

在采用获得图25所示的数据的离子源的情况下,在H+、H2 +、以及H3 +中,H3 +的生成仅在7%左右。另一方面,在采用获得图24所示的数据的离子源的情况下,可以将H3 +的比率成为50%以上(在上述条件下大约为80%)。可以估计这是起因于在上述考察中获知的处理室内的压力及电场。

(H3 +的照射机制)

在生成如图24那样包含多个离子种类的等离子体且对生成了的离子种类不进行质量分离而照射到单晶半导体衬底的情况下,H+、H2 +、H3 +的每个离子被照射到单晶半导体衬底的表面。为了再现从照射离子到形成离子引入区域的机制,举出下列的五种模式:

1.照射的离子种类为H+,照射之后也为H+(H)的情况;

2.照射的离子种类为H2 +,照射之后也为H2 +(H2)的情况;

3.照射的离子种类为H2 +,照射之后分成两个H(H+)的情况;

4.照射的离子种类为H3 +,照射之后也为H3 +(H3)的情况;

5.照射的离子种类为H3 +,照射之后分成三个H(H+)的情况。

(模拟结果和实测值的比较)

根据上述模式,进行当将氢离子种类照射到Si衬底时的模拟。作为用于模拟的软件,使用SRIM(the Stopping and Range of Ions inMatter:通过蒙特卡罗(Monte Carlo)法的离子引入过程的模拟软件,是TRIM(the Transport of Ions in Matter)的改良版)。注意,为了计算上的方便,在模式2中将H2 +转换为具有两倍质量的H+进行计算,另外,在模式4中将H3 +转换为具有三倍质量的H+进行计算。再者,在模式3中将H2 +转换为具有1/2动能的H+进行计算,并且在模式5中将H3 +转换为具有1/3动能的H+进行计算。

注意,虽然SRIM是以非晶结构为对象的软件,但是在以高能量、高剂量的条件照射氢离子种类的情况下,可以利用SRIM。这是因为由于氢离子种类和Si原子的碰撞,Si衬底的晶体结构变成非单晶结构的缘故。

在图26中示出使用模式1至模式5照射氢离子种类的情况(以H换算照射10万个)的计算结果。另外,一起示出照射图24所示的氢离子种类的Si衬底中的氢浓度(SIMS(Secondary Ion MassSpectroscopy:二次离子质谱)的数据)。对于使用模式1至模式5进行的计算的结果,以氢原子的个数表示纵轴(右轴),对于SIMS数据,以氢原子的浓度表示纵轴(左轴)。横轴为离Si衬底的表面的深度。在对实测值的SIMS数据和计算结果进行比较的情况下,模式2及模式4明显地从SIMS数据的峰值偏离,并且在SIMS数据中不能观察到对应于模式3的峰值。由此,可知模式2至模式4的影响相对较小。通过考虑虽然离子的动能为keV的数量级,但H-H键能只不过大约为几eV,可以估计模式2及模式4的影响小是由于与Si的碰撞,大部分的H2 +或H3 +分成H+或H的缘故。

根据上述理由,下面不考虑模式2至模式4。在图27至图29中示出当使用模式1及模式5照射氢离子种类时(以H换算照射10万个)的计算结果。另外,一起示出照射图24所示的氢离子种类的Si衬底中的氢浓度(SIMS数据)及将上述模拟结果拟合于SIMS数据的数据(下面称为拟合函数)。在此,图27示出将加速电压设定为80kV的情况,图28示出将加速电压设定为60kV的情况,并且图29示出将加速电压设定为40kV的情况。注意,对于使用模式1及模式5进行计算的结果,以氢原子的个数表示纵轴(右轴),对于SIMS数据以及拟合函数,以氢原子的浓度表示纵轴(左轴)。横轴为离Si衬底的表面的深度。

通过考虑模式1及模式5使用下面的计算式算出拟合函数。注意,在计算式中,X、Y为关于拟合的参数,并且V为体积。

[拟合函数]=X/V×[模式1的数据]+Y/V×[模式5的数据]

当考虑实际上照射的离子种类的比率(大约为H+∶H2 +∶H3 +=1∶1∶8)时,也应该顾及H2 +的影响(即,模式3),但是因为下面所示的理由,在此排除模式3。

·由于通过模式3所示的照射过程而引入的氢与模式5的照射过程相比极少,因此排除模式3来顾及也没有大的影响(SIMS数据中也没有出现峰值)。

·由于在模式5中发生的沟道效应(起因于结晶的晶格结构的元素移动),其峰值位置与模式5接近的模式3不明显的可能性高。就是,预计模式3的拟合参数是很困难的。这是因为在本模拟中以非晶Si为前提,因此不顾及起因于结晶度的影响的缘故。

在图30中总结上述的拟合参数。在上述所有的加速电压下,引入的H的数量的比率大约为[模式1]∶[模式5]=1∶42至1∶45(当在模式1中的H的个数为1的情况下,在模式5中的H的个数大约为42以上且45以下),并且照射的离子种类的个数的比率大约为[H+(模式1)]∶[H3 +(模式5)]=1∶14至1∶15(当在模式1中的H+的个数为1的情况下,在模式5中的H3 +的个数大约为14以上且15以下)。通过考虑不顾及模式3和假设用非晶Si而进行计算等的条件,可以认为获得了与关于实际上的照射的离子种类的比率(大约为H+∶H2 +∶H3 +=1∶1∶8)接近的值。

(使用H3 +的效果)

通过将如图24所示那样的提高H3 +的比率的氢离子种类照射到衬底,可以获得起因于H3 +的多个优点。例如,因为H3 +分成H+或H等而引入到衬底内,与主要照射H+或H2 +的情况相比,可以提高离子的引入效率。因此,可以提高半导体衬底的产率。另外,H3 +分开之后的H+或H的动能有变小的趋势,因此适合于较薄的半导体层的制造。

注意,在本说明书中,为了高效地照射H3 +,对利用能够照射如图24所示那样的氢离子种类的离子掺杂装置的方法进行说明。离子掺杂装置的价格低廉且适合于大面积处理,因而通过利用这种离子掺杂装置照射H3 +,可以获得明显的效果如提高半导体特性、实现大面积化、低成本化、提高产率等。另一方面,当以H3 +的照射考虑为首要时,不需要被解释为限于利用离子掺杂装置的方式。

本说明书根据2007年5月11日在日本专利局受理的日本专利申请编号2007-127270而制作,所述申请内容包括在本说明书中。

Claims (12)

1.一种制造半导体装置的方法,包括:

在单晶半导体衬底上形成阻挡层;

通过将所述单晶半导体衬底的端部去除来在所述单晶半导体衬底的表面上形成槽;

用离子照射所述单晶半导体衬底的所述表面,以在所述单晶半导体衬底中形成脆弱区域;

在所述阻挡层上形成第一接合层;

将所述单晶半导体衬底接合到具有绝缘表面的支撑衬底,允许所述第一接合层和所述绝缘表面被夹在所述单晶半导体衬底和所述支撑衬底之间;

将所述单晶半导体衬底与所述支撑衬底分离,以允许将所述第一接合层、所述阻挡层、以及与被夹在所述阻挡层和所述脆弱区域之间区域对应的所述单晶半导体衬底的薄层转置到所述支撑衬底上;以及

将激光束照射在所述单晶半导体衬底的薄层上。

2.一种制造半导体装置的方法,包括:

用离子照射单晶半导体衬底的表面,以在所述单晶半导体衬底中形成脆弱区域;

通过将所述单晶半导体衬底的端部去除来在所述单晶半导体衬底的所述表面上形成槽;

在所述单晶半导体衬底上形成阻挡层;

在所述阻挡层上形成第一接合层;

将所述单晶半导体衬底接合到具有绝缘表面的支撑衬底,允许所述第一接合层和所述绝缘表面被夹在所述单晶半导体衬底和所述支撑衬底之间;

将所述单晶半导体衬底与所述支撑衬底分离,以允许将所述第一接合层、所述阻挡层、以及与被夹在所述阻挡层和所述脆弱区域之间区域对应的所述单晶半导体衬底的薄层转置到所述支撑衬底上;以及将激光束照射在所述单晶半导体衬底的薄层上。

3.如权利要求1和2中任一所述的方法,进一步包括在所述支撑衬底上形成第二接合层的步骤,

其中所述第二接合层的形成是在将所述单晶半导体衬底接合到所述支撑衬底之前进行的。

4.一种制造半导体装置的方法,包括:

在单晶半导体衬底上形成阻挡层;

通过将所述单晶半导体衬底的端部去除来在所述单晶半导体衬底的表面上形成槽,以形成凸部;

用离子照射所述单晶半导体衬底的所述表面,以在所述凸部中形成连续的脆弱区域;

在具有绝缘表面的支撑衬底上形成第一接合层;

将所述单晶半导体衬底接合到所述支撑衬底,允许所述第一接合层和所述绝缘表面被夹在所述单晶半导体衬底和所述支撑衬底之间;

将所述单晶半导体衬底与所述支撑衬底分离,以允许将所述第一接合层、所述阻挡层、以及与被夹在所述阻挡层和所述脆弱区域之间区域对应的所述单晶半导体衬底的薄层转置到所述支撑衬底上;以及

将激光束照射在所述单晶半导体衬底的薄层上,

其中,所述脆弱区域形成为横穿整个所述凸部。

5.一种制造半导体装置的方法,包括:

用离子照射单晶半导体衬底的表面,以在所述单晶半导体衬底中形成脆弱区域;

通过将所述单晶半导体衬底的端部去除来在所述单晶半导体衬底的所述表面上形成槽;

在所述单晶半导体衬底上形成阻挡层;

在具有绝缘表面的支撑衬底上形成第一接合层;

将所述单晶半导体衬底接合到支撑衬底;

将所述单晶半导体衬底与所述支撑衬底分离,以允许将所述第一接合层、所述阻挡层、以及与被夹在所述阻挡层和所述脆弱区域之间区域对应的所述单晶半导体衬底的薄层转置到所述支撑衬底上;以及

将激光束照射在所述单晶半导体衬底的薄层上。

6.如权利要求1、2、4和5中任一所述的方法,

其中所述阻挡层包括选自氮化硅、氮氧化硅、氮化铝及氮氧化铝的材料。

7.如权利要求1、2、4和5中任一所述的方法,

其中所述脆弱区域形成在深度比所述槽的深度深的区域中。

8.如权利要求1、2、4和5中任一所述的方法,

其中所述单晶半导体衬底的所述薄层的厚度大于等于10nm且小于等于200nm。

9.如权利要求4和5中任一所述的方法,进一步包括在所述阻挡层上形成第二结合层的步骤,

其中所述第二接合层的形成是在将所述单晶半导体衬底接合到所述支撑衬底之前进行的。

10.一种通过如权利要求1、2、4、5中任一所述的方法制造的SOI衬底。

11.如权利要求10所述的SOI衬底,

其中所述阻挡层包括选自氮化硅、氮氧化硅、氮化铝及氮氧化铝的材料。

12.如权利要求10所述的SOI衬底,

其中所述单晶半导体衬底的薄层的厚度大于等于10nm且小于等于200nm。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007-127270 | 2007-05-11 | ||

| JP2007127270 | 2007-05-11 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101303967A CN101303967A (zh) | 2008-11-12 |

| CN101303967B true CN101303967B (zh) | 2012-05-30 |

Family

ID=39969907

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2008100907193A Expired - Fee Related CN101303967B (zh) | 2007-05-11 | 2008-03-31 | 半导体装置的制造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (3) | US7601601B2 (zh) |

| JP (1) | JP5348939B2 (zh) |

| KR (1) | KR101443580B1 (zh) |

| CN (1) | CN101303967B (zh) |

| TW (1) | TWI455245B (zh) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5507063B2 (ja) | 2007-07-09 | 2014-05-28 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8101501B2 (en) * | 2007-10-10 | 2012-01-24 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing semiconductor device |

| JP2010114409A (ja) * | 2008-10-10 | 2010-05-20 | Sony Corp | Soi基板とその製造方法、固体撮像装置とその製造方法、および撮像装置 |

| JP5618521B2 (ja) * | 2008-11-28 | 2014-11-05 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| TWI607670B (zh) * | 2009-01-08 | 2017-12-01 | 半導體能源研究所股份有限公司 | 發光裝置及電子裝置 |

| JP2010161671A (ja) * | 2009-01-09 | 2010-07-22 | Murata Mfg Co Ltd | 圧電デバイスの製造方法 |

| JP5607399B2 (ja) * | 2009-03-24 | 2014-10-15 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| US8043938B2 (en) * | 2009-05-14 | 2011-10-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing SOI substrate and SOI substrate |

| GB0914251D0 (en) | 2009-08-14 | 2009-09-30 | Nat Univ Ireland Cork | A hybrid substrate |

| JP5866088B2 (ja) * | 2009-11-24 | 2016-02-17 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| JP5926887B2 (ja) * | 2010-02-03 | 2016-05-25 | 株式会社半導体エネルギー研究所 | Soi基板の作製方法 |

| JP5355618B2 (ja) * | 2011-03-10 | 2013-11-27 | 三星ディスプレイ株式會社 | 可撓性表示装置及びこの製造方法 |

| JP6040609B2 (ja) * | 2012-07-20 | 2016-12-07 | 東京エレクトロン株式会社 | 成膜装置及び成膜方法 |

| KR102007834B1 (ko) * | 2013-06-27 | 2019-08-07 | 엘지디스플레이 주식회사 | 가요성 표시장치의 제조방법 |

| US10510560B2 (en) * | 2015-09-04 | 2019-12-17 | Nanyang Technological University | Method of encapsulating a substrate |

| CN108417523B (zh) * | 2018-04-16 | 2020-08-04 | 歌尔股份有限公司 | Led衬底的剥离方法 |

| CN108493106B (zh) * | 2018-05-15 | 2020-10-02 | 浙江蓝晶芯微电子有限公司 | 一种半导体晶圆刻蚀方法 |

| US11050012B2 (en) * | 2019-04-01 | 2021-06-29 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method to protect electrodes from oxidation in a MEMS device |

| US11728199B2 (en) * | 2019-12-23 | 2023-08-15 | Asmpt Nexx, Inc. | Substrate support features and method of application |

| CN111106029B (zh) * | 2019-12-31 | 2023-02-10 | 深圳市锐骏半导体股份有限公司 | 一种晶圆快速热处理机台的监控方法 |

| CN111366618B (zh) * | 2020-04-01 | 2022-07-29 | 上海华虹宏力半导体制造有限公司 | 一种温湿度传感器及其制造方法 |

| KR20230154933A (ko) * | 2021-03-09 | 2023-11-09 | 도쿄엘렉트론가부시키가이샤 | 반도체 칩의 제조 방법 및 기판 처리 장치 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1200560A (zh) * | 1997-03-26 | 1998-12-02 | 佳能株式会社 | 半导体衬底及其制作方法 |

| CN1272684A (zh) * | 1999-02-02 | 2000-11-08 | 佳能株式会社 | 衬底及其制造方法 |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0254532A (ja) * | 1988-08-17 | 1990-02-23 | Sony Corp | Soi基板の製造方法 |

| US5347154A (en) * | 1990-11-15 | 1994-09-13 | Seiko Instruments Inc. | Light valve device using semiconductive composite substrate |

| TW211621B (zh) * | 1991-07-31 | 1993-08-21 | Canon Kk | |

| FR2681472B1 (fr) * | 1991-09-18 | 1993-10-29 | Commissariat Energie Atomique | Procede de fabrication de films minces de materiau semiconducteur. |

| EP1043768B1 (en) * | 1992-01-30 | 2004-09-08 | Canon Kabushiki Kaisha | Process for producing semiconductor substrates |

| JP3237888B2 (ja) * | 1992-01-31 | 2001-12-10 | キヤノン株式会社 | 半導体基体及びその作製方法 |

| TW330313B (en) * | 1993-12-28 | 1998-04-21 | Canon Kk | A semiconductor substrate and process for producing same |

| US6107213A (en) * | 1996-02-01 | 2000-08-22 | Sony Corporation | Method for making thin film semiconductor |

| US5831276A (en) * | 1995-06-07 | 1998-11-03 | Micron Technology, Inc. | Three-dimensional container diode for use with multi-state material in a non-volatile memory cell |

| JPH10284431A (ja) | 1997-04-11 | 1998-10-23 | Sharp Corp | Soi基板の製造方法 |

| US6191007B1 (en) * | 1997-04-28 | 2001-02-20 | Denso Corporation | Method for manufacturing a semiconductor substrate |

| US6534380B1 (en) | 1997-07-18 | 2003-03-18 | Denso Corporation | Semiconductor substrate and method of manufacturing the same |

| JPH1145862A (ja) * | 1997-07-24 | 1999-02-16 | Denso Corp | 半導体基板の製造方法 |

| JPH1174208A (ja) * | 1997-08-27 | 1999-03-16 | Denso Corp | 半導体基板の製造方法 |

| JPH11163363A (ja) | 1997-11-22 | 1999-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置およびその作製方法 |

| JP2000012864A (ja) * | 1998-06-22 | 2000-01-14 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法 |

| US6093623A (en) | 1998-08-04 | 2000-07-25 | Micron Technology, Inc. | Methods for making silicon-on-insulator structures |

| JP2000077287A (ja) * | 1998-08-26 | 2000-03-14 | Nissin Electric Co Ltd | 結晶薄膜基板の製造方法 |

| JP4476390B2 (ja) | 1998-09-04 | 2010-06-09 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2000124092A (ja) | 1998-10-16 | 2000-04-28 | Shin Etsu Handotai Co Ltd | 水素イオン注入剥離法によってsoiウエーハを製造する方法およびこの方法で製造されたsoiウエーハ |

| US6380019B1 (en) * | 1998-11-06 | 2002-04-30 | Advanced Micro Devices, Inc. | Method of manufacturing a transistor with local insulator structure |

| US6375738B1 (en) * | 1999-03-26 | 2002-04-23 | Canon Kabushiki Kaisha | Process of producing semiconductor article |

| JP2001015721A (ja) * | 1999-04-30 | 2001-01-19 | Canon Inc | 複合部材の分離方法及び薄膜の製造方法 |

| US20010053559A1 (en) | 2000-01-25 | 2001-12-20 | Semiconductor Energy Laboratory Co., Ltd. | Method of fabricating display device |

| US6583440B2 (en) | 2000-11-30 | 2003-06-24 | Seiko Epson Corporation | Soi substrate, element substrate, semiconductor device, electro-optical apparatus, electronic equipment, method of manufacturing the soi substrate, method of manufacturing the element substrate, and method of manufacturing the electro-optical apparatus |

| JP4507395B2 (ja) * | 2000-11-30 | 2010-07-21 | セイコーエプソン株式会社 | 電気光学装置用素子基板の製造方法 |

| US6601783B2 (en) * | 2001-04-25 | 2003-08-05 | Dennis Chisum | Abrasivejet nozzle and insert therefor |