JP5331371B2 - 電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 - Google Patents

電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 Download PDFInfo

- Publication number

- JP5331371B2 JP5331371B2 JP2008110463A JP2008110463A JP5331371B2 JP 5331371 B2 JP5331371 B2 JP 5331371B2 JP 2008110463 A JP2008110463 A JP 2008110463A JP 2008110463 A JP2008110463 A JP 2008110463A JP 5331371 B2 JP5331371 B2 JP 5331371B2

- Authority

- JP

- Japan

- Prior art keywords

- external connection

- land

- electronic component

- circuit board

- solder ball

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01R—ELECTRICALLY-CONDUCTIVE CONNECTIONS; STRUCTURAL ASSOCIATIONS OF A PLURALITY OF MUTUALLY-INSULATED ELECTRICAL CONNECTING ELEMENTS; COUPLING DEVICES; CURRENT COLLECTORS

- H01R43/00—Apparatus or processes specially adapted for manufacturing, assembling, maintaining, or repairing of line connectors or current collectors or for joining electric conductors

- H01R43/02—Apparatus or processes specially adapted for manufacturing, assembling, maintaining, or repairing of line connectors or current collectors or for joining electric conductors for soldered or welded connections

- H01R43/0256—Apparatus or processes specially adapted for manufacturing, assembling, maintaining, or repairing of line connectors or current collectors or for joining electric conductors for soldered or welded connections for soldering or welding connectors to a printed circuit board

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

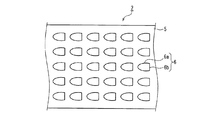

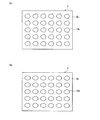

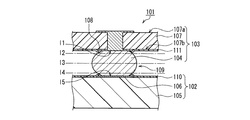

- H05K1/111—Pads for surface mounting, e.g. lay-out

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/341—Surface mounted components

- H05K3/3431—Leadless components

- H05K3/3436—Leadless components having an array of bottom contacts, e.g. pad grid array or ball grid array components

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/30—Assembling printed circuits with electric components, e.g. with resistor

- H05K3/32—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits

- H05K3/34—Assembling printed circuits with electric components, e.g. with resistor electrically connecting electric components or wires to printed circuits by soldering

- H05K3/3452—Solder masks

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01N—INVESTIGATING OR ANALYSING MATERIALS BY DETERMINING THEIR CHEMICAL OR PHYSICAL PROPERTIES

- G01N2223/00—Investigating materials by wave or particle radiation

- G01N2223/60—Specific applications or type of materials

- G01N2223/611—Specific applications or type of materials patterned objects; electronic devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0556—Disposition

- H01L2224/05568—Disposition the whole external layer protruding from the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/05573—Single external layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09209—Shape and layout details of conductors

- H05K2201/09372—Pads and lands

- H05K2201/09381—Shape of non-curved single flat metallic pad, land or exposed part thereof; Shape of electrode of leadless component

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/0989—Coating free areas, e.g. areas other than pads or lands free of solder resist

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/09—Shape and layout

- H05K2201/09818—Shape or layout details not covered by a single group of H05K2201/09009 - H05K2201/09809

- H05K2201/099—Coating over pads, e.g. solder resist partly over pads

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/10—Details of components or other objects attached to or integrated in a printed circuit board

- H05K2201/10613—Details of electrical connections of non-printed components, e.g. special leads

- H05K2201/10621—Components characterised by their electrical contacts

- H05K2201/10734—Ball grid array [BGA]; Bump grid array

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008110463A JP5331371B2 (ja) | 2007-04-24 | 2008-04-21 | 電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007113721 | 2007-04-24 | ||

| JP2007113721 | 2007-04-24 | ||

| JP2008058263 | 2008-03-07 | ||

| JP2008058263 | 2008-03-07 | ||

| JP2008110463A JP5331371B2 (ja) | 2007-04-24 | 2008-04-21 | 電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009239239A JP2009239239A (ja) | 2009-10-15 |

| JP2009239239A5 JP2009239239A5 (enExample) | 2011-05-12 |

| JP5331371B2 true JP5331371B2 (ja) | 2013-10-30 |

Family

ID=39886707

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008110463A Expired - Fee Related JP5331371B2 (ja) | 2007-04-24 | 2008-04-21 | 電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8233288B2 (enExample) |

| JP (1) | JP5331371B2 (enExample) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5473666B2 (ja) * | 2010-02-19 | 2014-04-16 | 三菱電機株式会社 | X線検査方法及びx線検査装置 |

| JP6468054B2 (ja) * | 2015-04-28 | 2019-02-13 | 富士通株式会社 | プリント基板及びシールド板金固定方法 |

| JP6436141B2 (ja) * | 2016-09-20 | 2018-12-12 | オムロン株式会社 | X線検査装置およびその制御方法 |

| KR102678759B1 (ko) | 2016-10-14 | 2024-06-27 | 삼성전자주식회사 | 반도체 소자 |

| WO2025115431A1 (ja) * | 2023-11-30 | 2025-06-05 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及び電子機器 |

| KR102872674B1 (ko) * | 2024-10-18 | 2025-10-17 | 테크밸리 주식회사 | 엑스레이 이미지를 통한 bga불량 검출방법 및 이를 위한 분석시스템 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2932964B2 (ja) | 1995-03-30 | 1999-08-09 | 松下電器産業株式会社 | チップキャリアとその実装体 |

| JPH10335796A (ja) | 1997-05-29 | 1998-12-18 | Canon Inc | 回路基板と電子回路装置、及びその製造方法、及びその接合部の検査方法 |

| JPH11297889A (ja) | 1998-04-16 | 1999-10-29 | Sony Corp | 半導体パッケージおよび実装基板、ならびにこれらを用いた実装方法 |

| US6518675B2 (en) * | 2000-12-29 | 2003-02-11 | Samsung Electronics Co., Ltd. | Wafer level package and method for manufacturing the same |

| JP3860000B2 (ja) * | 2001-09-07 | 2006-12-20 | Necエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP3857103B2 (ja) * | 2001-10-22 | 2006-12-13 | 京セラ株式会社 | 配線基板 |

| TW591981B (en) | 2002-05-17 | 2004-06-11 | Nec Corp | Printed wiring board |

| JP2004311535A (ja) * | 2003-04-03 | 2004-11-04 | Matsushita Electric Ind Co Ltd | チップサイズパッケージ半導体装置 |

| JP2006024858A (ja) | 2004-07-09 | 2006-01-26 | Audio Technica Corp | プリント配線板の製造方法およびプリント配線板 |

| JP2006041167A (ja) * | 2004-07-27 | 2006-02-09 | Matsushita Electric Ind Co Ltd | 半導体装置の検査方法および検査装置 |

| JP4910378B2 (ja) * | 2005-03-01 | 2012-04-04 | 株式会社デンソー | X線検査装置及びx線検査方法 |

| JP2007005452A (ja) | 2005-06-22 | 2007-01-11 | Renesas Technology Corp | 半導体装置 |

-

2008

- 2008-04-21 JP JP2008110463A patent/JP5331371B2/ja not_active Expired - Fee Related

- 2008-04-22 US US12/107,454 patent/US8233288B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US8233288B2 (en) | 2012-07-31 |

| JP2009239239A (ja) | 2009-10-15 |

| US20080266825A1 (en) | 2008-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6734557B2 (en) | Semiconductor device | |

| JP5107959B2 (ja) | 基板 | |

| JP5331371B2 (ja) | 電子部品パッケージ、回路基板、電子部品実装装置、およびそれらの接合部の検査方法 | |

| US20130119012A1 (en) | Interconnection element for electric circuits | |

| JP2009239239A5 (enExample) | ||

| CN102163581B (zh) | 半导体模块 | |

| WO2012035688A1 (ja) | 半導体装置、半導体装置ユニット、および半導体装置の製造方法 | |

| JP3613167B2 (ja) | パッド電極の接続状態の検査方法 | |

| KR20010069987A (ko) | 반도체 장치 | |

| US8716868B2 (en) | Semiconductor module for stacking and stacked semiconductor module | |

| KR100636364B1 (ko) | 플립칩 패키지의 솔더패드 접합방법 | |

| JP3601714B2 (ja) | 半導体装置及び配線基板 | |

| CN101894817B (zh) | 层叠用半导体模块及层叠型半导体模块 | |

| JP2022173486A (ja) | プリント回路板及び電子機器 | |

| JPH10335796A (ja) | 回路基板と電子回路装置、及びその製造方法、及びその接合部の検査方法 | |

| JPH1074802A (ja) | ボールグリッドアレイパッケージの接続構造及びその接続検査方法 | |

| JP2007266501A (ja) | 半導体装置の実装方法及び実装基板 | |

| JP4828139B2 (ja) | 半導体装置 | |

| JP4712426B2 (ja) | 半導体装置 | |

| US20080164054A1 (en) | Printed circuit board capable of void control during surface mounting process | |

| JP2015053390A (ja) | プリント配線板および半導体装置 | |

| JP2005217069A (ja) | 半導体装置 | |

| JP2005235854A (ja) | グリッドアレイ型電極を有する電子部品の電極構造とその実装基板 | |

| JP2003264259A (ja) | 半導体装置及びその実装方法 | |

| JP2007005495A (ja) | プリント配線板及び半導体パッケージの実装方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110329 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110329 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130618 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130701 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130729 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5331371 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |