JP5316612B2 - 炭化珪素半導体エピタキシャル基板の製造方法 - Google Patents

炭化珪素半導体エピタキシャル基板の製造方法 Download PDFInfo

- Publication number

- JP5316612B2 JP5316612B2 JP2011173502A JP2011173502A JP5316612B2 JP 5316612 B2 JP5316612 B2 JP 5316612B2 JP 2011173502 A JP2011173502 A JP 2011173502A JP 2011173502 A JP2011173502 A JP 2011173502A JP 5316612 B2 JP5316612 B2 JP 5316612B2

- Authority

- JP

- Japan

- Prior art keywords

- epitaxial layer

- silicon carbide

- point defect

- density

- center

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Crystals, And After-Treatments Of Crystals (AREA)

- Chemical Vapour Deposition (AREA)

Description

より、基板上にエピタキシャル層を成長させる。

コンの位置に収まったアンチサイト欠陥が組み合わさったもの)として存在することもあ

る。

させることが好ましい。

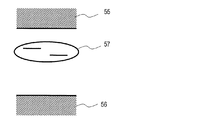

素半導体層には、1013cm-3程度の点欠陥が存在している。半導体層中に点欠陥が存在すると、図9に示すように、伝導帯55と価電子帯56との間の本来準位が存在しない禁制帯に、準位57が発生する。これを一般的に「深い準位(deep level)」と呼ぶ。こうした点欠陥による準位は、点欠陥の種類などによって異なるエネルギーを持つ。半導体中の深い準位は、バイポーラデバイスの伝導度変調の効果を低減させ、この結果、バイポーラデバイスの順方向の抵抗が増加するといった悪影響を及ぼすと考えられる。また、逆方向の漏れ電流を増加させるといった問題点も指摘されている。

H6/7センターの密度が5×1011cm-3以下となる成長条件で前記エピタキシャル層を

成長させる。

タキシャル層中において、前記ΔEaが1.33ev以上1.53eV以下の準位を持つ点欠陥の密度が前記熱処理を行う前の1/2以下となる条件で前記エピタキシャル層を熱処理する。

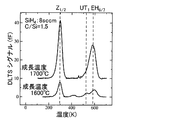

センターおよび点欠陥EH6/7センターに基づく強いピークが観測される。ここで、点欠

陥は、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差ΔEaで示されるエネルギー準位を有し、通常、発見者等にちなんだ名称がつけられる。DLTSのグラフでは、

ΔEaに対応する温度において、その点欠陥に対応するピークが観測される。点欠陥Z1/2センターは、Z1センターおよびZ2センターを含む総称である。Z1センターおよびZ2

センターに帰属するピークは近接しており、また、Z2センターのピークは小さい。この

ため、通常、2つのピークは分離して観測されない。EH6/7センターも同様である。

のピークに帰属する点欠陥はこれまで報告されておらず、本願発明者が発見した。以下、このピークに由来する点欠陥をUT1(Unknown Trap 1)センターと称する。

H6/7センターは、炭化珪素半導体の伝導帯下端からそれぞれ0.57eVおよび1.6

5eVの活性化エネルギー差を有する準位に位置している。また、本願発明者が発見した点欠陥UT1センターは1.33eVから1.53eVの準位を有し、典型的には1.4

3eVのエネルギー準位を有していることが分かった。

ーおよび点欠陥UT1センターによる準位は、禁制帯のほぼ中間に位置する。このため、

点欠陥EH6/7センターおよび点欠陥UT1センターは、キャリアが禁制帯を超えて再結合する原因となりやすい。したがって、発見した点欠陥UT1の密度も低減しなければ、良

好な品位を有する炭化珪素半導体エピタキシャル基板は得られない。

ターは、生成したエピタキシャル層を熱処理することによって、低減できることが分かった。また、エピタキシャル層の点欠陥の密度はエピタキシャル層を生成する際の原料比にも依存することが分かった。

低減できることが分かった。これにより、点欠陥密度が小さく、良好な品質のエピタキシャル層を有する炭化珪素半導体エピタキシャル基板が得られる。

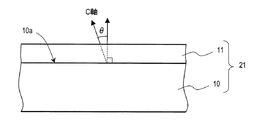

いる。

H4ガスを8sccmの流量で炉内に導入し、エピタキシャル層11を成長させた。図4

に示すように、1700℃でエピタキシャル層11を形成した場合、点欠陥Z1/2センタ

ー、点欠陥EH6/7センターおよび点欠陥UT1センターの密度は、それぞれ約1×1013cm-3、約5×1012cm-3および約6×1012cm-3である。これに対し、1600℃でエピタキシャル層11を形成した場合、点欠陥Z1/2センター、点欠陥EH6/7センターおよび点欠陥UT1センターの密度は、それぞれ約1×1012cm-3、約5×1011cm-3および約3×1011cm-3であり、点欠陥Z1/2センターおよび点欠陥EH6/7センター

の密度は、1700℃で成長させた場合に比べて1/10程度になっている。

いて説明するように、点欠陥UT1センターは熱処理によって減少させることができるた

め、点欠陥Z1/2センターおよび点欠陥EH6/7センターの密度ができるだけ小さくなるように、C/Si比は大きい方が好ましい。具体的には、C/Si比は1.5以上2以下であることが好ましい。C/Si比が1.5より小さい場合、点欠陥Z1/2センターおよび

点欠陥EH6/7センターの密度の低減が十分ではない。また、C/Si比が2より大きい

場合、エピタキシャル層を形成するのが困難となる。C/Si比は1.5以上である場合、点欠陥Z1/2センターおよび点欠陥EH6/7センターの密度を、1700℃でエピタキシャル層を成長させた場合に比べて1/10以下にすることができる。このとき、点欠陥UT1センターの密度は、点欠陥Z1/2センターおよび点欠陥EH6/7センターの密度とトレ

ードオフの関係にあるため、3×1011cm-3以上になる。

がある。

、点欠陥Z1/2センターおよび点欠陥EH6/7センターに帰属するピークの強度が、図1に示すグラフに比べて大きく低下している。また、図1に示す1700℃で成長したエピタキシャル層には見られなかった点欠陥UT1センターに帰属する強いピークが観測される

。

しくは、3×1011cm-3以下となるように、温度および時間を調整することが好ましい。

タキシャル層11に新たな面欠陥が生じるため、好ましくない。一方、熱処理温度が1300℃よりも低いと点欠陥UT1センターを低減させる効果があまり得られず、長時間熱

処理を行っても点欠陥UT1センターの密度が3×1011cm-3以下にはならない。

減少させるための熱処理を行ってもエピタキシャル層11の表面モフォロジーが悪化することはない。

理することはない。このため、半導体素子を形成する際に用いられる半導体プロセスのいずれかの工程を上述の熱処理工程と兼ねることはできない。また、半導体素子を形成する際に用いられる半導体プロセスによっては、点欠陥UT1センターの密度を低減させる効

果はほとんど得られない。

×1011cm-3程度に大きく減少している。これに対し、点欠陥Z1/2センターおよび点

欠陥EH6/7センターの密度も減少はするが、点欠陥UT1センターほど大きく欠陥密度が減少する効果は得られない。

11 エピタキシャル層

21 炭化珪素半導体エピタキシャル基板

Claims (5)

- オフセット角が2°以上10°以下である4H炭化珪素単結晶基板を用意する工程と、

化学気相堆積法により、1400℃以上1650℃以下の温度で、炭化珪素からなるエピタキシャル層を前記炭化珪素単結晶基板上に成長させる工程と、

前記エピタキシャル層を1300℃以上1800℃以下の温度で熱処理する工程と、

を包含し、

前記エピタキシャル層を成長させる工程において、原料ガス中の炭素原子の珪素原子に対する比C/Siは1.5以上2以下であり、

前記エピタキシャル層を成長させる工程を、3kPa以上54kPa以下の圧力で行い、

前記エピタキシャル層を成長させる工程は、前記エピタキシャル層中の点欠陥Z 1/2 センターの密度が1×10 12 cm -3 以下であり、点欠陥EH 6/7 センターの密度が5×10 11 cm -3 以下となる成長条件で前記エピタキシャル層を成長させ、

前記エピタキシャル層を10μm/h以上、23μm/h以下の速度で成長させる、炭化珪素半導体エピタキシャル基板の製造方法。 - 前記エピタキシャル層を成長させる工程において成長するエピタキシャル層は、深い準位過渡分光法において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差ΔEaが1.33ev以上1.53eV以下である準位のピークが、点欠陥EH6/7センターのピークから分離して観測される請求項1に記載の炭化珪素半導体エピタキシャル基板の製造方法。

- 前記エピタキシャル層を成長させる工程は、前記エピタキシャル層中において、炭化珪素半導体の伝導帯の下端からの活性化エネルギー差ΔEaが1.33ev以上1.53eV以下の準位を持つ点欠陥の密度が3×1011cm-3以上となる成長条件で前記エピタキシャル層を成長させる請求項2に記載の炭化珪素半導体エピタキシャル基板の製造方法。

- 前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層中において、前記ΔEaが1.33ev以上1.53eV以下の準位を持つ点欠陥の密度が前記熱処理を行う前の1/2以下となる条件で前記エピタキシャル層を熱処理する請求項1に記載の炭化珪素半導体エピタキシャル基板の製造方法。

- 前記エピタキシャル層を熱処理する工程は、前記エピタキシャル層中において、前記1.33ev以上1.53eV以下の準位を持つ点欠陥の密度が3×1011cm-3以下となる条件で前記エピタキシャル層を熱処理する請求項4に記載の炭化珪素半導体エピタキシャル基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011173502A JP5316612B2 (ja) | 2011-08-09 | 2011-08-09 | 炭化珪素半導体エピタキシャル基板の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011173502A JP5316612B2 (ja) | 2011-08-09 | 2011-08-09 | 炭化珪素半導体エピタキシャル基板の製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006226368A Division JP4946264B2 (ja) | 2006-08-23 | 2006-08-23 | 炭化珪素半導体エピタキシャル基板の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011233932A JP2011233932A (ja) | 2011-11-17 |

| JP2011233932A5 JP2011233932A5 (ja) | 2012-03-01 |

| JP5316612B2 true JP5316612B2 (ja) | 2013-10-16 |

Family

ID=45322866

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011173502A Active JP5316612B2 (ja) | 2011-08-09 | 2011-08-09 | 炭化珪素半導体エピタキシャル基板の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5316612B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5189156B2 (ja) * | 2010-11-29 | 2013-04-24 | 株式会社豊田中央研究所 | SiC単結晶の製造方法 |

| US8860040B2 (en) | 2012-09-11 | 2014-10-14 | Dow Corning Corporation | High voltage power semiconductor devices on SiC |

| US9018639B2 (en) | 2012-10-26 | 2015-04-28 | Dow Corning Corporation | Flat SiC semiconductor substrate |

| KR102119755B1 (ko) * | 2012-11-30 | 2020-06-08 | 엘지이노텍 주식회사 | 에피택셜 웨이퍼 및 그 제조 방법 |

| KR102053077B1 (ko) * | 2012-11-30 | 2020-01-08 | 엘지이노텍 주식회사 | 에피택셜 웨이퍼 및 그 제조 방법 |

| WO2014084550A1 (ko) | 2012-11-30 | 2014-06-05 | 엘지이노텍 주식회사 | 에피택셜 웨이퍼, 이를 이용한 스위치 소자 및 발광 소자 |

| KR102098209B1 (ko) * | 2013-02-05 | 2020-04-08 | 엘지이노텍 주식회사 | 에피택셜 웨이퍼 및 그 제조 방법 |

| US9797064B2 (en) | 2013-02-05 | 2017-10-24 | Dow Corning Corporation | Method for growing a SiC crystal by vapor deposition onto a seed crystal provided on a support shelf which permits thermal expansion |

| US9738991B2 (en) | 2013-02-05 | 2017-08-22 | Dow Corning Corporation | Method for growing a SiC crystal by vapor deposition onto a seed crystal provided on a supporting shelf which permits thermal expansion |

| US9017804B2 (en) | 2013-02-05 | 2015-04-28 | Dow Corning Corporation | Method to reduce dislocations in SiC crystal growth |

| US8940614B2 (en) | 2013-03-15 | 2015-01-27 | Dow Corning Corporation | SiC substrate with SiC epitaxial film |

| US9279192B2 (en) | 2014-07-29 | 2016-03-08 | Dow Corning Corporation | Method for manufacturing SiC wafer fit for integration with power device manufacturing technology |

| JP6624868B2 (ja) * | 2015-09-29 | 2019-12-25 | 昭和電工株式会社 | p型低抵抗率炭化珪素単結晶基板 |

| FR3108774B1 (fr) * | 2020-03-27 | 2022-02-18 | Soitec Silicon On Insulator | Procede de fabrication d’une structure composite comprenant une couche mince en sic monocristallin sur un substrat support en sic |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3508519B2 (ja) * | 1997-11-28 | 2004-03-22 | 松下電器産業株式会社 | エピタキシャル成長装置およびエピタキシャル成長法 |

| JP2003234301A (ja) * | 2001-10-25 | 2003-08-22 | Matsushita Electric Ind Co Ltd | 半導体基板、半導体素子及びその製造方法 |

-

2011

- 2011-08-09 JP JP2011173502A patent/JP5316612B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011233932A (ja) | 2011-11-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5316612B2 (ja) | 炭化珪素半導体エピタキシャル基板の製造方法 | |

| JP4946264B2 (ja) | 炭化珪素半導体エピタキシャル基板の製造方法 | |

| CN102822396B (zh) | 外延碳化硅单晶基板的制造方法及根据该方法得到的外延碳化硅单晶基板 | |

| JP5706823B2 (ja) | SiC単結晶ウエハーとその製造方法 | |

| JP4946202B2 (ja) | 炭化珪素半導体エピタキシャル基板の製造方法。 | |

| WO2005093796A1 (ja) | バイポーラ型半導体装置およびその製造方法 | |

| JP5285202B2 (ja) | バイポーラ型半導体装置およびその製造方法 | |

| JPWO2003078702A1 (ja) | SiC結晶の製造方法およびSiC結晶 | |

| JP6264768B2 (ja) | 半導体構造物、半導体装置及び該半導体構造物の製造方法 | |

| WO2015064256A1 (ja) | 炭化シリコン半導体装置及びその製造方法 | |

| JP6891758B2 (ja) | 炭化珪素エピタキシャル基板及び炭化珪素半導体装置の製造方法 | |

| JP6624868B2 (ja) | p型低抵抗率炭化珪素単結晶基板 | |

| JP2017065986A (ja) | 低抵抗率炭化珪素単結晶基板の製造方法 | |

| JP2008091656A (ja) | 炭化珪素半導体装置の製造方法および炭化珪素半導体装置 | |

| KR20240069717A (ko) | 헤테로 에피택셜 웨이퍼의 제조방법 | |

| CN106169497B (zh) | 碳化硅基板以及碳化硅基板的制造方法 | |

| CN102560673A (zh) | 提高碳化硅材料载流子寿命的方法 | |

| WO2015159949A1 (ja) | 炭化珪素エピタキシャルウエハおよびその製造方法 | |

| JP2014027028A (ja) | SiCエピタキシャル基板製造装置、SiCエピタキシャル基板の製造方法、SiCエピタキシャル基板 | |

| WO2015097852A1 (ja) | 単結晶SiCエピタキシャル膜の形成方法 | |

| CN105140106B (zh) | 一种在零偏角衬底上外延碳化硅的方法 | |

| EP4653588A1 (en) | Method for manufacturing 3c-sic single-crystal epitaxial substrate, method for manufacturing 3c-sic free-standing substrate, and 3c-sic single-crystal epitaxial substrate | |

| JP7708198B2 (ja) | ヘテロエピタキシャル膜の作製方法 | |

| CN114975097B (zh) | 一种碳化硅晶体及其制备方法与应用 | |

| JP2025099753A (ja) | ヘテロエピタキシャルウェーハの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120118 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130326 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130523 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130611 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130624 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5316612 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |