JP5287508B2 - 信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 - Google Patents

信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 Download PDFInfo

- Publication number

- JP5287508B2 JP5287508B2 JP2009128702A JP2009128702A JP5287508B2 JP 5287508 B2 JP5287508 B2 JP 5287508B2 JP 2009128702 A JP2009128702 A JP 2009128702A JP 2009128702 A JP2009128702 A JP 2009128702A JP 5287508 B2 JP5287508 B2 JP 5287508B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- switching

- signal processing

- switches

- end circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000000034 method Methods 0.000 title claims description 10

- 230000007704 transition Effects 0.000 claims description 46

- 239000003990 capacitor Substances 0.000 claims description 35

- 230000000295 complement effect Effects 0.000 claims description 8

- 230000005540 biological transmission Effects 0.000 claims description 7

- 230000001629 suppression Effects 0.000 claims description 6

- 230000005669 field effect Effects 0.000 claims description 5

- 230000008569 process Effects 0.000 claims description 2

- 230000008054 signal transmission Effects 0.000 claims 2

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 claims 1

- 230000008859 change Effects 0.000 description 28

- 238000010586 diagram Methods 0.000 description 9

- 239000004065 semiconductor Substances 0.000 description 6

- 230000006866 deterioration Effects 0.000 description 5

- 238000002955 isolation Methods 0.000 description 5

- 230000005577 local transmission Effects 0.000 description 5

- 238000007599 discharging Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000002411 adverse Effects 0.000 description 1

- 230000003321 amplification Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 238000006731 degradation reaction Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002194 synthesizing effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/44—Receiver circuitry for the reception of television signals according to analogue transmission standards

- H04N5/50—Tuning indicators; Automatic tuning control

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03J—TUNING RESONANT CIRCUITS; SELECTING RESONANT CIRCUITS

- H03J1/00—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general

- H03J1/0008—Details of adjusting, driving, indicating, or mechanical control arrangements for resonant circuits in general using a central processing unit, e.g. a microprocessor

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03J—TUNING RESONANT CIRCUITS; SELECTING RESONANT CIRCUITS

- H03J5/00—Discontinuous tuning; Selecting predetermined frequencies; Selecting frequency bands with or without continuous tuning in one or more of the bands, e.g. push-button tuning, turret tuner

- H03J5/24—Discontinuous tuning; Selecting predetermined frequencies; Selecting frequency bands with or without continuous tuning in one or more of the bands, e.g. push-button tuning, turret tuner with a number of separate pretuned tuning circuits or separate tuning elements selectively brought into circuit, e.g. for waveband selection or for television channel selection

- H03J5/242—Discontinuous tuning; Selecting predetermined frequencies; Selecting frequency bands with or without continuous tuning in one or more of the bands, e.g. push-button tuning, turret tuner with a number of separate pretuned tuning circuits or separate tuning elements selectively brought into circuit, e.g. for waveband selection or for television channel selection used exclusively for band selection

- H03J5/244—Discontinuous tuning; Selecting predetermined frequencies; Selecting frequency bands with or without continuous tuning in one or more of the bands, e.g. push-button tuning, turret tuner with a number of separate pretuned tuning circuits or separate tuning elements selectively brought into circuit, e.g. for waveband selection or for television channel selection used exclusively for band selection using electronic means

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N21/00—Selective content distribution, e.g. interactive television or video on demand [VOD]

- H04N21/40—Client devices specifically adapted for the reception of or interaction with content, e.g. set-top-box [STB]; Operations thereof

- H04N21/41—Structure of client; Structure of client peripherals

- H04N21/426—Internal components of the client ; Characteristics thereof

- H04N21/42607—Internal components of the client ; Characteristics thereof for processing the incoming bitstream

- H04N21/4263—Internal components of the client ; Characteristics thereof for processing the incoming bitstream involving specific tuning arrangements, e.g. two tuners

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/44—Receiver circuitry for the reception of television signals according to analogue transmission standards

- H04N5/455—Demodulation-circuits

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Input Circuits Of Receivers And Coupling Of Receivers And Audio Equipment (AREA)

Description

(A)46〜147MHz(VLバンド)

(B)147〜401MHz(VHバンド)

(C)401〜887MHz(Uバンド)

の3バンドに分割し、ユーザのチャンネル選択操作に応じて、受信バンドを切り替えるようにしたフロントエンド回路が提供されている。

(2)第1のチューナ231と第2のチューナ232のいずれか一方の映像出力信号を表示装置部26に出力し、他方を記録再生装置部27に出力する第2の出力モード。

(3)第1のチューナ231および第2のチューナ232の映像出力信号を合成し、その合成した映像出力信号を表示装置部26に供給する第3の出力モード。

入力信号を、複数の出力端に分配して出力する信号分配手段と、

前記信号分配手段の前記複数の出力端のそれぞれに接続される信号処理部の複数個と、

前記複数個の信号処理部の少なくとも一つに設けられ、前記信号分配手段からの信号の伝送路をオン・オフする1または複数の信号用スイッチと、

前記1または複数の信号用スイッチの切替信号を発生する切替信号発生部と、

前記切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられたときに、前記1または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える信号処理装置を提供する。

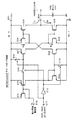

図1は、この発明による信号処理装置の第1の実施形態としてのテレビ受信機の構成例を示すブロックである。この図1の例は、前述した図14を用いて説明したテレビ受信機に、この発明の第1の実施形態を適用したもので、図14の例と同一部分には、同一参照符号を付して、その説明を省略する。

遷移補正回路31,32は、制御部20から受ける制御信号が、第1の制御信号EN1,第2の制御信号EN2というように異なるのみで、同様の構成を備える。

第1の実施形態では、チューナ231および232の信号入力側にインピーダンス遷移補正回路を設けるようにした。これに対して、第2の実施形態は、信号路中にインピーダンス遷移補正回路のような補正回路を設けることなく、バンド切替スイッチおよび当該バンド切替用スイッチに供給する切替信号のステップ状の急峻な変化を、急峻でない変化に抑制する構成とする。

第3の実施形態は、第2の実施形態の変形例である。第2の実施形態では、フロントエンド回路のバンド切替スイッチおよびその切替信号の制御回路40においては、時定数回路を備える切替信号補正回路43A,43B,43Cを用いた。

以上説明したように、上述の実施形態によれば、図11および図12に示したように、チューナ231,232において、バンド切り替えをした時に遷移する入力インピーダンスが、ステップ状の急峻な遷移ではなく、連続的で緩やかな遷移特性となる。

信号用スイッチ42A,42B,42Cに供給するバンド切替信号SW1,SW2,SW3をステップ状のものから、連続的で緩やかな変化するものに抑制する切替信号補正回路としては、上述の実施形態に限られるものではない。

Claims (20)

- 入力信号を、複数の出力端に分配して出力する信号分配手段と、

前記信号分配手段の前記複数の出力端のそれぞれに接続される信号処理部の複数個と、

前記複数個の信号処理部の少なくとも一つに設けられ、前記信号分配手段からの信号の伝送路をオン・オフする1または複数の信号用スイッチと、

前記1または複数の信号用スイッチの切替信号を発生する切替信号発生部と、

前記切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられたときに、前記1または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える信号処理装置。 - 請求項1に記載の信号処理装置において、

前記抑制手段は、前記信号分配手段と前記信号処理部との間の信号伝送路に設けられるインピーダンス遷移補正回路からなり、

前記インピーダンス遷移補正回路は、前記切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられるときに、前記信号処理部の入力インピーダンスが、急峻でない遷移をするように制御される

信号処理装置。 - 請求項1に記載の信号処理装置において、

前記抑制手段は、前記切替信号発生部からの急峻な遷移の前記切替信号を、急峻でない遷移をする切替信号に抑制して前記信号処理部の前記1または複数の信号用スイッチに供給する切替信号補正手段からなる

信号処理装置。 - 請求項3に記載の信号処理装置において、

前記切替信号補正手段は、前記切替信号の前記1または複数の信号用スイッチへの信号路に設けられる時定数回路からなる

信号処理装置。 - 請求項3に記載の信号処理装置において、

前記切替信号補正手段は、キャパシタ素子と、前記切替信号に基づいて駆動され、前記キャパシタ素子への充放電を行うチャージポンプ回路とから構成される

信号処理装置。 - 請求項5に記載の信号処理装置において、

前記切替信号補正手段を構成するチャージポンプ回路は、微小電流発生源から供給される微小電流を元に動作する

信号処理装置。 - 請求項6に記載の信号処理装置において、

前記微小電流発生源は、前記入力インピーダンスの遷移特性を可変するために、発生する前記微小電流を可変にする電流調節機能を備える

信号処理装置。 - 請求項3乃至請求項7のいずれかに記載の信号処理装置において、

前記1または複数の信号用スイッチは、電界効果トランジスタで構成されると共に、ゲート制御端子とドレイン制御端子とを備え、

前記切替信号補正手段は、前記切替信号に基づき、前記ゲート制御端子と前記ドレイン制御端子とに相補的な制御電位を与えることで、前記1または複数の信号用スイッチをオン・オフする

信号処理装置。 - 請求項1〜8のいずれかに記載の信号処理装置は、放送信号の受信装置であって、

前記複数個の信号処理部はチューナのフロントエンド回路であって、前記信号用スイッチが設けられるフロントエンド回路は、受信信号の周波数帯域を複数に分割して、各分割周波数帯域毎に処理するようにするものであり、

前記信号分配手段は、受信した放送信号を、複数個のチューナのフロントエンド回路に分配して供給するものであり、

前記信号用スイッチは、前記信号分配手段からの受信信号の前記複数の周波数帯域のうちの前記信号処理部で処理する分割周波数帯域を選択するためのスイッチであり、

前記切替信号は、前記チューナにおける選局チャンネルが、いずれの分割周波数帯域に含まれるかにより、前記信号処理部に対して自動的に生成されて供給される

信号処理装置。 - 受信信号が分配されて入力される複数個の信号処理部のうちの1つの信号処理部であるフロントエンド回路であって、

入力端を通じて入力される受信信号の伝送路をオン・オフする1または複数の信号用スイッチと、

切替信号により、前記1または複数の信号用スイッチが切り替えられたときに、入力インピーダンスが、急峻でない遷移をするように抑制するための抑制手段と、

を備える受信装置のフロントエンド回路。 - 請求項10に記載の受信装置のフロントエンド回路において、

前記受信信号の周波数帯域を複数に分割して、各分割周波数帯域毎に処理するようにするものであり、

前記信号用スイッチは、前記受信信号の前記複数の周波数帯域のうちで処理する分割周波数帯域を選択するためのスイッチであり、

前記切替信号は、選局チャンネルが、いずれの分割周波数帯域に含まれるかにより、前記信号処理部に対して自動的に生成されて供給される

受信装置のフロントエンド回路。 - 請求項10に記載の受信装置のフロントエンド回路において、

前記抑制手段は、急峻な遷移の前記切替信号を、急峻でない遷移をする切替信号に変更して前記1または複数の信号用スイッチに供給する切替信号補正手段からなる

受信装置のフロントエンド回路。 - 請求項12に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段は、前記切替信号の前記1または複数の信号用スイッチへの信号路に設けられる時定数回路からなる

受信装置のフロントエンド回路。 - 請求項12に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段は、キャパシタ素子と、前記切替信号に基づいて駆動され、前記キャパシタ素子への充放電を行うチャージポンプ回路とから構成される

受信装置のフロントエンド回路。 - 請求項14に記載の受信装置のフロントエンド回路において、

前記切替信号補正手段を構成するチャージポンプ回路は、微小電流発生源から供給される微小電流を元に動作する

受信装置のフロントエンド回路。 - 請求項15に記載の受信装置のフロントエンド回路において、

前記微小電流発生源は、前記入力インピーダンスの遷移特性を可変するために、発生する前記微小電流を可変にする電流調節機能を備える

受信装置のフロントエンド回路。 - 請求項12乃至請求項16のいずれかに記載の受信装置のフロントエンド回路において、

前記1または複数の信号用スイッチは、電界効果トランジスタで構成されると共に、ゲート制御端子とドレイン制御端子とを備え、

前記切替信号補正手段は、前記切替信号に基づき、前記ゲート制御端子と前記ドレイン制御端子とに相補的な制御電位を与えることで、前記1または複数の信号用スイッチをオン・オフする

受信装置のフロントエンド回路。 - IC(Integrated Circuit;集積回路)化されていることを特徴とする請求項12乃至請求項17のいずれかに記載の受信装置のフロントエンド回路。

- 信号伝送路をオン・オフする1または複数の信号用スイッチを備える信号処理部の複数個に、入力信号を信号分配手段により分配して供給する信号処理装置におけるスイッチ切替制御方法であって、

制御手段が、切替信号により前記信号処理部の前記1または複数の信号用スイッチが切り替えられたときに、前記1または複数の信号用スイッチが切り替えられた信号処理部の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制工程を有する

信号処理装置におけるスイッチ切替制御方法。 - 受信信号が分配されて入力される複数個の信号処理部のうちの1つの信号処理部であるフロントエンド回路であって、入力端を通じて入力される受信信号の伝送路をオン・オフする1または複数の信号用スイッチと、制御手段を備えるフロントエンド回路におけるスイッチ切替制御方法であって、

切替信号により、前記1または複数の信号用スイッチが切り替えられたときに、前記制御手段が、前記フロントエンド回路の入力インピーダンスが、急峻でない遷移をするように抑制するための抑制工程を有する

フロントエンド回路におけるスイッチ切替制御方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009128702A JP5287508B2 (ja) | 2009-05-28 | 2009-05-28 | 信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 |

| US12/662,638 US8896760B2 (en) | 2009-05-28 | 2010-04-27 | Signal processing device and signal processing method |

| EP10005135.8A EP2259427B1 (en) | 2009-05-28 | 2010-05-17 | Signal processing device and signal processing method |

| CN2010101845261A CN101924888B (zh) | 2009-05-28 | 2010-05-21 | 信号处理设备与信号处理方法 |

| US14/550,105 US9432609B2 (en) | 2009-05-28 | 2014-11-21 | Signal processing device and signal processing method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009128702A JP5287508B2 (ja) | 2009-05-28 | 2009-05-28 | 信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010278719A JP2010278719A (ja) | 2010-12-09 |

| JP2010278719A5 JP2010278719A5 (ja) | 2012-04-12 |

| JP5287508B2 true JP5287508B2 (ja) | 2013-09-11 |

Family

ID=42288661

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009128702A Expired - Fee Related JP5287508B2 (ja) | 2009-05-28 | 2009-05-28 | 信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8896760B2 (ja) |

| EP (1) | EP2259427B1 (ja) |

| JP (1) | JP5287508B2 (ja) |

| CN (1) | CN101924888B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102014213741A1 (de) * | 2014-07-15 | 2016-02-18 | Micro-Epsilon Messtechnik Gmbh & Co. Kg | Schaltung und Verfahren zum Ansteuern eines Wegmesssensors |

| WO2020195000A1 (ja) * | 2019-03-27 | 2020-10-01 | パナソニックIpマネジメント株式会社 | 信号処理装置、慣性力センサ、信号処理方法、及びプログラム |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2828838C2 (de) * | 1977-07-01 | 1983-10-20 | Hitachi, Ltd., Tokyo | HF-Eingangsschaltung für Fernsehempfänger |

| JPS5875922A (ja) * | 1981-10-30 | 1983-05-07 | Toshiba Corp | 半導体スイツチ回路 |

| US4641190A (en) * | 1985-05-10 | 1987-02-03 | Rca Corporation | Muting system |

| JPH0770981B2 (ja) * | 1991-01-14 | 1995-07-31 | 関西日本電気株式会社 | パワーmosスイッチ |

| CN1021272C (zh) * | 1991-04-09 | 1993-06-16 | 詹国华 | 无干扰电扇多功能控制器 |

| JP3124879B2 (ja) * | 1993-10-07 | 2001-01-15 | 株式会社フジクラ | 通信線路の切換方法 |

| JPH07234731A (ja) | 1994-02-21 | 1995-09-05 | Sony Tektronix Corp | 可変電流源回路 |

| JP3777209B2 (ja) | 1995-11-14 | 2006-05-24 | 富士通株式会社 | 高周波スイッチ及び高周波スイッチ付き送受信装置 |

| JP3088323B2 (ja) * | 1997-02-18 | 2000-09-18 | 埼玉日本電気株式会社 | Tdma方式無線機とシンセサイザ出力レベル調整回路 |

| JP3381547B2 (ja) | 1997-04-07 | 2003-03-04 | 三菱電機株式会社 | 高周波スイッチと送受信切替装置 |

| TWI239522B (en) * | 2001-07-16 | 2005-09-11 | Hitachi Maxell | Optical disk, its production method, its drive-device, and stamper used in the production of an optical disk |

| US7034632B2 (en) * | 2004-05-12 | 2006-04-25 | Broadcom Corporation | Multi-tuner receivers with cross talk reduction |

| JP4241511B2 (ja) | 2004-06-04 | 2009-03-18 | 日産自動車株式会社 | エンジンのノック制御装置 |

| JP2006197446A (ja) * | 2005-01-17 | 2006-07-27 | Sony Corp | 受信装置 |

| CN101243684A (zh) * | 2005-08-22 | 2008-08-13 | Nxp股份有限公司 | 用于接收rf信号的多调谐器设备 |

| JP2007143031A (ja) * | 2005-11-22 | 2007-06-07 | Staf Corp | アンテナ整合回路 |

| PT2087623E (pt) * | 2006-11-03 | 2010-10-21 | Rf Magic Inc | Transposição e sobreposição de frequência do sinal de satélite |

| US8457574B2 (en) | 2007-02-16 | 2013-06-04 | Broadcom Corporation | Front-end integrated circuit for television receivers |

-

2009

- 2009-05-28 JP JP2009128702A patent/JP5287508B2/ja not_active Expired - Fee Related

-

2010

- 2010-04-27 US US12/662,638 patent/US8896760B2/en not_active Expired - Fee Related

- 2010-05-17 EP EP10005135.8A patent/EP2259427B1/en not_active Not-in-force

- 2010-05-21 CN CN2010101845261A patent/CN101924888B/zh active Active

-

2014

- 2014-11-21 US US14/550,105 patent/US9432609B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| CN101924888B (zh) | 2013-08-21 |

| US20100302460A1 (en) | 2010-12-02 |

| US8896760B2 (en) | 2014-11-25 |

| JP2010278719A (ja) | 2010-12-09 |

| CN101924888A (zh) | 2010-12-22 |

| US20150131007A1 (en) | 2015-05-14 |

| EP2259427A1 (en) | 2010-12-08 |

| US9432609B2 (en) | 2016-08-30 |

| EP2259427B1 (en) | 2018-04-18 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101242163B (zh) | 可变增益放大电路、接收器以及接收器集成电路 | |

| JP5151145B2 (ja) | スイッチ回路、可変コンデンサ回路およびそのic | |

| US7956933B2 (en) | Tuner circuit and digital broadcast receiver with low distortion performance and low power consumption | |

| JP5287508B2 (ja) | 信号処理装置、フロントエンド回路、信号処理装置におけるスイッチ切替制御方法、フロントエンド回路におけるスイッチ切替制御方法 | |

| US7430404B2 (en) | Tuner circuit and digital broadcast receiver with the same | |

| JP2013247536A (ja) | 信号処理装置および方法、並びに通信装置 | |

| KR20060097500A (ko) | 연산증폭기 | |

| JP2844609B2 (ja) | Agc回路 | |

| JP4937375B2 (ja) | 受光回路および受光回路を備える電子機器 | |

| US8649751B2 (en) | Receiver | |

| JP2008187329A (ja) | 可変利得増幅回路および可変利得アンプの入力インピーダンスマッチング方法 | |

| WO2005067286A1 (en) | Apparatus and method for providing automatic gain control | |

| JP3565739B2 (ja) | テレビジョンチューナ | |

| JP2009027463A (ja) | 地上波tv及びcatv共用受信機 | |

| JP3602289B2 (ja) | テレビチューナ | |

| JPH11284537A (ja) | チューナ | |

| JP2003244007A (ja) | 高周波入力回路 | |

| JPH10271401A (ja) | テレビチュ−ナ及びそのテレビチュ−ナを備えたテレビ受信機 | |

| JPH09107304A (ja) | 高周波信号受信装置 | |

| JP2008182534A (ja) | 半導体集積回路装置 | |

| JP2005079697A (ja) | 選局装置 | |

| JPH0583154A (ja) | Ic化受信装置 | |

| JP2005277919A (ja) | チューナ | |

| JP2004229146A (ja) | 放送波受信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120229 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120229 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130213 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130221 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130415 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130507 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130520 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5287508 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |