JP5085939B2 - 書き込み/消去失敗検出機構を有するフラッシュ記憶システム - Google Patents

書き込み/消去失敗検出機構を有するフラッシュ記憶システム Download PDFInfo

- Publication number

- JP5085939B2 JP5085939B2 JP2006547166A JP2006547166A JP5085939B2 JP 5085939 B2 JP5085939 B2 JP 5085939B2 JP 2006547166 A JP2006547166 A JP 2006547166A JP 2006547166 A JP2006547166 A JP 2006547166A JP 5085939 B2 JP5085939 B2 JP 5085939B2

- Authority

- JP

- Japan

- Prior art keywords

- data storage

- storage area

- flag

- data

- sector

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0416—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a single floating gate transistor and no select transistor, e.g. UV EPROM

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/102—External programming circuits, e.g. EPROM programmers; In-circuit programming or reprogramming; EPROM emulators

- G11C16/105—Circuits or methods for updating contents of nonvolatile memory, especially with 'security' features to ensure reliable replacement, i.e. preventing that old data is lost before new data is reliably written

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/14—Circuits for erasing electrically, e.g. erase voltage switching circuits

- G11C16/16—Circuits for erasing electrically, e.g. erase voltage switching circuits for erasing blocks, e.g. arrays, words, groups

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5646—Multilevel memory with flag bits, e.g. for showing that a "first page" of a word line is programmed but not a "second page"

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2216/00—Indexing scheme relating to G11C16/00 and subgroups, for features not directly covered by these groups

- G11C2216/12—Reading and writing aspects of erasable programmable read-only memories

- G11C2216/16—Flash programming of all the cells in an array, sector or block simultaneously

Description

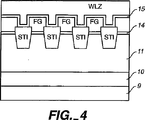

特定の実施例を提示するために図1〜7を参照して、本発明の様々な態様が実施される特定の不揮発性メモリシステムを説明する。消去処理における外乱の量を減らすために、本発明は選択されない記憶素子のコントロールゲートを基底のウエル構造と同じ電圧レベルに保つ。例示的な実施形態では、記憶素子はウエル構造の上に形成されている。消去処理中、ウエル上方の選択された記憶素子と選択されない記憶素子の双方とも、ウエル内にその電圧レベルを確立すると同時に消去電圧まで上昇される。次に、この電圧はウエルと選択されない記憶素子で保持されることによって、消去に関連するいかなる外乱の機会を減らす一方、選択された記憶素子は放電可能にされて必要な消去条件を作り出す。さらに、これは回路のピッチ領域を増やしたり、或いはメモリアレイ内に新たなワイヤを補足したりせずに達成することができ、その結果、回路に追加される付加的な周辺領域は最小限となる。

本発明の基本的な態様は、メモリのプログラミングおよび消去中に電源が遮断された場合に、システム性能への最小限の犠牲で書き込みおよび消去失敗検出のための信頼性がある機構を確保する技術である。構想は以下にさらに説明するようにさらに一般化して適用されるが、参照のための特定の実施形態を用いる場合、本発明は、主としてこれまでに説明してきたようにNAND構成を有するフラッシュ形のメモリに関して記載されている。

Claims (14)

- 複数のデータ記憶領域を備える不揮発性メモリであって、

各データ記憶領域が、

ユーザデータ部と、

オーバーヘッドデータ部と、を備え、

各データ記憶領域のオーバーヘッドデータ部が第1のフラグを含み、

前記不揮発性メモリは、第1のデータ記憶領域にユーザデータの第1の論理ページを書き込み、第2のデータ記憶領域にユーザデータの第2の論理ページを書き込み、また第2のデータ記憶領域の第1のフラグを利用することによって、第1のデータ記憶領域が適正に書き込まれたことを示すように構成され、た不揮発性メモリにおいて、

各データ記憶領域の第1のフラグをデータ記憶領域のユーザデータ部と同時に書き込み、

各データ記憶領域のオーバーヘッドデータ部は、そのデータ記憶領域自体が適正に書き込まれたことを示す第2のフラグをさらに含む不揮発性メモリ。 - 請求項1記載の不揮発性メモリにおいて、

前記データ記憶領域は、それぞれデータセクタに対応する不揮発性メモリ。 - 請求項1または2記載の不揮発性メモリにおいて、

前記データ記憶領域を複数の消去ユニットに編成し、

各消去ユニット内の所定のデータ記憶領域のオーバーヘッドデータ部は、所定のデータ記憶領域が属する消去ユニットが消去動作を完了したことを示す第3のフラグをさらに含む不揮発性メモリ。 - 請求項3記載の不揮発性メモリにおいて、

前記第3のフラグは、複数ビットからなる不揮発性メモリ。 - 請求項1記載の不揮発性メモリにおいて、

前記データ記憶領域を複数の消去ユニットに編成し、

前記消去ユニットは、それぞれそのオーバーヘッドデータ部が前記第2のフラグを有するが、前記第1のフラグを有していない追加のデータ記憶領域をさらに含む不揮発性メモリ。 - 請求項5記載の不揮発性メモリにおいて、

前記第1のフラグを有していないデータ記憶領域のそれぞれのオーバーヘッドデータ部は、前記第1のフラグを有していないデータ記憶領域が属する消去ユニットが消去動作を完了したことを示す第3のフラグを含む不揮発性メモリ。 - 請求項6記載の不揮発性メモリにおいて、

前記データ記憶領域は、所定のシーケンスに従って書き込まれ、

前記データ記憶領域とは別のデータ記憶領域は、シーケンスにおいて先行するデータ記憶領域であり、

前記第1のフラグを有していないデータ記憶領域は、それらが属するそれぞれのブロック内の前記シーケンスにおける第1のデータ記憶領域である不揮発性メモリ。 - 請求項1記載の不揮発性メモリにおいて、

前記第1のフラグは、それぞれ複数ビットからなる不揮発性メモリ。 - 請求項1〜6のいずれか記載の不揮発性メモリにおいて、

前記データ記憶領域は、所定のシーケンスに従って書き込まれ、

前記データ記憶領域とは別のデータ記憶領域は、シーケンスにおいて先行するデータ記憶領域である不揮発性メモリ。 - 請求項1記載の不揮発性メモリにおいて、

前記第1のフラグとユーザデータ部のコンテンツは、誤り訂正符号によって保護される不揮発性メモリ。 - 請求項1記載の不揮発性メモリにおいて、

データをメモリに読み込みかつ書き込むためのコントローラをさらに備え、2つまたはそれ以上の前記データ記憶領域へのデータの順次書き込み処理中に、第1のデータ記憶領域に続く各データ記憶領域ごとに、先行するデータ記憶領域の書き込みを示す表示がその書き込み処理の一部として現行のデータ記憶領域に書き込まれる不揮発性メモリ。 - 請求項11記載の不揮発性メモリにおいて、

前記コントローラは、順次書き込み処理の最後のデータ記憶領域について、順次書き込み処理中に、最後のデータ記憶領域の書き込みを示す表示が最後のデータ記憶領域に書き込まれるようにさらに構成される不揮発性メモリ。 - 不揮発性メモリの動作方法であって、

第1のデータ記憶領域にユーザデータの第1の論理ページをプログラムするステップと、

第1の論理ページが前記第1のデータ記憶領域に適正にプログラムされたかを検証するステップと、

引き続いて、第2のデータ記憶領域にユーザデータの第2の論理ページをプログラムするステップと、

前記第2の論理ページをプログラムするステップと同時に、第1のデータ記憶領域が適正にプログラムされたことを示す表示を前記第2のデータ記憶領域に書き込むステップと、を含む方法において、

前記データ記憶領域は、所定の順序で書き込まれ、

前記データ記憶領域を消去ユニットにグループ化し、

前記第2の論理ページをプログラムするステップに引き続いて、前記第2の論理ページが前記第2のデータ記憶領域に適正にプログラムされたかを検証するステップと、

前記第2のデータ記憶領域が、前記第2のデータ記憶領域が属する消去ユニットに所定の順序で書き込まれた最後のデータ記憶領域である場合は、引き続いて前記第2のデータ記憶領域が適正にプログラムされたことを示す表示を前記第2のデータ記憶領域に書き込むステップと、をさらに含む方法。 - 請求項13記載の方法において、

前記第2の論理ページと、前記第1のデータ記憶領域が適正にプログラムされたことを示す表示は、誤り訂正符号によって保護される方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/751,096 US7299314B2 (en) | 2003-12-31 | 2003-12-31 | Flash storage system with write/erase abort detection mechanism |

| US10/751,096 | 2003-12-31 | ||

| PCT/US2004/042462 WO2005066973A1 (en) | 2003-12-31 | 2004-12-16 | Flash storage system with write/erase abort detection mechanism |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007520801A JP2007520801A (ja) | 2007-07-26 |

| JP2007520801A5 JP2007520801A5 (ja) | 2008-01-31 |

| JP5085939B2 true JP5085939B2 (ja) | 2012-11-28 |

Family

ID=34701265

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006547166A Expired - Fee Related JP5085939B2 (ja) | 2003-12-31 | 2004-12-16 | 書き込み/消去失敗検出機構を有するフラッシュ記憶システム |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7299314B2 (ja) |

| EP (1) | EP1700312B1 (ja) |

| JP (1) | JP5085939B2 (ja) |

| KR (1) | KR100992985B1 (ja) |

| CN (1) | CN1902712B (ja) |

| TW (1) | TWI290321B (ja) |

| WO (1) | WO2005066973A1 (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8415302B2 (en) | 2004-01-28 | 2013-04-09 | The Regents Of The University Of California | Surgical applications for BMP binding protein |

| US8975231B2 (en) | 2004-01-28 | 2015-03-10 | The Regents Of The University Of California | Bone morphogenic protein binding peptide |

| US9072709B2 (en) | 2009-06-23 | 2015-07-07 | The Regents Of The University Of California | Enhancement of bone morphogenic protein (BMP) retention with BMP binding peptide (BBP) |

Families Citing this family (78)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7761770B2 (en) * | 2003-05-29 | 2010-07-20 | Emc Corporation | Disk controller architecture to allow on-the-fly error correction and write disruption detection |

| JP2005108273A (ja) * | 2003-09-26 | 2005-04-21 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US20050235063A1 (en) * | 2004-04-15 | 2005-10-20 | Wilson Christopher S | Automatic discovery of a networked device |

| US20050231849A1 (en) * | 2004-04-15 | 2005-10-20 | Viresh Rustagi | Graphical user interface for hard disk drive management in a data storage system |

| US7500135B2 (en) * | 2004-04-15 | 2009-03-03 | Broadcom Corporation | Fault tolerant data storage device |

| US7681007B2 (en) * | 2004-04-15 | 2010-03-16 | Broadcom Corporation | Automatic expansion of hard disk drive capacity in a storage device |

| US7395402B2 (en) * | 2004-04-15 | 2008-07-01 | Broadcom Corporation | Method and system of data storage capacity allocation and management using one or more data storage drives |

| US20050235283A1 (en) * | 2004-04-15 | 2005-10-20 | Wilson Christopher S | Automatic setup of parameters in networked devices |

| US7966353B2 (en) * | 2005-01-31 | 2011-06-21 | Broadcom Corporation | Method and system for flexibly providing shared access to non-data pool file systems |

| US8065350B2 (en) * | 2005-01-31 | 2011-11-22 | Broadcom Corporation | Method and system for flexibly providing shared access to data pools |

| US20060248252A1 (en) * | 2005-04-27 | 2006-11-02 | Kharwa Bhupesh D | Automatic detection of data storage functionality within a docking station |

| KR100732628B1 (ko) * | 2005-07-28 | 2007-06-27 | 삼성전자주식회사 | 멀티-비트 데이터 및 싱글-비트 데이터를 저장하는 플래시메모리 장치 |

| US7971071B2 (en) * | 2006-05-24 | 2011-06-28 | Walkoe Wilbur J | Integrated delivery and protection device for digital objects |

| KR100809319B1 (ko) * | 2006-09-13 | 2008-03-05 | 삼성전자주식회사 | 플래시 메모리에서 연속한 섹터 쓰기 요청에 대해 원자성을제공하는 장치 및 방법 |

| KR100833189B1 (ko) * | 2006-11-03 | 2008-05-28 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의환경설정정보 설정 방법 |

| TWI386796B (zh) * | 2007-01-04 | 2013-02-21 | Sandisk Il Ltd | 用於回復於一主機及一資料儲存裝置之間之一損壞之檔案傳送之方法、主機裝置及與電腦可讀取媒體 |

| US7668018B2 (en) * | 2007-04-03 | 2010-02-23 | Freescale Semiconductor, Inc. | Electronic device including a nonvolatile memory array and methods of using the same |

| US8266391B2 (en) * | 2007-06-19 | 2012-09-11 | SanDisk Technologies, Inc. | Method for writing data of an atomic transaction to a memory device |

| US20080320253A1 (en) * | 2007-06-19 | 2008-12-25 | Andrew Tomlin | Memory device with circuitry for writing data of an atomic transaction |

| US8151034B2 (en) * | 2007-09-12 | 2012-04-03 | Sandisk Technologies Inc. | Write abort and erase abort handling |

| KR20090042039A (ko) * | 2007-10-25 | 2009-04-29 | 삼성전자주식회사 | 불휘발성 메모리 장치의 데이터 관리 방법 |

| US8832408B2 (en) * | 2007-10-30 | 2014-09-09 | Spansion Llc | Non-volatile memory array partitioning architecture and method to utilize single level cells and multi-level cells within the same memory |

| TW200929225A (en) * | 2007-12-25 | 2009-07-01 | Powerchip Semiconductor Corp | Memory programming method and data access method |

| US8775758B2 (en) * | 2007-12-28 | 2014-07-08 | Sandisk Technologies Inc. | Memory device and method for performing a write-abort-safe firmware update |

| CN101364444B (zh) | 2008-02-05 | 2011-05-11 | 威盛电子股份有限公司 | 控制方法及运用该控制方法的存储器及处理系统 |

| TW200951960A (en) * | 2008-06-12 | 2009-12-16 | Genesys Logic Inc | Flash memory control apparatus having sequential writing and method thereof |

| TWI399651B (zh) * | 2008-09-12 | 2013-06-21 | Communication protocol method and system for input / output device | |

| KR101541736B1 (ko) * | 2008-09-22 | 2015-08-04 | 삼성전자주식회사 | 멀티-레벨 셀 플래시 메모리 장치에서의 lsb 페이지 복구 방법 |

| US8102705B2 (en) | 2009-06-05 | 2012-01-24 | Sandisk Technologies Inc. | Structure and method for shuffling data within non-volatile memory devices |

| US8027195B2 (en) | 2009-06-05 | 2011-09-27 | SanDisk Technologies, Inc. | Folding data stored in binary format into multi-state format within non-volatile memory devices |

| US20110002169A1 (en) | 2009-07-06 | 2011-01-06 | Yan Li | Bad Column Management with Bit Information in Non-Volatile Memory Systems |

| CN102004706B (zh) * | 2009-09-01 | 2012-09-19 | 联芯科技有限公司 | 一种基于ftl的闪存擦写掉电保护方法 |

| EP2299363B1 (fr) | 2009-09-21 | 2013-01-09 | STMicroelectronics (Rousset) SAS | Procédé de nivellement de l'usure dans une mémoire non volatile |

| FR2950465B1 (fr) * | 2009-09-21 | 2012-08-17 | St Microelectronics Rousset | Methode d'ecriture de donnees dans une memoire non volatile, protegee contre l'arrachement |

| US8271719B2 (en) * | 2009-10-29 | 2012-09-18 | Freescale Semiconductor, Inc. | Non-volatile memory controller device and method therefor |

| US8468294B2 (en) | 2009-12-18 | 2013-06-18 | Sandisk Technologies Inc. | Non-volatile memory with multi-gear control using on-chip folding of data |

| US20110153912A1 (en) * | 2009-12-18 | 2011-06-23 | Sergey Anatolievich Gorobets | Maintaining Updates of Multi-Level Non-Volatile Memory in Binary Non-Volatile Memory |

| US8144512B2 (en) | 2009-12-18 | 2012-03-27 | Sandisk Technologies Inc. | Data transfer flows for on-chip folding |

| US8054684B2 (en) | 2009-12-18 | 2011-11-08 | Sandisk Technologies Inc. | Non-volatile memory and method with atomic program sequence and write abort detection |

| US8725935B2 (en) | 2009-12-18 | 2014-05-13 | Sandisk Technologies Inc. | Balanced performance for on-chip folding of non-volatile memories |

| US9396104B1 (en) * | 2010-03-22 | 2016-07-19 | Seagate Technology, Llc | Accessing compressed data of varying-sized quanta in non-volatile memory |

| EP2413329B1 (en) * | 2010-07-28 | 2014-03-26 | Fujitsu Semiconductor Europe GmbH | Electronic apparatuses |

| US9026761B2 (en) * | 2010-12-20 | 2015-05-05 | Stmicroelectronics (Grenoble 2) Sas | Interface system, and corresponding integrated circuit and method |

| EP2466478B1 (en) | 2010-12-20 | 2013-11-27 | STMicroelectronics (Grenoble 2) SAS | Communication system, and corresponding integrated circuit and method |

| US9342446B2 (en) | 2011-03-29 | 2016-05-17 | SanDisk Technologies, Inc. | Non-volatile memory system allowing reverse eviction of data updates to non-volatile binary cache |

| JP5803614B2 (ja) * | 2011-11-29 | 2015-11-04 | ソニー株式会社 | 不揮発性キャッシュメモリ、不揮発性キャッシュメモリの処理方法、コンピュータシステム |

| US9141308B2 (en) | 2011-12-30 | 2015-09-22 | Sandisk Technologies Inc. | Controller and method for using a transaction flag for page protection |

| US20130205066A1 (en) * | 2012-02-03 | 2013-08-08 | Sandisk Technologies Inc. | Enhanced write abort management in flash memory |

| US8842473B2 (en) | 2012-03-15 | 2014-09-23 | Sandisk Technologies Inc. | Techniques for accessing column selecting shift register with skipped entries in non-volatile memories |

| ITMI20120595A1 (it) | 2012-04-12 | 2013-10-13 | St Microelectronics Srl | Gestione della cancellazione di pagine operative di un dispositivo di memoria flash tramite pagine di servizio |

| US8681548B2 (en) | 2012-05-03 | 2014-03-25 | Sandisk Technologies Inc. | Column redundancy circuitry for non-volatile memory |

| KR101944793B1 (ko) | 2012-09-04 | 2019-02-08 | 삼성전자주식회사 | 플래시 메모리를 포함하는 플래시 메모리 시스템 및 그것의 비정상 워드 라인 검출 방법 |

| US8897080B2 (en) | 2012-09-28 | 2014-11-25 | Sandisk Technologies Inc. | Variable rate serial to parallel shift register |

| US9076506B2 (en) | 2012-09-28 | 2015-07-07 | Sandisk Technologies Inc. | Variable rate parallel to serial shift register |

| US9490035B2 (en) | 2012-09-28 | 2016-11-08 | SanDisk Technologies, Inc. | Centralized variable rate serializer and deserializer for bad column management |

| BR112015018304A2 (pt) * | 2013-01-30 | 2017-07-18 | Hewlett Packard Development Co | mecanismo de escrita de memória não volátil |

| US9378829B2 (en) * | 2013-02-07 | 2016-06-28 | Cypress Semiconductor Corporation | Non-volatile memory device with an EPLI comparator |

| US9218279B2 (en) | 2013-03-15 | 2015-12-22 | Western Digital Technologies, Inc. | Atomic write command support in a solid state drive |

| KR102116983B1 (ko) | 2013-08-14 | 2020-05-29 | 삼성전자 주식회사 | 메모리 장치 및 메모리 시스템의 동작 방법. |

| TWI501242B (zh) * | 2013-10-04 | 2015-09-21 | Winbond Electronics Corp | 快閃記憶體之抹除方法 |

| KR20150046974A (ko) * | 2013-10-23 | 2015-05-04 | 에스케이하이닉스 주식회사 | 저항성 메모리 장치 및 동작 방법과 이를 포함하는 시스템 |

| CN104575604B (zh) * | 2013-10-25 | 2018-01-19 | 华邦电子股份有限公司 | 快闪存储器的抹除方法 |

| US9934872B2 (en) | 2014-10-30 | 2018-04-03 | Sandisk Technologies Llc | Erase stress and delta erase loop count methods for various fail modes in non-volatile memory |

| US9224502B1 (en) | 2015-01-14 | 2015-12-29 | Sandisk Technologies Inc. | Techniques for detection and treating memory hole to local interconnect marginality defects |

| WO2016115737A1 (en) | 2015-01-23 | 2016-07-28 | Hewlett-Packard Development Company, L.P. | Aligned variable reclamation |

| US10032524B2 (en) | 2015-02-09 | 2018-07-24 | Sandisk Technologies Llc | Techniques for determining local interconnect defects |

| US9564219B2 (en) | 2015-04-08 | 2017-02-07 | Sandisk Technologies Llc | Current based detection and recording of memory hole-interconnect spacing defects |

| US9269446B1 (en) | 2015-04-08 | 2016-02-23 | Sandisk Technologies Inc. | Methods to improve programming of slow cells |

| US9659619B2 (en) | 2015-05-21 | 2017-05-23 | Sandisk Technologies Llc | System and method for memory integrated circuit chip write abort indication |

| KR102491624B1 (ko) * | 2015-07-27 | 2023-01-25 | 삼성전자주식회사 | 데이터 저장 장치의 작동 방법과 상기 데이터 저장 장치를 포함하는 시스템의 작동 방법 |

| US9653154B2 (en) * | 2015-09-21 | 2017-05-16 | Sandisk Technologies Llc | Write abort detection for multi-state memories |

| US9929167B2 (en) * | 2016-07-13 | 2018-03-27 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device and manufacturing method thereof |

| KR20180025356A (ko) * | 2016-08-29 | 2018-03-09 | 삼성전자주식회사 | 불휘발성 메모리 및 불휘발성 메모리 시스템 |

| KR20180031853A (ko) * | 2016-09-19 | 2018-03-29 | 에스케이하이닉스 주식회사 | 메모리 시스템 및 메모리 시스템의 동작 방법 |

| TWI616807B (zh) * | 2016-11-17 | 2018-03-01 | 英屬維京群島商大心電子(英屬維京群島)股份有限公司 | 資料寫入方法以及儲存控制器 |

| CN106951189B (zh) * | 2017-03-17 | 2019-11-26 | 数据通信科学技术研究所 | 一种在线深度擦除flash文件的方法 |

| US11294579B2 (en) | 2020-06-18 | 2022-04-05 | Western Digital Technologies, Inc. | Mode handling in multi-protocol devices |

| US11557348B1 (en) | 2021-06-24 | 2023-01-17 | Western Digital Technologies, Inc. | Enhanced word line stripe erase abort detection |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6050666A (ja) | 1983-08-29 | 1985-03-20 | Hitachi Ltd | 記録制御方式 |

| GB9116493D0 (en) | 1991-07-30 | 1991-09-11 | Inmos Ltd | Read and write circuitry for a memory |

| JP3391475B2 (ja) * | 1992-07-16 | 2003-03-31 | 大日本印刷株式会社 | データの書き込み方法および読み出し方法ならびにこれらの方法を実施するデータ記録再生装置 |

| FR2703501B1 (fr) | 1993-04-01 | 1995-05-19 | Gemplus Card Int | Circuit intégré pour carte à mémoire et procédé de décomptage d'unités dans une carte à mémoire. |

| US5838614A (en) * | 1995-07-31 | 1998-11-17 | Lexar Microsystems, Inc. | Identification and verification of a sector within a block of mass storage flash memory |

| JPH09185551A (ja) * | 1996-01-08 | 1997-07-15 | Mitsubishi Electric Corp | 半導体記憶装置 |

| JP3718578B2 (ja) * | 1997-06-25 | 2005-11-24 | ソニー株式会社 | メモリ管理方法及びメモリ管理装置 |

| JPH11213626A (ja) * | 1998-01-21 | 1999-08-06 | Toshiba Corp | データ記録媒体とデータ記録装置とデータ再生装置 |

| JP3640802B2 (ja) * | 1998-06-08 | 2005-04-20 | 富士通株式会社 | データバックアップ方式 |

| US6662334B1 (en) | 1999-02-25 | 2003-12-09 | Adaptec, Inc. | Method and device for performing error correction on ECC data sectors |

| JP3920501B2 (ja) | 1999-04-02 | 2007-05-30 | 株式会社東芝 | 不揮発性半導体記憶装置及びそのデータ消去制御方法 |

| US6535949B1 (en) * | 1999-04-19 | 2003-03-18 | Research In Motion Limited | Portable electronic device having a log-structured file system in flash memory |

| US6564307B1 (en) * | 1999-08-18 | 2003-05-13 | International Business Machines Corporation | Method, system, and program for logically erasing data |

| JP2001250388A (ja) * | 2000-03-06 | 2001-09-14 | Fujitsu Ltd | 消去動作情報を記憶する不揮発性メモリ |

| JP4031190B2 (ja) * | 2000-09-29 | 2008-01-09 | 株式会社東芝 | メモリカード、不揮発性メモリ、不揮発性メモリのデータ書き込み方法及びデータ書き込み装置 |

| JP4037605B2 (ja) * | 2000-12-04 | 2008-01-23 | 株式会社東芝 | 不揮発性メモリユニットのコントローラ、同コントローラを有するメモリシステム及び不揮発性メモリユニットの制御方法 |

| US6549467B2 (en) | 2001-03-09 | 2003-04-15 | Micron Technology, Inc. | Non-volatile memory device with erase address register |

| JP3692313B2 (ja) * | 2001-06-28 | 2005-09-07 | 松下電器産業株式会社 | 不揮発性メモリの制御方法 |

| JP3675375B2 (ja) * | 2001-07-25 | 2005-07-27 | ソニー株式会社 | 不揮発性メモリ並びに不揮発性メモリのデータ書き換え方法 |

| CN1255733C (zh) | 2001-07-25 | 2006-05-10 | 索尼株式会社 | 非易失性存储器和非易失性存储器的数据改写方法 |

| US6977847B2 (en) | 2001-11-23 | 2005-12-20 | M-Systems Flash Disk Pioneers Ltd. | Detecting partially erased units in flash devices |

| US7010662B2 (en) * | 2002-02-27 | 2006-03-07 | Microsoft Corporation | Dynamic data structures for tracking file system free space in a flash memory device |

| GB2386212A (en) * | 2002-03-09 | 2003-09-10 | Sharp Kk | Storing temporally consecutive values in a memory segment that cannot be overwritten using sequential and bridging pointers |

| JP3978720B2 (ja) * | 2002-05-13 | 2007-09-19 | 日本電気株式会社 | データ記憶方法 |

| US6891690B2 (en) | 2002-11-20 | 2005-05-10 | International Business Machines Corporation | On-drive integrated sector format raid error correction code system and method |

| JP3984209B2 (ja) * | 2003-07-31 | 2007-10-03 | 株式会社東芝 | 半導体記憶装置 |

-

2003

- 2003-12-31 US US10/751,096 patent/US7299314B2/en active Active

-

2004

- 2004-12-16 EP EP04814618A patent/EP1700312B1/en not_active Not-in-force

- 2004-12-16 JP JP2006547166A patent/JP5085939B2/ja not_active Expired - Fee Related

- 2004-12-16 KR KR1020067012950A patent/KR100992985B1/ko not_active IP Right Cessation

- 2004-12-16 WO PCT/US2004/042462 patent/WO2005066973A1/en active Application Filing

- 2004-12-16 CN CN2004800393113A patent/CN1902712B/zh not_active Expired - Fee Related

- 2004-12-29 TW TW093141183A patent/TWI290321B/zh not_active IP Right Cessation

-

2007

- 2007-11-07 US US11/936,440 patent/US7669004B2/en not_active Expired - Lifetime

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8415302B2 (en) | 2004-01-28 | 2013-04-09 | The Regents Of The University Of California | Surgical applications for BMP binding protein |

| US8975231B2 (en) | 2004-01-28 | 2015-03-10 | The Regents Of The University Of California | Bone morphogenic protein binding peptide |

| US9610320B2 (en) | 2004-01-28 | 2017-04-04 | Regents Of The University Of California | Surgical applications for BMP binding protein |

| US9855368B2 (en) | 2004-01-28 | 2018-01-02 | The Regents Of The University Of California | Bone morphogenic protein binding peptide |

| US9072709B2 (en) | 2009-06-23 | 2015-07-07 | The Regents Of The University Of California | Enhancement of bone morphogenic protein (BMP) retention with BMP binding peptide (BBP) |

| US9694047B2 (en) | 2009-06-23 | 2017-07-04 | The Regents Of The University Of California | Enhancement of bone morphogenic protein (BMP) retention with BMP binding peptide (BBP) |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2005066973A1 (en) | 2005-07-21 |

| CN1902712B (zh) | 2012-03-28 |

| EP1700312B1 (en) | 2012-09-05 |

| TWI290321B (en) | 2007-11-21 |

| EP1700312A1 (en) | 2006-09-13 |

| US20050144362A1 (en) | 2005-06-30 |

| KR20060127015A (ko) | 2006-12-11 |

| US20080065818A1 (en) | 2008-03-13 |

| KR100992985B1 (ko) | 2010-11-08 |

| TW200535853A (en) | 2005-11-01 |

| US7669004B2 (en) | 2010-02-23 |

| US7299314B2 (en) | 2007-11-20 |

| CN1902712A (zh) | 2007-01-24 |

| JP2007520801A (ja) | 2007-07-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5085939B2 (ja) | 書き込み/消去失敗検出機構を有するフラッシュ記憶システム | |

| KR101368375B1 (ko) | 소거된 섹터 검출 메커니즘 | |

| US7616499B2 (en) | Retention margin program verification | |

| KR101089575B1 (ko) | 사이클 카운트를 저장하는 대량 소거 블록들을 구비한비휘발성 반도체 메모리 | |

| US7872910B2 (en) | Non-volatile semiconductor storage system | |

| JP2005538485A (ja) | メモリセルの隣接する行の記憶素子間の結合の効果を減少させる方法 | |

| JP2008027511A (ja) | 半導体記憶装置およびその制御方法 | |

| JP2007507055A5 (ja) | ||

| US7652918B2 (en) | Retention margin program verification | |

| JP2009104729A (ja) | 不揮発性半導体記憶装置 | |

| CN106898378B (zh) | 半导体存储装置及与非型快闪存储器的编程方法 | |

| US9910749B2 (en) | Non-volatile memory with dynamic repurpose of word line | |

| CN111383703B (zh) | 非易失性存储器及其操作方法 | |

| JP6293846B2 (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071207 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110301 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110308 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110513 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110520 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110701 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110726 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20111013 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20111020 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120124 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120321 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120704 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20120706 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120705 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120727 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120814 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120906 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5085939 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |