JP5047529B2 - 微細コンタクトを備える半導体素子及びその製造方法 - Google Patents

微細コンタクトを備える半導体素子及びその製造方法 Download PDFInfo

- Publication number

- JP5047529B2 JP5047529B2 JP2006104573A JP2006104573A JP5047529B2 JP 5047529 B2 JP5047529 B2 JP 5047529B2 JP 2006104573 A JP2006104573 A JP 2006104573A JP 2006104573 A JP2006104573 A JP 2006104573A JP 5047529 B2 JP5047529 B2 JP 5047529B2

- Authority

- JP

- Japan

- Prior art keywords

- contact

- interlayer insulating

- insulating film

- semiconductor device

- spacer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 51

- 238000000034 method Methods 0.000 title description 52

- 238000004519 manufacturing process Methods 0.000 title description 12

- 239000011229 interlayer Substances 0.000 claims description 80

- 125000006850 spacer group Chemical group 0.000 claims description 72

- 239000000758 substrate Substances 0.000 claims description 36

- 238000005530 etching Methods 0.000 claims description 27

- 239000010410 layer Substances 0.000 claims description 24

- 239000000463 material Substances 0.000 claims description 10

- 150000004767 nitrides Chemical group 0.000 claims description 6

- 230000000149 penetrating effect Effects 0.000 claims description 3

- 230000015572 biosynthetic process Effects 0.000 description 20

- 229920002120 photoresistant polymer Polymers 0.000 description 18

- 239000004020 conductor Substances 0.000 description 16

- 230000002093 peripheral effect Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 229920003209 poly(hydridosilsesquioxane) Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- CGEORJKFOZSMEZ-MBZVMHRFSA-N (+)-sesamin monocatechol Chemical compound C1=C(O)C(O)=CC=C1[C@@H]1[C@@H](CO[C@@H]2C=3C=C4OCOC4=CC=3)[C@@H]2CO1 CGEORJKFOZSMEZ-MBZVMHRFSA-N 0.000 description 1

- IMSOBGJSYSFTKG-PKPIPKONSA-N Lysinoalanine Chemical compound OC(=O)[C@@H](N)CCCCNCC(N)C(O)=O IMSOBGJSYSFTKG-PKPIPKONSA-N 0.000 description 1

- 229910003697 SiBN Inorganic materials 0.000 description 1

- 229910004541 SiN Inorganic materials 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229920001709 polysilazane Polymers 0.000 description 1

- 239000005368 silicate glass Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

また、周辺領域を第1スペーサまたは第2スペーサで保護することにより、セル領域と周辺領域とに同時にコンタクトを形成できる。

[実施例]

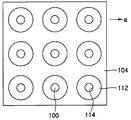

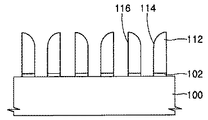

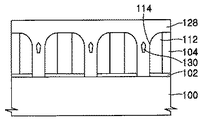

図1Aないし図6Aは、本発明の第1実施例による微細コンタクトの形成方法を説明するための平面図であり、図1Bないし図6Bは、図2AのA−A線の断面図である。

図1A及び図1Bを参照すれば、導電領域(図示せず)が形成された基板100、例えば、シリコン基板上に第1エッチング停止膜102及び層間絶縁膜104を順次に形成する。第1エッチング停止膜102は、層間絶縁膜104に比べてエッチング選択比が十分に大きい物質で蒸着できる。層間絶縁膜104は、低誘電定数を有する物質、例えば、シリコン酸化膜からなりうる。

図7A及び図8Aは、本発明の第2実施例による微細コンタクトの形成方法を説明するための平面図であり、図7B及び図8Bは、図2AのA−A線の断面図である。本実施例は、前記第1実施例において第3コンタクトホール116を形成する過程で露出された第2コンタクトホール114内の基板100の損傷を防止することを目的とする。

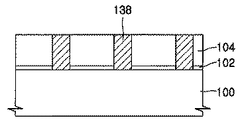

図9Aは、本発明の第3実施例による微細コンタクトの形成方法を説明するための平面図であり、図9Bは、図2AのA−A線の断面図である。本実施例では、第3コンタクトホール116を形成するために、第1実施例のライン形態の第2フォトレジストパターン118の代りにコンタクト形態の第3フォトレジストパターン132を形成することである。

図10A及び図11Aは、本発明の第4実施例による微細コンタクトの形成方法を説明するための平面図であり、図10B及び図11Bは、図10AのB−B線の断面図であり、図10C及び図11Cは、図10AのC−C線の断面図である。本実施例では、第1方向(a方向)と垂直な方向に延長される第2方向(b方向)の層間絶縁膜104に所定のコンタクトを形成している。

図12Aないし図20Aは、本発明の第5実施例による微細コンタクトの形成方法を説明するための平面図であり、図12Bないし図20Bは、図12AのD−D線の断面図であり、図12Cないし図20Cは、図12AのE−E線の断面図である。本実施例は、スペーサを利用した微細コンタクトの製造方法を半導体素子に適用する例であって、フラッシュメモリを中心として説明する。

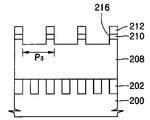

図14Aないし図14Cを参照すれば、第2層間絶縁膜212上に第5コンタクトホール(図15Aの216)を定義する第5フォトレジストパターン214を形成する。ここで、第5コンタクトホール216は、第1ゲートライン204間にコンタクトを形成するためのものでありうる。

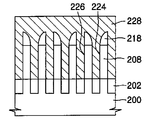

図18Aないし図18Cを参照すれば、第2スペーサ218が形成された第6コンタクトホール219を下部に垂直に拡張して、半導体基板200を露出させる第7コンタクトホール224を形成する。同時に、第2スペーサ218の間の第1層間絶縁膜208を除去して第8コンタクトホール226を形成する。

本発明の第5実施例によれば、第4コンタクト230と第5コンタクト232とを形成する過程で第2スペーサ218と第2エッチング停止膜210とが除去されるので、第2スペーサ218及び第2エッチング停止膜210の誘電率に影響されない。また、第2エッチング停止膜210を利用して、所望の部分にコンタクトを形成できる。

以上、本発明を望ましい実施例を挙げて詳細に説明したが、本発明は、前記実施例に限定されず、本発明の技術的思想の範囲内で当業者によって多様な変形が可能であろう。

102 第1エッチング停止膜

104 層間絶縁膜

106 第1コンタクトホール

110 第1PRパターン

112 第1スペーサ

114 第2コンタクトホール

116 第3コンタクトホール

118 第2フォトレジストパターン

120 導電性物質層

122 第1コンタクト

124 第2コンタクト

126、128 膜質

132 第3PRパターン

134 第4PRパターン

136 第4コンタクトホール

138 第3コンタクト

202 導電領域

204 第1ゲートライン

206 第2ゲートライン

208 第1層間絶縁膜

210 第2エッチング停止膜

212 第2層間絶縁膜

214 第5PRパターン

216 第5コンタクトホール

218 第2スペーサ

219 第6コンタクトホール

222 第6PRパターン

224 第7コンタクトホール

226 第8コンタクトホール

230 第4コンタクト

232 第5コンタクト

Claims (15)

- 導電領域を内在する基板と、

前記基板上に形成された少なくとも1層以上の層間絶縁膜と、

前記層間絶縁膜を貫通して前記導電領域と連結され、前記層間絶縁膜の最上層に前記層間絶縁膜とエッチング選択比が異なる第1スペーサにより取り囲まれた第1コンタクトと、

前記導電領域と連結され、前記第1コンタクトと共に第1方向に配列されつつ前記第1スペーサの間に埋め込まれる第2コンタクトと、を備える微細コンタクトを備える半導体素子。 - 前記層間絶縁膜は、低誘電定数を有する物質であることを特徴とする請求項1に記載の微細コンタクトを備える半導体素子。

- 前記第1スペーサと前記第1コンタクトとを備える第1コンタクトホールの前記第1方向の幅は、前記第2コンタクトの幅の3倍であることを特徴とする請求項1又は2に記載の微細コンタクトを備える半導体素子。

- 前記第1コンタクトホール内の前記第1コンタクトの幅は、前記第1スペーサの厚さによって決定されることを特徴とする請求項3に記載の微細コンタクトを備える半導体素子。

- 前記第1コンタクトホール間のピッチは、前記第1コンタクトと第2コンタクトとの間の間隔に対して2倍であることを特徴とする請求項3又は4に記載の微細コンタクトを備える半導体素子。

- 前記層間絶縁膜は酸化膜であり、前記第1スペーサは窒化膜であることを特徴とする請求項1〜5のいずれか一項に記載の微細コンタクトを備える半導体素子。

- 前記層間絶縁膜は窒化膜であり、前記第1スペーサは酸化膜であることを特徴とする請求項1〜5のいずれか一項に記載の微細コンタクトを備える半導体素子。

- 前記基板と前記層間絶縁膜との間に第1エッチング停止膜をさらに備えることを特徴とする請求項1〜7のいずれか一項に記載の微細コンタクトを備える半導体素子。

- 前記第1コンタクトと前記第2コンタクトとは、交互に反復的に形成されることを特徴とする請求項1〜8のいずれか一項に記載の微細コンタクトを備える半導体素子。

- 前記第1方向と垂直な第2方向に形成された前記第1スペーサ間の前記層間絶縁膜を貫通して前記基板と電気的に連結された第3コンタクトをさらに備えることを特徴とする請求項1〜9のいずれか一項に記載の微細コンタクトを備える半導体素子。

- 導電領域を内在する半導体基板と、

前記半導体基板上に形成され、相異なるサイズの第1ゲートラインの一部と第2ゲートラインとを覆う第1層間絶縁膜と、

前記第1ゲートライン間の前記第1層間絶縁膜を貫通して前記導電領域と連結され、前記第1層間絶縁膜に前記層間絶縁膜とエッチング選択比が異なる第2スペーサにより取り囲まれた第4コンタクトと、

前記第1ゲートライン間の前記第1層間絶縁膜を貫通して前記導電領域と連結され、前記第4コンタクトと共に第1方向に配列されつつ前記第2スペーサの間に埋め込まれる第5コンタクトと、を備えることを特徴とする微細コンタクトを備える半導体素子。 - 前記層間絶縁膜は、低誘電定数を有する物質であることを特徴とする請求項11に記載の微細コンタクトを備える半導体素子。

- 前記第2スペーサと前記第4コンタクトとを備える第5コンタクトホールの前記第1方向の幅は、前記第5コンタクトの幅の3倍であることを特徴とする請求項11又は12に記載の微細コンタクトを備える半導体素子。

- 前記第5コンタクトホール内の前記第4コンタクトの幅は、前記第2スペーサの厚さによって決定されることを特徴とする請求項13に記載の微細コンタクトを備える半導体素子。

- 前記第5コンタクトホール間のピッチは、前記第4コンタクトと第5コンタクトとの間の間隔に対して2倍であることを特徴とする請求項13又は14に記載の微細コンタクトを備える半導体素子。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020050032296A KR100640639B1 (ko) | 2005-04-19 | 2005-04-19 | 미세콘택을 포함하는 반도체소자 및 그 제조방법 |

| KR10-2005-0032296 | 2005-04-19 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006303488A JP2006303488A (ja) | 2006-11-02 |

| JP2006303488A5 JP2006303488A5 (ja) | 2009-05-21 |

| JP5047529B2 true JP5047529B2 (ja) | 2012-10-10 |

Family

ID=37107698

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006104573A Active JP5047529B2 (ja) | 2005-04-19 | 2006-04-05 | 微細コンタクトを備える半導体素子及びその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7855408B2 (ja) |

| JP (1) | JP5047529B2 (ja) |

| KR (1) | KR100640639B1 (ja) |

Families Citing this family (68)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7151040B2 (en) * | 2004-08-31 | 2006-12-19 | Micron Technology, Inc. | Methods for increasing photo alignment margins |

| US7910288B2 (en) | 2004-09-01 | 2011-03-22 | Micron Technology, Inc. | Mask material conversion |

| US7115525B2 (en) * | 2004-09-02 | 2006-10-03 | Micron Technology, Inc. | Method for integrated circuit fabrication using pitch multiplication |

| US7655387B2 (en) | 2004-09-02 | 2010-02-02 | Micron Technology, Inc. | Method to align mask patterns |

| US7253118B2 (en) | 2005-03-15 | 2007-08-07 | Micron Technology, Inc. | Pitch reduced patterns relative to photolithography features |

| US7390746B2 (en) | 2005-03-15 | 2008-06-24 | Micron Technology, Inc. | Multiple deposition for integration of spacers in pitch multiplication process |

| US7611944B2 (en) | 2005-03-28 | 2009-11-03 | Micron Technology, Inc. | Integrated circuit fabrication |

| US7429536B2 (en) | 2005-05-23 | 2008-09-30 | Micron Technology, Inc. | Methods for forming arrays of small, closely spaced features |

| US7560390B2 (en) | 2005-06-02 | 2009-07-14 | Micron Technology, Inc. | Multiple spacer steps for pitch multiplication |

| US7396781B2 (en) | 2005-06-09 | 2008-07-08 | Micron Technology, Inc. | Method and apparatus for adjusting feature size and position |

| US7541632B2 (en) * | 2005-06-14 | 2009-06-02 | Micron Technology, Inc. | Relaxed-pitch method of aligning active area to digit line |

| US7888721B2 (en) | 2005-07-06 | 2011-02-15 | Micron Technology, Inc. | Surround gate access transistors with grown ultra-thin bodies |

| US7768051B2 (en) | 2005-07-25 | 2010-08-03 | Micron Technology, Inc. | DRAM including a vertical surround gate transistor |

| US7413981B2 (en) * | 2005-07-29 | 2008-08-19 | Micron Technology, Inc. | Pitch doubled circuit layout |

| US8123968B2 (en) | 2005-08-25 | 2012-02-28 | Round Rock Research, Llc | Multiple deposition for integration of spacers in pitch multiplication process |

| US7816262B2 (en) | 2005-08-30 | 2010-10-19 | Micron Technology, Inc. | Method and algorithm for random half pitched interconnect layout with constant spacing |

| US7829262B2 (en) * | 2005-08-31 | 2010-11-09 | Micron Technology, Inc. | Method of forming pitch multipled contacts |

| US7696567B2 (en) | 2005-08-31 | 2010-04-13 | Micron Technology, Inc | Semiconductor memory device |

| US7687342B2 (en) | 2005-09-01 | 2010-03-30 | Micron Technology, Inc. | Method of manufacturing a memory device |

| US7557032B2 (en) | 2005-09-01 | 2009-07-07 | Micron Technology, Inc. | Silicided recessed silicon |

| US7759197B2 (en) * | 2005-09-01 | 2010-07-20 | Micron Technology, Inc. | Method of forming isolated features using pitch multiplication |

| US7393789B2 (en) | 2005-09-01 | 2008-07-01 | Micron Technology, Inc. | Protective coating for planarization |

| US7572572B2 (en) | 2005-09-01 | 2009-08-11 | Micron Technology, Inc. | Methods for forming arrays of small, closely spaced features |

| US7416943B2 (en) | 2005-09-01 | 2008-08-26 | Micron Technology, Inc. | Peripheral gate stacks and recessed array gates |

| US7776744B2 (en) | 2005-09-01 | 2010-08-17 | Micron Technology, Inc. | Pitch multiplication spacers and methods of forming the same |

| US7476933B2 (en) | 2006-03-02 | 2009-01-13 | Micron Technology, Inc. | Vertical gated access transistor |

| US7842558B2 (en) | 2006-03-02 | 2010-11-30 | Micron Technology, Inc. | Masking process for simultaneously patterning separate regions |

| US7902074B2 (en) | 2006-04-07 | 2011-03-08 | Micron Technology, Inc. | Simplified pitch doubling process flow |

| US8003310B2 (en) | 2006-04-24 | 2011-08-23 | Micron Technology, Inc. | Masking techniques and templates for dense semiconductor fabrication |

| US7488685B2 (en) | 2006-04-25 | 2009-02-10 | Micron Technology, Inc. | Process for improving critical dimension uniformity of integrated circuit arrays |

| US7795149B2 (en) * | 2006-06-01 | 2010-09-14 | Micron Technology, Inc. | Masking techniques and contact imprint reticles for dense semiconductor fabrication |

| US7723009B2 (en) | 2006-06-02 | 2010-05-25 | Micron Technology, Inc. | Topography based patterning |

| US7611980B2 (en) | 2006-08-30 | 2009-11-03 | Micron Technology, Inc. | Single spacer process for multiplying pitch by a factor greater than two and related intermediate IC structures |

| US7666578B2 (en) * | 2006-09-14 | 2010-02-23 | Micron Technology, Inc. | Efficient pitch multiplication process |

| KR100789391B1 (ko) * | 2006-10-20 | 2008-01-02 | 삼성전자주식회사 | 콘택 구조물 형성 방법 |

| US8809932B2 (en) * | 2007-03-26 | 2014-08-19 | Samsung Electronics Co., Ltd. | Semiconductor memory device, method of fabricating the same, and devices employing the semiconductor memory device |

| KR100924611B1 (ko) * | 2007-05-11 | 2009-11-02 | 주식회사 하이닉스반도체 | 반도체 소자의 미세 패턴 형성방법 |

| US7923373B2 (en) | 2007-06-04 | 2011-04-12 | Micron Technology, Inc. | Pitch multiplication using self-assembling materials |

| KR100877107B1 (ko) * | 2007-06-28 | 2009-01-07 | 주식회사 하이닉스반도체 | 반도체 소자의 층간절연막 형성방법 |

| US8563229B2 (en) | 2007-07-31 | 2013-10-22 | Micron Technology, Inc. | Process of semiconductor fabrication with mask overlay on pitch multiplied features and associated structures |

| US7737039B2 (en) | 2007-11-01 | 2010-06-15 | Micron Technology, Inc. | Spacer process for on pitch contacts and related structures |

| US7659208B2 (en) | 2007-12-06 | 2010-02-09 | Micron Technology, Inc | Method for forming high density patterns |

| JP5193582B2 (ja) | 2007-12-12 | 2013-05-08 | 株式会社東芝 | 半導体装置の製造方法 |

| US7790531B2 (en) | 2007-12-18 | 2010-09-07 | Micron Technology, Inc. | Methods for isolating portions of a loop of pitch-multiplied material and related structures |

| US8030218B2 (en) | 2008-03-21 | 2011-10-04 | Micron Technology, Inc. | Method for selectively modifying spacing between pitch multiplied structures |

| KR101379508B1 (ko) * | 2008-03-28 | 2014-03-27 | 삼성전자주식회사 | 수직 채널 트랜지스터 및 이의 제조 방법 |

| US8076208B2 (en) | 2008-07-03 | 2011-12-13 | Micron Technology, Inc. | Method for forming transistor with high breakdown voltage using pitch multiplication technique |

| US8101497B2 (en) | 2008-09-11 | 2012-01-24 | Micron Technology, Inc. | Self-aligned trench formation |

| US8492282B2 (en) | 2008-11-24 | 2013-07-23 | Micron Technology, Inc. | Methods of forming a masking pattern for integrated circuits |

| TWI366890B (en) * | 2008-12-31 | 2012-06-21 | Ind Tech Res Inst | Method of manufacturing through-silicon-via and through-silicon-via structure |

| KR101166799B1 (ko) * | 2009-12-29 | 2012-07-26 | 에스케이하이닉스 주식회사 | 홀 패턴 제조 방법 |

| KR20120117127A (ko) * | 2011-04-14 | 2012-10-24 | 삼성전자주식회사 | 소자 분리막 구조물 및 그 형성 방법 |

| KR101903477B1 (ko) | 2012-01-11 | 2018-10-02 | 삼성전자주식회사 | 반도체 장치의 제조 방법 |

| KR20130124861A (ko) | 2012-05-07 | 2013-11-15 | 삼성전자주식회사 | 패턴 형성 방법 |

| US9054156B2 (en) | 2012-07-30 | 2015-06-09 | International Business Machines Corporation | Non-lithographic hole pattern formation |

| US8999852B2 (en) | 2012-12-12 | 2015-04-07 | Micron Technology, Inc. | Substrate mask patterns, methods of forming a structure on a substrate, methods of forming a square lattice pattern from an oblique lattice pattern, and methods of forming a pattern on a substrate |

| US8889558B2 (en) | 2012-12-12 | 2014-11-18 | Micron Technology, Inc. | Methods of forming a pattern on a substrate |

| US8889559B2 (en) | 2012-12-12 | 2014-11-18 | Micron Technology, Inc. | Methods of forming a pattern on a substrate |

| US8937018B2 (en) * | 2013-03-06 | 2015-01-20 | Micron Technology, Inc. | Methods of forming a pattern on a substrate |

| CN104733310B (zh) * | 2013-12-18 | 2017-11-03 | 中芯国际集成电路制造(北京)有限公司 | 鳍式场效应管的形成方法 |

| US9184058B2 (en) * | 2013-12-23 | 2015-11-10 | Micron Technology, Inc. | Methods of forming patterns by using a brush layer and masks |

| US9412806B2 (en) | 2014-06-13 | 2016-08-09 | Invensas Corporation | Making multilayer 3D capacitors using arrays of upstanding rods or ridges |

| US9397038B1 (en) | 2015-02-27 | 2016-07-19 | Invensas Corporation | Microelectronic components with features wrapping around protrusions of conductive vias protruding from through-holes passing through substrates |

| US9558956B2 (en) * | 2015-07-01 | 2017-01-31 | Samsung Electronics Co., Ltd. | Method for fabricating semiconductor device |

| TWI661466B (zh) * | 2016-04-14 | 2019-06-01 | 日商東京威力科創股份有限公司 | 使用具有多種材料之一層的基板圖案化方法 |

| US9934970B1 (en) * | 2017-01-11 | 2018-04-03 | International Business Machines Corporation | Self aligned pattern formation post spacer etchback in tight pitch configurations |

| CN106847821B (zh) | 2017-03-07 | 2018-09-14 | 长江存储科技有限责任公司 | 半导体结构及其形成方法 |

| KR102369509B1 (ko) * | 2018-01-08 | 2022-03-02 | 삼성전자주식회사 | 반도체 장치 및 그 제조 방법 |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0669153A (ja) * | 1991-12-30 | 1994-03-11 | Nec Corp | 微細コンタクト孔の形成方法 |

| US5313089A (en) * | 1992-05-26 | 1994-05-17 | Motorola, Inc. | Capacitor and a memory cell formed therefrom |

| US5432739A (en) * | 1994-06-17 | 1995-07-11 | Philips Electronics North America Corporation | Non-volatile sidewall memory cell method of fabricating same |

| KR0161438B1 (ko) * | 1995-09-19 | 1999-02-01 | 김광호 | 미세 크기의 접촉창을 가지는 반도체 메모리 장치 및 그 제조 방법 |

| US6967369B1 (en) * | 1995-09-20 | 2005-11-22 | Micron Technology, Inc. | Semiconductor memory circuitry |

| JP2739855B2 (ja) * | 1995-12-14 | 1998-04-15 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| KR100223832B1 (ko) * | 1996-12-27 | 1999-10-15 | 구본준 | 반도체 소자 및 그 제조방법 |

| JP3168999B2 (ja) * | 1998-12-11 | 2001-05-21 | 日本電気株式会社 | 半導体装置の製造方法 |

| KR100356798B1 (ko) * | 1999-12-27 | 2002-10-18 | 주식회사 하이닉스반도체 | 반도체 소자의 제조방법 |

| KR100350056B1 (ko) * | 2000-03-09 | 2002-08-24 | 삼성전자 주식회사 | 다마신 게이트 공정에서 자기정렬콘택패드 형성 방법 |

| KR100378183B1 (ko) * | 2000-09-18 | 2003-03-29 | 삼성전자주식회사 | 반도체 메모리 장치 및 그의 제조 방법 |

| KR100396137B1 (ko) | 2001-06-13 | 2003-08-27 | 재단법인서울대학교산학협력재단 | 극미세 다중 패턴의 형성방법 |

| KR20030001084A (ko) | 2001-06-28 | 2003-01-06 | 주식회사 하이닉스반도체 | 반도체소자의 패턴 형성 방법 |

| KR100800131B1 (ko) * | 2001-06-29 | 2008-02-01 | 주식회사 하이닉스반도체 | 반도체소자의 제조방법 |

| US6638441B2 (en) | 2002-01-07 | 2003-10-28 | Macronix International Co., Ltd. | Method for pitch reduction |

| US6689658B2 (en) * | 2002-01-28 | 2004-02-10 | Silicon Based Technology Corp. | Methods of fabricating a stack-gate flash memory array |

| KR100539272B1 (ko) * | 2003-02-24 | 2005-12-27 | 삼성전자주식회사 | 반도체 장치 및 그 제조방법 |

| US20060186733A1 (en) | 2003-07-11 | 2006-08-24 | Continal Teves Ag & Co. Ohg | Electrohydraulic brake system for motor vehicles |

| US6815704B1 (en) * | 2003-09-04 | 2004-11-09 | Silicon Storage Technology, Inc. | Phase change memory device employing thermally insulating voids |

| US6853024B1 (en) * | 2003-10-03 | 2005-02-08 | Taiwan Semiconductor Manufacturing Company, Ltd. | Self-aligned MIM capacitor process for embedded DRAM |

| US7244673B2 (en) * | 2003-11-12 | 2007-07-17 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integration film scheme for copper / low-k interconnect |

| KR100526059B1 (ko) * | 2004-02-19 | 2005-11-08 | 삼성전자주식회사 | 반도체 소자 제조 공정에서의 자기-정렬 컨택 형성 방법 |

-

2005

- 2005-04-19 KR KR1020050032296A patent/KR100640639B1/ko active IP Right Grant

-

2006

- 2006-03-06 US US11/367,436 patent/US7855408B2/en active Active

- 2006-04-05 JP JP2006104573A patent/JP5047529B2/ja active Active

-

2010

- 2010-11-10 US US12/943,142 patent/US8242018B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US7855408B2 (en) | 2010-12-21 |

| US8242018B2 (en) | 2012-08-14 |

| KR100640639B1 (ko) | 2006-10-31 |

| US20060231900A1 (en) | 2006-10-19 |

| US20110076846A1 (en) | 2011-03-31 |

| JP2006303488A (ja) | 2006-11-02 |

| KR20060110096A (ko) | 2006-10-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5047529B2 (ja) | 微細コンタクトを備える半導体素子及びその製造方法 | |

| US8247291B2 (en) | Methods of forming fine patterns in integrated circuit devices and methods of manufacturing integrated circuit devices including the same | |

| KR102607555B1 (ko) | 반도체 소자 | |

| JP4976977B2 (ja) | 半導体装置の製造方法 | |

| JP5062969B2 (ja) | 半導体素子のランディングプラグコンタクト形成方法 | |

| JP2005026659A (ja) | フラッシュ素子のビットライン形成方法 | |

| KR101096186B1 (ko) | 패턴의 무너짐을 방지하는 반도체장치 제조 방법 | |

| CN105321874A (zh) | 自对准双重图案化 | |

| JP2007096321A (ja) | 化学機械的研磨を利用した自己整列コンタクトパッドの形成方法 | |

| JP2010153458A (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2000277708A (ja) | 半導体装置及びこれを形成する方法 | |

| JP2005167188A (ja) | 半導体素子の製造方法 | |

| JP4860189B2 (ja) | 半導体メモリ素子の金属配線形成方法 | |

| JP2008311623A (ja) | 半導体素子及びその製造方法 | |

| US20040166667A1 (en) | Method for manufacturing a semiconductor device | |

| TWI308786B (en) | Method for fabricating semiconductor device | |

| JP4943008B2 (ja) | 半導体素子の形成方法 | |

| JP2008047630A (ja) | 半導体装置およびその製造方法 | |

| JP2004072109A (ja) | 導電性ライン下部に延長された絶縁スペーサーを備えた集積回路及びその製造方法 | |

| JP2003023109A (ja) | 集積回路メモリ素子及びその製造方法 | |

| JP2008091368A (ja) | 半導体装置及びその製造方法 | |

| JP5107499B2 (ja) | 半導体装置 | |

| JP2006245198A (ja) | 半導体装置の製造方法 | |

| KR20060029006A (ko) | 반도체 소자 제조 방법 | |

| JP2003249572A (ja) | 半導体装置の製造方法及び半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090403 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090403 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120228 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120528 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120619 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120718 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150727 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5047529 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |