JP5041285B2 - 高周波部品 - Google Patents

高周波部品 Download PDFInfo

- Publication number

- JP5041285B2 JP5041285B2 JP2007114657A JP2007114657A JP5041285B2 JP 5041285 B2 JP5041285 B2 JP 5041285B2 JP 2007114657 A JP2007114657 A JP 2007114657A JP 2007114657 A JP2007114657 A JP 2007114657A JP 5041285 B2 JP5041285 B2 JP 5041285B2

- Authority

- JP

- Japan

- Prior art keywords

- balanced

- multilayer substrate

- terminal

- ground

- signal terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Waveguide Switches, Polarizers, And Phase Shifters (AREA)

- Surface Acoustic Wave Elements And Circuit Networks Thereof (AREA)

- Transceivers (AREA)

Description

ところで弾性波フィルタは不平衡入出力型フィルタがほとんどであったが、欧州地域をはじめとして広く適用されているEGSM900やDCS1800等の携帯電話機では、雑音指数を下げ、受信感度を上げるように、増幅器・ミキサ等の回路部品で平衡型のものが用いられている。これに伴い、前記回路部品と接続する弾性波フィルタも入力及び/又は出力が平衡型であるものが用いられるようになってきている。

弾性表面波素子3の不平衡入力ポートや平衡出力ポートは、前記接続線路を介して前記多層基板の底面に設けられた高周波端子(不平衡信号入力端子20a、平衡信号出力端子20c)と接続し、グランドポートは同様に接続線路を介して多層基板の底面に設けられたグランド端子(図示せず)と接続する。

そこで本発明は、弾性波フィルタに用いる多層基板の構造に起因する位相特性の劣化を改善し、優れた電気的特性を有する弾性波フィルタや複合部品を提供することを目的とする。

このような構成により、不平衡信号端子と平衡信号端子との間の干渉を防ぐことができる。また、平衡信号端子間には位相特性の劣化を防ぐため、グランド端子を設けないのが好ましい。

本発明においては、弾性波素子は少なくとも一対の平衡ポートを有するものであり、前記各平衡ポートから各平衡信号端子までの経路の電気長を実質的に等しくすることにより、位相特性の劣化を防ぐことができる。

また、前記平衡信号端子と前記平衡ポートとは、積層方向に連続するビアホール群を介して接続するのが好ましく、前記平衡信号端子と前記平衡ポートとの間の経路が、グランド電極と重なり合わないことで、平面的に配置された他の電極パターンとの干渉を抑えることが出来る。

複数のグランド電極と、それらを電気的に接続するビアホール群で囲まれた領域に、整合回路やフィルタ回路を設け、その外領域に平衡信号端子と平衡ポートとを接続する経路を設けるのが好ましい。

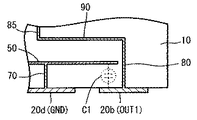

しかしながら試作を繰り返して行く内に、多層基板の構成によって位相特性にばらつきが生じることが判明した。図9は最底面側にグランド電極を形成した多層基板の部分拡大断面図である。また図10はその多層基板を用いて構成された弾性波フィルタの回路ブロック図である。鋭意研究の結果、グランド電極50と高周波端子のうちの平衡信号出力端子20b、20c等とが、積層方向で重なり合いって生じた寄生容量C1,C2により、接続線路の電気長にばらつきが生じたことが分かった。グランド電極50と平衡信号出力端子20b、20cは例えば数十μm〜50μmの間隔をもって配置され、その間は比誘電率が5〜30程度の誘電体が占める。このため高周波においては無視できない程度のキャパシタンス(寄生容量)が接続線路80とグランドとの間に接続され、また形成される寄生容量C1,C2も一様では無い。

そこで上記問題を鑑みて、多層基板の最も底面側に実質的にグランド電極のみを形成し、ビアホールを除く接続線路を形成しない構成とするとともに、更に前記グランド電極と平衡信号出力端子20b、20cとを積層方向に重ね合わせない構成とすることを着想した。

多層基板10の内部には、電極パターン(ラインパターンやビアホール)で形成された接続線路70,80,85,90が形成され、多層基板10の上面部には弾性表面波素子(図示せず)が搭載され、この多層基板10の上面側に、弾性表面波素子を気密封止するエポキシ樹脂などの樹脂部材15を備えている。

弾性表面波素子の不平衡入力ポートや平衡出力ポートは、前記接続線路を介して矩形に形成された多層基板の底面に設けられた高周波端子(不平衡信号入力端子20a、平衡信号出力端子20c)と接続し、グランドポートは同様に接続線路とグランド電極50を介して多層基板の底面に設けられたグランド端子(20d)と接続する。前記グランド端子(20d)は、多層基板の対向する側面に、それぞれ形成された不平衡信号入力端子20aと平衡信号出力端子20cの間に配置されている。本実施例においては、グランド端子を帯状の電極パターンで形成しているが、他の高周波端子と同形状の電極パターンとし、複数の電極パターンを、平衡信号出力端子間を除く他の側面側等の異なる位置に設けて形成しても良い。

グランド電極は平衡信号出力端子と積層方向に重なり合わないが、絶縁層面に広がって形成されているため、その上層に設けられた伝送線路が実装基板の電極パターンと干渉するのを防ぐ。また平衡信号出力端子との重なりを除く構成によって、寄生容量の形成を抑え、位相特性が劣化することが無く、優れた電気的特性を得ることが出来る。

分波回路120は、前記第1通信方式の受信信号を通過させるローパスフィルタ120aと、前記第3通信方式の受信信号を通過させるハイパスフィルタ120bを並列に接続したものである。整合回路180、185、186、187、188、190は主としてインピーダンスマッチングのために用いられるが、高周波信号の位相調整のために用いられる場合もある。

フィルタ回路110,130,140、分波回路120、及び整合回路180、185、186、187、188、190はインダクタとコンデンサで構成されており、これらは、誘電体層と、AgやCu等の金属や前記金属をベースとする合金を用いてなるペーストを所定の形状に形成した電極パターンとで形成される多層基板に、前記電極パターンやチップ部品として構成される。

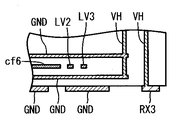

最下層のグリーンシート14の表面には、ほぼ全面を覆うアース用パターンGND(第1グランド電極)が形成されており、裏面には回路基板に実装するための端子電極が形成されている。前記端子電極は、各通信システム共通のアンテナポートANT(100a)と、第1の通信システムの送信信号が入力する第1送信ポートTX1(100b)と、第2、第3の通信システムの送信信号が入力する第2送信ポートTX2(100c)と、第1の通信システムが出力する受信ポートRX1(100d、100d2)と,第3の通信システムが出力する受信ポートRX2(100e1、100e2)と,第2の通信システムが出力する受信ポートRX3(100f1,100f2)と,第4の通信システムが入出力する送受信ポートTRX(100g)と、グランドポートGNDと、スイッチ回路制御用のコントロールポート(制御端子)V1,V2,V3,Vddを有し、それぞれがグリーンシートに形成されたビアホール(図中、黒丸、黒四角で表示)を介して上層のグリーンシート上の電極パターンと接続される。

前記スイッチ回路制御用のコントロールポートV1,V2,V3,Vddは、多層基板の一側面に側に集められており、積層方向に連続するビアホールと、グリーンシート13上に並行して走るラインパターン(制御信号用線路)を介して前記第1の主面に形成された複数のデコーダ用実装電極と接続される。また同じ層にはフィルタ回路や整合回路を構成するコンデンサ用電極パターンが形成されている。

各電極パターンは適宜ビアホールを介して適宜接続され、得られた積層体を850℃〜1000℃程度(用いる導体や誘電体セラミクスによる)で焼結して多層基板とし、これにFETスイッチやSAWフィルタを実装して本発明に係るスイッチモジュールとした。

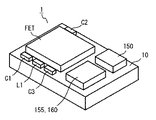

本実施例においては、更にDCカットコンデンサC1〜C3、ESD対策回路のインダクタL1、コンデンサC1(コンデンサC1はDCカットと共用)を積層基板上に実装している。なお、これらのインダクタやコンデンサを積層基板内に電極パターンで形成することも可能であるが、他の回路素子と比べて、比較的大きな容量値、インダクタンス値が必要となるので、専らチップ部品として積層基板上に実装する場合が多い。

図8に多層基板10の部分断面拡大図を示す。前記SAWフィルタの平衡出力ポートと接続する実装電極は、多層基板の裏面に形成された高周波端子のうちの平衡出力端子RX3と、積層方向に連続する第1ビアホール群を介して接続されている。図示していないが他の平衡出力端子も同様に、それぞれが他の第1ビアホール群を介してSAWフィルタの平衡出力ポートと接続する。またグランド電極は平衡出力端子と積層方向に重なり合わない構成によりフェイズバランスやアンプリチュードバランス等の位相特性を損ねることが無い。更に前記第1ビアホール群と前記制御信号用線路との間には、面内に縦列し、積層方向に連続した第2ビアホール群が形成され、第1グランド電極〜第4グランド電極の間を接続している。このような構成により、ノイズの影響を受け易い受信信号の経路を、制御信号の経路、送信信号の経路から分離して配置することで、更に優れた挿入損失特性を得ることが出来た。

110,130,140 フィルタ回路

115 FETスイッチ

120 ESD対策回路

150,155,160 SAWフィルタ

180、185、186、187、190 整合回路

120 分波回路

Claims (2)

- 多層基板に平衡出力の弾性波素子とスイッチング素子を実装し、前記多層基板の底面にグランド端子と高周波端子を備え、前記スイッチング素子で構成された高周波スイッチ回路に分波回路が接続され、前記分波回路には前記弾性波素子でなる複数の弾性波フィルタが接続されており、

前記スイッチング素子及び前記弾性波素子の下部であって、前記多層基板の内層には、異なる層に形成され、ビアホールを介して接続された複数のグランド電極を有し、前記グランド電極間には、前記分波回路を構成するリアクタンス素子用の電極パターンを含み、

前記高周波端子は少なくとも平衡信号端子と不平衡信号端子を有し、前記平衡信号端子は各弾性波素子の平衡ポートと前記多層基板に設けられた接続線路を介して接続し、前記多層基板の底面の一側面側にのみに並設され、

前記多層基板の内層において、前記平衡信号端子と積層方向に重なる部位には、前記接続線路のみが設けられ、前記グランド電極は、前記平衡信号端子と、前記多層基板の表面に形成された弾性波素子の平衡ポートと接続する実装電極とに積層方向に重なり合わないことを特徴とする高周波部品。 - 前記平衡信号端子が位置する底面の一側面側と対向する側面側に、アンテナ端子を含む前記不平衡信号端子が位置し、前記グランド電極の内、底面側のグランド電極とビアホールを介して接続されたグランド端子が、前記平衡信号端子と前記不平衡信号端子との間に挟まれた中央の領域と不平衡信号端子が配置された側面側を除く側面側に分かれて配置されたことを特徴とする請求項1に記載の高周波部品。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007114657A JP5041285B2 (ja) | 2007-04-24 | 2007-04-24 | 高周波部品 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007114657A JP5041285B2 (ja) | 2007-04-24 | 2007-04-24 | 高周波部品 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008271421A JP2008271421A (ja) | 2008-11-06 |

| JP2008271421A5 JP2008271421A5 (ja) | 2010-04-30 |

| JP5041285B2 true JP5041285B2 (ja) | 2012-10-03 |

Family

ID=40050304

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007114657A Expired - Fee Related JP5041285B2 (ja) | 2007-04-24 | 2007-04-24 | 高周波部品 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5041285B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009089165A (ja) * | 2007-10-01 | 2009-04-23 | Murata Mfg Co Ltd | 高周波モジュール |

| JP5273861B2 (ja) | 2009-04-22 | 2013-08-28 | 太陽誘電株式会社 | 通信モジュール |

| CN103026622B (zh) * | 2010-07-27 | 2015-06-17 | 株式会社村田制作所 | 高频模块 |

| WO2018043206A1 (ja) * | 2016-09-05 | 2018-03-08 | 株式会社村田製作所 | Lcフィルタ、高周波フロントエンド回路および通信装置 |

| JP6661521B2 (ja) | 2016-12-05 | 2020-03-11 | 太陽誘電株式会社 | フィルタおよびマルチプレクサ |

| JP6729790B2 (ja) * | 2017-03-14 | 2020-07-22 | 株式会社村田製作所 | 高周波モジュール |

| WO2019150787A1 (ja) * | 2018-02-01 | 2019-08-08 | 株式会社村田製作所 | フィルタモジュールおよび高周波モジュール |

| EP3809519A4 (en) * | 2018-06-12 | 2022-06-22 | KMW Inc. | CAVITY FILTER AND CONNECTION STRUCTURE |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3869919B2 (ja) * | 1997-11-05 | 2007-01-17 | Tdk株式会社 | 弾性表面波装置 |

| JP2002118487A (ja) * | 2000-10-06 | 2002-04-19 | Matsushita Electric Ind Co Ltd | 高周波複合スイッチモジュール |

| JP4532825B2 (ja) * | 2000-11-01 | 2010-08-25 | 日立金属株式会社 | 高周波スイッチモジュール |

| JP3729396B2 (ja) * | 2001-11-01 | 2005-12-21 | 日立金属株式会社 | 高周波部品 |

| JP2003304139A (ja) * | 2002-02-07 | 2003-10-24 | Ngk Spark Plug Co Ltd | 弾性表面波分波器用パッケージ及び弾性表面波分波器用パッケージの製造方法 |

| JP3911426B2 (ja) * | 2002-02-26 | 2007-05-09 | 京セラ株式会社 | 弾性表面波フィルタ用パッケージおよび弾性表面波フィルタ装置 |

| JP2004080233A (ja) * | 2002-08-14 | 2004-03-11 | Murata Mfg Co Ltd | 分波器 |

| JP2004166258A (ja) * | 2002-10-25 | 2004-06-10 | Hitachi Metals Ltd | 平衡−不平衡型マルチバンドフィルタモジュール |

| JP3967289B2 (ja) * | 2003-04-30 | 2007-08-29 | 富士通メディアデバイス株式会社 | 分波器及び電子装置 |

| JP4323972B2 (ja) * | 2004-01-30 | 2009-09-02 | 三星電子株式会社 | 変調回路及び変調方法 |

| EP1729413B1 (en) * | 2004-03-16 | 2015-12-09 | Hitachi Metals, Ltd. | High-frequency circuit and high-frequency component |

| JP4412123B2 (ja) * | 2004-09-09 | 2010-02-10 | エプソントヨコム株式会社 | 表面弾性波デバイス |

| JP4091043B2 (ja) * | 2004-12-22 | 2008-05-28 | 富士通メディアデバイス株式会社 | 分波器 |

| JP4601415B2 (ja) * | 2004-12-24 | 2010-12-22 | 京セラ株式会社 | 弾性表面波装置および通信装置 |

| ATE552657T1 (de) * | 2004-12-28 | 2012-04-15 | Murata Manufacturing Co | Symmetrisches/unsymmetrisches filtermodul und kommunikationsvorrichtung |

| JP4446922B2 (ja) * | 2005-04-21 | 2010-04-07 | 富士通メディアデバイス株式会社 | フィルタおよび分波器 |

-

2007

- 2007-04-24 JP JP2007114657A patent/JP5041285B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008271421A (ja) | 2008-11-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4324807B2 (ja) | 高周波スイッチモジュール | |

| JP5316544B2 (ja) | 高周波回路、高周波部品、及びマルチバンド通信装置 | |

| JP5029946B2 (ja) | スイッチモジュール | |

| JP5041285B2 (ja) | 高周波部品 | |

| US7924118B2 (en) | Duplexer and elastic wave device | |

| JP2003198325A (ja) | 分波器、通信装置 | |

| JP5630697B2 (ja) | 電子部品 | |

| JP5796579B2 (ja) | フィルタ及びバランを備えた積層体型電子部品 | |

| JP2001211097A (ja) | マルチバンド用高周波スイッチモジュール | |

| JP2005268878A (ja) | アンテナ共用器 | |

| JP4702622B2 (ja) | スイッチモジュール | |

| JP2010147589A (ja) | 高周波回路、高周波部品及び通信装置 | |

| JP3729396B2 (ja) | 高周波部品 | |

| US11075658B2 (en) | Multilayer substrate, filter, multiplexer, radio-frequency front-end circuit, and communication device | |

| US20040012461A1 (en) | High-frequency device and communication apparatus | |

| JP2003142981A5 (ja) | ||

| JP4936119B2 (ja) | 積層型バラントランス及び高周波部品 | |

| JP4678572B2 (ja) | 積層型バラントランス及びそれを用いた高周波スイッチモジュール | |

| JP5549820B2 (ja) | トリプレクサ | |

| JP4794247B2 (ja) | 高周波モジュール | |

| JP2006279553A (ja) | 高周波スイッチングモジュール及び無線通信装置 | |

| WO2022230708A1 (ja) | 高周波回路及び通信装置 | |

| JP2010136288A (ja) | バンドパスフィルタ、高周波部品および通信装置 | |

| JP2005167624A (ja) | 積層型電子部品、無線装置 | |

| JP2009159412A (ja) | 高周波部品及び通信装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100315 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120224 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120424 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120615 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120628 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5041285 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150720 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |