JP4948784B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4948784B2 JP4948784B2 JP2005147088A JP2005147088A JP4948784B2 JP 4948784 B2 JP4948784 B2 JP 4948784B2 JP 2005147088 A JP2005147088 A JP 2005147088A JP 2005147088 A JP2005147088 A JP 2005147088A JP 4948784 B2 JP4948784 B2 JP 4948784B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- region

- layer

- base region

- type sic

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

- H10D12/031—Manufacture or treatment of IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/149—Source or drain regions of field-effect devices

- H10D62/151—Source or drain regions of field-effect devices of IGFETs

- H10D62/156—Drain regions of DMOS transistors

- H10D62/157—Impurity concentrations or distributions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

Landscapes

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

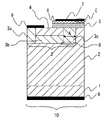

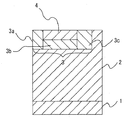

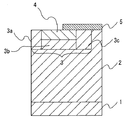

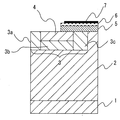

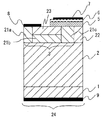

以下、本発明の実施の形態1におけるSiCを用いたMOSFETと、その製造方法について説明する。図1は実施の形態1におけるMOSFETの断面図である。実際のMOSFETの構成は、図1の断面構造の右側辺を軸にして左右対称に折り返した構造を複数個横に並べて、同種類の電極を並列に接続した構成となる。

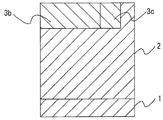

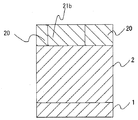

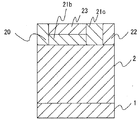

実施の形態1においては、n型SiCドリフト層2にp型SiCベース領域3とn型SiCソース領域4とをイオン注入によってMOSFETを製造する方法を示した。実施の形態2では、MOSFETの別な製造方法について、図10〜16に基づいて説明する。

Claims (7)

- 第1導電型の半導体基板と、

前記半導体基板の主表面上に形成された第1導電型のドリフト層と、

前記ドリフト層の表層部の所定箇所に形成され、所定深さを有する第2導電型のベース領域と、

前記ベース領域の表層部の所定箇所に形成され、前記ベース領域の深さよりも浅い第1導電型のソース領域と、

前記ソース領域と前記ドリフト層の表面上に形成され、前記ソース領域と前記ドリフト層とを接続する、前記ドリフト層と同じ半導体材料である第2導電型のチャネル層と、

前記チャネル層の表面上に形成された絶縁膜と、

前記絶縁膜の表面上に形成されたゲート電極と、

前記ベース領域と前記ソース領域の表面上に形成されたソース電極と、

前記半導体基板の下面に形成されたドレイン電極とより構成され、

前記チャネル層がエピタキシャル成長により形成され、その表面が平坦となることを特徴とする

半導体装置。 - 第1導電型がn型半導体であり、第2導電型がp型半導体であることを特徴とする請求項1記載の半導体装置。

- 第2導電型のベース領域と、第1導電型のソース領域とが自己整合的に形成されたことを特徴とする請求項1記載の半導体装置。

- 第1導電型のドリフト層のうち、第2導電型のべース領域が形成されない第1導電型のデプレッション領域の不純物濃度を前記ドリフト層よりも高めたことを特徴とする請求項1記載の半導体装置。

- 請求項1乃至4のいずれか1項に記載の半導体装置を複数個備え、前記複数個の半導体装置の各同一電極が並列に接続されたことを特徴とする半導体装置。

- 第1導電型の半導体基板の主表面上に第1導電型のドリフト層を形成する工程と、

前記ドリフト層の表層部の所定箇所に、所定深さを有する第2導電型のベース領域を形成する工程と、

前記ベース領域の表層部の所定箇所に、前記ベース領域の深さよりも浅い第1導電型のソース領域を形成する工程と、

前記ソース領域と前記ドリフト層との表面上に、前記ドリフト層と同じ半導体材料である第2導電型のチャネル層をエピタキシャル成長により形成する工程とを備えたことを特徴とする半導体装置の製造方法。 - 第1導電型の半導体基板の主表面上に第1導電型のドリフト層を形成する工程と、

前記ドリフト層の全面に第2導電型の層を形成する工程と、

前記第2導電型の層の表層部の所定箇所に、所定深さを有し、前記第2導電型の層よりも高濃度の第2導電型のベース領域を形成する工程と、

前記ベース領域の表層部の所定箇所に、前記ベース領域の深さよりも浅い第1導電型のソース領域を形成する工程と、

前記第2導電型の層の表層部の所定箇所に、不純物濃度を高めた第1導電型のデプレッション領域を形成する工程と、

前記第2導電型の層の表層部の前記デプレッション領域と前記ソース領域とが形成されていない所定箇所に、ソース電極と接触し、前記ベース領域よりも不純物濃度を高めた領域を形成する工程と、

前記ソース領域と前記デプレッション領域との表面上に、前記ドリフト層と同じ半導体材料である第2導電型のチャネル層をエピタキシャル成長により形成する工程とを備えたことを特徴とする半導体装置の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005147088A JP4948784B2 (ja) | 2005-05-19 | 2005-05-19 | 半導体装置及びその製造方法 |

| DE112006001280.0T DE112006001280B4 (de) | 2005-05-19 | 2006-02-14 | Halbleitervorrichtung und Verfahren zu deren Herstellung |

| US11/908,530 US7829898B2 (en) | 2005-05-19 | 2006-02-14 | Power semiconductor device having raised channel and manufacturing method thereof |

| PCT/JP2006/302516 WO2006123458A1 (ja) | 2005-05-19 | 2006-02-14 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005147088A JP4948784B2 (ja) | 2005-05-19 | 2005-05-19 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006324517A JP2006324517A (ja) | 2006-11-30 |

| JP2006324517A5 JP2006324517A5 (ja) | 2008-06-05 |

| JP4948784B2 true JP4948784B2 (ja) | 2012-06-06 |

Family

ID=37431041

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005147088A Expired - Lifetime JP4948784B2 (ja) | 2005-05-19 | 2005-05-19 | 半導体装置及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7829898B2 (ja) |

| JP (1) | JP4948784B2 (ja) |

| DE (1) | DE112006001280B4 (ja) |

| WO (1) | WO2006123458A1 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5560519B2 (ja) * | 2006-04-11 | 2014-07-30 | 日産自動車株式会社 | 半導体装置及びその製造方法 |

| DE112010000882B4 (de) * | 2009-02-24 | 2015-03-19 | Mitsubishi Electric Corporation | Siliziumkarbid-Halbleitervorrichtung |

| US8742427B2 (en) * | 2010-10-29 | 2014-06-03 | Panasonic Corporation | Semiconductor element |

| JP2012253108A (ja) * | 2011-06-01 | 2012-12-20 | Sumitomo Electric Ind Ltd | 炭化珪素半導体装置およびその製造方法 |

| CN109585541B (zh) * | 2018-12-27 | 2024-03-26 | 西安中车永电电气有限公司 | 一种埋沟式SiC IGBT常关器件及其制备方法 |

| US12272745B2 (en) * | 2020-04-14 | 2025-04-08 | National Institute Of Advanced Industrial Science And Technology | Semiconductor device |

| EP4310920A1 (en) * | 2022-07-22 | 2024-01-24 | Nexperia B.V. | A vertical oriented semiconductor device comprising well regions having two lateral doping gradients at different depths and a corresponding manufacturing method |

| EP4310919A1 (en) * | 2022-07-22 | 2024-01-24 | Nexperia B.V. | A vertical oriented semiconductor device comprising well regions having a lateral doping gradient and corresponding manufacturing method |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5561302A (en) * | 1994-09-26 | 1996-10-01 | Motorola, Inc. | Enhanced mobility MOSFET device and method |

| US6573534B1 (en) | 1995-09-06 | 2003-06-03 | Denso Corporation | Silicon carbide semiconductor device |

| JP3385938B2 (ja) | 1997-03-05 | 2003-03-10 | 株式会社デンソー | 炭化珪素半導体装置及びその製造方法 |

| JP3461274B2 (ja) * | 1996-10-16 | 2003-10-27 | 株式会社東芝 | 半導体装置 |

| US6281521B1 (en) * | 1998-07-09 | 2001-08-28 | Cree Research Inc. | Silicon carbide horizontal channel buffered gate semiconductor devices |

| JP3428459B2 (ja) | 1998-09-01 | 2003-07-22 | 富士電機株式会社 | 炭化けい素nチャネルMOS半導体素子およびその製造方法 |

| JP2000323583A (ja) * | 1999-05-13 | 2000-11-24 | Miyazaki Oki Electric Co Ltd | 半導体装置 |

| JP2001257347A (ja) * | 2000-03-10 | 2001-09-21 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JP4802378B2 (ja) | 2001-03-12 | 2011-10-26 | 株式会社デンソー | 炭化珪素半導体装置の製造方法 |

| JP4876321B2 (ja) * | 2001-03-30 | 2012-02-15 | 株式会社デンソー | 炭化珪素半導体装置の製造方法 |

| US7217950B2 (en) * | 2002-10-11 | 2007-05-15 | Nissan Motor Co., Ltd. | Insulated gate tunnel-injection device having heterojunction and method for manufacturing the same |

| JP3580304B2 (ja) * | 2002-10-11 | 2004-10-20 | 日産自動車株式会社 | 炭化珪素半導体装置及びその製造方法 |

| EP1566843B1 (en) * | 2002-10-18 | 2013-12-18 | National Institute of Advanced Industrial Science and Technology | Manufacturing method of a silicon carbide semiconductor device |

| JP2004146626A (ja) * | 2002-10-25 | 2004-05-20 | Toshiba Corp | 半導体装置 |

| US7221010B2 (en) * | 2002-12-20 | 2007-05-22 | Cree, Inc. | Vertical JFET limited silicon carbide power metal-oxide semiconductor field effect transistors |

| JP4020196B2 (ja) * | 2002-12-25 | 2007-12-12 | 三菱電機株式会社 | 半導体素子の製造方法 |

| JP2004247545A (ja) * | 2003-02-14 | 2004-09-02 | Nissan Motor Co Ltd | 半導体装置及びその製造方法 |

| JP4193596B2 (ja) | 2003-06-09 | 2008-12-10 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2005033030A (ja) | 2003-07-07 | 2005-02-03 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2005116896A (ja) * | 2003-10-09 | 2005-04-28 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

-

2005

- 2005-05-19 JP JP2005147088A patent/JP4948784B2/ja not_active Expired - Lifetime

-

2006

- 2006-02-14 DE DE112006001280.0T patent/DE112006001280B4/de not_active Expired - Lifetime

- 2006-02-14 WO PCT/JP2006/302516 patent/WO2006123458A1/ja not_active Ceased

- 2006-02-14 US US11/908,530 patent/US7829898B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US7829898B2 (en) | 2010-11-09 |

| DE112006001280B4 (de) | 2016-08-18 |

| JP2006324517A (ja) | 2006-11-30 |

| WO2006123458A1 (ja) | 2006-11-23 |

| US20090020834A1 (en) | 2009-01-22 |

| DE112006001280T5 (de) | 2008-03-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8354715B2 (en) | Semiconductor device and method of fabricating the same | |

| JP3620513B2 (ja) | 炭化珪素半導体装置 | |

| JP7786512B2 (ja) | 半導体装置 | |

| JP6021032B2 (ja) | 半導体素子およびその製造方法 | |

| US8563988B2 (en) | Semiconductor element and manufacturing method therefor | |

| JP4900662B2 (ja) | ショットキーダイオードを内蔵した炭化ケイ素mos電界効果トランジスタおよびその製造方法 | |

| US8748977B2 (en) | Semiconductor device and method for producing same | |

| WO2011027540A1 (ja) | 半導体素子およびその製造方法 | |

| JP6183087B2 (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| JP6802454B2 (ja) | 半導体装置およびその製造方法 | |

| JP3826828B2 (ja) | 炭化珪素半導体を用いた電界効果トランジスタ | |

| WO2014083771A1 (ja) | 半導体素子及びその製造方法 | |

| JP5556863B2 (ja) | ワイドバンドギャップ半導体縦型mosfet | |

| JP6862782B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP5547022B2 (ja) | 半導体装置 | |

| JP5145694B2 (ja) | SiC半導体縦型MOSFETの製造方法。 | |

| JP4948784B2 (ja) | 半導体装置及びその製造方法 | |

| JP7755242B2 (ja) | 炭化珪素半導体装置および炭化珪素半導体装置の製造方法 | |

| JP7765318B2 (ja) | 半導体装置 | |

| WO2015076020A1 (ja) | 半導体装置 | |

| WO2015111177A1 (ja) | 半導体装置,パワーモジュール,電力変換装置,および鉄道車両 | |

| CN103548142B (zh) | 半导体元件、半导体装置、及其制造方法 | |

| JP5098293B2 (ja) | ワイドバンドギャップ半導体を用いた絶縁ゲート型半導体装置およびその製造方法 | |

| CN101233618B (zh) | 半导体装置及其制造方法 | |

| JP2003347548A (ja) | 炭化珪素半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080212 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110913 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20111017 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111028 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120130 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120306 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120307 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150316 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4948784 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |