JP4887346B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4887346B2 JP4887346B2 JP2008297134A JP2008297134A JP4887346B2 JP 4887346 B2 JP4887346 B2 JP 4887346B2 JP 2008297134 A JP2008297134 A JP 2008297134A JP 2008297134 A JP2008297134 A JP 2008297134A JP 4887346 B2 JP4887346 B2 JP 4887346B2

- Authority

- JP

- Japan

- Prior art keywords

- island

- semiconductor device

- sealing resin

- semiconductor chip

- back surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1305—Bipolar Junction Transistor [BJT]

- H01L2924/13055—Insulated gate bipolar transistor [IGBT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

Description

樹脂モールドされた半導体装置は、通常、ガラスエポキシ基板等のプリント基板に実装され、同じくプリント基板上に実装された他の素子と電気的に接続することにより、所望の回路網を構成する。この時、リード端子3が樹脂5の外部に導出された半導体装置では、リード端子3の先端から先端までの距離10(図10(B)図示)を実装面積として占有するので、実装面積が大きいという欠点がある。

金型内に設置したときのリードフレームとキャビティ9との位置合わせ精度はプラス・マイナス50μ程度が限界である。このため、アイランド2の大きさは前記合わせ精度を考慮した大きさに設計しなければならない。従って、合わせ精度の問題は、パッケージの外形寸法に対するアイランド2の寸法を小さくし、これがパッケージの外形寸法に対して収納可能な半導体チップ1の最大寸法に制限を与えていた。

半導体装置を実装基板上に実装するときは、前記実装基板上に形成したプリント配線とリード端子3とを半田で固着するが、この時半田がどの程度まで盛り上がるか(半田フィレットがどこまで盛り上がるか)によって半導体装置の固着強度が大きく左右される。半導体装置を微細化した場合であっても、この固着強度は維持しなければならないという課題がある。

お互いが対向する第1の側辺および第2の側辺と、および前記第1の側辺および第2の側辺と角部を成し、お互いが対向する第3の側辺および第4の側辺から成るCuを主材料とした矩形のアイランドと、

前記第1の側辺および前記第2の側辺に設けられ、前記アイランドと一体で同一材料から成る第1の突起部および第2の突起部と、

前記第3の側辺から前記アイランドと一体で同一材料から成る第3の突起部と、

前記第4の側辺に一端が近接して設けられたCuを主材料とする複数のリード端子と、

前記アイランドに電気的に接続されて設けられた半導体チップと、

前記半導体チップ表面に設けられた電極と前記リード端子とを電気的に接続する金属細線と、

前記アイランド、前記第1〜第3の突起部、前記半導体チップ、前記複数のリード端子を封止し、表面、前記表面と対向する裏面、前記表面と前記裏面の周囲から延在する4側面から成る6面体の封止樹脂と、

前記封止樹脂の側面には、前記第1〜第3の突起部および前記複数のリードが延在して成る半導体装置をもって解決するものである。

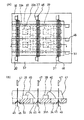

先ず、リードフレーム30を準備する。図1(A)はリードフレーム30の平面図であり、図1(B)は図1(A)のAA断面図である。

次に、リードフレーム30に対してダイボンド工程とワイヤボンド工程を行う。図2(B)は図2(A)のAA線断面図である。

次に、全体を樹脂モールドする。図3(B)は図3(A)のAA線断面図である。

次に、リードフレーム30の裏面側の樹脂41を部分的に除去してスリット孔42を形成する。図4(B)は図4(A)のAA線断面図である。

第4工程で形成したスリット孔42に沿って、第2のスリット孔42aを形成する。

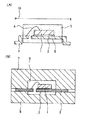

スリット孔42、42aを形成したことにより露出させたリード端子34の表面に半田メッキ等のメッキ層45を形成する。このメッキ層45は、リードフレーム30を電極の一方とする電解メッキ法により行われる。スリット孔42、42aはリード端子34の板厚の全部を切断していないので、アイランド33とリード端子34は未だ電気的な導通が保たれている。更に各アイランド33が連結バー35によって枠体32に共通接続されている。このように露出した金属表面のすべてが電気的に導通しているので、一回のメッキ工程でメッキ層45を形成することができる。

次に、素子搭載部31毎に樹脂層41を切断して各々の素子A、素子B、素子C・・・を分離する。即ち、アイランド33とこの上に固着された半導体チップ39に接続されたリード端子34を囲む領域(同図の切断ライン46)で切断することにより、素子搭載部31毎に分割した半導体装置を形成する。切断にはダイシング装置が用いられ、ダイシング装置のブレード47によって樹脂層41とリードフレーム30とを同時に切断する。スリット孔42が位置する箇所では、少なくともスリット孔42aの傾斜した側壁に付着したメッキ層45を残すように形成する。この様に残存させたメッキ層45は、半導体装置をプリント基板上に実装する際に利用される。また、切断したリード端子34の他方はア

イランド33に連続する突起部33aとして残存し、切断した連結バー35はアイランド33に連続する突起部33bとして残存する。切断されたリード端子34及び突起部33a、33bの切断面は、樹脂層41の切断面と同一平面を形成し、該同一平面に露出する。ダイシング工程においては裏面側(スリット孔42を設けた側)にブルーシート(たとえば、商品名:UVシート、リンテック株式会社製)を貼り付け、前記ダイシングブレード47がブルーシートの表面に到達するような切削深さで切断する。この時に、あらかじめ形成した合わせマーク37をダイシング装置側で自動認識し、これを位置基準として用いてダイシングする。本実施の形態では、合わせマーク37を長方形の形状とし、該長方形の長辺を基準位置とした。更に、ダイシングブレードの板厚は第2のスリット孔42aの幅よりも薄い(例えば、幅0.1mm)ものを用い、スリット孔42の中心線に沿って、ダイシングブレード47がリード端子33の凹部36上を通過するようにダイシングした。これで、切断後のリード端子33の先端部が先細りの形状となり、樹脂41から容易には抜け落ちない形状に加工できる。

Claims (5)

- お互いが対向する第1の側辺および第2の側辺と、および前記第1の側辺および第2の側辺と角部を成し、お互いが対向する第3の側辺および第4の側辺から成るCuを主材料とした矩形のアイランドと、

前記第1の側辺および第2の側辺に設けられ、前記アイランドと一体で同一材料から成る第1の突起部および第2の突起部と、

前記第3の側辺から前記アイランドと一体で同一材料から成る第3の突起部と、

前記第4の側辺に一端が近接して設けられたCuを主材料とする複数のリード端子と、

前記アイランドに電気的に接続されて設けられた半導体チップと、

前記半導体チップ表面に設けられた電極と前記リード端子とを電気的に接続する金属細線と、

前記アイランド、前記第1〜第3の突起部、前記半導体チップ、前記複数のリード端子を封止し、表面、前記表面と対向する裏面、前記表面と前記裏面の周囲から延在する4側面から成る6面体の封止樹脂と、

前記封止樹脂の側面に、前記第1〜第3の突起部および前記複数のリード端子が延在され、前記アイランドは、前記封止樹脂の側面から内側に後退して成り、

前記第3の突起部及び前記リード端子は、前記封止樹脂の裏面から露出することなく、

前記封止樹脂は、前記第3の突起部が延在する前記側面と前記裏面との間であり、前記裏面に対して前記表面側に傾斜する第1の傾斜面と、前記リード端子が延在する前記側面と前記裏面との間であり、前記裏面に対して前記表面側に傾斜する第2の傾斜面とを有し、

前記第1の傾斜面から露出する前記第3の突起部及び前記第2の傾斜面から露出する前記リード端子にはメッキ層が形成される事を特徴とした半導体装置。 - 前記アイランドは、前記封止樹脂の裏面から露出することなく、前記第1及び前記第2の突起部は、前記封止樹脂の側面から露出する請求項1に記載の半導体装置。

- 前記アイランドに搭載される半導体チップは、3端子のトランジスタ、BIP型の集積回路またはMOS型の集積回路である請求項1または請求項2に記載の半導体装置。

- 前記アイランドには、複数の半導体チップが設けられる請求項1または請求項2に記載の半導体装置。

- 前記3端子のトランジスタは、前記アイランドと前記トランジスタの裏面が電気的に接続され、電流が前記トランジスタの縦方向に流れる請求項3に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008297134A JP4887346B2 (ja) | 2008-11-20 | 2008-11-20 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008297134A JP4887346B2 (ja) | 2008-11-20 | 2008-11-20 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006243624A Division JP4383436B2 (ja) | 2006-09-08 | 2006-09-08 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009049435A JP2009049435A (ja) | 2009-03-05 |

| JP2009049435A5 JP2009049435A5 (ja) | 2010-04-30 |

| JP4887346B2 true JP4887346B2 (ja) | 2012-02-29 |

Family

ID=40501297

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008297134A Expired - Fee Related JP4887346B2 (ja) | 2008-11-20 | 2008-11-20 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4887346B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10388616B2 (en) | 2016-05-02 | 2019-08-20 | Rohm Co., Ltd. | Semiconductor device and method for manufacturing the same |

| JP6752639B2 (ja) | 2016-05-02 | 2020-09-09 | ローム株式会社 | 半導体装置の製造方法 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62150868A (ja) * | 1985-12-25 | 1987-07-04 | Hitachi Micro Comput Eng Ltd | 半導体装置用リ−ドフレ−ムとそれを使用する樹脂封止方法 |

| JP3304705B2 (ja) * | 1995-09-19 | 2002-07-22 | セイコーエプソン株式会社 | チップキャリアの製造方法 |

| JP3209696B2 (ja) * | 1996-03-07 | 2001-09-17 | 松下電器産業株式会社 | 電子部品の製造方法 |

| JP3877402B2 (ja) * | 1997-11-28 | 2007-02-07 | 三洋電機株式会社 | 半導体装置の製造方法 |

-

2008

- 2008-11-20 JP JP2008297134A patent/JP4887346B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009049435A (ja) | 2009-03-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11145582B2 (en) | Method of manufacturing semiconductor devices with a paddle and electrically conductive clip connected to a leadframe and corresponding semiconductor device | |

| JP3819574B2 (ja) | 半導体装置の製造方法 | |

| JP3877401B2 (ja) | 半導体装置の製造方法 | |

| US6498392B2 (en) | Semiconductor devices having different package sizes made by using common parts | |

| JP4614586B2 (ja) | 混成集積回路装置の製造方法 | |

| JP4417150B2 (ja) | 半導体装置 | |

| US8592962B2 (en) | Semiconductor device packages with protective layer and related methods | |

| JP3877409B2 (ja) | 半導体装置の製造方法 | |

| US20130017652A1 (en) | Method of manufacturing a semiconductor device package with a heatsink | |

| JP3877410B2 (ja) | 半導体装置の製造方法 | |

| JP4784945B2 (ja) | 半導体装置の製造方法 | |

| JP3877405B2 (ja) | 半導体装置の製造方法 | |

| JP3877402B2 (ja) | 半導体装置の製造方法 | |

| JP4887346B2 (ja) | 半導体装置 | |

| JP3831504B2 (ja) | リードフレーム | |

| JP4987041B2 (ja) | 半導体装置の製造方法 | |

| JPH11307673A (ja) | 半導体装置とその製造方法 | |

| JP5086315B2 (ja) | 半導体装置の製造方法 | |

| US20210111108A1 (en) | Package with separate substrate sections | |

| JP2006279088A (ja) | 半導体装置の製造方法 | |

| JP4383436B2 (ja) | 半導体装置 | |

| JP4698658B2 (ja) | 半導体チップ搭載用の絶縁基板 | |

| WO2022202242A1 (ja) | 半導体装置、および、半導体装置の製造方法 | |

| JP5121807B2 (ja) | 半導体装置の製造方法 | |

| JP4723776B2 (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081212 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100311 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20110530 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110801 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111027 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111205 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111212 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141216 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141216 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141216 Year of fee payment: 3 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R360 | Written notification for declining of transfer of rights |

Free format text: JAPANESE INTERMEDIATE CODE: R360 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141216 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141216 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |