JP4842983B2 - 半導体光集積素子及びその作製方法 - Google Patents

半導体光集積素子及びその作製方法 Download PDFInfo

- Publication number

- JP4842983B2 JP4842983B2 JP2008033121A JP2008033121A JP4842983B2 JP 4842983 B2 JP4842983 B2 JP 4842983B2 JP 2008033121 A JP2008033121 A JP 2008033121A JP 2008033121 A JP2008033121 A JP 2008033121A JP 4842983 B2 JP4842983 B2 JP 4842983B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor

- waveguide

- integrated device

- modulator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Semiconductor Lasers (AREA)

Description

例えば、半導体レーザ及び半導体光変調器を、バットジョイント(以下、BJと略す。)法を用いて、同一基板上にモノリシック集積する場合には、半導体レーザ又は半導体光変調器のいずれか一方を結晶成長させ、半導体レーザ又は半導体光変調器のいずれか他方となる領域をエッチングし、そのエッチングした領域に半導体レーザ又は半導体光変調器のいずれか他方を結晶成長させるが、Al系半導体材料はサイドエッチ量が大きいため、結合部分となる部分もエッチングされてしまい、その後の結晶成長のときに、半導体レーザと半導体光変調器との結合部分に空孔が残ってしまう。そのため、半導体レーザと半導体光変調器がきれいに結合されず、その結合効率が劣化し、光出力を減少させることが問題となっていた。

例えば、BJ構造を形成する場合、結合部分となる部分の表面が酸化している状態でBJ法を行うと、その部分でうまく結晶成長が出来ず、空孔が残ってしまう。そのため、半導体レーザと半導体光変調器の結合効率が劣化し、光出力を減少させる原因となっていた。

同一の半導体基板上に、Alを含む半導体材料からなる活性層を備えるレーザ部光導波路とAlを含む半導体材料からなる変調器層を備える変調器部光導波路とをモノリシック集積した半導体光集積素子において、

前記活性層と前記変調器層との間に、Alを含まない半導体材料からなる半導体層を設けると共に、前記半導体層の上層に、前記活性層及び前記変調器層の上層にまで延設された、Alを含まない半導体材料からなる共通導波路層を設けることにより、前記レーザ部光導波路と前記変調器部光導波路との間に結合部光導波路を設け、

前記共通導波路層以上をリッジ構造に形成し、前記結合部光導波路のリッジ幅を、前記レーザ部光導波路及び前記変調器部光導波路のリッジ幅より大きくすると共に、前記リッジ構造の両側面を半絶縁性半導体材料により埋め込んだことを特徴とする。

上記第1の発明に記載の半導体光集積素子において、

Alを含まない半導体材料からなる窓構造部を、当該半導体光集積素子の端部に設け、

前記活性層及び前記変調器層の端面を前記窓構造部で覆って、空気中に露出しないようにしたことを特徴とする。

上記第1又は第2の発明に記載の半導体光集積素子において、

前記半絶縁性半導体材料がRuによりドープされていることを特徴とする。

上記第1〜第3の発明のいずれか1つに記載の半導体光集積素子において、

当該半導体光集積素子の発振波長を1.55μmとする場合、

前記共通導波路層の組成波長を1.0μm以上1.4μm以下としたことを特徴とする。

上記第4の発明に記載の半導体光集積素子において、

前記結合部光導波路のリッジ幅を1.0μm以上2.0μm未満の範囲としたことを特徴とする。

同一の半導体基板上に、Alを含む半導体材料からなる活性層を備えるレーザ部光導波路とAlを含む半導体材料からなる変調器層を備える変調器部光導波路とをモノリシック集積する半導体光集積素子の作製方法において、

前記半導体基板上に、前記活性層と前記変調器層とを隣接して形成すると共に、前記活性層と前記変調器層との隣接部分を除去し、

除去した前記隣接部分に、Alを含まない半導体材料からなる半導体層を形成し、

前記活性層、前記変調器層及び前記半導体層上に、エッチストップ層を形成し、

前記エッチストップ層上に、Alを含まない半導体材料からなる共通導波路層を形成し、

前記共通導波路層上にAlを含まない半導体材料からなる上部クラッド層を形成し、

前記共通導波路層以上をリッジ構造に形成し、

前記結合部光導波路のリッジ幅を、前記レーザ部光導波路及び前記変調器部光導波路のリッジ幅より大きく形成し、

前記リッジ構造の両側面を半絶縁性半導体材料により埋め込むことを特徴とする。

上記第6の発明に記載の半導体光集積素子の作製方法において、

前記隣接部分を除去する際、当該半導体光集積素子の端部となる前記活性層及び前記変調器層の端部も同時に除去し、

前記半導体層を形成する際、除去した前記端部部分に前記半導体層を同時に形成することにより窓構造部を形成し、前記活性層及び前記変調器層の端面を前記窓構造部で覆って、空気中に露出しないようにすることを特徴とする。

上記第6又は第7の発明に記載の半導体光集積素子の作製方法において、

前記半絶縁性半導体材料にRuをドープすることを特徴とする。

上記第6〜第8の発明のいずれか1つに記載の半導体光集積素子の作製方法において、

当該半導体光集積素子の発振波長を1.55μmとする場合、

前記共通導波路層の組成波長が1.0μm以上1.4μm以下となる組成から、前記共通導波路層を構成することを特徴とする。

上記第9の発明に記載の半導体光集積素子の作製方法において、

前記結合部光導波路のリッジ幅を1.0μm以上2.0μm未満の範囲で形成することを特徴とする。

図1は、本発明に係る半導体光集積素子の実施形態の一例を示す斜視図である。又、図2〜図5は、図1に示す半導体光集積素子の断面図であり、図2が、その導波方向に沿う断面図、図3が、その半導体レーザ部の断面図、図4が、その結合部の断面図、図5が、その半導体光変調器部の断面図である。最初に、図1〜図5を参照して、その構成を説明する。

次に、図1〜図5を参照しながら、図6(a)〜(d)、図7(a)〜(f)を用いて、本発明に係る半導体光集積素子の作製方法を説明する。

本発明に係る半導体光集積素子は、上述した基本構成だけでも様々な利点を有するが、後述するように、埋め込み導波路幅等を最適な条件に設定することで、導波路をシングルモードとすると共に、レーザ部1と結合部3及び結合部3と変調器部2の結合効率を80%以上とすることができる。そこで、結合効率を80%以上にする構成条件について、以下、図8〜図27を参照して、詳細に説明する。

最初に、共通導波路層15の組成について述べる。

共通導波路層15には、非Al系半導体材料であるInGaAsPが用いられている。ここで、共通導波路層15を構成するInGaAsPの組成について、組成によって決まるフォトルミネッセンス測定における発光波長(組成波長又はPL波長)を用いて説明する。図8に、PL波長の温度依存性を示す。又、1.55μm波長帯のDFB−LDの発振波長の温度依存性も示す。

次に、共通導波路層15の層厚dについて説明する。共通導波路層15の層厚dは、0.1μm未満になると結合効率が低下して、素子特性が低下するので、0.1μm以上であることが望ましい。一方、0.6μmより厚くなると、共通導波路層15の光閉じ込めが増大する一方、レーザ部1の活性層11の光閉じ込めが低下して、レーザの特性が低下(閾値電流の増大等)するので、0.6μm以下であることが望ましい。更に、層厚を0.35μm以下にすると、閾値電流が更に低減するので有効である。

次に、レーザ部1の共通導波路層15の幅、即ち、レーザ部1の埋め込み導波路幅WLについて説明する。レーザ部1からの発振光は共通導波路層15をシングルモードで導波しなくてはならない。

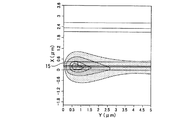

又、図14においては、この図が埋め込み導波路断面の右半分だけを示していることを考慮すると、埋め込み導波路幅WLが1.7μmのときは、マルチモードの光のフィールドが結合していないこと、つまり、シングルモードであることを表している。

一方、図15においては、埋め込み導波路幅WLが1.8μmのときは、マルチモードの光のフィールドが結合して、光がマルチモード導波していることを示している。

このように、共通導波路層15のPL波長が1.3μmのときは、埋め込み導波路幅WLが1.8μm未満である必要がある。

次に、結合部3の埋め込み導波路幅WPについて説明する。

前述の図11で示したように、PL波長1.3μm、層厚0.2μmの共通導波路層15において、レーザ部1の埋め込み導波路幅WLが1.0μmのときは、結合部3の埋め込み導波路幅WPは、1.0μmより1.2μm〜1.5μmの方が、結合効率が高い。同様に、レーザ部1の埋め込み導波路幅WLが1.2μmのときは、結合部3の埋め込み導波路幅WPは、1.2μmより1.5μmの方が、結合効率が高い。

次に、レーザ部1の活性層11、共通導波路層15、変調器部2の変調器層12の光閉じ込めについて述べる。

又、図24に示すように、埋め込み導波路幅WLが大きくなるに従い、共通導波路層15の閉じ込め係数が増大していることが分かる。

図25に示すように、レーザ部1の埋め込み導波路幅WLが1.0μm以上2.0μm以下において、活性層11の光閉じ込め係数は0.2程度、共通導波路層15の光閉じ込め係数は0.27〜0.3程度である。

図26に示すように、結合部3の埋め込み導波路幅WPが1.0μm以上2.0μm以下において、共通導波路層15の光閉じ込め係数は0.28〜0.31程度である。

図27に示すように、変調器部2の埋め込み導波路幅WEが1.0μm以上2.0μm以下において、変調器層12の光閉じ込め係数は0.27〜0.28程度、共通導波路層15の光閉じ込め係数は0.25〜0.27程度である。

2 半導体光変調器部

3 結合部

4、5 窓構造部

10 基板

11 活性層

12 変調器層

13 半導体層

14 エッチストップ層

15 共通光導波路層

16 上部クラッド層

17 埋込層

18 コンタクト層

19 上部電極層

20 下部電極層

Claims (10)

- 同一の半導体基板上に、Alを含む半導体材料からなる活性層を備えるレーザ部光導波路とAlを含む半導体材料からなる変調器層を備える変調器部光導波路とをモノリシック集積した半導体光集積素子において、

前記活性層と前記変調器層との間に、Alを含まない半導体材料からなる半導体層を設けると共に、前記半導体層の上層に、前記活性層及び前記変調器層の上層にまで延設された、Alを含まない半導体材料からなる共通導波路層を設けることにより、前記レーザ部光導波路と前記変調器部光導波路との間に結合部光導波路を設け、

前記共通導波路層以上をリッジ構造に形成し、前記結合部光導波路のリッジ幅を、前記レーザ部光導波路及び前記変調器部光導波路のリッジ幅より大きくすると共に、前記リッジ構造の両側面を半絶縁性半導体材料により埋め込んだことを特徴とする半導体光集積素子。 - 請求項1に記載の半導体光集積素子において、

Alを含まない半導体材料からなる窓構造部を、当該半導体光集積素子の端部に設け、

前記活性層及び前記変調器層の端面を前記窓構造部で覆って、空気中に露出しないようにしたことを特徴とする半導体光集積素子。 - 請求項1又は請求項2に記載の半導体光集積素子において、

前記半絶縁性半導体材料がRuによりドープされていることを特徴とする半導体光集積素子。 - 請求項1から請求項3のいずれか1つに記載の半導体光集積素子において、

当該半導体光集積素子の発振波長を1.55μmとする場合、

前記共通導波路層の組成波長を1.0μm以上1.4μm以下としたことを特徴とする半導体光集積素子。 - 請求項4に記載の半導体光集積素子において、

前記結合部光導波路のリッジ幅を1.0μm以上2.0μm未満の範囲としたことを特徴とする半導体光集積素子。 - 同一の半導体基板上に、Alを含む半導体材料からなる活性層を備えるレーザ部光導波路とAlを含む半導体材料からなる変調器層を備える変調器部光導波路とをモノリシック集積する半導体光集積素子の作製方法において、

前記半導体基板上に、前記活性層と前記変調器層とを隣接して形成すると共に、前記活性層と前記変調器層との隣接部分を除去し、

除去した前記隣接部分に、Alを含まない半導体材料からなる半導体層を形成し、

前記活性層、前記変調器層及び前記半導体層上に、エッチストップ層を形成し、

前記エッチストップ層上に、Alを含まない半導体材料からなる共通導波路層を形成し、

前記共通導波路層上にAlを含まない半導体材料からなる上部クラッド層を形成し、

前記共通導波路層以上をリッジ構造に形成し、

前記結合部光導波路のリッジ幅を、前記レーザ部光導波路及び前記変調器部光導波路のリッジ幅より大きく形成し、

前記リッジ構造の両側面を半絶縁性半導体材料により埋め込むことを特徴とする半導体光集積素子の作製方法。 - 請求項6に記載の半導体光集積素子の作製方法において、

前記隣接部分を除去する際、当該半導体光集積素子の端部となる前記活性層及び前記変調器層の端部も同時に除去し、

前記半導体層を形成する際、除去した前記端部部分に前記半導体層を同時に形成することにより窓構造部を形成し、前記活性層及び前記変調器層の端面を前記窓構造部で覆って、空気中に露出しないようにすることを特徴とする半導体光集積素子の作製方法。 - 請求項6又は請求項7に記載の半導体光集積素子の作製方法において、

前記半絶縁性半導体材料にRuをドープすることを特徴とする半導体光集積素子の作製方法。 - 請求項6から請求項8のいずれか1つに記載の半導体光集積素子の作製方法において、

当該半導体光集積素子の発振波長を1.55μmとする場合、

前記共通導波路層の組成波長が1.0μm以上1.4μm以下となる組成から、前記共通導波路層を構成することを特徴とする半導体光集積素子の作製方法。 - 請求項9に記載の半導体光集積素子の作製方法において、

前記結合部光導波路のリッジ幅を1.0μm以上2.0μm未満の範囲で形成することを特徴とする半導体光集積素子の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008033121A JP4842983B2 (ja) | 2008-02-14 | 2008-02-14 | 半導体光集積素子及びその作製方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008033121A JP4842983B2 (ja) | 2008-02-14 | 2008-02-14 | 半導体光集積素子及びその作製方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009194149A JP2009194149A (ja) | 2009-08-27 |

| JP4842983B2 true JP4842983B2 (ja) | 2011-12-21 |

Family

ID=41075912

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008033121A Active JP4842983B2 (ja) | 2008-02-14 | 2008-02-14 | 半導体光集積素子及びその作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4842983B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012002929A (ja) * | 2010-06-15 | 2012-01-05 | Opnext Japan Inc | 半導体光素子の製造方法、レーザモジュール、光伝送装置 |

| JP2017201353A (ja) * | 2016-05-02 | 2017-11-09 | 住友電気工業株式会社 | スポットサイズ変換器、半導体光デバイス |

| JP6717733B2 (ja) * | 2016-11-04 | 2020-07-01 | 日本電信電話株式会社 | 半導体光集積回路 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5333438B2 (ja) * | 1974-06-12 | 1978-09-13 | ||

| JP3245932B2 (ja) * | 1992-02-06 | 2002-01-15 | キヤノン株式会社 | 光半導体装置、その駆動方法及びそれを用いた光伝送方式 |

| GB2352085A (en) * | 1999-07-15 | 2001-01-17 | Univ Bristol | Integrated semiconductor optical devices |

| JP4618854B2 (ja) * | 2000-08-11 | 2011-01-26 | Okiセミコンダクタ株式会社 | 半導体装置およびその製造方法 |

| JP4934344B2 (ja) * | 2006-04-07 | 2012-05-16 | 日本オプネクスト株式会社 | 半導体光集積素子及び半導体光集積デバイス |

-

2008

- 2008-02-14 JP JP2008033121A patent/JP4842983B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009194149A (ja) | 2009-08-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4977377B2 (ja) | 半導体発光装置 | |

| US7340142B1 (en) | Integrated optoelectronic device and method of fabricating the same | |

| JP3484394B2 (ja) | 光半導体装置およびその製造方法 | |

| JP2008010484A (ja) | 半導体光素子及び光送信モジュール | |

| JP4893306B2 (ja) | 半導体レーザ、半導体光アンプ、及び光通信装置 | |

| JPH1168241A (ja) | 半導体レーザー | |

| JP4676068B2 (ja) | 半導体光素子の作製方法 | |

| JP4690515B2 (ja) | 光変調器、半導体光素子、及びそれらの作製方法 | |

| JP5051054B2 (ja) | 半導体レーザおよび半導体レーザを作製する方法 | |

| JP4842983B2 (ja) | 半導体光集積素子及びその作製方法 | |

| JP2006261340A (ja) | 半導体デバイス及びその製造方法 | |

| JP6084428B2 (ja) | 半導体光集積素子及びその製造方法 | |

| US7711229B2 (en) | Optical integrated device and manufacturing method thereof | |

| JP7134350B2 (ja) | 半導体光集積素子および半導体光集積素子の製造方法 | |

| JP2009094410A (ja) | 半導体光集積素子及びその作製方法 | |

| JP2001274510A (ja) | 導波路型光素子及びその製造方法 | |

| JP4014861B2 (ja) | 化合物半導体デバイス及びその作製方法 | |

| US7618836B2 (en) | Method for manufacturing semiconductor optical device | |

| JP4151043B2 (ja) | 光半導体装置の製造方法 | |

| JP5163355B2 (ja) | 半導体レーザ装置 | |

| JP4971235B2 (ja) | 半導体光集積素子 | |

| JP2009295879A (ja) | 半導体光機能素子とその製造方法および電界吸収型光変調器集積半導体レーザ | |

| JPH11204773A (ja) | 導波路型半導体光集積素子およびその製造方法 | |

| JP2002043688A (ja) | リッジ型分布帰還半導体レーザ素子 | |

| JP2002057405A (ja) | 半導体レーザ装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100120 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110921 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111004 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111006 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4842983 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141014 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |