JP4825529B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4825529B2 JP4825529B2 JP2006027830A JP2006027830A JP4825529B2 JP 4825529 B2 JP4825529 B2 JP 4825529B2 JP 2006027830 A JP2006027830 A JP 2006027830A JP 2006027830 A JP2006027830 A JP 2006027830A JP 4825529 B2 JP4825529 B2 JP 4825529B2

- Authority

- JP

- Japan

- Prior art keywords

- holes

- hole

- wiring board

- semiconductor device

- main surface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

- H01L2224/451—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof

- H01L2224/45138—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron (B), silicon (Si), germanium (Ge), arsenic (As), antimony (Sb), tellurium (Te) and polonium (Po), and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950°C and less than 1550°C

- H01L2224/45144—Gold (Au) as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49171—Fan-out arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

Description

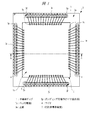

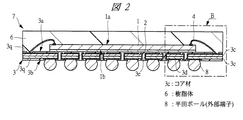

図1は本発明の実施の形態1の半導体装置の構造の一例を封止体を透過して示す平面図、図2は図1に示すA−A線に沿って切断した断面の構造を示す断面図、図3は図2に示すB部の構造を示す拡大部分断面図、図4は図1に示す半導体装置に組み込まれる配線基板の主面側の導体パターンの一例を示す平面図、図5は図4に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。また、図6は図4に示す配線基板のスルーホールの構造の一例を示す拡大部分断面図、図7は図4に示す配線基板の変形例のスルーホールの構造を示す拡大部分断面図である。さらに、図8は図1に示す半導体装置の組み立てにおける樹脂モールドまでの組み立ての一例を示す製造プロセスフロー図、図9は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての一例を示す製造プロセスフロー図、図10は図1に示す半導体装置の組み立てにおける樹脂モールド後の組み立ての変形例を示す製造プロセスフロー図である。

図11は本発明の実施の形態2の半導体装置の構造の一例を封止体を透過して示す平面図、図12は図11に示すA−A線に沿って切断した断面の構造を示す断面図、図13は図12に示すB部の構造を示す拡大部分断面図である。また、図14は図11に示す半導体装置に組み込まれる配線基板の主面側の導体パターンの一例を示す平面図、図15は図14に示す配線基板の裏面側の導体パターンの一例を示す裏面図、図16は図14に示すC−C線に沿って切断した断面の構造を示す拡大部分断面図である。

図17は本発明の実施の形態3の半導体装置の構造の一例を封止体を透過して示す平面図、図18は図17に示すA−A線に沿って切断した断面の構造を示す断面図、図19は図17に示すB−B線に沿って切断した断面の構造を示す断面図、図20は図18に示すC部の構造を示す拡大部分断面図である。さらに、図21は図17に示す半導体装置に組み込まれる配線基板の主面側の導体パターンの一例を示す平面図、図22は図21に示す配線基板の裏面側の導体パターンの一例を示す裏面図である。

1a 主面

1b 裏面

1c パッド(電極)

2 接着剤

3 パッケージ基板(配線基板)

3a 主面

3b 裏面

3c コア材

3d ランド部

3e スルーホール(第1貫通孔)

3f 開口窓

3g メッキ膜

3h 金属膜

3i 絶縁膜

3j,3k 開口部

3m ダミースルーホール(第2貫通孔)

3n 配線

3p ボンディング用端子(ワイヤ接合部)

3q ソルダレジスト膜

3r 給電線

4 ワイヤ

5 一括封止体

6 樹脂体

7 CSP(半導体装置)

8 半田ボール(外部端子)

9 多数個取り基板

10 マーキング

11 ダイシングブレード

12 ダイシングテープ

13,14 CSP(半導体装置)

15 樹脂成形金型

15a キャビティ

Claims (7)

- 平面形状が方形状からなる主面、平面形状が方形状からなり、かつ前記主面とは反対側の裏面、前記主面に形成された複数のワイヤ接合部、前記裏面に形成された複数のランド部、前記主面と前記裏面の間に形成された複数の第1貫通孔、前記主面と前記裏面の間に形成された複数の第2貫通孔、および前記複数の第1貫通孔のそれぞれの内壁に形成され、前記複数のワイヤ接合部と前記複数のランド部とをそれぞれ電気的に接続するメッキ膜を有する配線基板と、

前記配線基板の主面上に搭載された半導体チップと、

前記半導体チップの複数の電極と前記配線基板の主面に形成された前記複数のワイヤ接合部とをそれぞれ電気的に接続する複数のワイヤと、

前記半導体チップ及び前記複数のワイヤを封止する樹脂体と、

前記複数のランド部上に形成された複数の外部端子と、

を有し、

前記複数の第1貫通孔のうち、前記複数のランド部において最外周に配置された第1ランド部と電気的に接続されるメッキ膜が形成された貫通孔は、前記第1ランド部より前記配線基板の中心側に形成されており、

前記複数の第2貫通孔は、前記複数の第1貫通孔および前記複数のランド部より前記配線基板の外側にそれぞれ形成されており、かつ、前記複数のワイヤ接合部のうちの前記配線基板の第1辺と並ぶ第1方向に沿って形成された複数の第1ワイヤ接合部の配列延長線と、前記複数のワイヤ接合部のうちの前記配線基板の前記第1辺と交差する第2辺と並ぶ第2方向に沿って形成された複数の第2ワイヤ接合部の配列延長線との交点部にそれぞれ形成されており、

前記複数の第2貫通孔のそれぞれは、前記複数のワイヤ接合部、前記複数のランド部、および前記複数の第1貫通孔のそれぞれの内壁に形成された前記メッキ膜と接続されていないことを特徴とする半導体装置。 - 請求項1記載の半導体装置において、前記複数の第1貫通孔の内部に金属膜が埋め込まれていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記複数の第1貫通孔及び前記複数の第2貫通孔の内部に金属膜が埋め込まれていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記複数の第1貫通孔はレーザによって形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記複数の第1貫通孔及び前記複数の第2貫通孔はレーザによって形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記配線基板は、複数のコア材を貼り合わせて形成されていることを特徴とする半導体装置。

- 請求項1記載の半導体装置において、前記複数の第1貫通孔のそれぞれは、前記複数のワイヤ接合部よりも前記配線基板の中心側に形成されていることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006027830A JP4825529B2 (ja) | 2006-02-06 | 2006-02-06 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006027830A JP4825529B2 (ja) | 2006-02-06 | 2006-02-06 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007208153A JP2007208153A (ja) | 2007-08-16 |

| JP2007208153A5 JP2007208153A5 (ja) | 2009-03-19 |

| JP4825529B2 true JP4825529B2 (ja) | 2011-11-30 |

Family

ID=38487328

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006027830A Expired - Fee Related JP4825529B2 (ja) | 2006-02-06 | 2006-02-06 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4825529B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4998338B2 (ja) * | 2008-03-11 | 2012-08-15 | 富士通セミコンダクター株式会社 | 半導体装置及び回路基板 |

| JP5223571B2 (ja) * | 2008-09-30 | 2013-06-26 | 富士通株式会社 | 半導体装置、基板設計方法、基板設計装置 |

| JP5557439B2 (ja) | 2008-10-24 | 2014-07-23 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置及びその製造方法 |

| JP6375517B2 (ja) | 2013-06-25 | 2018-08-22 | パナソニックIpマネジメント株式会社 | マイクロ波回路 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3685347B2 (ja) * | 1995-12-30 | 2005-08-17 | ソニー株式会社 | 半導体装置 |

| JPH113954A (ja) * | 1997-06-11 | 1999-01-06 | Hitachi Cable Ltd | 半導体素子搭載用配線基板および半導体装置 |

| JP2002118204A (ja) * | 1999-11-17 | 2002-04-19 | Sumitomo Bakelite Co Ltd | 半導体装置、並びに半導体搭載用基板及びその製造方法 |

| JP3936681B2 (ja) * | 2003-08-25 | 2007-06-27 | 沖電気工業株式会社 | 半導体装置 |

| JP4308608B2 (ja) * | 2003-08-28 | 2009-08-05 | 株式会社ルネサステクノロジ | 半導体装置 |

| JP4273895B2 (ja) * | 2003-09-24 | 2009-06-03 | 日立化成工業株式会社 | 半導体素子搭載用パッケージ基板の製造方法 |

-

2006

- 2006-02-06 JP JP2006027830A patent/JP4825529B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007208153A (ja) | 2007-08-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8383456B2 (en) | Semiconductor device and manufacturing method therefor | |

| US7566969B2 (en) | Semiconductor device with improved arrangement of a through-hole in a wiring substrate | |

| US7829987B2 (en) | Carrier structure embedded with semiconductor chips and method for manufacturing the same | |

| JP2007335581A (ja) | 半導体装置の製造方法 | |

| JP2008218979A (ja) | 電子パッケージ及びその製造方法 | |

| JP2007235009A (ja) | 半導体装置 | |

| JP2011035302A (ja) | 半導体装置の製造方法 | |

| US10304767B2 (en) | Semiconductor device | |

| JP2007027526A (ja) | 両面電極パッケージ及びその製造方法 | |

| JP2009194079A (ja) | 半導体装置用配線基板とその製造方法及びそれを用いた半導体装置 | |

| US10134665B2 (en) | Semiconductor device | |

| JP5501562B2 (ja) | 半導体装置 | |

| KR20050009036A (ko) | 적층 패키지 및 그 제조 방법 | |

| JP4494249B2 (ja) | 半導体装置 | |

| JP4825529B2 (ja) | 半導体装置 | |

| US7745260B2 (en) | Method of forming semiconductor package | |

| JP2009043793A (ja) | 半導体装置、およびその半導体装置の製造方法 | |

| JP2020025019A (ja) | 半導体装置 | |

| JP2010010269A (ja) | 半導体装置、半導体装置製造用中間体およびそれらの製造方法 | |

| JP2006344827A (ja) | 半導体装置の製造方法 | |

| JP2009182004A (ja) | 半導体装置 | |

| JP2009283835A (ja) | 半導体装置及びその製造方法 | |

| JP5298714B2 (ja) | 半導体装置の製造方法 | |

| JP4232613B2 (ja) | 半導体装置の製造方法 | |

| JP2011061055A (ja) | 半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090202 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090202 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090421 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110531 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110816 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110912 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140916 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |