JP4801249B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4801249B2 JP4801249B2 JP2000347343A JP2000347343A JP4801249B2 JP 4801249 B2 JP4801249 B2 JP 4801249B2 JP 2000347343 A JP2000347343 A JP 2000347343A JP 2000347343 A JP2000347343 A JP 2000347343A JP 4801249 B2 JP4801249 B2 JP 4801249B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- tft

- region

- impurity

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

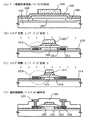

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Thin Film Transistor (AREA)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000347343A JP4801249B2 (ja) | 1999-11-19 | 2000-11-14 | 半導体装置の作製方法 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP33017499 | 1999-11-19 | ||

| JP1999330174 | 1999-11-19 | ||

| JP11-330174 | 1999-11-19 | ||

| JP2000347343A JP4801249B2 (ja) | 1999-11-19 | 2000-11-14 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001210832A JP2001210832A (ja) | 2001-08-03 |

| JP2001210832A5 JP2001210832A5 (enExample) | 2007-12-27 |

| JP4801249B2 true JP4801249B2 (ja) | 2011-10-26 |

Family

ID=26573434

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000347343A Expired - Fee Related JP4801249B2 (ja) | 1999-11-19 | 2000-11-14 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4801249B2 (enExample) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW495854B (en) | 2000-03-06 | 2002-07-21 | Semiconductor Energy Lab | Semiconductor device and manufacturing method thereof |

| TW513753B (en) | 2000-03-27 | 2002-12-11 | Semiconductor Energy Lab | Semiconductor display device and manufacturing method thereof |

| JP5046452B2 (ja) | 2000-10-26 | 2012-10-10 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4954366B2 (ja) | 2000-11-28 | 2012-06-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2004031409A (ja) * | 2002-06-21 | 2004-01-29 | Sanyo Electric Co Ltd | 薄膜トランジスタの製造方法 |

| US7508034B2 (en) | 2002-09-25 | 2009-03-24 | Sharp Kabushiki Kaisha | Single-crystal silicon substrate, SOI substrate, semiconductor device, display device, and manufacturing method of semiconductor device |

| JP4872197B2 (ja) * | 2004-08-25 | 2012-02-08 | カシオ計算機株式会社 | 薄膜トランジスタパネル及びその製造方法 |

| KR100659758B1 (ko) | 2004-09-22 | 2006-12-19 | 삼성에스디아이 주식회사 | 박막트랜지스터 제조 방법 |

| JP2007258453A (ja) * | 2006-03-23 | 2007-10-04 | Toshiba Matsushita Display Technology Co Ltd | 薄膜トランジスタ、及びその製造方法 |

| JP2013054359A (ja) * | 2012-09-18 | 2013-03-21 | Semiconductor Energy Lab Co Ltd | 表示装置 |

| US10338446B2 (en) * | 2014-12-16 | 2019-07-02 | Sharp Kabushiki Kaisha | Semiconductor device having low resistance source and drain regions |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2719252B2 (ja) * | 1991-08-26 | 1998-02-25 | シャープ株式会社 | 薄膜トランジスタ |

| JP3474604B2 (ja) * | 1993-05-25 | 2003-12-08 | 三菱電機株式会社 | 薄膜トランジスタおよびその製法 |

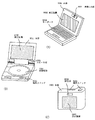

| JP3871736B2 (ja) * | 1996-06-25 | 2007-01-24 | 株式会社半導体エネルギー研究所 | 液晶表示装置及び撮影装置及び情報処理装置 |

| JPH10125928A (ja) * | 1996-10-23 | 1998-05-15 | Semiconductor Energy Lab Co Ltd | 半導体集積回路及びその作製方法 |

| JP3883706B2 (ja) * | 1998-07-31 | 2007-02-21 | シャープ株式会社 | エッチング方法、及び薄膜トランジスタマトリックス基板の製造方法 |

-

2000

- 2000-11-14 JP JP2000347343A patent/JP4801249B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001210832A (ja) | 2001-08-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8957424B2 (en) | Electroluminescence display device | |

| JP4562835B2 (ja) | 半導体装置の作製方法 | |

| JP5483763B2 (ja) | 液晶表示装置 | |

| CN100530542C (zh) | 半导体器件的制造方法 | |

| JP4801249B2 (ja) | 半導体装置の作製方法 | |

| JP4076720B2 (ja) | 半導体装置の作製方法 | |

| JP4939689B2 (ja) | 半導体装置およびその作製方法 | |

| JP4986332B2 (ja) | 半導体装置の作製方法 | |

| JP2006293385A (ja) | 表示装置 | |

| JP2006126855A (ja) | 表示装置 | |

| JP4494369B2 (ja) | 液晶表示装置 | |

| JP5244274B2 (ja) | 半導体装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP2006313363A (ja) | 表示装置 | |

| JP4463377B2 (ja) | 半導体装置およびその作製方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP5159005B2 (ja) | 半導体装置の作製方法 | |

| JP4472082B2 (ja) | 半導体装置の作製方法 | |

| JP2001053286A (ja) | 半導体膜およびその作製方法 | |

| JP4618842B2 (ja) | 半導体装置の作製方法 | |

| JP4700159B2 (ja) | 半導体装置の作製方法 | |

| JP2003303833A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071025 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071025 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110131 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110301 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110330 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110802 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110805 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140812 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140812 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |