JP4801249B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4801249B2 JP4801249B2 JP2000347343A JP2000347343A JP4801249B2 JP 4801249 B2 JP4801249 B2 JP 4801249B2 JP 2000347343 A JP2000347343 A JP 2000347343A JP 2000347343 A JP2000347343 A JP 2000347343A JP 4801249 B2 JP4801249 B2 JP 4801249B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- tft

- region

- impurity

- layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 158

- 238000000034 method Methods 0.000 title claims description 147

- 238000004519 manufacturing process Methods 0.000 title claims description 36

- 239000012535 impurity Substances 0.000 claims description 192

- 238000005530 etching Methods 0.000 claims description 120

- 239000010408 film Substances 0.000 description 321

- 239000010410 layer Substances 0.000 description 261

- 239000000758 substrate Substances 0.000 description 118

- 238000005401 electroluminescence Methods 0.000 description 55

- 230000008569 process Effects 0.000 description 54

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 49

- 229910052710 silicon Inorganic materials 0.000 description 49

- 239000010703 silicon Substances 0.000 description 49

- 239000011159 matrix material Substances 0.000 description 44

- 239000004973 liquid crystal related substance Substances 0.000 description 43

- 239000000463 material Substances 0.000 description 40

- 230000015572 biosynthetic process Effects 0.000 description 30

- 239000007789 gas Substances 0.000 description 29

- 230000006870 function Effects 0.000 description 23

- 239000011521 glass Substances 0.000 description 23

- 125000006850 spacer group Chemical group 0.000 description 22

- 239000011229 interlayer Substances 0.000 description 20

- 239000003990 capacitor Substances 0.000 description 19

- 229910052739 hydrogen Inorganic materials 0.000 description 19

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 18

- 238000000137 annealing Methods 0.000 description 17

- 238000004544 sputter deposition Methods 0.000 description 17

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 16

- 239000001257 hydrogen Substances 0.000 description 16

- 238000002425 crystallisation Methods 0.000 description 15

- 230000007423 decrease Effects 0.000 description 15

- 230000003287 optical effect Effects 0.000 description 15

- 239000010936 titanium Substances 0.000 description 15

- 229910021417 amorphous silicon Inorganic materials 0.000 description 14

- 230000003197 catalytic effect Effects 0.000 description 14

- 238000010438 heat treatment Methods 0.000 description 14

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 14

- 239000000460 chlorine Substances 0.000 description 13

- 238000002347 injection Methods 0.000 description 13

- 239000007924 injection Substances 0.000 description 13

- 238000012545 processing Methods 0.000 description 13

- 239000004020 conductor Substances 0.000 description 12

- 229910052760 oxygen Inorganic materials 0.000 description 12

- 230000002829 reductive effect Effects 0.000 description 12

- 239000002585 base Substances 0.000 description 11

- 230000008025 crystallization Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 11

- 238000005224 laser annealing Methods 0.000 description 11

- 229920005989 resin Polymers 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- 229910045601 alloy Inorganic materials 0.000 description 10

- 239000000956 alloy Substances 0.000 description 10

- 238000006243 chemical reaction Methods 0.000 description 10

- 230000006866 deterioration Effects 0.000 description 10

- 238000010586 diagram Methods 0.000 description 10

- 230000005684 electric field Effects 0.000 description 10

- 150000002500 ions Chemical class 0.000 description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 10

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 9

- 229910052581 Si3N4 Inorganic materials 0.000 description 9

- 229910052698 phosphorus Inorganic materials 0.000 description 9

- 239000011574 phosphorus Substances 0.000 description 9

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 9

- 239000011787 zinc oxide Substances 0.000 description 9

- 239000012298 atmosphere Substances 0.000 description 8

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 150000001875 compounds Chemical class 0.000 description 8

- 239000000945 filler Substances 0.000 description 8

- PQXKHYXIUOZZFA-UHFFFAOYSA-M lithium fluoride Chemical class [Li+].[F-] PQXKHYXIUOZZFA-UHFFFAOYSA-M 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- 239000012071 phase Substances 0.000 description 8

- 238000005070 sampling Methods 0.000 description 8

- 239000000565 sealant Substances 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 239000003054 catalyst Substances 0.000 description 7

- 238000009826 distribution Methods 0.000 description 7

- 229910003437 indium oxide Inorganic materials 0.000 description 7

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical group [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 7

- 238000009616 inductively coupled plasma Methods 0.000 description 7

- -1 polyethylene terephthalate Polymers 0.000 description 7

- 238000003860 storage Methods 0.000 description 7

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 239000000969 carrier Substances 0.000 description 6

- 238000001312 dry etching Methods 0.000 description 6

- 229910052715 tantalum Inorganic materials 0.000 description 6

- 229910052721 tungsten Inorganic materials 0.000 description 6

- 238000001994 activation Methods 0.000 description 5

- 239000010949 copper Substances 0.000 description 5

- 238000005984 hydrogenation reaction Methods 0.000 description 5

- 238000002161 passivation Methods 0.000 description 5

- 230000009467 reduction Effects 0.000 description 5

- 239000002356 single layer Substances 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- 230000001133 acceleration Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 229910021419 crystalline silicon Inorganic materials 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 238000004151 rapid thermal annealing Methods 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 4

- 239000010409 thin film Substances 0.000 description 4

- 229910052719 titanium Inorganic materials 0.000 description 4

- 238000007740 vapor deposition Methods 0.000 description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 229910052802 copper Inorganic materials 0.000 description 3

- 239000013078 crystal Substances 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- 238000005247 gettering Methods 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 239000011810 insulating material Substances 0.000 description 3

- 229910052750 molybdenum Inorganic materials 0.000 description 3

- 239000012299 nitrogen atmosphere Substances 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 229920003023 plastic Polymers 0.000 description 3

- 239000004033 plastic Substances 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 230000010287 polarization Effects 0.000 description 3

- 229920003227 poly(N-vinyl carbazole) Polymers 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- 238000001878 scanning electron micrograph Methods 0.000 description 3

- 239000003566 sealing material Substances 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 241000894007 species Species 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 230000003068 static effect Effects 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 3

- 229910001887 tin oxide Inorganic materials 0.000 description 3

- 238000002834 transmittance Methods 0.000 description 3

- 239000010937 tungsten Substances 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- 229910000838 Al alloy Inorganic materials 0.000 description 2

- 229920002799 BoPET Polymers 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 2

- 239000005041 Mylar™ Substances 0.000 description 2

- CBENFWSGALASAD-UHFFFAOYSA-N Ozone Chemical compound [O-][O+]=O CBENFWSGALASAD-UHFFFAOYSA-N 0.000 description 2

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 230000003213 activating effect Effects 0.000 description 2

- 229910052783 alkali metal Inorganic materials 0.000 description 2

- 150000001340 alkali metals Chemical class 0.000 description 2

- 239000005407 aluminoborosilicate glass Substances 0.000 description 2

- 239000007864 aqueous solution Substances 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052788 barium Inorganic materials 0.000 description 2

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 239000005388 borosilicate glass Substances 0.000 description 2

- DQXBYHZEEUGOBF-UHFFFAOYSA-N but-3-enoic acid;ethene Chemical compound C=C.OC(=O)CC=C DQXBYHZEEUGOBF-UHFFFAOYSA-N 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 230000015556 catabolic process Effects 0.000 description 2

- 230000007797 corrosion Effects 0.000 description 2

- 238000005260 corrosion Methods 0.000 description 2

- ZOCHARZZJNPSEU-UHFFFAOYSA-N diboron Chemical compound B#B ZOCHARZZJNPSEU-UHFFFAOYSA-N 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 230000005611 electricity Effects 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 239000005038 ethylene vinyl acetate Substances 0.000 description 2

- 239000011152 fibreglass Substances 0.000 description 2

- 229910052731 fluorine Inorganic materials 0.000 description 2

- 239000011737 fluorine Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910010272 inorganic material Inorganic materials 0.000 description 2

- 239000011147 inorganic material Substances 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 239000012528 membrane Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 2

- 230000007935 neutral effect Effects 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 229920001200 poly(ethylene-vinyl acetate) Polymers 0.000 description 2

- 229920000553 poly(phenylenevinylene) Polymers 0.000 description 2

- 229920002037 poly(vinyl butyral) polymer Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920000647 polyepoxide Polymers 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 239000004800 polyvinyl chloride Substances 0.000 description 2

- 229920000915 polyvinyl chloride Polymers 0.000 description 2

- 238000007639 printing Methods 0.000 description 2

- 239000010453 quartz Substances 0.000 description 2

- 239000012495 reaction gas Substances 0.000 description 2

- 230000004044 response Effects 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 229910021332 silicide Inorganic materials 0.000 description 2

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229920002050 silicone resin Polymers 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052724 xenon Inorganic materials 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- POILWHVDKZOXJZ-ARJAWSKDSA-M (z)-4-oxopent-2-en-2-olate Chemical compound C\C([O-])=C\C(C)=O POILWHVDKZOXJZ-ARJAWSKDSA-M 0.000 description 1

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 description 1

- ZCYVEMRRCGMTRW-UHFFFAOYSA-N 7553-56-2 Chemical compound [I] ZCYVEMRRCGMTRW-UHFFFAOYSA-N 0.000 description 1

- 229910001316 Ag alloy Inorganic materials 0.000 description 1

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 description 1

- 238000001069 Raman spectroscopy Methods 0.000 description 1

- 229910020328 SiSn Inorganic materials 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- 241000862969 Stella Species 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000003513 alkali Substances 0.000 description 1

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- LDDQLRUQCUTJBB-UHFFFAOYSA-O azanium;hydrofluoride Chemical compound [NH4+].F LDDQLRUQCUTJBB-UHFFFAOYSA-O 0.000 description 1

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 description 1

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- YXTPWUNVHCYOSP-UHFFFAOYSA-N bis($l^{2}-silanylidene)molybdenum Chemical compound [Si]=[Mo]=[Si] YXTPWUNVHCYOSP-UHFFFAOYSA-N 0.000 description 1

- 229920005549 butyl rubber Polymers 0.000 description 1

- 239000010406 cathode material Substances 0.000 description 1

- 239000003795 chemical substances by application Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 229910052801 chlorine Inorganic materials 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 238000010835 comparative analysis Methods 0.000 description 1

- 229920000547 conjugated polymer Polymers 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 239000002274 desiccant Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 125000005678 ethenylene group Chemical group [H]C([*:1])=C([H])[*:2] 0.000 description 1

- 230000001747 exhibiting effect Effects 0.000 description 1

- 238000011049 filling Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 230000005525 hole transport Effects 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 229910052740 iodine Inorganic materials 0.000 description 1

- 239000011630 iodine Substances 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- LQJIDIOGYJAQMF-UHFFFAOYSA-N lambda2-silanylidenetin Chemical compound [Si].[Sn] LQJIDIOGYJAQMF-UHFFFAOYSA-N 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 1

- 229910001507 metal halide Inorganic materials 0.000 description 1

- 150000005309 metal halides Chemical class 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910021344 molybdenum silicide Inorganic materials 0.000 description 1

- 125000005487 naphthalate group Chemical group 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 230000000737 periodic effect Effects 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 238000002294 plasma sputter deposition Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920002098 polyfluorene Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 229910052700 potassium Inorganic materials 0.000 description 1

- 239000011591 potassium Substances 0.000 description 1

- 230000001681 protective effect Effects 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 230000002040 relaxant effect Effects 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000007790 solid phase Substances 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

- 238000007738 vacuum evaporation Methods 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 239000013585 weight reducing agent Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/441—Interconnections, e.g. scanning lines

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

Landscapes

- Liquid Crystal (AREA)

- Electrodes Of Semiconductors (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は絶縁表面を有する基板上に薄膜トランジスタ(以下、TFTと記す)で構成された回路を有する半導体装置およびその作製方法に関する。特に本発明は、画素部と駆動回路を同一の基板上に設けた液晶表示装置またはEL表示装置に代表される電気光学装置、およびそのような電気光学装置を搭載した電子機器に好適に利用できる技術を提供する。尚、本明細書において半導体装置とは、半導体特性を利用することで機能する装置全般を指し、上記電気光学装置およびその電気光学装置を搭載した機器をその範疇に含んでいる。

【0002】

【従来の技術】

能動素子を配列して画素部を構成した表示装置はアクティブマトリクス型表示装置と呼ばれ、液晶表示装置やエレクトロルミネッセンス(以下、ELと記す)表示装置などが開発されている。能動素子には絶縁ゲート型のトランジスタが用いられ、好適にはTFTが用いられている。TFTはガラスなどの基板上に気相成長法などにより半導体膜を形成し、その半導体膜でチャネル形成領域やソース領域やドレイン領域などを形成している。その半導体膜にはシリコンや、シリコン・ゲルマニウムなどシリコンを主成分とする材料が好適に用いられている。半導体膜はその作製法により、非晶質シリコンに代表される非晶質半導体膜と、多結晶シリコンに代表される結晶質半導体膜とに分類することができる。その他に近年では単結晶シリコン基板に形成された絶縁ゲート型のトランジスタで画素部を構成する技術も開発されている。

【0003】

非晶質半導体(代表的には非晶質シリコン)膜で活性層を形成したTFTは、非晶質構造などに起因する電子物性的要因から、10cm2/V・sec以上の電界効果移動度を得ることは殆ど不可能であった。そのため、アクティブマトリクス型の液晶表示装置では、画素部において液晶を駆動するためのスイッチング素子(このスイッチング素子をTFTで形成したものを以下、画素TFTと記す)として使用することはできても、画像表示を行うための駆動回路を形成することは不可能である。従って、駆動回路はTAB(Tape Automated Bonding)方式やCOG(Chip on Glass)方式を使ってドライバICなどを実装する技術が用いられている。

【0004】

一方、結晶構造を含む半導体(以下、結晶質半導体と記す)膜(代表的には、結晶質シリコン、或いは多結晶シリコン)を活性層としたTFTでは、高い電界効果移動度が得られることから各種の機能回路を形成して駆動させることが出来、同一のガラス基板上に画素TFTの他に駆動回路においてシフトレジスタ回路、レベルシフタ回路、バッファ回路、サンプリング回路などを実現することが可能となった。駆動回路は、nチャネル型TFTとpチャネル型TFTとから成るCMOS回路を基本として形成されている。このような駆動回路の実装技術が根拠となり、液晶表示装置において軽量化および薄型化を推進するためには、画素部の他に駆動回路を同一基板上に一体形成できる結晶質半導体層を活性層とするTFTが適していると考えられている。

【0005】

【発明が解決しようとする課題】

TFTの特性から比較すると結晶質半導体層で活性層を形成した方が優れているが、画素TFTの他に各種回路に対応したTFTを作製するためには、その製造工程が複雑なものとなり工程数が増加してしまう問題がある。工程数の増加は製造コストの増加要因になるばかりか、製造歩留まりを低下させる原因となることは明らかである。

【0006】

画素TFTと駆動回路のTFTとでは、それらの回路の動作条件は必ずしも同一ではなく、そのことからTFTに要求される特性も少なからず異なっている。nチャネル型TFTで形成される画素TFTは、スイッチング素子として液晶に電圧を印加して駆動させている。液晶は交流で駆動しているので、フレーム反転駆動と呼ばれる方式が多く採用されている。画素TFTは1フレーム期間の間、液晶層に蓄積した電荷を保持するためにオフ電流値(TFTがオフ動作時に流れるドレイン電流)を十分低くすることが要求されている。一方、駆動回路のバッファ回路などには高い駆動電圧が印加されるため、高電圧が印加されても壊れないように耐圧を高めておく必要がある。また電流駆動能力を高めるために、オン電流値(TFTがオン動作時に流れるドレイン電流)を十分確保する必要がある。

【0007】

オフ電流値を低減するためのTFTの構造として、低濃度ドレイン(LDD:Lightly Doped Drain)構造が知られている。この構造はチャネル形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼んでいる。また、ホットキャリアによるオン電流値の劣化を防ぐための手段として、LDD領域をゲート絶縁膜を介してゲート電極と重ねて配置させた、いわゆるGOLD(Gate-drain Overlapped LDD)構造がある。このような構造とすることで、ドレイン近傍の高電界が緩和されてホットキャリア注入を防ぎ、劣化現象の防止に有効であることが知られている。

【0008】

しかし、画素TFTと、シフトレジスタ回路やバッファ回路などの駆動回路のTFTとでは、そのバイアス状態も必ずしも同じではない。例えば、画素TFTにおいてはゲートに大きな逆バイアス(nチャネル型TFTでは負の電圧)が印加されるが、駆動回路のTFTは基本的に逆バイアス状態で動作することはない。また、GOLD構造はオン電流値の劣化を防ぐ効果は高いが、単純にゲート電極と重ねて配置させるだけではオフ電流値が大きくなってしまう。一方、通常のLDD構造はオフ電流値を抑える効果は高いが、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を防ぐ効果は低い。このような問題は、特に結晶質シリコンTFTにおいて、その特性が向上し、またアクティブマトリクス型液晶表示装置に要求される性能が高まるほど顕在化してきている。従って、TFTの動作状態の違いを考慮して、かつ、上記ホットキャリア効果を防ぐには、LDD領域の不純物濃度やその分布などを最適なものとする必要がある。

【0009】

本発明はこのような問題点を解決するための技術であり、TFTを用いて作製するアクティブマトリクス型の表示装置に代表される半導体装置において、各種回路に配置されるTFTの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【0010】

【課題を解決するための手段】

製造コストの低減および歩留まりを実現するには、工程数を削減することが一つの手段として適用できる。具体的には、TFTの製造に要するフォトマスクの枚数を削減することが必要である。フォトマスクはフォトリソグラフィーの技術において、エッチング工程のマスクとするレジストパターンを基板上に形成するために用いる。このフォトマスクを1枚使用することは、その前後の工程において被膜の成膜およびエッチングなどの工程の他に、レジスト剥離、洗浄や乾燥工程などが付加され、フォトリソグラフィーの工程においても、レジスト塗布、プレベーク、露光、現像、ポストベークなどの煩雑な工程が行われることを意味する。

【0011】

フォトマスク数を削減しても、各種回路に配置されるTFTの構造をその回路の機能に応じて適切なものとする。具体的には、画素部に設けるスイッチング素子用のTFTは、動作速度よりもオフ電流値を低減させることに重点を置いた構造が望ましい。そのような構造として、マルチゲート構造を採用する。一方、高速動作が要求される駆動回路に設けられるTFTは、動作速度を高めることと、それと同時に顕著な問題となるホットキャリア注入による劣化を抑制することに重点を置いた構造が必要となる。その構造をLDD領域に工夫を加えて実現する。即ち、チャネル形成領域とドレイン領域との間に設けるLDD領域において、ドレイン領域に近づくにつれて徐々に導電型制御用の不純物元素の濃度が高くなるような濃度勾配を持たせることにより、ドレイン領域近傍の空乏層において電界が集中するのを緩和する効果を高めることができる。LDD領域の一部はゲート電極と重ねるように設けても良い。

【0012】

上記のような不純物元素の濃度勾配を有するLDD領域を形成するために、イオン化した導電型制御用の不純物元素を、電界で加速してゲート電極の一部とゲート絶縁膜(本発明では、ゲート電極と半導体層とに密接してその両者の間に設けられるゲート絶縁膜と該ゲート絶縁膜からその周辺の領域に延在する絶縁膜を含めてゲート絶縁膜と称する)を通過させて、半導体層にドーピングする方法を用いる。さらに、ゲート電極の形状をゲート電極の端部から内側に向かって徐々に厚さが増加するいわゆるテーパー形状とし、その厚さの変化を利用して半導体層にドーピングする不純物元素の濃度を制御する。即ち、TFTのチャネル長方向に向かって不純物元素濃度が徐々に変化するLDD領域を形成する。

【0013】

具体的には、ゲート電極を形成する導電層に対して第1のエッチング処理を行い、所定の領域の導電層を除去して半導体層上の一部の領域にゲート絶縁膜が露出させる。このとき導電層は端部から内側に向かって徐々に厚さが増加するテーパー形状とする。そして、一導電型の不純物元素を添加する第1のドーピング処理を行い、第1の低濃度不純物領域の形成を行う。次いで、同様に第2のエッチング処理と、第2のドーピング処理を行い、第2の低濃度不純物領域の形成を行う。LDD領域は第1と第2の低濃度不純物領域から形成される。この場合、第2のエッチング処理によってゲート電極の形状が確定し、第2のドーピング処理の条件を適当なものとすればLDD領域の一部をゲート電極と重ねて設けることができる。

【0014】

このように、本発明はエッチング処理とドーピング処理を複数回繰り返して行い、LDD領域を形成することに特徴がある。その結果、チャネル長方向に対して濃度の異なるLDD領域を複数個形成することができ、LDD領域の不純物濃度を段階的または連続的に変化させることができる。

【0015】

ゲート電極を形成する導電層は耐熱性導電性材料を用いることが好ましく、タングステン(W)、タンタル(Ta)、チタン(Ti)から選ばれた元素、または前記元素を成分とする化合物或いは合金から形成する。このような耐熱性導電性材料を高速でかつ精度良エッチングして、さらに端部をテーパー形状とするためには、高密度プラズマを用いたドライエッチング法を適用することが好ましい。高密度プラズマを得る手法にはマイクロ波や誘導結合プラズマ(Inductively Coupled Plasma:ICP)を用いたエッチング装置が適している。特に、ICPエッチング装置はプラズマの制御が容易であり、基板の大面積化にも対応できる。

【0016】

以上のように、本発明の構成は、半導体層と、該半導体層に接して形成された絶縁膜と、該絶縁膜の上にテーパー部を有するゲート電極とを有する半導体装置において、半導体層は、チャネル形成領域と、一導電型の不純物元素を含むソース領域またはドレイン領域を形成する第1の不純物領域と、該チャネル形成領域に接しLDD領域を形成する第2の不純物領域を有し、第2の不純物領域の一部はゲート電極と重ねて設けられ、該第2の不純物領域に含まれる一導電型の不純物元素の濃度は、チャネル形成領域から遠ざかるにつれて高くなることを特徴としている。

【0017】

このような本発明の構成は、基板上にTFTを形成した半導体装置に好適に用いることができる。nチャネル型TFTとpチャネル型TFTを有する半導体装置においては、nチャネル型TFTの半導体層が、チャネル形成領域と、一導電型の不純物元素を含むソース領域またはドレイン領域を形成する第1の不純物領域と該チャネル形成領域に接しLDD領域を形成する第2の不純物領域を有し、第2の不純物領域の一部はゲート電極と重ねて設けられ、該第2の不純物領域に含まれる前記一導電型の不純物元素の濃度は、チャネル形成領域から遠ざかるにつれて高くなり、pチャネル型TFTの半導体層が、チャネル形成領域と、ソース領域またはドレイン領域を形成する第3の不純物領域と、該チャネル形成領域に接しLDD領域を形成する第4の不純物領域を有し、第3の不純物領域と第4の不純物領域とには、一導電型の不純物元素と一導電型とは逆の導電型の不純物元素を含むことを特徴としている。

【0018】

画素部を有する半導体装置においては、各画素に設けられる少なくとも一つのTFTの半導体層は、チャネル形成領域と、一導電型の不純物元素を含むソース領域またはドレイン領域を形成する第1の不純物領域と、該チャネル形成領域に接しLDD領域を形成する第2の不純物領域を有し、第2の不純物領域の一部はゲート電極と重ねて設けられ、該第2の不純物領域に含まれる前記一導電型の不純物元素の濃度は、チャネル形成領域から遠ざかるにつれて高くなることを特徴としている。

【0019】

また、本発明の半導体装置の作製方法は、半導体層上に絶縁膜を形成する第1の工程と、絶縁膜上に導電層を形成する第2の工程と、導電層を選択的にエッチングして第1のテーパー形状を有する導電層を形成する第3の工程と、第3の工程の後に一導電型の不純物元素を半導体層にドーピングする第4の工程と、第1のテーパー形状を有する導電層を選択的にエッチングして第2のテーパー形状を有する導電層を形成する第5の工程と、第5の工程の後に一導電型の不純物元素を前記半導体層にドーピングする第6の工程とを有し、第6の工程でドーピングする一導電型の不純物元素の濃度は、第4の工程でドーピングする一導電型の不純物元素の濃度よりも低いことを特徴としている。

【0020】

このような本発明の構成は、基板上にTFTを形成した半導体装置の作製方法に好適に用いることができる。nチャネル型薄膜トランジスタとpチャネル型薄膜トランジスタを有する半導体装置においては、それぞれの半導体層上に絶縁膜を形成する第1の工程と、絶縁膜上に導電層を形成する第2の工程と、導電層を選択的にエッチングして第1のテーパー形状を有する導電層を形成する第3の工程と、第3の工程の後に一導電型の不純物元素を半導体層にドーピングする第4の工程と、第1のテーパー形状を有する導電層を選択的にエッチングして第2のテーパー形状を有する導電層を形成する第5の工程と、第5の工程の後に一導電型の不純物元素を半導体層にドーピングする第6の工程と、第6の工程の後にpチャネル型薄膜トランジスタの半導体層に一導電型とは逆の導電型の不純物元素をドーピングする第7の工程とを有し、第6の工程でドーピングする一導電型の不純物元素の濃度は、第4の工程でドーピングする一導電型の不純物元素の濃度よりも低いことを特徴としている。

【0021】

画素部を有する半導体装置の作製方法においては、各画素に設けられるTFTを形成する半導体層上に絶縁膜を形成する第1の工程と、絶縁膜上に導電層を形成する第2の工程と、導電層を選択的にエッチングして第1のテーパー形状を有する導電層を形成する第3の工程と、第3の工程の後に一導電型の不純物元素を半導体層にドーピングする第4の工程と、第1のテーパー形状を有する導電層を選択的にエッチングして第2のテーパー形状を有する導電層を形成する第5の工程と、第5の工程の後に一導電型の不純物元素を半導体層にドーピングする第6の工程とを有し、第6の工程でドーピングする一導電型の不純物元素の濃度は、第4の工程でドーピングする一導電型の不純物元素の濃度よりも低いことを特徴としている。

【0022】

【発明の実施の形態】

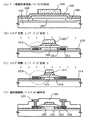

本発明の実施の形態を図1と図2を用いて説明する。図1(A)において、基板1001にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)など光学的異方性を有しないプラスチック基板を用いることができる。また、石英基板を用いても良い。ガラス基板を用いる場合には、ガラス歪み点よりも10〜20℃程度低い温度であらかじめ熱処理しておくとその後の工程で基板が変形することを防ぐことができる。

【0023】

基板1001のTFTを形成する表面に、基板1001からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜1002を10〜200nmの厚さで形成する。下地膜は前記絶縁膜の一層で形成しても良いし、複数の層で形成しても良い。

【0024】

島状半導体層1003は、非晶質構造を有する半導体膜をレーザーアニール法や熱アニール法、またはラピットサーマルアニール法(RTA法)などで結晶化させた結晶質半導体膜から形成する。また、スパッタ法、プラズマCVD法、熱CVD法などで形成した結晶質半導体膜から形成しても良い。或いは特開平7−130652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質半導体層103bを形成することもできる。結晶化の工程ではまず、非晶質半導体層が含有する水素を放出させておくことが好ましく、400〜500℃で1時間程度の熱処理を行い含有する水素量を5atomic%以下にしてから結晶化させると膜表面の荒れを防ぐことができるので良い。いずれにしても、このように形成した結晶質半導体膜を選択的にエッチングして所定の場所に島状半導体層1003を形成する。

【0025】

または、基板1001上に単結晶シリコン層を形成したSOI(Silicon On Insulators)基板としても良い。SOI基板にはその構造や作製方法によっていくつかの種類が知られているが、代表的には、SIMOX(Separation by Implanted Oxygen)、ELTRAN(Epitaxial Layer Transfer:キャノン社の登録商標)基板、Smart-Cut(SOITEC社の登録商標)などを使用することができる。勿論、その他のSOI基板を使用することも可能である。

【0026】

ゲート絶縁膜はプラズマCVD法、スパッタ法、減圧CVD法などにより、膜厚を40〜150nmとしてシリコンを含む絶縁膜で形成する。例えば、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜などから形成する。これを第1の形状のゲート絶縁膜1004とする。そして、第1の形状のゲート絶縁膜1004上にゲート電極を形成するための導電層1005を形成する。この導電層1005は耐熱性を有する導電性材料から形成することが望ましく、単層で形成しても良いが、必要に応じて二層あるいは三層といった複数の層から成る積層構造としても良い。例えば、タングステン(W)、タンタル(Ta)、チタン(Ti)、モリブデン(Mo)から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜で形成する。また、これらの元素の窒化物である窒化タングステン(WN)、窒化タンタル(TaN)、窒化チタン(TiN)、窒化モリブデン(MoN)やシリサイド化物であるタングステンシリサイド、タンタルシリサイド、チタンシリサイド、モリブデンシリサイドなどとの積層構造を形成しても良い。そして、第1の形状のマスク1006を形成する。第1の形状のマスク1006はフォトリソグラフィーの技術を用いてレジスト材料で形成する。

【0027】

そして図1(B)で示す第1のエッチング処理を行う。このエッチング処理はテーパーエッチングであり、導電層1005を第1の形状のマスク1006により端部にテーパー部が形成されるようにエッチング処理する。エッチング処理はドライエッチング法を用い、好適にはICPエッチング装置を用いて行う。エッチングガスにはCF4とCl2の混合ガスを用い、基板にバイアス電圧を印加して行い、少なくとも島状半導体層1003上に第1のテーパー形状を有する導電層1008を形成する。テーパー部の形状は、上記エッチングガスの混合比、エッチング時の圧力、基板側に印加するバイアス電圧によって変化させることができる。最もテーパー形状を制御できるのは基板側に印加するバイアス電圧である。

【0028】

ドライエッチングでは、フッ素(F)や塩素(Cl)などの元素または該元素を含む分子の中性種やイオン種により行われる。通常、中性種によるエッチングが支配的であると等方性にエッチングが進み、テーパー形状は形成されにくくなる。基板側に正または負のバイアス電圧を印加することにより異方性のエッチングが成される。テーパー形状を形成するためのエッチングは、基板側にバイアス電圧を印加すると同時に、被膜とレジストとのエッチング速度の差(選択比とも呼び、被加工物のエッチング速度/レジストのエッチング速度で表す)をある一定の範囲の値として、レジストを同時にエッチングしながら行う。最初に形成するレジストの形状を適したものとすることにより、レジストの端部から徐々にエッチングされ、下地にある被膜にテーパー形状を形成することができる。第1の形状のマスク1006の形状も変化し、第2の形状のマスク1007が形成される。また、エッチングが進むと導電層1005の下層にあるゲート絶縁膜1004の表面が露呈され、ゲート絶縁膜も表面からある程度エッチングされて第2の形状のゲート絶縁膜1009が形成される。

【0029】

その後、レジスト1009をマスクとして、第1のドーピング処理を行い、島状半導体層1003に一導電型の不純物元素を添加する。ドーピング処理は不純物元素をイオン化し電界で加速して半導体層に注入するイオンドープ法やイオン注入法で行う。一導電型の不純物元素はゲート絶縁膜を通してその下の半導体層に添加する。一部の一導電型の不純物元素はテーパー形状が形成された第1のテーパー形状を有する導電層1008の端部及びその近傍を通してその下の半導体層に添加することができる。

【0030】

第1の不純物領域1011には一導電型の不純物元素の濃度が1×1020〜1×1021atoms/cm3の濃度で含まれるようにする。また、第2の不純物領域(A)1012は第1の不純物領域1011に比較して第2の形状のゲート絶縁膜1009の厚さが増加する分半導体層に添加される不純物元素の濃度が低下し、第2の不純物領域(A)1012内で必ずしも均一な濃度分布を取り得ないが、1×1017〜1×1020atoms/cm3の濃度範囲で不純物元素が添加されるようにする。

【0031】

図1(B)において点線で囲んだ領域1017の拡大図を図2(A−1)に示す。また、図2(A−2)は不純物元素の濃度分布を任意の単位量で模式的に表す図でありうる。不純物領域はゲート絶縁膜とゲート電極のテーパー部の下に形成される。不純物元素の濃度分布は線1030で示され、第1の不純物領域1011から遠ざかるにつれ減少する。この減少の割合は、イオンドープにおける加速電圧やドーズ量などの条件、テーパー部の角度θ1や第1の形状のゲート電極1008の厚さにより異なってくる。

【0032】

次に、図1(C)に示すように第2のエッチング処理を行う。第2のエッチング処理は異方性エッチングであり、第1の形状を有するゲート電極1008のチャネル長方向の幅を短くするようにエッチングする。エッチングの方法は、第1のエッチング処理と同じでありICPエッチング装置を用いる。エッチングガスには同様にCF4とCl2の混合ガスを用い、基板側にバイアス電圧を印加して行い、第2のテーパー形状を有する導電層1015を形成する。第2のエッチング処理においても下地であるゲート絶縁膜の一部が表面からエッチングされることにより第2形状のゲート絶縁膜1016が形成される。図1(C)で点線で囲んだ領域1019の拡大図を図2(B−1)に示すが、第2のテーパー形状を有する導電層1015の端部にもテーパー部が形成されるものの、チャネル長方向の幅を短くすることに重点を置いたエッチングのためテーパー角θ2はθ1よりも大きくなる。

【0033】

そして、レジスト1014をマスクとして、第2のドーピング処理を行い、島状半導体層1003に一導電型の不純物元素を添加する。この場合、一部の不純物元素は第2のテーパー形状を有する導電層1015の端部及びその近傍を通してその下の半導体層に添加することができる。

【0034】

第2のドーピング処理では、半導体層に1×1016〜5×1018atoms/cm3の濃度で一導電型の不純物元素が含まれるようにする。図2(B−2)にも示すように、この処理では第1のドーピング処理で形成された第1の不純物領域1011と第2の不純物領域(A)1012にも重ねて一導電型の不純物元素が添加されるが、添加量が低いためその影響を無視することができる。新に形成される第2の不純物領域(B)1018には一導電型の不純物元素の濃度が1×1016〜5×1018atoms/cm3の濃度で含まれるようにする。第2の不純物領域(B)1018は第2のテーパー形状を有する導電層1016の厚さが増加する分半導体層に添加される不純物元素の濃度が低下し、第2の不純物領域(B)1018内で必ずしも均一な濃度分布を取り得ないが上記濃度範囲で不純物元素が含まれるようにする。

【0035】

第2の不純物領域(B)1018は第2の形状のゲート絶縁膜1016と第2のテーパー形状を有する導電層1015のテーパー部の下に形成される。不純物元素の濃度分布は線1031で示され、第1の不純物領域1011から遠ざかるにつれ減少する。第2のテーパー形状を有する導電層1015はゲート電極として用いる。このように、ゲート電極の端部をテーパー形状として、テーパー部を通して不純物元素をドーピングすることにより、テーパー部の下に存在する半導体層中に、徐々に前記不純物元素の濃度が変化するような不純物領域を形成することができる。本発明はこのような不純物領域を積極的に活用する。このような不純物領域を形成することにより、ドレイン領域近傍に発生する高電界を緩和して、ホットキャリアの発生を防ぎ、TFTの劣化を防止することができる。

【0036】

以上のようにして、島状半導体層1003にソース領域またはドレイン領域となる第1の不純物領域、ゲート電極と重ならないLDD領域を形成する第2の不純物領域(A)、ゲート電極と一部が重なるLDD領域を形成する第2の不純物領域(B)及びチャネル形成領域1023が形成される。その後、図1(D)に示すように、必要に応じて層間絶縁膜1020を形成しソース領域またはドレイン領域とコンタクトを形成する配線1021を形成しても良い。

【0037】

【実施例】

[実施例1]

本発明の実施例を図3〜図5を用いて説明する。ここでは、画素部の画素TFTおよび保持容量と、画素部の周辺に設けられる駆動回路のTFTを同時に作製する方法について工程に従って詳細に説明する。

【0038】

図3(A)において、基板101にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板や石英基板などを用いる。ガラス基板を用いる場合には、ガラス歪み点よりも10〜20℃程度低い温度であらかじめ熱処理しておいても良い。そして、基板101のTFTを形成する表面に、基板101からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜102を形成する。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜102aを10〜200nm(好ましくは50〜100nm)、同様にSiH4、N2Oから作製される酸化窒化水素化シリコン膜102bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。ここでは下地膜102を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させて形成しても良い。

【0039】

酸化窒化シリコン膜は平行平板型のプラズマCVD法を用いて形成する。酸化窒化シリコン膜102aは、SiH4を10SCCM、NH3を100SCCM、N2Oを20SCCMとして反応室に導入し、基板温度325℃、反応圧力40Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。一方、酸化窒化水素化シリコン膜102bは、SiH4を5SCCM、N2Oを120SCCM、H2を125SCCMとして反応室に導入し、基板温度400℃、反応圧力20Pa、放電電力密度0.41W/cm2、放電周波数60MHzとした。これらの膜は、基板温度を変化させ、反応ガスの切り替えのみで連続して形成することができる。

【0040】

このようにして作製した酸化窒化シリコン膜102aは、密度が9.28×1022/cm3であり、フッ化水素アンモニウム(NH4HF2)を7.13%とフッ化アンモニウム(NH4F)を15.4%含む混合溶液(ステラケミファ社製、商品名LAL500)の20℃におけるエッチング速度が約63nm/minと遅く、緻密で硬い膜である。このような膜を下地膜に用いると、この上に形成する半導体層にガラス基板からのアルカリ金属元素が拡散するのを防ぐのに有効である。

【0041】

次に、25〜80nm(好ましくは30〜60nm)の厚さで非晶質構造を有する半導体層103aを、プラズマCVD法やスパッタ法などの方法で形成する。非晶質構造を有する半導体膜には、非晶質半導体層や微結晶半導体膜があり、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用しても良い。プラズマCVD法で非晶質シリコン膜を形成する場合には、下地膜102と非晶質半導体層103aとは両者を連続形成することも可能である。例えば、前述のように酸化窒化シリコン膜102aと酸化窒化水素化シリコン膜102bをプラズマCVD法で連続して成膜後、反応ガスをSiH4、N2O、H2からSiH4とH2或いはSiH4のみに切り替えれば、一旦大気雰囲気に晒すことなく連続形成できる。その結果、酸化窒化水素化シリコン膜102bの表面の汚染を防ぐことが可能となり、作製するTFTの特性バラツキやしきい値電圧の変動を低減させることができる。

【0042】

そして、結晶化の工程を行い非晶質半導体層103aから結晶質半導体層103bを作製する。その方法としてレーザーアニール法や熱アニール法(固相成長法)、またはラピットサーマルアニール法(RTA法)を適用することができる。前述のようなガラス基板や耐熱性の劣るプラスチック基板を用いる場合には、特にレーザーアニール法を適用することが好ましい。RTA法では、赤外線ランプ、ハロゲンランプ、メタルハライドランプ、キセノンランプなどを光源に用いる。或いは特開平7−130652号公報で開示された技術に従って、触媒元素を用いる結晶化法で結晶質半導体層103bを形成することもできる。結晶化の工程ではまず、非晶質半導体層が含有する水素を放出させておくことが好ましく、400〜500℃で1時間程度の熱処理を行い含有する水素量を5atomic%以下にしてから結晶化させると膜表面の荒れを防ぐことができるので良い。

【0043】

また、プラズマCVD法で非晶質シリコン膜の形成工程において、反応ガスにSiH4とアルゴン(Ar)を用い、成膜時の基板温度を400〜450℃として形成すると、非晶質シリコン膜の含有水素濃度を5atomic%以下にすることもできる。このような場合において水素を放出させるための熱処理は不要となる。

【0044】

結晶化をレーザーアニール法にて行う場合には、パルス発振型または連続発光型のエキシマレーザーやアルゴンレーザーをその光源とする。パルス発振型のエキシマレーザーを用いる場合には、レーザー光を線状に加工してレーザーアニールを行う。レーザーアニール条件は実施者が適宣選択するものであるが、例えば、レーザーパルス発振周波数30Hzとし、レーザーエネルギー密度を100〜500mJ/cm2(代表的には300〜400mJ/cm2)とする。そして線状ビームを基板全面に渡って照射し、この時の線状ビームの重ね合わせ率(オーバーラップ率)を80〜98%として行う。このようにして図3(B)に示すように結晶質半導体層103bを得ることができる。

【0045】

そして、結晶質半導体層103b上に第1のフォトマスク(PM1)を用い、フォトリソグラフィーの技術を用いてレジストパターンを形成し、ドライエッチングによって結晶質半導体層を島状に分割し、図3(C)に示すように島状半導体層104〜108を形成する。結晶質シリコン膜のドライエッチングにはCF4とO2の混合ガスを用いる。

【0046】

このような島状半導体層に対し、TFTのしきい値電圧(Vth)を制御する目的でp型を付与する不純物元素を1×1016〜5×1017atoms/cm3程度の濃度で島状半導体層の全面に添加しても良い。半導体に対してp型を付与する不純物元素には、ホウ素(B)、アルミニウム(Al)、ガリウム(Ga)など周期律表第13族の元素が知られている。その方法として、イオン注入法やイオンドープ法(或いはイオンシャワードーピング法)を用いることができるが、大面積基板を処理するにはイオンドープ法が適している。イオンドープ法ではジボラン(B2H6)をソースガスとして用いホウ素(B)を添加する。このような不純物元素の注入は必ずしも必要でなく省略しても差し支えないが、特にnチャネル型TFTのしきい値電圧を所定の範囲内に収めるために好適に用いる手法である。

【0047】

ゲート絶縁膜109はプラズマCVD法またはスパッタ法を用い、膜厚を40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さで酸化窒化シリコン膜から形成する。また、SiH4とN2OにO2を添加させて作製された酸化窒化シリコン膜は、膜中の固定電荷密度が低減されているのでこの用途に対して好ましい材料となる。また、SiH4とN2OとH2とから作製する酸化窒化シリコン膜はゲート絶縁膜との界面欠陥密度を低減できるので好ましい。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法で、TEOS(Tetraethyl Ortho Silicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製された酸化シリコン膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0048】

そして、図3(D)に示すように、第1の形状のゲート絶縁膜109上にゲート電極を形成するための耐熱性導電層111を200〜400nm(好ましくは250〜350nm)の厚さで形成する。耐熱性導電層は単層で形成しても良いし、必要に応じて二層あるいは三層といった複数の層から成る積層構造としても良い。本明細書でいう耐熱性導電層にはTa、Ti、W、Moから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜が含まれる。これらの耐熱性導電層はスパッタ法やCVD法で形成されるものであり、低抵抗化を図るために含有する不純物濃度を低減させることが好ましく、特に酸素濃度に関しては30ppm以下とすると良い。本実施例ではW膜を300nmの厚さで形成する。W膜はWをターゲットとしてスパッタ法で形成しても良いし、6フッ化タングステン(WF6)を用いて熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができる。

【0049】

一方、耐熱性導電層111にTa膜を用いる場合には、同様にスパッタ法で形成することが可能である。Ta膜はスパッタガスにArを用いる。また、スパッタ時のガス中に適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。α相のTa膜の抵抗率は20μΩcm程度でありゲート電極に使用することができるが、β相のTa膜の抵抗率は180μΩcm程度でありゲート電極とするには不向きであった。TaN膜はα相に近い結晶構造を持つので、Ta膜の下地にTaN膜を形成すればα相のTa膜が容易に得られる。また、図示しないが、耐熱性導電層111の下に2〜20nm程度の厚さでリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、耐熱性導電層111が微量に含有するアルカリ金属元素が第1の形状のゲート絶縁膜109に拡散するのを防ぐことができる。いずれにしても、耐熱性導電層111は抵抗率を10〜50μΩcmの範囲ですることが好ましい。

【0050】

次に、第2のフォトマスク(PM2)を用い、フォトリソグラフィーの技術を使用してレジストによるマスク112〜117を形成する。そして、第1のエッチング処理を行う。本実施例ではICPエッチング装置を用い、エッチング用ガスにCl2とCF4を用い、1Paの圧力で3.2W/cm2のRF(13.56MHz)電力を投入してプラズマを形成して行う。基板側(試料ステージ)にも224mW/cm2のRF(13.56MHz)電力を投入し、これにより実質的に負の自己バイアス電圧が印加される。この条件でW膜のエッチング速度は約100nm/minである。第1のエッチング処理はこのエッチング速度を基にW膜がちょうどエッチングされる時間を推定し、それよりもエッチング時間を20%増加させた時間をエッチング時間とした。

【0051】

第1のエッチング処理により第1のテーパー形状を有する導電層118〜123が形成される。図2(A)で示すと同様にテーパー部の角度は15〜30°が形成される。残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させるオーバーエッチングを施すものとする。W膜に対する酸化窒化シリコン膜(第1の形状のゲート絶縁膜109)の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされ第1のテーパー形状を有する導電層の端部近傍にテーパー形状が形成された第2の形状のゲート絶縁膜134が形成される。

【0052】

そして、第1のドーピング処理を行い一導電型の不純物元素を島状半導体層に添加する。ここでは、n型を付与する不純物元素添加の工程を行う。第1の形状の導電層を形成したマスク112〜117をそのまま残し、第1のテーパー形状を有する導電層118〜123をマスクとして自己整合的にn型を付与する不純物元素をイオンドープ法で添加する。n型を付与する不純物元素をゲート電極の端部におけるテーパー部とゲート絶縁膜とを通して、その下に位置する半導体層に達するように添加するためにドーズ量を1×1013〜5×1014atoms/cm2とし、加速電圧を80〜160keVとして行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いた。このようなイオンドープ法により第1の不純物領域124〜128には1×1020〜1×1021atomic/cm3の濃度範囲でn型を付与する不純物元素が添加され、テーパー部の下方に形成される第2の不純物領域(A)には同領域内で必ずしも均一ではないが1×1017〜1×1020atomic/cm3の濃度範囲でn型を付与する不純物元素が添加される。

【0053】

この工程において、第2の不純物領域(A)129〜133において、少なくとも第1の形状の導電層118〜123と重なった部分に含まれるn型を付与する不純物元素の濃度変化は、テーパー部の膜厚変化を反映する。即ち、第2の不純物領域(A)129〜133へ添加されるリン(P)の濃度は、第1の形状の導電層に重なる領域において、該導電層の端部から内側に向かって徐々に濃度が低くなる。これはテーパー部の膜厚の差によって、半導体層に達するリン(P)の濃度が変化するためであり、その濃度変化は図2(A−2)で示した通りである。

【0054】

次に、図4(B)に示すように第2のエッチング処理を行う。エッチング処理も同様にICPエッチング装置により行い、エッチングガスにCF4とCl2の混合ガスを用い、RF電力3.2W/cm2(13.56MHz)、バイアス電力45mW/cm2(13.56MHz)、圧力1.0Paでエッチングを行う。この条件で形成される第2の形状を有する導電層140〜145が形成される。その端部にはテーパー部が形成され、該端部から内側にむかって徐々に厚さが増加するテーパー形状となる。第1のエッチング処理と比較して基板側に印加するバイアス電力を低くした分等方性エッチングの割合が多くなり、テーパー部の角度は30〜60°となる。また、第2の形状のゲート絶縁膜134の表面が40nm程度エッチングされ、新たに第3の形状のゲート絶縁膜170が形成される。

【0055】

そして、第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型を付与する不純物元素をドーピングする。例えば、加速電圧を70〜120keVとし、1×1013atoms/cm2のドーズ量で行い、第2の形状を有する導電層140〜145と重なる領域の不純物濃度を1×1016〜1×1018atoms/cm3となるようにする。このようにして、第2の不純物領域(B)146〜150を形成する。

【0056】

pチャネル型TFTを形成する島状半導体層104、106に一導電型とは逆の導電型の不純物領域156、157を形成する。この場合も第2の形状の導電層140、142をマスクとしてp型を付与する不純物元素を添加し、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTを形成する島状半導体層105、107、108は、第3のフォトマスク(PM3)を用いてレジストのマスク151〜153を形成し全面を被覆しておく。ここで形成される不純物領域156、157はジボラン(B2H6)を用いたイオンドープ法で形成する。不純物領域156、157のp型を付与する不純物元素の濃度は、2×1020〜2×1021atoms/cm3となるようにする。

【0057】

しかしながら、この不純物領域156、157は詳細にはn型を付与する不純物元素を含有する3つの領域に分けて見ることができる。第3の不純物領域156a、157aは1×1020〜1×1021atoms/cm3の濃度でn型を付与する不純物元素を含み、第4の不純物領域(A)156b、157bは1×1017〜1×1020atoms/cm3の濃度でn型を付与する不純物元素を含み、第4の不純物領域(B)156c、157cは1×1016〜5×1018atoms/cm3の濃度でn型を付与する不純物元素を含んでいる。しかし、これらの不純物領域156b、156c、157b、157cのp型を付与する不純物元素の濃度を1×1019atoms/cm3以上となるようにし、第3の不純物領域156a、157aにおいては、p型を付与する不純物元素の濃度を1.5から3倍となるようにすることにより、第3の不純物領域でpチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題はな生じない。また、第4の不純物領域(B)156c、157cは一部が第2のテーパー形状を有する導電層140または142と一部が重なって形成される。

【0058】

その後、図5(A)に示すように、ゲート電極およびゲート絶縁膜上から第1の層間絶縁膜158を形成する。第1の層間絶縁膜は酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても第1の層間絶縁膜158は無機絶縁物材料から形成する。第1の層間絶縁膜158の膜厚は100〜200nmとする。ここで、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOSとO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。また、酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2O、NH3から作製される酸化窒化シリコン膜、またはSiH4、N2Oから作製される酸化窒化シリコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度300〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することができる。また、SiH4、N2O、H2から作製される酸化窒化水素化シリコン膜を適用しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製することが可能である。

【0059】

そして、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行った。また、基板101に耐熱温度が低いプラスチック基板を用いる場合にはレーザーアニール法を適用することが好ましい。

【0060】

活性化の工程に続いて、雰囲気ガスを変化させ、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により島状半導体層にある1016〜1018/cm3のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。いずれにしても、島状半導体層104〜108中の欠陥密度を1016/cm3以下とすることが望ましく、そのために水素を0.01〜0.1atomic%程度付与すれば良い。

【0061】

このように、第2の層間絶縁膜を有機絶縁物材料で形成することにより、表面を良好に平坦化させることができる。また、有機樹脂材料は一般に誘電率が低いので、寄生容量を低減することができる。しかし、吸湿性があり保護膜としては適さないので、本実施例のように、第1の層間絶縁膜158として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜などと組み合わせて用いると良い。

【0062】

その後、第4のフォトマスク(PM4)を用い、所定のパターンのレジストマスクを形成し、それぞれの島状半導体層に形成されソース領域またはドレイン領域とする不純物領域に達するコンタクトホールを形成する。コンタクトホールはドライエッチング法で形成する。この場合、エッチングガスにCF4、O2、Heの混合ガスを用い有機樹脂材料から成る第2の層間絶縁膜159をまずエッチングし、その後、続いてエッチングガスをCF4、O2として第1の層間絶縁膜158をエッチングする。さらに、島状半導体層との選択比を高めるために、エッチングガスをCHF3に切り替えて第3の形状のゲート絶縁膜170をエッチングすることによりコンタクトホールを形成することができる。

【0063】

そして、導電性の金属膜をスパッタ法や真空蒸着法で形成し、第5のフォトマスク(PM5)によりレジストマスクパターンを形成し、エッチングによってソース線160〜164とドレイン線165〜168を形成する。画素電極169はドレイン線と一緒に形成される。画素電極171は隣の画素に帰属する画素電極を表している。図示していないが、本実施例ではこの配線を、Ti膜を50〜150nmの厚さで形成し、島状半導体層のソースまたはドレイン領域を形成する不純物領域とコンタクトを形成し、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さで形成(図5(C)において160a〜169aで示す)し、さらにその上に透明導電膜を80〜120nmの厚さで形成(図5(C)において160b〜169bで示す)した。透明導電膜には酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを好適に用いることができる。

【0064】

こうして5枚のフォトマスクにより、同一の基板上に、駆動回路のTFTと画素部の画素TFTとを有した基板を完成させることができる。駆動回路には第1のpチャネル型TFT200、第1のnチャネル型TFT201、第2のpチャネル型TFT202、第2のnチャネル型TFT203、画素部には画素TFT204、保持容量205が形成されている。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0065】

駆動回路の第1のpチャネル型TFT200には、第2のテーパー形状を有する導電層がゲート電極220としての機能を有し、島状半導体層104にチャネル形成領域206、ソース領域またはドレイン領域として機能する第3の不純物領域207a、ゲート電極220と重ならないLDD領域を形成する第4の不純物領域(A)207b、一部がゲート電極220と重なるLDD領域を形成する第4の不純物領域(B)207cを有する構造となっている。

【0066】

第1のnチャネル型TFT201には、第2のテーパー形状を有する導電層がゲート電極221としての機能を有し、島状半導体層105にチャネル形成領域208、ソース領域またはドレイン領域として機能する第1の不純物領域209a、ゲート電極221と重ならないLDD領域を形成する第2の不純物領域(A)209b、一部がゲート電極221と重なるLDD領域を形成する第2の不純物領域(B)209cを有する構造となっている。チャネル長2〜7μmに対して、第2の不純物領域(B)209cがゲート電極221と重なる部分の長さは0.1〜0.3μmとする。このLovの長さはゲート電極221の厚さとテーパー部の角度から制御する。nチャネル型TFTにおいてこのようなLDD領域を形成することにより、ドレイン領域近傍に発生する高電界を緩和して、ホットキャリアの発生を防ぎ、TFTの劣化を防止することができる。

【0067】

駆動回路の第2のpチャネル型TFT202は同様に、第2のテーパー形状を有する導電層がゲート電極222としての機能を有し、島状半導体層106にチャネル形成領域210、ソース領域またはドレイン領域として機能する第3の不純物領域211a、ゲート電極222と重ならないLDD領域を形成する第4の不純物領域(A)211b、一部がゲート電極222と重なるLDD領域を形成する第4の不純物領域(B)211cを有する構造となっている。

【0068】

駆動回路の第2のnチャネル型TFT203には、第2のテーパー形状を有する導電層がゲート電極223としての機能を有し、島状半導体層107にチャネル形成領域212、ソース領域またはドレイン領域として機能する第1の不純物領域213a、ゲート電極223と重ならないLDD領域を形成する第2の不純物領域(A)213b、一部がゲート電極223と重なるLDD領域を形成する第2の不純物領域(B)213cを有する構造となっている。第2のnチャネル型TFT201と同様に第2の不純物領域(B)213cがゲート電極223と重なる部分の長さは0.1〜0.3μmとする。

【0069】

駆動回路はシフトレジスタ回路、バッファ回路などのロジック回路やアナログスイッチで形成されるサンプリング回路などで形成される。図5(B)ではこれらを形成するTFTを一対のソース・ドレイン間に一つのゲート電極を設けたシングルゲートの構造で示したが、複数のゲート電極を一対のソース・ドレイン間に設けたマルチゲート構造としても差し支えない。

【0070】

画素TFT204には、第2のテーパー形状を有する導電層がゲート電極224としての機能を有し、島状半導体層108にチャネル形成領域214a、214b、ソース領域またはドレイン領域として機能する第1の不純物領域215a、217、ゲート電極224と重ならないLDD領域を形成する第2の不純物領域(A)215b、一部がゲート電極224と重なるLDD領域を形成する第2の不純物領域(B)215cを有する構造となっている。第2の不純物領域(B)213cがゲート電極224と重なる部分の長さは0.1〜0.3μmとする。また、第1の不純物領域217から延在し、第2の不純物領域(A)219b、第2の不純物領域(B)219c、導電型を決定する不純物元素が添加されていない領域218を有する半導体層と、第3の形状を有するゲート絶縁膜と同層で形成される絶縁層と、第2のテーパー形状を有する導電層から形成される容量配線225から保持容量が形成されている。

【0071】

図11は画素部のほぼ一画素分を示す上面図である。図中に示すA−A'断面が図5(B)に示す画素部の断面図に対応している。画素TFT204のゲート電極224は図示されていないゲート絶縁膜を介してその下の島状半導体層108と交差し、さらに複数の島状半導体層に跨って延在してゲート配線を兼ねている。図示はしていないが、島状半導体層には、図5(B)で説明したソース領域、ドレイン領域、LDD領域が形成されている。また、230はソース配線164とソース領域215aとのコンタクト部、231は画素電極169とドレイン領域217とのコンタクト部である。保持容量205は、画素TFT204のドレイン領域217から延在する半導体層とゲート絶縁膜を介して容量配線225が重なる領域で形成されている。この構成において半導体層218には、価電子制御を目的とした不純物元素は添加されていない。

【0072】

以上の様な構成は、画素TFTおよび駆動回路が要求する仕様に応じて各回路を構成するTFTの構造を最適化し、半導体装置の動作性能と信頼性を向上させることを可能としている。さらにゲート電極を耐熱性を有する導電性材料で形成することによりLDD領域やソース領域およびドレイン領域の活性化を容易としている。さらに、ゲート電極にゲート絶縁膜を介して重なるLDD領域を形成する際に、導電型を制御する目的で添加した不純物元素に濃度勾配を持たせてLDD領域を形成することで、特にドレイン領域近傍における電界緩和効果が高まることが期待できる。

【0073】

アクティブマトリクス型の液晶表示装置の場合、第1のpチャネル型TFT200と第1のnチャネル型TFT201は高速動作を重視するシフトレジスタ回路、バッファ回路、レベルシフタ回路などを形成するのに用いる。図5(B)ではこれらの回路をロジック回路部として表している。第1のnチャネル型TFT201の第2の不純物領域(B)209cはホットキャリア対策を重視した構造となっている。さらに、耐圧を高め動作を安定化させるために、図9(A)で示すようにこのロジック回路部のTFTを第1のpチャネル型TFT280と第1のnチャネル型TFT281で形成しても良い。このTFTは、一対のソース・ドレイン間に2つのゲート電極を設けたダブルゲート構造であり、このようなTFTは本実施例の工程を用いて同様に作製できる。第1のpチャネル型TFT280には、島状半導体層にチャネル形成領域236a、236b、ソースまたはドレイン領域として機能する第3の不純物領域238a、239a、240a、LDD領域となる第4の不純物領域(A)238b、239b、240b及びゲート電極237と一部が重なりLDD領域となる第4の不純物領域(B)238c、239c、240cを有した構造となっている。第1のnチャネル型TFT281には、島状半導体層にチャネル形成領域241a、241b、ソースまたはドレイン領域として機能する第1の不純物領域243a、244a、245aとLDD領域となる第2の不純物領域(A)243b、244b、245b及びゲート電極242と一部が重なりLDD領域となる第2の不純物領域(B)243c、244c、245cを有している。チャネル長は3〜7μmとして、ゲート電極と重なるLDD領域をLovとしてそのチャネル長方向の長さは0.1〜0.3μmとする。

【0074】

また、アナログスイッチで構成するサンプリング回路には、同様な構成とした第2のpチャネル型TFT202と第2のnチャネル型TFT203を適用することができる。サンプリング回路はホットキャリア対策と低オフ電流動作が重視されるので、図9(B)で示すようにこの回路のTFTを第2のpチャネル型TFT282と第2のnチャネル型TFT283で形成しても良い。この第2のpチャネル型TFT282は、一対のソース・ドレイン間に3つのゲート電極を設けたトリプルゲート構造であり、このようなTFTは本実施例の工程を用いて同様に作製できる。第2のpチャネル型TFT282には、島状半導体層にチャネル形成領域246a、246b、246cソースまたはドレイン領域として機能する第3の不純物領域249a、250a、251a、252a、LDD領域となる第4の不純物領域(A)249b、250b、251b、252b及びゲート電極247と一部が重なりLDD領域となる第4の不純物領域(B)249c、250c、251c、252cを有した構造となっている。第2のnチャネル型TFT283には、島状半導体層にチャネル形成領域253a、253b、ソースまたはドレイン領域として機能する第1の不純物領域255a、256a、257aとLDD領域となる第2の不純物領域(A)255b、256b、257b及びゲート電極254と一部が重なりLDD領域となる第2の不純物領域(B)255c、256c、257cを有している。チャネル長は3〜7μmとして、ゲート電極と重なるLDD領域をLovとしてそのチャネル長方向の長さは0.1〜0.3μmとする。

【0075】

このように、TFTのゲート電極の構成をシングルゲート構造とするか、複数のゲート電極を一対のソース・ドレイン間に設けたマルチゲート構造とするかは、回路の特性に応じて実施者が適宣選択すれば良い。そして、本実施例で完成したアクティブマトリクス基板を用いることで反射型の液晶表示装置を作製することができる。

【0076】

[実施例2]

実施例1ではゲート電極の材料にWやTaなどの耐熱性導電材料を用いる例を示した。このような材料を用いる理由は、ゲート電極形成後に導電型の制御を目的として半導体層に添加した不純物元素を400〜700℃の熱アニールによって活性化させる必要があり、その工程を実施する上でゲート電極に耐熱性を持たせる必要があるからである。しかしながら、このような耐熱性導電材料は面積抵抗で10Ω程度あり、画面サイズが4インチクラスかそれ以上の表示装置には必ずしも適していない。ゲート電極に接続するゲート線を同じ材料で形成すると、基板上における引回し長さが必然的に大きくなり、配線抵抗の影響による配線遅延の問題を無視することができなくなる。

【0077】

例えば、画素密度がVGAの場合、480本のゲート配線と640本のソース線が形成され、XGAの場合には768本のゲート配線と1024本のソース配線が形成される。表示領域の画面サイズは、13インチクラスの場合対角線の長さは340mmとなり、18インチクラスの場合には460mmとなる。本実施例ではこのような液晶表示装置を実現する手段として、ゲート配線をAlや銅(Cu)などの低抵抗導電性材料で形成する方法について図6を用いて説明する。

【0078】

まず、実施例1と同様にして図3(A)〜図4(C)に示す工程を行う。そして導電型の制御を目的として、それぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では500℃で4時間の熱処理を行う。

【0079】

この熱処理において、第2のテーパー形状を有する導電層140〜145は表面から5〜80nmの厚さで導電層(C)172a〜172fが形成される。例えば、第2のテーパー形状を有する導電層がWの場合には、窒化タングステンが形成され、Taの場合には窒化タンタルが形成される。さらに、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い(図6(A))。

【0080】

活性化および水素化処理の後、ゲート線を低抵抗導電材料で形成する。低抵抗導電材料はAlやCuを主成分とするものであり、このような材料から形成される低抵抗導電層からゲート線を形成する。例えば、Tiを0.1〜2重量%含むAl膜を低抵抗導電層として全面に形成する(図示せず)。低抵抗導電層は200〜400nm(好ましくは250〜350nm)の厚さで形成する。そして、所定のレジストパターンを形成し、エッチング処理して、ゲート線173、174を形成する。このとき同じ材料で画素部に設ける保持容量と接続する容量線175も形成する。低抵抗導電層がAlを主成分とする材料である場合には、エッチング処理はリン酸系のエッチング溶液によるウエットエッチングで下地との選択加工性を保ってゲート線を形成することができる。第1の層間絶縁膜176は実施例1と同様にして形成する(図6(B))。

【0081】

その後、実施例1と同様にして有機絶縁物材料から成る第2の層間絶縁膜159、ソース線160〜164、ドレイン線165〜168、画素電極169、171を形成してアクティブマトリクス基板を完成させることができる。図7(A)、(B)はこの状態の上面図を示し、図7(A)のB−B'断面および図7(B)のC−C'断面は図5(C)のB−B'およびC−C'に対応している。図7(A)、(B)ではゲート絶縁膜、第1の層間絶縁膜、第2の層間絶縁膜を省略して示しているが、島状半導体層104、105、108の図示されていないソースおよびドレイン領域にソース線160、161、164とドレイン線165、166、及び画素電極169がコンタクトホールを介して接続している。また、図7(A)のD−D'断面および図6(B)のE−E'断面を図8(A)と(B)にそれぞれ示す。ゲート線173はゲート電極220と、またゲート線174はゲート電極225と島状半導体層104、108の外側で重なるように形成され、ゲート電極と低抵抗導電層とがコンタクトホールを介さずに接触して電気的に導通している。このようにゲート線を低抵抗導電材料で形成することにより、配線抵抗を十分低減できる。従って、画素部(画面サイズ)が4インチクラス以上の表示装置に適用することができる。

【0082】

[実施例3]

実施例1で作製したアクティブマトリクス基板はそのまま反射型の表示装置に適用することができる。一方、透過型の液晶表示装置とする場合には画素部の各画素に設ける画素電極を透明電極で形成すれば良い。本実施例では透過型の液晶表示装置に対応するアクティブマトリクス基板の作製方法について図10を用いて説明する。

【0083】

アクティブマトリクス基板は実施例1と同様に作製する。図10(A)では、ソース配線とドレイン配線は導電性の金属膜をスパッタ法や真空蒸着法で形成する。ドレイン線256を例としてこの構成を図10(B)で詳細に説明すると、Ti膜256aを50〜150nmの厚さで形成し、島状半導体層のソースまたはドレイン領域を形成する半導体膜とコンタクトを形成する。そのTi膜256a上に重ねてAl膜256bを300〜400nmの厚さで形成し、さらにTi膜256cまたは窒化チタン(TiN)膜を100〜200nmの厚さで形成して3層構造とする。その後、透明導電膜を全面に形成し、フォトマスクを用いたパターニング処理およびエッチング処理により画素電極257を形成する。画素電極257は、有機樹脂材料から成る第2の層間絶縁膜上に形成され、コンタクトホールを介さずに画素TFT204のドレイン線256と重なる部分を設け電気的な接続を形成している。

【0084】

図10(C)では最初に第2の層間絶縁膜上に透明導電膜を形成し、パターニング処理およびエッチング処理をして画素電極258を形成した後、ドレイン線259を画素電極258とコンタクトホールを介さずに接続部を形成した例である。ドレイン線259は、図10(D)で示すようにTi膜259aを50〜150nmの厚さで形成し、島状半導体層のソースまたはドレイン領域を形成する半導体膜とコンタクトを形成し、そのTi膜259a上に重ねてAl膜259bを300〜400nmの厚さで形成して設ける。この構成にすると、画素電極258はドレイン配線259を形成するTi膜259aのみと接触することになる。その結果、透明導電膜材料とAlとが直接接し反応するのを確実に防止できる。

【0085】

透明導電膜の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2;ITO)などをスパッタ法や真空蒸着法などを用いて形成して用いることができる。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金(In2O3―ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOに対して熱安定性にも優れているので、図20(A)、(B)の構成においてドレイン配線256の端面で、Al膜256bが画素電極257と接触して腐蝕反応をすることを防止できる。同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができる。

【0086】

実施例1では反射型の液晶表示装置を作製できるアクティブマトリクス基板を5枚のフォトマスクにより作製したが、さらに1枚のフォトマスクの追加(合計6枚)で、透過型の液晶表示装置に対応したアクティブマトリクス基板を完成させることができる。本実施例では、実施例1と同様な工程として説明したが、このような構成は実施例2で示すアクティブマトリクス基板に適用することができる。

【0087】

[実施例4]

本実施例では、実施例1〜実施例3で示したアクティブマトリクス基板のTFTの活性層を形成する結晶質半導体層の他の作製方法について示す。結晶質半導体層は非晶質半導体層を熱アニール法やレーザーアニール法、またはRTA法などで結晶化させて形成するが、その他に特開平7−130652号公報で開示されている触媒元素を用いる結晶化法を適用することもできる。その場合の例を図12を用いて説明する。

【0088】

図12(A)で示すように、実施例1と同様にして、ガラス基板1101上に下地膜1102a、1102b、非晶質構造を有する半導体層1103を25〜80nmの厚さで形成する。非晶質半導体層は非晶質シリコン(a−Si)膜、非晶質シリコンゲルマニウム(a−SiGe)膜、非晶質炭化シリコン(a−SiC)膜,非晶質シリコン・スズ(a−SiSn)膜などが適用できる。これらの非晶質半導体層は水素を0.1〜40atomic%程度含有するようにして形成すると良い。例えば、非晶質シリコン膜を55nmの厚さで形成する。そして、重量換算で10ppmの触媒元素を含む水溶液をスピナーで基板を回転させて塗布するスピンコート法で触媒元素を含有する層1104を形成する。触媒元素にはニッケル(Ni)、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)などである。この触媒元素を含有する層1104は、スピンコート法の他に印刷法やスプレー法、バーコーター法、或いはスパッタ法や真空蒸着法によって上記触媒元素の層を1〜5nmの厚さに形成しても良い。

【0089】

そして、図12(B)に示す結晶化の工程では、まず400〜500℃で1時間程度の熱処理を行い、非晶質シリコン膜の含有水素量を5atomic%以下にする。非晶質シリコン膜の含有水素量が成膜後において最初からこの値である場合にはこの熱処理は必ずしも必要でない。そして、ファーネスアニール炉を用い、窒素雰囲気中で550〜600℃で1〜8時間の熱アニールを行う。以上の工程により結晶質シリコン膜から成る結晶質半導体層1105を得ることができる(図12(C))。しかし、この熱アニールによって作製された結晶質半導体層1105は、光学顕微鏡観察により巨視的に観察すると局所的に非晶質領域が残存していることが観察されることがあり、このような場合、同様にラマン分光法では480cm-1にブロードなピークを持つ非晶質成分が観測される。そのため、熱アニールの後に実施例1で説明したレーザーアニール法で結晶質半導体層1105を処理してその結晶性を高めることは有効な手段として適用できる。

【0090】

図17は同様に触媒元素を用いる結晶化法の実施例であり、触媒元素を含有する層をスパッタ法により形成するものである。まず、実施例1と同様にして、ガラス基板1201上に下地膜1202a、1202b、非晶質構造を有する半導体層1203を25〜80nmの厚さで形成する。そして、非晶質構造を有する半導体層1203の表面に0.5〜5nm程度の酸化膜(図示せず)を形成する。このような厚さの酸化膜は、プラズマCVD法やスパッタ法などで積極的に該当する被膜を形成しても良いが、100〜300℃に基板を加熱してプラズマ化した酸素雰囲気中に非晶質構造を有する半導体層1203の表面を晒しても良いし、過酸化水素水(H2O2)を含む溶液に非晶質構造を有する半導体層1203の表面を晒して形成しても良い。或いは、酸素を含む雰囲気中で紫外線光を照射してオゾンを発生させ、そのオゾン雰囲気中に非晶質構造を有する半導体層1203を晒すことによっても形成できる。

【0091】

このようにして表面に薄い酸化膜を有する非晶質構造を有する半導体層1203上に前記触媒元素を含有する層1204をスパッタ法で形成する。この層の厚さに限定はないが、10〜100nm程度の厚さに形成すれば良い。例えば、Niをターゲットとして、Ni膜を形成することは有効な方法である。スパッタ法では、電界で加速された前記触媒元素から成る高エネルギー粒子の一部が基板側にも飛来し、非晶質構造を有する半導体層1203の表面近傍、または該半導体層表面に形成した酸化膜中に打ち込まれる。その割合はプラズマ生成条件や基板のバイアス状態によって異なるものであるが、好適には非晶質構造を有する半導体層1203の表面近傍や該酸化膜中に打ち込まれる触媒元素の量を1×1011〜1×1014atoms/cm2程度となるようにすると良い。

【0092】

その後、触媒元素を含有する層1204を選択的に除去する。例えば、この層がNi膜で形成されている場合には、硝酸などの溶液で除去することが可能であり、または、フッ酸を含む水溶液で処理すればNi膜と非晶質構造を有する半導体層1203上に形成した酸化膜を同時に除去できる。いずれにしても、非晶質構造を有する半導体層1203の表面近傍の触媒元素の量を1×1011〜1×1014atoms/cm2程度となるようにしておく。そして、図17(B)で示すように、図12(B)と同様にして熱アニールによる結晶化の工程を行い、結晶質半導体層1205を得ることができる(図17(C))。

【0093】

図12または図17で作製された結晶質半導体層1105、1205から島状半導体層104〜108を作製すれば、実施例1と同様にしてアクティブマトリクス基板を完成させることができる。しかし、結晶化の工程においてシリコンの結晶化を助長する触媒元素を使用した場合、島状半導体層中には微量(1×1017〜1×1019atoms/cm3程度)の触媒元素が残留する。勿論、そのような状態でもTFTを完成させることが可能であるが、残留する触媒元素を少なくともチャネル形成領域から除去する方がより好ましかった。この触媒元素を除去する手段の一つにリン(P)によるゲッタリング作用を利用する手段がある。

【0094】

この目的におけるリン(P)によるゲッタリング処理は、図5(A)で説明した活性化工程で同時に行うことができる。この様子を図13で説明する。ゲッタリングに必要なリン(P)の濃度は高濃度n型不純物領域の不純物濃度と同程度でよく、活性化工程の熱アニールにより、nチャネル型TFTおよびpチャネル型TFTのチャネル形成領域から触媒元素をその濃度でリン(P)を含有する不純物領域へ偏析させることができる(図13で示す矢印の方向)。その結果その不純物領域には1×1017〜1×1019atoms/cm3程度の触媒元素が偏析した。このようにして作製したTFTはオフ電流値が下がり、結晶性が良いことから高い電界効果移動度が得られ、良好な特性を達成することができる。本実施例の構成は、実施例1〜3と組み合わせることができる。

【0095】

[実施例5]

本実施例では実施例1で作製したアクティブマトリクス基板から、アクティブマトリクス型液晶表示装置を作製する工程を説明する。まず、図14(A)に示すように、図5(B)の状態のアクティブマトリクス基板に柱状スペーサから成るスペーサを形成する。スペーサは数μmの粒子を散布して設ける方法でも良いが、ここでは基板全面に樹脂膜を形成した後これをパターニングして形成する方法を採用した。このようなスペーサの材料に限定はないが、例えば、JSR社製のNN700を用い、スピナーで塗布した後、露光と現像処理によって所定のパターンに形成する。さらにクリーンオーブンなどで150〜200℃で加熱して硬化させる。このようにして作製されるスペーサは露光と現像処理の条件によって形状を異ならせることができるが、好ましくは、スペーサの形状は柱状で頂部が平坦な形状となるようにすると、対向側の基板を合わせたときに液晶表示パネルとしての機械的な強度を確保することができる。形状は円錐状、角錐状など特別の限定はないが、例えば円錐状としたときに具体的には、高さを1.2〜5μmとし、平均半径を5〜7μm、平均半径と底部の半径との比を1対1.5とする。このとき側面のテーパー角は±15°以下とする。

【0096】

スペーサの配置は任意に決定すれば良いが、好ましくは、図14(A)で示すように、画素部においては画素電極169のコンタクト部231と重ねてその部分を覆うように柱状スペーサ406を形成すると良い。コンタクト部231は平坦性が損なわれこの部分では液晶がうまく配向しなくなるので、このようにしてコンタクト部231にスペーサ用の樹脂を充填する形で柱状スペーサ406を形成することでディスクリネーションなどを防止することができる。また、駆動回路のTFT上にもスペーサ405a〜405eを形成しておく。このスペーサは駆動回路部の全面に渡って形成しても良いし、図14で示すようにソース線およびドレイン線を覆うようにして設けても良い。

【0097】

その後、配向膜407を形成する。通常液晶表示素子の配向膜にはポリイミド樹脂を用いる。配向膜を形成した後、ラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにした。画素部に設けた柱状スペーサ406の端部からラビング方向に対してラビングされない領域が2μm以下となるようにした。また、ラビング処理では静電気の発生がしばしば問題となるが、駆動回路のTFT上に形成したスペーサ405a〜405eにより静電気からTFTを保護する効果を得ることができる。また図では説明しないが、配向膜407を先に形成してから、スペーサ406、405a〜405eを形成した構成としても良い。

【0098】

対向側の対向基板401には、遮光膜402、透明導電膜403および配向膜404を形成する。遮光膜402はTi膜、Cr膜、Al膜などを150〜300nmの厚さで形成する。そして、画素部と駆動回路が形成されたアクティブマトリクス基板と対向基板とをシール剤408で貼り合わせる。シール剤408にはフィラー(図示せず)が混入されていて、このフィラーとスペーサ406、405a〜405eによって均一な間隔を持って2枚の基板が貼り合わせられる。その後、両基板の間に液晶材料409を注入する。液晶材料には公知の液晶材料を用いれば良い。例えば、TN液晶の他に、電場に対して透過率が連続的に変化する電気光学応答性を示す、無しきい値反強誘電性混合液晶を用いることもできる。この無しきい値反強誘電性混合液晶には、V字型の電気光学応答特性を示すものもある。このようにして図14(B)に示すアクティブマトリクス型液晶表示装置が完成する。

【0099】

図15はこのようなアクティブマトリクス基板の上面図を示し、画素部および駆動回路部とスペーサおよびシール剤の位置関係を示す上面図である。実施例1で述べたガラス基板101上に画素部604の周辺に駆動回路として走査信号駆動回路605と画像信号駆動回路606が設けられている。さらに、その他CPUやメモリなどの信号処理回路607も付加されていても良い。そして、これらの駆動回路は接続配線603によって外部入出力端子602と接続されている。画素部604では走査信号駆動回路605から延在するゲート配線群608と画像信号駆動回路606から延在するソース配線群609がマトリクス状に交差して画素を形成し、各画素にはそれぞれ画素TFT204と保持容量205が設けられている。

【0100】

図14において画素部において設けた柱状スペーサ406は、すべての画素に対して設けても良いが、図15で示すようにマトリクス状に配列した画素の数個から数十個おきに設けても良い。即ち、画素部を構成する画素の全数に対するスペーサの数の割合は20〜100%とすることが可能である。また、駆動回路部に設けるスペーサ405a〜405eはその全面を覆うように設けても良いし各TFTのソースおよびドレイン配線の位置にあわせて設けても良い。図15では駆動回路部に設けるスペーサの配置を610〜612で示す。そして、図15示すシール剤619は、基板101上の画素部604および走査信号駆動回路605、画像信号駆動回路606、その他の信号処理回路607の外側であって、外部入出力端子602よりも内側に形成する。

【0101】

このようなアクティブマトリクス型液晶表示装置の構成を図16の斜視図を用いて説明する。図16においてアクティブマトリクス基板は、ガラス基板101上に形成された、画素部604と、走査信号駆動回路605と、画像信号駆動回路606とその他の信号処理回路607とで構成される。画素部604には画素TFT204と保持容量205が設けられ、画素部の周辺に設けられる駆動回路はCMOS回路を基本として構成されている。走査信号駆動回路605と画像信号駆動回路606からは、それぞれゲート線(ゲート電極と連続して形成されている場合は図5(B)の224に相当する)とソース線164が画素部604に延在し、画素TFT204に接続している。また、フレキシブルプリント配線板(Flexible Printed Circuit:FPC)613が外部入力端子602に接続していて画像信号などを入力するのに用いる。FPC613は補強樹脂614によって強固に接着されている。そして接続配線603でそれぞれの駆動回路に接続している。また、対向基板401には図示していない、遮光膜や透明電極が設けられている。

【0102】

このような構成の液晶表示装置は、実施例1〜3で示したアクティブマトリクス基板を用いて形成することができる。実施例1で示すアクティブマトリクス基板を用いれば反射型の液晶表示装置が得られ、実施例3で示すアクティブマトリクス基板を用いると透過型の液晶表示装置を得ることができる。

【0103】

[実施例6]

図18は実施例1〜3で示したアクティブマトリクス基板の回路構成の一例であり、直視型の表示装置の回路構成を示す図である。このアクティブマトリクス基板は、画像信号駆動回路606、走査信号駆動回路(A)(B)605、画素部604を有している。尚、本明細書中において記した駆動回路とは、画像信号駆動回路606、走査信号駆動回路605を含めた総称である。

【0104】

画像信号駆動回路606は、シフトレジスタ回路501a、レベルシフタ回路502a、バッファ回路503a、サンプリング回路504を備えている。また、走査信号駆動回路(A)(B)185は、シフトレジスタ回路501b、レベルシフタ回路502b、バッファ回路503bを備えている。

【0105】

シフトレジスタ回路501a、501bは駆動電圧が5〜16V(代表的には10V)であり、この回路を形成するCMOS回路のTFTは、図5(B)の第1のpチャネル型TFT200と第1のnチャネル型TFT201で形成する。或いは、図9(A)で示す第1のpチャネル型TFT280と第1のnチャネル型TFT281で形成しても良い。また、レベルシフタ回路502a、502bやバッファ回路503a、503bは駆動電圧が14〜16Vと高くなるので図9(A)で示すようなマルチゲートのTFT構造とすることが望ましい。マルチゲート構造でTFTを形成すると耐圧が高まり、回路の信頼性を向上させる上で有効である。

【0106】

サンプリング回路504はアナログスイッチから成り、駆動電圧が14〜16Vであるが、極性が交互に反転して駆動される上、オフ電流値を低減させる必要があるため、図5(B)で示す第2のpチャネル型TFT202と第2のnチャネル型TFT203で形成することが望ましい。或いは、オフ電流値を効果的に低減させるために図9(B)で示す第2のpチャネル型TFT282と第2のnチャネル型TFT283で形成しても良い。

【0107】

また、画素部は駆動電圧が14〜16Vであり、低消費電力化の観点からサンプリング回路よりもさらにオフ電流値を低減することが要求され、図5(B)で示す画素TFT204のようにマルチゲート構造を基本とする。

【0108】

尚、本実例の構成は、実施例1〜3に示した工程に従ってTFTを作製することによって容易に実現することができる。本実施例では、画素部と駆動回路の構成のみを示しているが、実施例1〜3の工程に従えば、その他にも信号分割回路、分周波回路、D/Aコンバータ、γ補正回路、オペアンプ回路、さらにメモリ回路や演算処理回路などの信号処理回路、あるいは論理回路を同一基板上に形成することが可能である。このように、本発明は同一基板上に画素部とその駆動回路とを含む半導体装置、例えば信号制御回路および画素部を具備した液晶表示装置を実現することができる。

【0109】

[実施例7]

本実施例では、実施例5のアクティブマトリクス基板を用いてエレクトロルミネッセンス(EL:Electro Luminescence)材料を用いた自発光型の表示パネル(以下、EL表示装置と記す)を作製する例について説明する。図19(A)は本発明を用いたEL表示パネルの上面図である。図19(A)において、10は基板、11は画素部、12はソース側駆動回路、13はゲート側駆動回路であり、それぞれの駆動回路は配線14〜16を経てFPC17に至り、外部機器へと接続される。

【0110】

図19(B)は図19(A)のA−A'断面を表す図であり、このとき少なくとも画素部上、好ましくは駆動回路及び画素部上に対向板80を設ける。対向板80はシール材19でTFTとEL層が形成されているアクティブマトリクス基板と貼り合わされている。シール剤19にはフィラー(図示せず)が混入されていて、このフィラーによりほぼ均一な間隔を持って2枚の基板が貼り合わせられている。さらに、シール材19の外側とFPC17の上面及び周辺は封止剤81で密封する構造とする。封止剤81はシリコーン樹脂、エポキシ樹脂、フェノール樹脂、ブチルゴムなどの材料を用いる。

【0111】

このように、シール剤19によりアクティブマトリクス基板10と対向基板80とが貼り合わされると、その間には空間が形成される。その空間には充填剤83が充填される。この充填剤83は対向板80を接着する効果も合わせ持つ。充填剤83はPVC(ポリビニルクロライド)、エポキシ樹脂、シリコーン樹脂、PVB(ポリビニルブチラル)またはEVA(エチレンビニルアセテート)などを用いることができる。また、EL層は水分をはじめ湿気に弱く劣化しやすいので、この充填剤83の内部に酸化バリウムなどの乾燥剤を混入させておくと吸湿効果を保持できるので望ましい。また、EL層上に窒化シリコン膜や酸化窒化シリコン膜などで形成するパッシベーション膜82を形成し、充填剤83に含まれるアルカリ元素などによる腐蝕を防ぐ構造としていある。

【0112】

対向板80にはガラス板、アルミニウム板、ステンレス板、FRP(Fiberglass-Reinforced Plastics)板、PVF(ポリビニルフルオライド)フィルム、マイラーフィルム(デュポン社の商品名)、ポリエステルフィルム、アクリルフィルムまたはアクリル板などを用いることができる。また、数十μmのアルミニウム箔をPVFフィルムやマイラーフィルムで挟んだ構造のシートを用い、耐湿性を高めることもできる。このようにして、EL素子は密閉された状態となり外気から遮断されている。

【0113】

また、図19(B)において基板10、下地膜21の上に駆動回路用TFT(但し、ここではnチャネル型TFTとpチャネル型TFTを組み合わせたCMOS回路を図示している。)22及び画素部用TFT23(但し、ここではEL素子への電流を制御するTFTだけ図示している。)が形成されている。これらのTFTの内特にnチャネル型TFTにははホットキャリア効果によるオン電流の低下や、Vthシフトやバイアスストレスによる特性低下を防ぐため、本実施形態で示す構成のLDD領域が設けられている。

【0114】

例えば、駆動回路用TFT22とし、図5(b)に示すpチャネル型TFT200、202とnチャネル型TFT201、203を用いれば良い。また、画素部用TFT23には図5(B)に示す画素TFT204またはそれと同様な構造を有するpチャネル型TFTを用いれば良い。

【0115】

図5(B)または図6(B)の状態のアクティブマトリクス基板からEL表示装置を作製するには、ソース線、ドレイン線上に樹脂材料でなる層間絶縁膜(平坦化膜)26を形成し、その上に画素部用TFT23のドレインと電気的に接続する透明導電膜でなる画素電極27を形成する。透明導電膜としては、酸化インジウムと酸化スズとの化合物(ITOと呼ばれる)または酸化インジウムと酸化亜鉛との化合物を用いることができる。そして、画素電極27を形成したら、絶縁膜28を形成し、画素電極27上に開口部を形成する。

【0116】

次に、EL層29を形成する。EL層29は公知のEL材料(正孔注入層、正孔輸送層、発光層、電子輸送層または電子注入層)を自由に組み合わせて積層構造または単層構造とすれば良い。どのような構造とするかは公知の技術を用いれば良い。また、EL材料には低分子系材料と高分子系(ポリマー系)材料がある。低分子系材料を用いる場合は蒸着法を用いるが、高分子系材料を用いる場合には、スピンコート法、印刷法またはインクジェット法等の簡易な方法を用いることが可能である。

【0117】

EL層はシャドーマスクを用いて蒸着法、またはインクジェット法、ディスペンサー法などで形成する。いずれにしても、画素毎に波長の異なる発光が可能な発光層(赤色発光層、緑色発光層及び青色発光層)を形成することで、カラー表示が可能となる。その他にも、色変換層(CCM)とカラーフィルターを組み合わせた方式、白色発光層とカラーフィルターを組み合わせた方式があるがいずれの方法を用いても良い。勿論、単色発光のEL表示装置とすることもできる。

【0118】

EL層29を形成したら、その上に陰極30を形成する。陰極30とEL層29の界面に存在する水分や酸素は極力排除しておくことが望ましい。従って、真空中でEL層29と陰極30を連続して形成するか、EL層29を不活性雰囲気で形成し、大気解放しないで真空中で陰極30を形成するといった工夫が必要である。本実施例ではマルチチャンバー方式(クラスターツール方式)の成膜装置を用いることで上述のような成膜を可能とする。

【0119】

なお、本実施例では陰極30として、LiF(フッ化リチウム)膜とAl(アルミニウム)膜の積層構造を用いる。具体的にはEL層29上に蒸着法で1nm厚のLiF(フッ化リチウム)膜を形成し、その上に300nm厚のアルミニウム膜を形成する。勿論、公知の陰極材料であるMgAg電極を用いても良い。そして陰極30は31で示される領域において配線16に接続される。配線16は陰極30に所定の電圧を与えるための電源供給線であり、異方性導電性ペースト材料32を介してFPC17に接続される。FPC17上にはさらに樹脂層80が形成され、この部分の接着強度を高めている。

【0120】

31に示された領域において陰極30と配線16とを電気的に接続するために、層間絶縁膜26及び絶縁膜28にコンタクトホールを形成する必要がある。これらは層間絶縁膜26のエッチング時(画素電極用コンタクトホールの形成時)や絶縁膜28のエッチング時(EL層形成前の開口部の形成時)に形成しておけば良い。また、絶縁膜28をエッチングする際に、層間絶縁膜26まで一括でエッチングしても良い。この場合、層間絶縁膜26と絶縁膜28が同じ樹脂材料であれば、コンタクトホールの形状を良好なものとすることができる。

【0121】

また、配線16はシール19と基板10との間を隙間(但し封止剤81で塞がれている。)を通ってFPC17に電気的に接続される。なお、ここでは配線16について説明したが、他の配線14、15も同様にしてシーリング材18の下を通ってFPC17に電気的に接続される。

【0122】

ここで画素部のさらに詳細な断面構造を図20に、上面構造を図21(A)に、回路図を図21(B)に示す。図20(A)において、基板2401上に設けられたスイッチング用TFT2402は実施例1の図5(B)の画素TFT204と同じ構造で形成される。ダブルゲート構造とすることで実質的に二つのTFTが直列された構造となり、オフ電流値を低減することができるという利点がある。なお、本実施例ではダブルゲート構造としているがトリプルゲート構造やそれ以上のゲート本数を持つマルチゲート構造でも良い。

【0123】

また、電流制御用TFT2403は図5(B)で示すnチャネル型TFT201を用いて形成する。このとき、スイッチング用TFT2402のドレイン線35は配線36によって電流制御用TFTのゲート電極37に電気的に接続されている。また、38で示される配線は、スイッチング用TFT2402のゲート電極39a、39bを電気的に接続するゲート線である。

【0124】

このとき、電流制御用TFT2403が本発明の構造であることは非常に重要な意味を持つ。電流制御用TFTはEL素子を流れる電流量を制御するための素子であるため、多くの電流が流れ、熱による劣化やホットキャリアによる劣化の危険性が高い素子でもある。そのため、電流制御用TFTにゲート電極と一部が重なるLDD領域を設けることでTFTの劣化を防ぎ、動作の安定性を高めることができる。

【0125】

また、本実施例では電流制御用TFT2403をシングルゲート構造で図示しているが、複数のTFTを直列につなげたマルチゲート構造としても良い。さらに、複数のTFTを並列につなげて実質的にチャネル形成領域を複数に分割し、熱の放射を高い効率で行えるようにした構造としても良い。このような構造は熱による劣化対策として有効である。

【0126】

また、図21(A)に示すように、電流制御用TFT2403のゲート電極37となる配線は2404で示される領域で、電流制御用TFT2403のドレイン線40と絶縁膜を介して重なる。このとき、2404で示される領域ではコンデンサが形成される。このコンデンサ2404は電流制御用TFT2403のゲートにかかる電圧を保持するためのコンデンサとして機能する。なお、ドレイン線40は電流供給線(電源線)2501に接続され、常に一定の電圧が加えられている。

【0127】

スイッチング用TFT2402及び電流制御用TFT2403の上には第1パッシベーション膜41が設けられ、その上に樹脂絶縁膜でなる平坦化膜42が形成される。平坦化膜42を用いてTFTによる段差を平坦化することは非常に重要である。後に形成されるEL層は非常に薄いため、段差が存在することによって発光不良を起こす場合がある。従って、EL層をできるだけ平坦面に形成しうるように画素電極を形成する前に平坦化しておくことが望ましい。

【0128】

また、43は反射性の高い導電膜でなる画素電極(EL素子の陰極)であり、電流制御用TFT2403のドレインに電気的に接続される。画素電極43としてはアルミニウム合金膜、銅合金膜または銀合金膜など低抵抗な導電膜またはそれらの積層膜を用いることが好ましい。勿論、他の導電膜との積層構造としても良い。また、絶縁膜(好ましくは樹脂)で形成されたバンク44a、44bにより形成された溝(画素に相当する)の中に発光層44が形成される。なお、ここでは一画素しか図示していないが、R(赤)、G(緑)、B(青)の各色に対応した発光層を作り分けても良い。発光層とする有機EL材料としてはπ共役ポリマー系材料を用いる。代表的なポリマー系材料としては、ポリパラフェニレンビニレン(PPV)系、ポリビニルカルバゾール(PVK)系、ポリフルオレン系などが挙げられる。 なお、PPV系有機EL材料としては様々な型のものがあるが、例えば「H. Shenk, H.Becker, O.Gelsen, E.Kluge, W.Kreuder and H.Spreitzer,“Polymers for Light Emitting Diodes”,Euro Display,Proceedings,1999,p.33-37」や特開平10−92576号公報に記載されたような材料を用いれば良い。

【0129】

具体的な発光層としては、赤色に発光する発光層にはシアノポリフェニレンビニレン、緑色に発光する発光層にはポリフェニレンビニレン、青色に発光する発光層にはポリフェニレンビニレン若しくはポリアルキルフェニレンを用いれば良い。膜厚は30〜150nm(好ましくは40〜100nm)とすれば良い。但し、以上の例は発光層として用いることのできる有機EL材料の一例であって、これに限定する必要はまったくない。発光層、電荷輸送層または電荷注入層を自由に組み合わせてEL層(発光及びそのためのキャリアの移動を行わせるための層)を形成すれば良い。例えば、本実施例ではポリマー系材料を発光層として用いる例を示したが、低分子系有機EL材料を用いても良い。また、電荷輸送層や電荷注入層として炭化珪素等の無機材料を用いることも可能である。これらの有機EL材料や無機材料は公知の材料を用いることができる。

【0130】

本実施例では発光層45の上にPEDOT(ポリチオフェン)またはPAni(ポリアニリン)でなる正孔注入層46を設けた積層構造のEL層としている。そして、正孔注入層46の上には透明導電膜でなる陽極47が設けられる。本実施例の場合、発光層45で生成された光は上面側に向かって(TFTの上方に向かって)放射されるため、陽極は透光性でなければならない。透明導電膜としては酸化インジウムと酸化スズとの化合物や酸化インジウムと酸化亜鉛との化合物を用いることができるが、耐熱性の低い発光層や正孔注入層を形成した後で形成するため、可能な限り低温で成膜できるものが好ましい。

【0131】

陽極47まで形成された時点でEL素子2405が完成する。なお、ここでいうEL素子2405は、画素電極(陰極)43、発光層45、正孔注入層46及び陽極47で形成されたコンデンサを指す。図22(A)に示すように画素電極43は画素の面積にほぼ一致するため、画素全体がEL素子として機能する。従って、発光の利用効率が非常に高く、明るい画像表示が可能となる。

【0132】

ところで、本実施例では、陽極47の上にさらに第2パッシベーション膜48を設けている。第2パッシベーション膜48としては窒化珪素膜または窒化酸化珪素膜が好ましい。この目的は、外部とEL素子とを遮断することであり、有機EL材料の酸化による劣化を防ぐ意味と、有機EL材料からの脱ガスを抑える意味との両方を併せ持つ。これによりEL表示装置の信頼性が高められる。

【0133】

以上のように本願発明のEL表示パネルは図21のような構造の画素からなる画素部を有し、オフ電流値の十分に低いスイッチング用TFTと、ホットキャリア注入に強い電流制御用TFTとを有する。従って、高い信頼性を有し、且つ、良好な画像表示が可能なEL表示パネルが得られる。

【0134】

図20(B)はEL層の構造を反転させた例を示す。電流制御用TFT2601は図5(B)のpチャネル型TFT200を用いて形成される。作製プロセスは実施例1を参照すれば良い。本実施例では、画素電極(陽極)50として透明導電膜を用いる。具体的には酸化インジウムと酸化亜鉛との化合物でなる導電膜を用いる。勿論、酸化インジウムと酸化スズとの化合物でなる導電膜を用いても良い。

【0135】

そして、絶縁膜でなるバンク51a、51bが形成された後、溶液塗布によりポリビニルカルバゾールでなる発光層52が形成される。その上にはカリウムアセチルアセトネート(acacKと表記される)でなる電子注入層53、アルミニウム合金でなる陰極54が形成される。この場合、陰極54がパッシベーション膜としても機能する。こうしてEL素子2602が形成される。本実施例の場合、発光層53で発生した光は、矢印で示されるようにTFTが形成された基板の方に向かって放射される。本実施例のような構造とする場合、電流制御用TFT2601はpチャネル型TFTで形成することが好ましい。

【0136】

尚、本実施例の構成は、実施例1〜2のTFTの構成を自由に組み合わせて実施することが可能である。また、実施例9の電子機器の表示部として本実施例のEL表示パネルを用いることは有効である。

【0137】

[実施例8]

本実施例では、図21(B)に示した回路図とは異なる構造の画素とした場合の例について図22に示す。なお、本実施例において、2701はスイッチング用TFT2702のソース配線、2703はスイッチング用TFT2702のゲート配線、2704は電流制御用TFT、2705はコンデンサ、2706、2708は電流供給線、2707はEL素子とする。

【0138】

図22(A)は、二つの画素間で電流供給線2706を共通とした場合の例である。即ち、二つの画素が電流供給線2706を中心に線対称となるように形成されている点に特徴がある。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。

【0139】

また、図22(B)は、電流供給線2708をゲート配線2703と平行に設けた場合の例である。なお、図22(B)では電流供給線2708とゲート配線2703とが重ならないように設けた構造となっているが、両者が異なる層に形成される配線であれば、絶縁膜を介して重なるように設けることもできる。この場合、電源供給線2708とゲート配線2703とで専有面積を共有させることができるため、画素部をさらに高精細化することができる。

【0140】

また、図22(C)は、図22(B)の構造と同様に電流供給線2708をゲート配線2703と平行に設け、さらに、二つの画素を電流供給線2708を中心に線対称となるように形成する点に特徴がある。また、電流供給線2708をゲート配線2703のいずれか一方と重なるように設けることも有効である。この場合、電源供給線の本数を減らすことができるため、画素部をさらに高精細化することができる。図22(A)、図22(B)では電流制御用TFT2404のゲートにかかる電圧を保持するためにコンデンサ2405を設ける構造としているが、コンデンサ2405を省略することも可能である。

【0141】

電流制御用TFT2404として図20(A)に示すような本願発明のnチャネル型TFTを用いているため、ゲート絶縁膜を介してゲート電極(と重なるように設けられたLDD領域を有している。この重なり合った領域には一般的にゲート容量と呼ばれる寄生容量が形成されるが、本実施例ではこの寄生容量をコンデンサ2405の代わりとして積極的に用いる点に特徴がある。この寄生容量のキャパシタンスは上記ゲート電極とLDD領域とが重なり合った面積で変化するため、その重なり合った領域に含まれるLDD領域の長さによって決まる。また、図22(A)、(B)、(C)の構造においても同様にコンデンサ2705を省略することは可能である。

【0142】

尚、本実施例の構成は、実施例1〜2のTFTの構成を自由に組み合わせて実施することが可能である。また、実施例9の電子機器の表示部として本実施例のEL表示パネルを用いることは有効である。

【0143】

[実施例9]

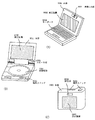

本実施例では、本発明のTFT回路によるアクティブマトリクス型液晶表示装置を組み込んだ半導体装置について図23、図24、図25で説明する。

【0144】

このような半導体装置には、携帯情報端末(電子手帳、モバイルコンピュータ、携帯電話等)、ビデオカメラ、スチルカメラ、パーソナルコンピュータ、テレビ等が挙げられる。それらの一例を図23と図24に示す。

【0145】

図23(A)は携帯電話であり、本体9001、音声出力部9002、音声入力部9003、表示装置9004、操作スイッチ9005、アンテナ9006から構成されている。本願発明は音声出力部9002、音声入力部9003、及びアクティブマトリクス基板を備えた表示装置9004に適用することができる。

【0146】

図23(B)はビデオカメラであり、本体9101、表示装置9102、音声入力部9103、操作スイッチ9104、バッテリー9105、受像部9106から成っている。本願発明は音声入力部9103、及びアクティブマトリクス基板を備えた表示装置9102、受像部9106に適用することができる。

【0147】

図23(C)はモバイルコンピュータ或いは携帯型情報端末であり、本体9201、カメラ部9202、受像部9203、操作スイッチ9204、表示装置9205で構成されている。本願発明は受像部9203、及びアクティブマトリクス基板を備えた表示装置9205に適用することができる。

【0148】

図23(D)はヘッドマウントディスプレイであり、本体9301、表示装置9302、アーム部9303で構成される。本願発明は表示装置9302に適用することができる。また、表示されていないが、その他の信号制御用回路に使用することもできる。

【0149】

図23(E)はリア型プロジェクターであり、本体9401、光源9402、表示装置9403、偏光ビームスプリッタ9404、リフレクター9405、9406、スクリーン9407で構成される。本発明は表示装置9403に適用することができる。

【0150】

図23(F)は携帯書籍であり、本体9501、表示装置9502、9503、記憶媒体9504、操作スイッチ9505、アンテナ9506から構成されており、ミニディスク(MD)やDVDに記憶されたデータや、アンテナで受信したデータを表示するものである。表示装置9502、9503は直視型の表示装置であり、本発明はこの適用することができる。

【0151】

図24(A)はパーソナルコンピュータであり、本体9601、画像入力部9602、表示装置9603、キーボード9604で構成される。

【0152】

図24(B)はプログラムを記録した記録媒体(以下、記録媒体と呼ぶ)を用いるプレーヤーであり、本体9701、表示装置9702、スピーカ部9703、記録媒体9704、操作スイッチ9705で構成される。なお、この装置は記録媒体としてDVD(Digital Versatile Disc)、CD等を用い、音楽鑑賞や映画鑑賞やゲームやインターネットを行うことができる。

【0153】

図24(C)はデジタルカメラであり、本体9801、表示装置9802、接眼部9803、操作スイッチ9804、受像部(図示しない)で構成される。

【0154】

図25(A)はフロント型プロジェクターであり、表示装置3601、スクリーン3602で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。

【0155】

図25(B)はリア型プロジェクターであり、本体3701、投射装置3702、ミラー3703、スクリーン3704で構成される。本発明は表示装置やその他の信号制御回路に適用することができる。

【0156】

なお、図25(C)は、図25(A)及び図25(B)中における投射装置3601、3702の構造の一例を示した図である。投射装置3601、3702は、光源光学系3801、ミラー3802、3804〜3806、ダイクロイックミラー3803、プリズム3807、液晶表示装置3808、位相差板3809、投射光学系3810で構成される。投射光学系3810は、投射レンズを含む光学系で構成される。本実施例は三板式の例を示したが、特に限定されず、例えば単板式であってもよい。また、図25(C)中において矢印で示した光路に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するためのフィルム、IRフィルム等の光学系を設けてもよい。

【0157】

また、図25(D)は、図25(C)中における光源光学系3801の構造の一例を示した図である。本実施例では、光源光学系3801は、リフレクター3811、光源3812、レンズアレイ3813、3814、偏光変換素子3815、集光レンズ3816で構成される。なお、図25(D)に示した光源光学系は一例であって特に限定されない。例えば、光源光学系に実施者が適宜、光学レンズや、偏光機能を有するフィルムや、位相差を調節するフィルム、IRフィルム等の光学系を設けてもよい。

【0158】

また、本発明はその他にも、イメージセンサやEL型表示素子に適用することも可能である。このように、本願発明の適用範囲はきわめて広く、あらゆる分野の電子機器に適用することが可能である。

【0159】

[実施例10]

実施例1において示す第1のエッチング処理と第2のエッチング処理は、ゲート電極の形成を前提としてW、Ta、Ti、Moから選ばれた元素、またはこれらの元素を組み合わせた合金から成る導電膜を対象とするものである。エッチングにおいては、対象とする導電膜のエッチング速度と、下地にある絶縁膜との選択比を特に考慮する必要がある。選択比が小さいと、選択加工が困難となり、所望のTFTを形成することができなくなる。

【0160】

エッチング速度の評価は、ガラス基板上にW膜または酸化窒化シリコン膜を形成した試料を用いて行った。マスクを形成するレジストは1500nmの厚さに形成し、そのエッチング速度も評価した。エッチングはICPエッチング装置を用いて行い、エッチングガスとしてCF4とCl2の混合ガスを用いた場合(条件1)と、CF4とCl2とO2の混合ガスを用いた場合(条件2)について調べた。表1にその結果を示す。

【0161】

【表1】

【0162】

表2はエッチング時間に対する酸化窒化シリコン膜の膜厚の減少量を示す。エッチングは上記と同様に条件1と条件2を比較した。試料はガラス基板上に30nmのシリコン膜と200nmの酸化窒化シリコン膜を積層させたものを用いた。同様に、図26にエッチング時間に対する膜厚の減少量のグラフを示す。

【0163】

【表2】

【0164】

表1と表2の結果において、エッチングガスにO2が添加されている方がW膜のエッチング速度が速くなり、酸化窒化シリコン膜のエッチング速度は低下している。即ち、下地との選択比が向上していることを示している。W膜のエッチング速度が向上するのは、O2の添加によりフッ素ラジカルの量が多くなるためである。また、酸化窒化シリコン膜のエッチング速度が低下するのは、O2の添加によりレジストの成分である炭素が酸素と結合しCO2が形成され、炭素の量が減少するので酸化窒化シリコン膜のエッチング速度が低下するものと考えることができる。

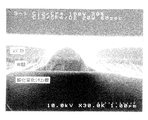

【0165】

エッチングにより加工される導電膜の形状は走査電子顕微鏡(SEM)により観察した。評価した試料は、ガラス基板上に200nmの酸化窒化シリコン膜、400nmのW膜が形成されているものを用いた。第1のエッチング処理(テーパーエッチング)は、エッチング用ガスにCl2を30SCCMとCF4を30SCCM流し、1Paの圧力で3.2W/cm2のRF(13.56MHz)電力を投入し、基板側(試料ステージ)にも224mW/cm2のRF(13.56MHz)電力を投入して行った。図27にこの条件でエッチング処理を行って得られる試料の断面形状をSEMにより観察した結果を示している。W膜の端部に形成されるテーパー部の角度は約30度となっている。

【0166】

その後、上記条件1と条件2により第2のエッチング処理(異方性エッチング)を行い比較評価した。図28は条件1により処理された試料、また図29は条件2により処理された試料をSEMにより観察した結果を示す。図28、図29共に同じ形状が得られている。但し、CF4とCl2の混合ガスにO2を加えることによりW膜のエッチング速度並びにレジストのエッチング速度が向上するので、図29に示す条件2で形成された試料の方が細くなっている。しかし、酸化窒化シリコン膜の膜厚の減少量から見ると、条件2の方が少なく選択加工する上で優れていると判断することができる。

【0167】

以上のような実験結果から、第1のエッチング処理と第2のエッチング処理において、エッチングガスとしてCF4とCl2とO2の混合ガスを採用することができる。このようなエッチングガスを選択したとしても、テーパーエッチングとするか、異方性エッチングとするかは基板側に印加するバイアス電力の制御により行うことができる。

【0168】

実際のTFTにおいてLDDの設計は、W膜の膜厚と、第1のエッチング処理によるテーパー角θ1と、第2のエッチング処理によるレジストのエッチング量から見積もることができる。例えば、図2において、W膜の厚さが400nmである場合、第1のエッチング処理により形成されるテーバー部の角度θ1が30度とすると、第2の不純物領域(A)1012のチャネル長方向の長さは700nmとなる。第2のエッチング処理によるレジストの減少量は表2より94nm/minであるのでそれを考慮すると825nmのLDD(Loff)が形成されると見積もることができる。実際には膜厚やエッチング速度に多少のばらつきがあるので、多少の増減はあるが、このようなエッチング処理により約1μmのLDDを形成することができる。

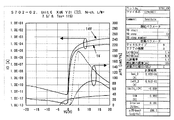

【0169】

図30は第1のエッチング処理として表2の条件を採用し、第2のエッチング処理として表2の条件を採用して作製されたTFTのゲート電圧(Vg)対ドレイン電流(Id)特性を示す。TFTの寸法はチャネル長7.5μm、チャネル幅8μmであり、LDD(Loff)は1μmが見積もられている。図30はnチャネル型TFTの特性を示し、LDD(Loff)によりゲート電圧−4.5V、ドレイン電圧14Vの時のオフ電流は6.5pAが得られている。

【0170】

【発明の効果】

本発明を用いることで、同一の基板上に複数の機能回路が形成された半導体装置(ここでは具体的には電気光学装置)において、その機能回路が要求する仕様に応じて適切な性能のTFTを配置することが可能となり、その動作特性を大幅に向上させることができる。

【0171】

本発明の半導体装置の作製方法に従えば、駆動回路部のpチャネル型TFT、nチャネル型TFTおよび画素TFTをゲート電極と一部が重なるLDD構造としたアクティブマトリクス基板を5枚のフォトマスクで製造することができ、LDD領域の一導電型の不純物元素の濃度を適したものとすることができる。このようなアクティブマトリクス基板から反射型の液晶表示装置を作製することができる。また、同工程に従えば透過型の液晶表示装置を6枚のフォトマスクで製造することができる。

【0172】

本発明の半導体装置の作製方法に従えば、ゲート電極を耐熱性導電性材料で形成し、ゲート配線を低抵抗導電性材料で形成したTFTにおいて、駆動回路部のpチャネル型TFT、nチャネル型TFTおよび画素TFTをゲート電極と重なるLDD構造としたアクティブマトリクス基板を6枚のフォトマスクで製造することができ、このようなアクティブマトリクス基板から反射型の液晶表示装置を作製することができる。また、同工程に従えば、透過型の液晶表示装置を7枚のフォトマスクで製造することができる。

【図面の簡単な説明】

【図1】 本発明のTFTの作製方法を説明する図。

【図2】 図1に対応したLDD領域の不純物元素の濃度分布を説明する図。

【図3】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図4】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図5】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図6】 画素TFT、駆動回路のTFTの作製工程を示す断面図。

【図7】 駆動回路のTFTと画素TFTの構造を示す上面図。