JP4635470B2 - 炭化珪素半導体装置およびその製造方法 - Google Patents

炭化珪素半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4635470B2 JP4635470B2 JP2004122796A JP2004122796A JP4635470B2 JP 4635470 B2 JP4635470 B2 JP 4635470B2 JP 2004122796 A JP2004122796 A JP 2004122796A JP 2004122796 A JP2004122796 A JP 2004122796A JP 4635470 B2 JP4635470 B2 JP 4635470B2

- Authority

- JP

- Japan

- Prior art keywords

- silicon carbide

- semiconductor substrate

- forming

- conductivity type

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/63—Vertical IGFETs

- H10D30/635—Vertical IGFETs having no inversion channels, e.g. vertical accumulation channel FETs [ACCUFET] or normally-on vertical IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/681—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered

- H10D64/685—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator having a compositional variation, e.g. multilayered being perpendicular to the channel plane

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/691—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator comprising metallic compounds, e.g. metal oxides or metal silicates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P90/00—Preparation of wafers not covered by a single main group of this subclass, e.g. wafer reinforcement

- H10P90/12—Preparing bulk and homogeneous wafers

- H10P90/129—Preparing bulk and homogeneous wafers by polishing

Landscapes

- Electrodes Of Semiconductors (AREA)

Description

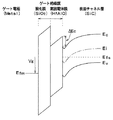

したがって、このように結晶欠陥が少なくできる(0001)Si面に対して10〜20°傾いた面を用いることにより、他の面と比べて界面準位を低減することができ、より界面準位による電流の流れの影響を低減することが可能となる。これにより、パワーMOSFETの更なるチャネル移動度の向上を図ることが可能となる。

また、チャネル層の表面に高誘電体膜を形成することで、界面準位がコンダクションバンド近辺に高密度に集中しないようにすることが可能となる。したがって、界面準位が電流の流れに影響を及ぼすことによってチャネル移動度を低下させるという問題を解消でき、チャネル移動度を向上させることが可能となる。

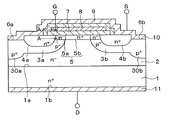

図1に、本実施の形態におけるノーマリオフ型のnチャネルタイププレーナ型MOSFET(縦型パワーMOSFET)の断面図を示す。本デバイスは、インバータや車両用オルタネータのレクチファイヤに適用すると好適である。以下、図1に基づいてプレーナ型MOSFETの構造について説明する。

まず、n型4Hまたは6Hまたは3C−SiC基板、すなわちn+型半導体基板1を用意する。例えば、n+型半導体基板1として、その厚さが400μm、主表面1aが(0001)Si面、又は、(112−0)a面のものを用いる。この基板1の主表面1aに厚さ5μmのn-型エピ層2をエピタキシャル成長させる。これにより、n-型エピ層2は下地の基板1と同様の結晶が得られ、n型4Hまたは6Hまたは3C−SiC層となる。

n-型エピ層2の上の所定領域にLTO膜20を配置し、これをマスクとしてB+(若しくはアルミニウム)をイオン注入して、p-型ベース領域3a、3bを形成する。このとき、イオン注入条件は、温度が700℃で、ドーズ量が1×1016cm-2としている。

LTO膜20を除去した後、基板1の上面からN+をイオン注入して、n-型エピ層2の表層部及びp-型ベース領域3a、3bの表面部(表層部)に表面チャネル層5を形成する。このとき、イオン注入条件は、温度が700℃、ドーズ量が1×1016cm-2としている。これにより、表面チャネル層5は、p-型ベース領域3a、3bの表面部では補償されてn型の不純物濃度が薄いn-型層5aとなり、n-型エピ層2の表面部ではn型の不純物濃度が濃いn+型層5bとなる。

表面チャネル層5の上の所定領域にLTO膜21を配置し、これをマスクとしてN+をイオン注入し、n+型ソース領域4a、4bを形成する。このときのイオン注入条件は、700℃、ドーズ量は1×1015cm-2としている。

そして、LTO膜21を除去した後、フォトレジスト法を用いて表面チャネル層5の上の所定領域にLTO膜22を配置し、これをマスクとしてRIEによりp-型炭化珪素ベース領域3a、3b上の表面チャネル層5を部分的にエッチング除去する。

さらに、LTO膜22をマスクにしてB+をイオン注入し、ディープベース層30a、30bを形成する。これにより、ベース領域3a、3bの一部が厚くなったものとなる。このディープベース層30a、30bは、n+型ソース領域4a、4bに重ならない部分に形成されると共に、p-型ベース領域3a、3bのうちディープベース層30a、30bが形成された厚みが厚くなった部分が、ディープベース層30aが形成されていない厚みの薄い部分よりも不純物濃度が濃く形成される。

LTO膜22を除去した後、基板上にゲート絶縁膜7として高誘電体膜であるHfO2を形成する。このとき、例えば、基板温度500℃としてスパッタ法により、HfO2を形成する。そして、スパッタ後に、O2雰囲気で適宜熱処理を行う。

引き続き、ゲート絶縁膜7の不要部分を除去した後、LTOよりなる絶縁膜9を形成しゲート絶縁膜7を覆う。このとき、成膜温度を425℃として、成膜後に1000℃のアニールを行う。

そして、室温での金属スパッタリングによりソース電極10及びドレイン電極11を配置する。また、成膜後に1000℃のアニールを行う。このようにして、図1に示す縦型パワーMOSFETが完成する。

上記第1実施形態では、ゲート絶縁膜7の材質となる高誘電体膜としてHfO2を用いているが、この他の高誘電体膜を用いることも可能である。例えば、HfAlOXを高誘電体膜として用いることも可能である。この場合、第1実施形態で示した図4(a)に示す工程において、例えばMO−CVD法によってHfAlOXを形成する。例えば、500℃のO2雰囲気中でHfAlOXの成膜を行い、成膜後に700℃の熱処理を行うことで、ゲート絶縁膜7を形成することができる。その他にもHfSiONを高誘電体膜として用いることも可能である。例えば反応性スパッタ法にて形成する。その後、N2雰囲気中で950℃〜1100℃の熱処理を行うことでゲート絶縁膜7を形成することができる。

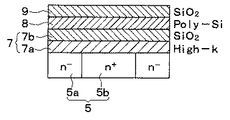

本発明の第2実施形態について説明する。本実施形態は、第1実施形態に対してゲート絶縁膜7の構造を変更したものであり、他の部分については同様であるため、異なる部分についてのみ説明する。

500℃のO2雰囲気中においてHfAlOXからなる高誘電体膜7aをMO−CVD法によって形成したのち、700℃の熱処理を行い、さらに、高誘電体膜7aの表面にCVD法により酸化膜7bを成膜することにより、ゲート絶縁膜7を形成することができる。その他にもHfSiONを高誘電体膜として用いることも可能で、例えば反応性スパッタ法にて形成する。その後、N2雰囲気中で950℃〜1100℃の熱処理を行うことでゲート絶縁膜7を形成することができる。

本発明の第3実施形態について説明する。本実施形態は、第1、第2実施形態に対してn-型半導体基板1の面方位を変更したものであり、他の部分については同様であるため、異なる部分についてのみ説明する。

本発明の第4実施形態について説明する。本実施形態は、第3実施形態と同様に、第1、第2実施形態に対してn-型半導体基板1の面方位を変更したものであり、他の部分については同様であるため、異なる部分についてのみ説明する。

上記実施形態では、n-型炭化珪素エピ層2の表層部及びp-型炭化珪素ベース領域3a、3bの表面部(表層部)に直接イオン注入を行うことにより表面チャネル層5を形成しているが、これらの上にn-型の表面チャネル層5をエピタキシャル成長させるようにしたパワーMOSFETに対しても、本発明を適用することが可能である。

Claims (10)

- 主表面および主表面の反対面である裏面を有し、前記主表面が(0001)Si面に対して10〜20°傾いた単結晶炭化珪素基板からなる半導体基板(1)と、

前記半導体基板の主表面上に形成され、前記半導体基板よりも低いドーパント濃度を有する第1導電型の炭化珪素からなるエピタキシャル層(2)と、

前記エピタキシャル層上の所定領域に形成され、所定厚さを有する第2導電型のベース領域(3a、3b)と、

前記ベース領域上の所定の表面部に形成され、ベース領域の深さよりも浅い第1導電型のソース領域(4a、4b)と、

前記エピタキシャル層および前記ベース領域の表面部に形成され、前記ソース領域と前記エピタキシャル層とを繋ぐように形成された所定厚さと所定濃度を有する第1導電型の炭化珪素からなる表面チャネル層(5)と、

前記表面チャネル層の表面に形成された高誘電体膜(7a)を含むゲート絶縁膜(7)と、

前記ゲート絶縁膜の上に形成されたゲート電極(8)と、

前記ソース領域上に形成されたソース電極(10)と、

前記半導体基板の裏面に形成された裏面電極(11)とを備えたことを特徴とする炭化珪素半導体装置。 - 主表面および主表面の反対面である裏面を有し、前記主表面が(0001)Si面と、(0001)Si面に対して10〜20°傾いた面との、少なくとも2面を含むステップバンチングが形成された単結晶炭化珪素基板からなる半導体基板(1)と、

前記半導体基板の主表面上に形成され、前記半導体基板よりも低いドーパント濃度を有する第1導電型の炭化珪素からなるエピタキシャル層(2)と、

前記エピタキシャル層上の所定領域に形成され、所定厚さを有する第2導電型のベース領域(3a、3b)と、

前記ベース領域上の所定の表面部に形成され、ベース領域の深さよりも浅い第1導電型のソース領域(4a、4b)と、

前記エピタキシャル層および前記ベース領域の表面部に形成され、前記ソース領域と前記エピタキシャル層とを繋ぐように形成された所定厚さと所定濃度を有する第1導電型の炭化珪素からなる表面チャネル層(5)と、

前記表面チャネル層の表面に形成された高誘電体膜(7a)を含むゲート絶縁膜(7)と、

前記ゲート絶縁膜の上に形成されたゲート電極(8)と、

前記ソース領域上に形成されたソース電極(10)と、

前記半導体基板の裏面に形成された裏面電極(11)とを備えたことを特徴とする炭化珪素半導体装置。 - 前記半導体基板は、前記(0001)Si面の面積と比べて、前記(0001)Si面に対して10〜20°傾いた面の面積の方が大きくなっていることを特徴とする請求項2に記載の炭化珪素半導体装置。

- 前記半導体基板における前記(0001)Si面に対して10〜20°傾いた面は、<11−20>方向に傾いてることを特徴とする請求項3に記載の炭化珪素半導体装置。

- 前記ゲート絶縁膜は、前記高誘電体膜とこの高誘電体膜の表面に形成された酸化膜(7b)の積層構造であることを特徴とする請求項1ないし4のいずれか1つに記載の炭化珪素半導体装置。

- 主表面および主表面の反対面である裏面を有し、単結晶炭化珪素からなる半導体基板(1)を用意し、この半導体基板の主表面上に、前記半導体基板よりも低いドーパント濃度を有する第1導電型の炭化珪素からなるエピタキシャル層(2)を形成する工程と、

前記エピタキシャル層上の所定領域に、所定厚さを有する第2導電型のベース領域(3a、3b)を形成する工程と、

前記ベース領域上の所定の表面部に、ベース領域の深さよりも浅い第1導電型のソース領域(4a、4b)を形成する工程と、

前記エピタキシャル層および前記ベース領域の表面部に、前記ソース領域と前記エピタキシャル層とを繋ぐように所定厚さと所定濃度を有する第1導電型の炭化珪素からなる表面チャネル層(5)を形成する工程と、

前記表面チャネル層の表面に高誘電体膜(7a)を形成することで、この高誘電体膜を含むゲート絶縁膜(7)を形成する工程と、

前記ゲート絶縁膜の上にゲート電極(8)を形成する工程と、

前記ソース領域上にソース電極(10)を形成する工程と、

前記半導体基板の裏面に裏面電極(11)を形成する工程とを有し、

前記半導体基板を用意する工程では、(0001)Si面を端面とした炭化珪素インゴットを(0001)Si面に対して10〜20°傾いた面で切り出すことにより、前記半導体基板として、前記主表面が(0001)Si面に対して10〜20°を成している単結晶炭化珪素基板を形成することを特徴とする炭化珪素半導体装置の製造方法。 - 主表面および主表面の反対面である裏面を有し、単結晶炭化珪素からなる半導体基板(1)を用意し、この半導体基板の主表面上に、前記半導体基板よりも低いドーパント濃度を有する第1導電型の炭化珪素からなるエピタキシャル層(2)を形成する工程と、

前記エピタキシャル層上の所定領域に、所定厚さを有する第2導電型のベース領域(3a、3b)を形成する工程と、

前記ベース領域上の所定の表面部に、ベース領域の深さよりも浅い第1導電型のソース領域(4a、4b)を形成する工程と、

前記エピタキシャル層および前記ベース領域の表面部に、前記ソース領域と前記エピタキシャル層とを繋ぐように所定厚さと所定濃度を有する第1導電型の炭化珪素からなる表面チャネル層(5)を形成する工程と、

前記表面チャネル層の表面に高誘電体膜(7a)を形成することで、この高誘電体膜を含むゲート絶縁膜(7)を形成する工程と、

前記ゲート絶縁膜の上にゲート電極(8)を形成する工程と、

前記ソース領域上にソース電極(10)を形成する工程と、

前記半導体基板の裏面に裏面電極(11)を形成する工程とを有し、

前記半導体基板を用意する工程では、前記半導体基板として、前記主表面が(0001)Si面と、(0001)Si面に対して10〜20°傾いた面との、少なくとも2面を含むステップバンチングが形成された単結晶炭化珪素基板を形成することを特徴とする炭化珪素半導体装置の製造方法。 - 前記半導体基板を用意する工程では、前記(0001)Si面の面積と比べて、前記(0001)Si面に対して10〜20°傾いた面の面積の方が大きくなるように前記単結晶炭化珪素基板を形成することを特徴とする請求項7に記載の炭化珪素半導体装置の製造方法。

- 前記半導体基板を用意する工程では、前記半導体基板における前記(0001)Si面に対して10〜20°傾いた面を<11−20>方向に傾けように前記単結晶炭化珪素基板を形成することを特徴とする請求項8に記載の炭化珪素半導体装置の製造方法。

- 前記ゲート絶縁膜を形成する工程では、前記高誘電体膜の表面に酸化膜(7b)を形成することで、前記ゲート絶縁膜を積層構造とすることを特徴とする請求項6ないし9のいずれか1つに記載の炭化珪素半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004122796A JP4635470B2 (ja) | 2004-04-19 | 2004-04-19 | 炭化珪素半導体装置およびその製造方法 |

| DE102005017814.6A DE102005017814B4 (de) | 2004-04-19 | 2005-04-18 | Siliziumkarbid-Halbleiterbauelement und Verfahren zu dessen Herstellung |

| US11/108,906 US7365363B2 (en) | 2004-04-19 | 2005-04-19 | Silicon carbide semiconductor device and method for manufacturing the same |

| SE0500865A SE527922C2 (sv) | 2004-04-19 | 2005-04-19 | Halvledaranordning av kiselkarbid |

| US11/882,137 US7968892B2 (en) | 2004-04-19 | 2007-07-31 | Silicon carbide semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004122796A JP4635470B2 (ja) | 2004-04-19 | 2004-04-19 | 炭化珪素半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005310886A JP2005310886A (ja) | 2005-11-04 |

| JP4635470B2 true JP4635470B2 (ja) | 2011-02-23 |

Family

ID=35439330

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004122796A Expired - Fee Related JP4635470B2 (ja) | 2004-04-19 | 2004-04-19 | 炭化珪素半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635470B2 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007012684A (ja) * | 2005-06-28 | 2007-01-18 | Mitsubishi Electric Corp | 半導体装置とゲート酸化膜の製造方法 |

| EP2264223A3 (en) * | 2006-09-14 | 2011-10-26 | Cree, Inc. | Micropipe-free silicon carbide and related method of manufacture |

| JP5071763B2 (ja) | 2006-10-16 | 2012-11-14 | 独立行政法人産業技術総合研究所 | 炭化ケイ素半導体装置およびその製造方法 |

| JP5036399B2 (ja) * | 2007-05-22 | 2012-09-26 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| JP2008294171A (ja) * | 2007-05-24 | 2008-12-04 | Oki Electric Ind Co Ltd | 半導体デバイス及びその製造方法 |

| JP2009182271A (ja) | 2008-01-31 | 2009-08-13 | Toshiba Corp | 炭化珪素半導体装置 |

| JP5646139B2 (ja) * | 2008-09-26 | 2014-12-24 | 株式会社東芝 | 半導体装置 |

| US8410489B2 (en) | 2009-04-30 | 2013-04-02 | Panasonic Corporation | Semiconductor element, semiconductor device, and power converter |

| JP4955128B2 (ja) | 2009-08-19 | 2012-06-20 | パナソニック株式会社 | 半導体素子、半導体装置および電力変換器 |

| JP5616665B2 (ja) | 2010-03-30 | 2014-10-29 | ローム株式会社 | 半導体装置 |

| JP6168945B2 (ja) * | 2013-09-20 | 2017-07-26 | 株式会社東芝 | 半導体装置およびその製造方法 |

| JP2015069989A (ja) * | 2013-09-26 | 2015-04-13 | 三菱電機株式会社 | 炭化珪素半導体装置の製造方法 |

| JP6526549B2 (ja) * | 2015-03-24 | 2019-06-05 | 株式会社東芝 | 半導体装置、インバータ回路、駆動装置、車両、及び、昇降機 |

| EP3176812A1 (en) * | 2015-12-02 | 2017-06-07 | ABB Schweiz AG | Semiconductor device and method for manufacturing such a semiconductor device |

| CN109585541B (zh) * | 2018-12-27 | 2024-03-26 | 西安中车永电电气有限公司 | 一种埋沟式SiC IGBT常关器件及其制备方法 |

| US12396219B2 (en) | 2020-01-16 | 2025-08-19 | Lg Electronics Inc. | Metal-oxide film semiconductor field-effect transistor device and method for manufacturing same |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE9404452D0 (sv) * | 1994-12-22 | 1994-12-22 | Abb Research Ltd | Semiconductor device having an insulated gate |

| JP2000106428A (ja) * | 1998-09-28 | 2000-04-11 | Toshiba Corp | 半導体装置 |

| JP3148982B2 (ja) * | 1998-11-11 | 2001-03-26 | 工業技術院長 | 半導体装置及びその製造方法 |

| JP4450123B2 (ja) * | 1999-11-17 | 2010-04-14 | 株式会社デンソー | 炭化珪素半導体装置 |

| JP3812396B2 (ja) * | 2001-10-04 | 2006-08-23 | 株式会社デンソー | 炭化珪素半導体装置の製造方法及び炭化硅素半導体装置 |

| JP2003234301A (ja) * | 2001-10-25 | 2003-08-22 | Matsushita Electric Ind Co Ltd | 半導体基板、半導体素子及びその製造方法 |

| JP3707424B2 (ja) * | 2001-11-22 | 2005-10-19 | 株式会社デンソー | 炭化珪素半導体装置及びその製造方法 |

| JP3697211B2 (ja) * | 2002-01-10 | 2005-09-21 | 日本原子力研究所 | 炭化珪素半導体素子及びその絶縁膜の形成方法 |

| TWI313060B (en) * | 2003-07-28 | 2009-08-01 | Japan Science & Tech Agency | Feild effect transisitor and fabricating method thereof |

-

2004

- 2004-04-19 JP JP2004122796A patent/JP4635470B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005310886A (ja) | 2005-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3893725B2 (ja) | 炭化珪素半導体装置の製造方法 | |

| JP4123636B2 (ja) | 炭化珪素半導体装置及びその製造方法 | |

| JP5586887B2 (ja) | 半導体装置及びその製造方法 | |

| JP4192353B2 (ja) | 炭化珪素半導体装置及びその製造方法 | |

| JP3385938B2 (ja) | 炭化珪素半導体装置及びその製造方法 | |

| JP6572423B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| US8658503B2 (en) | Semiconductor device and method of fabricating the same | |

| JP4635470B2 (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP5693851B2 (ja) | 半導体装置 | |

| JP5182359B2 (ja) | 炭化珪素半導体装置 | |

| JP3428459B2 (ja) | 炭化けい素nチャネルMOS半導体素子およびその製造方法 | |

| JP4595144B2 (ja) | 炭化珪素半導体装置及びその製造方法 | |

| US20090134402A1 (en) | Silicon carbide mos field-effect transistor and process for producing the same | |

| JPH11261061A (ja) | 炭化珪素半導体装置及びその製造方法 | |

| US20120193643A1 (en) | Semiconductor device | |

| CN108604600B (zh) | 碳化硅半导体装置及其制造方法 | |

| US11605732B2 (en) | Power device with graded channel | |

| JP2006066439A (ja) | 半導体装置およびその製造方法 | |

| JP6991476B2 (ja) | 半導体装置 | |

| US20130134442A1 (en) | Semiconductor device and method for manufacturing same | |

| JP4806852B2 (ja) | 炭化珪素半導体装置及びその製造方法 | |

| JP2003309262A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP4620368B2 (ja) | 半導体装置の製造方法 | |

| JP2010027833A (ja) | 炭化珪素半導体装置およびその製造方法 | |

| JP3496509B2 (ja) | 炭化珪素半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060531 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081017 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100624 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100720 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100909 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4635470 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |