JP4635430B2 - 積層コイル部品 - Google Patents

積層コイル部品 Download PDFInfo

- Publication number

- JP4635430B2 JP4635430B2 JP2003393565A JP2003393565A JP4635430B2 JP 4635430 B2 JP4635430 B2 JP 4635430B2 JP 2003393565 A JP2003393565 A JP 2003393565A JP 2003393565 A JP2003393565 A JP 2003393565A JP 4635430 B2 JP4635430 B2 JP 4635430B2

- Authority

- JP

- Japan

- Prior art keywords

- strip

- conductor

- ceramic

- conductors

- shaped

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Coils Or Transformers For Communication (AREA)

Description

このように、従来はインダクタンスを大きくして小型化を図るため、帯状導体のズレを少なくして積層している。しかし、帯状導体の重なり面積が大きくなり、コイルの浮遊容量が増加し、自己共振周波数(SRF)が低下して高周波帯でのインピーダンスが低下してしまう。

て、前記帯状導体の各々は、b=a−cの関係を満たす形状にされていることを特徴とする。

なお、この場合において、b=a−cの関係を満たし、各帯状導体の幅cが等しく、前記帯状導体の第1辺と第3辺の先端及び該辺の外縁から焼結体の接近した辺までの距離がほぼ等しく形成されていることがより好ましい。

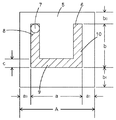

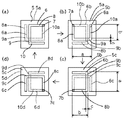

図2に示す帯状導体6の第2辺の長さをa、第1辺と第3辺の長さをb、第2辺の幅をcとしている。さらに、第1辺と第3辺の先端から接近した辺までの距離をb0とし、第1辺と第3辺の外縁から接近した辺までの距離をそれぞれa0 、a1とし、第2辺の外縁から接近した辺までの距離をそれぞれb1としている。そして、b≦a−c、a0=a1=b0、c+b0≦b1としている。

ここにおいて、b=a−c、a0=a1=b0、c+b0≦b1 とすることによって、隣接する帯状導体の重なりが小さくなって浮遊容量が低下し、SRFが高い積層コイル部品を得ることができる。

このように帯状導体が配置されたセラミックシートを積層することによってコイルを形成することで、コイルの内径を大きくとることができて、高いインダクタンスを得ることができる。

先ず、フェライト材料等の粉体材料を所要の組成になるように秤量し、所要の粒度に粉砕して乾燥する。得られた原料に溶媒、バインダー、分散剤を加えて混合後、ドクターブレード法、リバースロールコータ法等の成型方法により、所要の厚さのセラミックグリーンシートを作製する。バインダとしては、水系バインダ(酢酸ビニルや水溶性アクリル等)または有機系バインダ(ポリビニルブチラール等)等が使用される。また、消泡剤等を添加してもよい。

同士を導通させた状態でセラミックグリーンシートを積層する。そして、このようにして積層を繰り返して、所要のターン数の帯状導体のコイルを形成する。

その後、積層されたセラミックグリーンシートを圧着する。この圧着の加圧力は、98〜120MPa程度である。

次いで、チップのコイル巻軸方向のチップ端部に接続電極と接続される外部電極のNi下地を塗布した後焼成し、さらに電気めっき(Niめっき,Snめっき)して外部電極を形成して積層コイル部品を得る。

透磁率400のNiZnCuフェライト原料を得るため、所定量の酸化物原料を混合して800℃で、1時間仮焼した。それから、ボールミルで粉砕して乾燥し、平均粒径約2μmの粉末とした。得られたフェライト粉末原料に溶媒、バインダー、分散剤を加えて混合した後、ドクターブレード法により厚さ30μmのセラミックグリーンシートを作製した。

図4から明らかなように、本発明の積層チップインダクタによれば、従来品では自己共振周波数が600〜700MHzの間にあったものを、800〜900MHzの間まで高めることができた。また、本発明の積層チップインダクタは、750MHzより高い周波数の領域で、従来品より大きいインピーダンスが得られる。よって、本発明によれば、750MHz以上のノイズを減衰させるのに従来品より有利である。

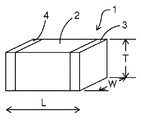

2 セラミック焼結体

3,4 外部電極

5 セラミック層(セラミック(グリーン)シート)

6 帯状導体

7 バイアホール

Claims (3)

- セラミック焼結体と、該セラミック焼結体を形成するセラミック層を介して配設される複数の帯状導体を、前記セラミック層に設けられたバイアホールによって直列に接続してなるコイルとを有する積層コイル部品であって、

前記帯状導体の各々は、同一構成を有し、しかも、それぞれ略直角のU字状に形成された3辺からなって3/4ターンしており、第2辺の長さをa、第1辺と第3辺の長さをb、第2辺の幅をcとして、3辺の前記帯状導体の幅が略一定で、かつ、b≦a−cの関係を満たす形状にされていることを特徴とする積層コイル部品。 - 前記帯状導体の各々は、b=a−cの関係を満たす形状にされていることを特徴とする請求項1に記載の積層コイル部品。

- 前記帯状導体の第1辺と第3辺の先端及び該辺の外縁から焼結体の接近した辺までの距離が等しく形成されていることを特徴とする請求項1又は2に記載の積層コイル部品。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003393565A JP4635430B2 (ja) | 2003-11-25 | 2003-11-25 | 積層コイル部品 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003393565A JP4635430B2 (ja) | 2003-11-25 | 2003-11-25 | 積層コイル部品 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005158920A JP2005158920A (ja) | 2005-06-16 |

| JP4635430B2 true JP4635430B2 (ja) | 2011-02-23 |

Family

ID=34719886

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003393565A Expired - Fee Related JP4635430B2 (ja) | 2003-11-25 | 2003-11-25 | 積層コイル部品 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4635430B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4683071B2 (ja) * | 2008-05-16 | 2011-05-11 | Tdk株式会社 | コモンモードフィルタ |

| KR101983139B1 (ko) * | 2013-03-14 | 2019-05-28 | 삼성전기주식회사 | 적층형 인덕터 및 적층형 인덕터 어레이 |

| JP7107250B2 (ja) * | 2019-03-04 | 2022-07-27 | 株式会社村田製作所 | 積層型コイル部品 |

| JP7751472B2 (ja) * | 2021-12-08 | 2025-10-08 | 株式会社村田製作所 | 積層型コイル部品 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0613239A (ja) * | 1992-06-25 | 1994-01-21 | Matsushita Electric Works Ltd | 平面形トランス |

| JPH0634216U (ja) * | 1992-10-02 | 1994-05-06 | 太陽誘電株式会社 | 積層チップインダクタ |

| JPH08130117A (ja) * | 1994-10-31 | 1996-05-21 | Kyocera Corp | 積層インダクタ |

| JPH09180939A (ja) * | 1995-12-22 | 1997-07-11 | Murata Mfg Co Ltd | 積層型コイル部品 |

| JP2002015918A (ja) * | 2000-06-28 | 2002-01-18 | Tdk Corp | 積層型電子部品 |

| JP2002043128A (ja) * | 2000-07-21 | 2002-02-08 | Alps Electric Co Ltd | スパイラルインダクタンス装置 |

| JP2002110424A (ja) * | 2000-09-29 | 2002-04-12 | Toko Inc | 積層チップ部品 |

-

2003

- 2003-11-25 JP JP2003393565A patent/JP4635430B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005158920A (ja) | 2005-06-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN102683015B (zh) | 多层陶瓷电容器及其制造方法 | |

| US8159322B2 (en) | Laminated coil | |

| JP6834091B2 (ja) | 積層セラミック電子部品及びその製造方法 | |

| JP5653886B2 (ja) | 積層セラミックキャパシタ及びその製造方法 | |

| US20180211786A1 (en) | Multilayer ceramic capacitor and method of manufacturing the same | |

| JP4246716B2 (ja) | 積層型フィルタ | |

| JP2013084871A (ja) | 積層セラミック電子部品及びその製造方法 | |

| KR100370670B1 (ko) | 인덕터 소자 및 그 제조방법 | |

| JP2004128506A (ja) | 積層型コイル部品及びその製造方法 | |

| US20120062348A1 (en) | Laminated coil | |

| JP3201309B2 (ja) | 積層型コイル及びその製造方法 | |

| JPH0855726A (ja) | 積層型電子部品及びその製造方法 | |

| JPH0258813A (ja) | 積層型インダクタ | |

| JP6784183B2 (ja) | 積層コイル部品 | |

| CN107045936A (zh) | 层叠陶瓷电容器 | |

| JPH11265823A (ja) | 積層型インダクタ及びその製造方法 | |

| JP2002093623A (ja) | 積層インダクタ | |

| JPH11273950A (ja) | 積層チップコイル部品 | |

| JPH0669057A (ja) | 積層チップインダクタの製造方法 | |

| JP4635430B2 (ja) | 積層コイル部品 | |

| US6466120B1 (en) | Laminated inductor and method of producing the same | |

| US6551426B2 (en) | Manufacturing method for a laminated ceramic electronic component | |

| JP4400430B2 (ja) | 積層型インダクタ | |

| JP2006351954A (ja) | 積層型コモンモードフィルタ | |

| US20140373341A1 (en) | Method for manufacturing laminated coil components |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060927 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090414 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090715 |

|

| A072 | Dismissal of procedure [no reply to invitation to correct request for examination] |

Free format text: JAPANESE INTERMEDIATE CODE: A072 Effective date: 20091215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100427 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100602 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101026 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101108 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131203 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4635430 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |