JP4609478B2 - 蓋体フレーム及びその製造方法 - Google Patents

蓋体フレーム及びその製造方法 Download PDFInfo

- Publication number

- JP4609478B2 JP4609478B2 JP2007268017A JP2007268017A JP4609478B2 JP 4609478 B2 JP4609478 B2 JP 4609478B2 JP 2007268017 A JP2007268017 A JP 2007268017A JP 2007268017 A JP2007268017 A JP 2007268017A JP 4609478 B2 JP4609478 B2 JP 4609478B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit board

- lid

- lid frame

- cavity

- semiconductor chip

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1517—Multilayer substrate

- H01L2924/15172—Fan-out arrangement of the internal vias

- H01L2924/15174—Fan-out arrangement of the internal vias in different layers of the multilayer substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Description

この発明は、音圧センサチップや圧力センサチップ等の半導体チップを備える半導体装置に使用する蓋体フレーム及びその製造方法に関する。

シリコンマイクや圧力センサ等の半導体装置では、音圧センサチップや圧力センサチップ等の半導体チップを回路基板に実装している。この種の半導体装置では、半導体チップを外部空間と連通させる必要がある。従来の半導体装置では、回路基板及び封止樹脂パッケージに形成された貫通孔を通じて、半導体チップを外部空間に連通させている(例えば、特許文献1参照。)。なお、封止樹脂パッケージに形成される貫通孔は、例えば、回路基板の貫通孔に連結された筒状のパイプにより構成されている。

ところで、この種の半導体装置の封止樹脂パッケージは、これを形成するためのキャビティを有する金型に、半導体チップやパイプを取り付けた回路基板を収容し、このキャビティに溶融した樹脂を流し込むことにより形成される。

したがって、封止樹脂パッケージを形成する溶融樹脂の流れによって回路基板に対するパイプの位置がずれることを防ぐと共に、パイプと回路基板との隙間に溶融樹脂が流入することを防ぐ必要がある。このため、従来では、封止樹脂パッケージを形成する前に、予めパイプを回路基板に固定している。このパイプの固定は、例えば、パイプを回路基板の貫通孔にかしめる、溶接する、半田付けをする、接着剤にて接着する等の方法により行われる。

特開平9−119875号公報

したがって、封止樹脂パッケージを形成する溶融樹脂の流れによって回路基板に対するパイプの位置がずれることを防ぐと共に、パイプと回路基板との隙間に溶融樹脂が流入することを防ぐ必要がある。このため、従来では、封止樹脂パッケージを形成する前に、予めパイプを回路基板に固定している。このパイプの固定は、例えば、パイプを回路基板の貫通孔にかしめる、溶接する、半田付けをする、接着剤にて接着する等の方法により行われる。

しかしながら、上記従来の半導体装置を製造する際には、回路基板に貫通孔を形成する工程やパイプを回路基板に固定する工程が必要となるため、半導体装置の製造コストが増加すると共に、半導体装置の製造効率が低下する虞がある。

この発明は、上述した事情に鑑みてなされたものであって、製造コストの削減、及び、製造効率の向上を図ることができる半導体装置に使用する蓋体フレーム及びその製造方法を提供することを目的としている。

この発明は、上述した事情に鑑みてなされたものであって、製造コストの削減、及び、製造効率の向上を図ることができる半導体装置に使用する蓋体フレーム及びその製造方法を提供することを目的としている。

上記課題を解決するために、この発明は以下の手段を提案している。

請求項1に係る発明は、回路基板にその厚さ方向の一端側に重ねて固定されると共に電気的に接続された半導体チップを、中空の空洞部を介して樹脂により覆う構成の半導体装置に使用する蓋体フレームであって、前記半導体チップを覆うように前記回路基板の一端側に設けて前記空洞部を形成する蓋体部と、該蓋体部から前記空洞部の外方側に突出すると共に前記空洞部を外方に開口させる筒状の突出部とを備え、前記突出部が、前記蓋体部の上端部からさらに前記厚さ方向に延びており、前記空洞部に対向する前記蓋体部の内面に、導電性のシールド部が形成されていることを特徴とする蓋体フレームを提案している。

請求項1に係る発明は、回路基板にその厚さ方向の一端側に重ねて固定されると共に電気的に接続された半導体チップを、中空の空洞部を介して樹脂により覆う構成の半導体装置に使用する蓋体フレームであって、前記半導体チップを覆うように前記回路基板の一端側に設けて前記空洞部を形成する蓋体部と、該蓋体部から前記空洞部の外方側に突出すると共に前記空洞部を外方に開口させる筒状の突出部とを備え、前記突出部が、前記蓋体部の上端部からさらに前記厚さ方向に延びており、前記空洞部に対向する前記蓋体部の内面に、導電性のシールド部が形成されていることを特徴とする蓋体フレームを提案している。

この発明に係る蓋体フレームを用いて半導体装置を製造する際には、回路基板に固定された半導体チップを蓋体部により覆うように蓋体フレームを回路基板に重ねて配し、その後に、蓋体部を覆う樹脂モールド部を形成する。この際には、はじめに、樹脂モールド部形成用の一対の金型により回路基板及び蓋体フレームを回路基板の厚さ方向から挟み込む。ここで、筒状に形成された蓋体フレームの突出部は、蓋体部の上端部から回路基板に対してさらに離間する方向に延びているため、一方の金型が突出部の開口端に当接し、一方の金型と蓋体部の上端部との間には隙間が形成される。

また、一対の金型により挟み込むため、突出部が回路基板に向けて押圧されることになる。そして、この突出部の押圧により、回路基板に接する蓋体部の下端部が回路基板に押し付けられるため、蓋体部の下端部と回路基板との隙間を塞ぐことができる。さらに、突出部の開口端も一方の金型に当接するため、突出部の開口端を一方の金型により塞ぐこともできる。以上のことから、空洞部が外方に対して密閉されることになる。

また、一対の金型により挟み込むため、突出部が回路基板に向けて押圧されることになる。そして、この突出部の押圧により、回路基板に接する蓋体部の下端部が回路基板に押し付けられるため、蓋体部の下端部と回路基板との隙間を塞ぐことができる。さらに、突出部の開口端も一方の金型に当接するため、突出部の開口端を一方の金型により塞ぐこともできる。以上のことから、空洞部が外方に対して密閉されることになる。

この一対の金型による挟み込みの後に、一方の金型、蓋体部、突出部及び回路基板により画定される樹脂形成空間に溶融樹脂を注入し、蓋体フレーム及び回路基板を一体的に固定する樹脂モールド部を形成する。この際、蓋体部の下端部と回路基板との隙間、及び、一方の金型と突出部の開口端との隙間は、一方の金型による突出部の押圧により塞がれているため、樹脂形成空間に注入された溶融樹脂が空洞部に流入することを防止できる。

また、一対の金型で蓋体フレームを回路基板に押さえつけることにより、蓋体フレームと回路基板との相対的な位置を固定できる。したがって、樹脂モールド部を形成する際に、樹脂形成空間に注入された溶融樹脂によって蓋体フレームが回路基板に対して動くことを防止できる。

また、一対の金型で蓋体フレームを回路基板に押さえつけることにより、蓋体フレームと回路基板との相対的な位置を固定できる。したがって、樹脂モールド部を形成する際に、樹脂形成空間に注入された溶融樹脂によって蓋体フレームが回路基板に対して動くことを防止できる。

さらに、内面に導電性を有するシールド部を形成した蓋体部により半導体チップを覆うことにより、半導体装置の外方側において発生した電気的なノイズが樹脂モールド部側から侵入しても、蓋体部においてノイズが空洞部内に侵入することを防止して半導体チップに到達することを防止できる。

請求項2に係る発明は、請求項1に記載の蓋体フレームにおいて、前記シールド部が、前記突出部の内面にも形成されていることを特徴とする蓋体フレームを提案している。

請求項3に係る発明は、請求項1又は請求項2に記載の蓋体フレームにおいて、熱硬化性樹脂によって形成され耐熱性を有することを特徴とする蓋体フレームを提案している。

請求項4に係る発明は、請求項1から請求項3のいずれか1項に記載の蓋体フレームにおいて、前記シールド部が、導電性材料からなることを特徴とする蓋体フレームを提案している。

請求項5に係る発明は、回路基板にその厚さ方向の一端側に重ねて固定されると共に電気的に接続された半導体チップを、中空の空洞部を介して樹脂により覆う構成の半導体装置に使用する蓋体フレームを製造する蓋体フレームの製造方法であって、耐熱性を有する熱硬化性樹脂を用いてインジェクション成形法により、前記回路基板と共に前記空洞部を形成する蓋体部と、前記蓋体部の上端部からさらに前記厚さ方向に延びるように突出すると共に前記空洞部を外方に開口させる筒状の突出部とを一体に形成し、前記空洞部に対向する前記蓋体部の内面に、導電性を有する導電性材料を塗布若しくは吹付して、導電性のシールド部を形成することを特徴とする蓋体フレームの製造方法を提案している。

本発明によれば、樹脂モールド部形成用の一対の金型により回路基板及び蓋体フレームを挟み込むだけで、樹脂モールド部を形成する際に、溶融樹脂が空洞部に流入することを防止できると共に、蓋体フレームが回路基板に対して動くことを防止できる。したがって、半導体チップを覆う蓋体フレームを回路基板に固定する工程や、回路基板に貫通孔を形成する工程が不要となるため、空洞部に配された半導体チップを外方空間に連通させた半導体装置の製造コスト削減、及び、製造効率の向上を図ることができる。

また、内面に導電性を有するシールド部を形成した蓋体部により、半導体装置の外方側において発生した電気的なノイズが半導体チップに到達することを防ぐため、ノイズに基づく半導体チップの誤作動を防止することができる。

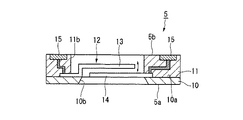

図1から図5は、本発明の第1の実施形態を示している。図1に示すように、この半導体装置1は、回路基板3と、回路基板3の厚さ方向の一端側に重ねて配された半導体チップ5、蓋体フレーム7及び樹脂モールド部9とを備えている。

半導体チップ5は、略板状に形成されており、その裏面5aが回路基板3の一端側に位置する表面3a上に接着固定されている。この半導体チップ5は、例えば、加速度を検知する機能を有した音圧センサチップからなる。

半導体チップ5は、略板状に形成されており、その裏面5aが回路基板3の一端側に位置する表面3a上に接着固定されている。この半導体チップ5は、例えば、加速度を検知する機能を有した音圧センサチップからなる。

すなわち、半導体チップ5は、図2に示すように、シリコン基板10の表面10aに多層配線板11を積層し、これらシリコン基板10及び多層配線板11の厚さ方向にわたって貫通する貫通孔10b,11bに配されたコンデンサユニット12を備えて構成されている。コンデンサユニット12は、貫通孔10b,11bの内面から突出する振動電極板13及び固定電極板14から構成されており、固定電極板14は、振動電極板13に対して微少な間隙を介して厚さ方向に重なるように配されている。これら振動電極板13及び固定電極板14は、シリコン基板10と多層配線板11との間に配されている。

このコンデンサユニット12では、多層配線板11の表面5b側から貫通孔11bに入射した音や圧力変化に基づいて振動電極板13が振動した際に、この振動に基づく振動電極板13と固定電極板14との間隙の変化を、振動電極板13と固定電極板14との間の静電容量の変化として出力するようになっている。

また、多層配線板11の表面5bには、複数のパッド電極15が露出して形成されている。これらパッド電極15は、半導体チップ5に電力を供給する役割や、コンデンサユニット12から取り出された出力信号を外部に伝達する端子としての機能を有するものである。

また、多層配線板11の表面5bには、複数のパッド電極15が露出して形成されている。これらパッド電極15は、半導体チップ5に電力を供給する役割や、コンデンサユニット12から取り出された出力信号を外部に伝達する端子としての機能を有するものである。

図1に示すように、蓋体フレーム7は、耐熱性を有する熱硬化性樹脂から形成されており、半導体チップ5を覆うように回路基板3の表面3aに配される蓋体部17と、蓋体部17から一体的に突出する筒状の突出部19とを備えている。

蓋体部17は、回路基板3の表面3aから厚さ方向に離間した位置に配される略板状の上端壁部(上端部)21と、上端壁部21の周縁から回路基板3の表面3aに向けて突出する側壁部23とを備えている。すなわち、蓋体部17は、これら上端壁部21及び側壁部23により側壁部23の先端部23a側に開口する略凹状に形成されている。そして、側壁部23の先端部23aを半導体チップ5の周縁に位置する回路基板3の表面3aに配した状態においては、回路基板3の表面3aと、上端壁部21及び側壁部23の内面21a,23bとにより中空の空洞部25が画定される。なお、この状態においては、上端壁部21が、蓋体部17のうち回路基板3の表面3aから最も離間して位置しており、また、上端壁部21及び側壁部23の内面21a,23bが、半導体チップ5に触れないように位置している。

蓋体部17は、回路基板3の表面3aから厚さ方向に離間した位置に配される略板状の上端壁部(上端部)21と、上端壁部21の周縁から回路基板3の表面3aに向けて突出する側壁部23とを備えている。すなわち、蓋体部17は、これら上端壁部21及び側壁部23により側壁部23の先端部23a側に開口する略凹状に形成されている。そして、側壁部23の先端部23aを半導体チップ5の周縁に位置する回路基板3の表面3aに配した状態においては、回路基板3の表面3aと、上端壁部21及び側壁部23の内面21a,23bとにより中空の空洞部25が画定される。なお、この状態においては、上端壁部21が、蓋体部17のうち回路基板3の表面3aから最も離間して位置しており、また、上端壁部21及び側壁部23の内面21a,23bが、半導体チップ5に触れないように位置している。

筒状の突出部19は、上端壁部21の中央部分から突出しており、上端壁部21よりも回路基板3の表面3aからさらに離間する方向に延びている。この突出部19は、空洞部25を樹脂モールド部9の外方に開口させる役割を果たしており、この突出部19の挿通孔19aを介して半導体チップ5の表面5bが外方に露出している。

また、突出部19は、回路基板3の表面3aや上端壁部21の外面21bに対して直立して延びており、蓋体部17に対して弾性変形可能となっている。すなわち、突出部19は、蓋体部17の上端壁部21との連結部分に形成された易変形部26を弾性変形させることにより、回路基板3の表面3aの直交方向に弾性的に移動させることができる。

また、突出部19は、回路基板3の表面3aや上端壁部21の外面21bに対して直立して延びており、蓋体部17に対して弾性変形可能となっている。すなわち、突出部19は、蓋体部17の上端壁部21との連結部分に形成された易変形部26を弾性変形させることにより、回路基板3の表面3aの直交方向に弾性的に移動させることができる。

また、この蓋体フレーム7には、空洞部25に対向する上端壁部21及び側壁部23の内面21a,23bに形成された薄膜状のシールド部27が設けられている。このシールド部27は、銅や銀等の導電性を有する導電性ペーストを上端壁部21及び側壁部23の内面21a,23b、並びに、突出部19の挿通孔19aの内面にわたって塗布若しくは吹付をしてなる。すなわち、蓋体部17及び突出部19は、このシールド部27によって導電性を有することになる。また、シールド部27は、蓋体部17の側壁部23の先端部23aまで延びて形成されており、蓋体フレーム7を配した状態において、回路基板3の表面3a上に接することになり、空洞部25はこのシールド部27によって覆われることになる。

また、この蓋体フレーム7には、上端壁部21の周縁から上端壁部21の長手方向に一体的に延びる一対の連結部29が形成されている。

また、この蓋体フレーム7には、上端壁部21の周縁から上端壁部21の長手方向に一体的に延びる一対の連結部29が形成されている。

回路基板3には、略板状に形成されており、表面3aに配された複数のパッド電極31と、回路基板3の厚さ方向の他端側に位置する裏面3bに配された複数の半田ボール(電極部)33と、回路基板3の内部に配され、複数のパッド電極31及び半田ボール33を個々に電気的に接続する配線部35とが設けられている。この配線部35は、例えば銅箔から形成されている。

パッド電極31は、半導体チップ5のパッド電極15とワイヤー37により電気的に接続するものであり、半導体チップ5の配置領域の周囲に配されると共に空洞部25に露出している。このパッド電極31は、例えば、銅箔に厚さ3〜5μmのニッケル(Ni)及び厚さ0.5μmの金(Au)のめっきを施したものからなる。

半田ボール33は、略球体状に形成されており、回路基板3の裏面3bから突出している。

パッド電極31は、半導体チップ5のパッド電極15とワイヤー37により電気的に接続するものであり、半導体チップ5の配置領域の周囲に配されると共に空洞部25に露出している。このパッド電極31は、例えば、銅箔に厚さ3〜5μmのニッケル(Ni)及び厚さ0.5μmの金(Au)のめっきを施したものからなる。

半田ボール33は、略球体状に形成されており、回路基板3の裏面3bから突出している。

また、回路基板3の表面3aには、導電性を有する薄膜状のシールド部材39が設けられている。このシールド部材39は、回路基板3の表面3aのうち、空洞部25と対向する領域、半導体チップ5の配置領域、及び蓋体部17の側壁部23の先端部23aを配する領域にわたって形成されている。すなわち、蓋体フレーム7を回路基板3の表面3aに配した状態においては、シールド部材39が蓋体フレーム7のシールド部27に接触するようになっている。したがって、シールド部材39は、蓋体フレーム7のシールド部27と共に半導体チップ5を含んで空洞部25を囲むように構成することになる。

なお、以上のことから前述した半導体チップ5は、このシールド部材39を介して回路基板3の表面3aに固定され、また、蓋体フレーム7の側壁部23の先端部23aも、このシールド部材39を介して回路基板3の表面3aに配されることになる。ただし、このシールド部材39には、回路基板3のパッド電極31が空洞部25に露出するように、この各パッド電極31を避ける孔39aが形成されており、シールド部材39とパッド電極31とは電気的に絶縁されている。

樹脂モールド部9は、回路基板3の表面3a、及び、内面21a,23bと反対側に位置する蓋体部17の外面21b,23cに接すると共に蓋体フレーム7の突出部19及び連結部29を包み込んでおり、回路基板3及び蓋体フレーム7を一体的に固定している。

なお、蓋体部17から突出する突出部19の開口端19b、及び、連結部29の先端部29aは、回路基板3の表面3aと同方向を向く樹脂モールド部9の表面9a、及び、この表面9aに隣接する側面9bからそれぞれ外方に露出している。

なお、蓋体部17から突出する突出部19の開口端19b、及び、連結部29の先端部29aは、回路基板3の表面3aと同方向を向く樹脂モールド部9の表面9a、及び、この表面9aに隣接する側面9bからそれぞれ外方に露出している。

すなわち、この樹脂モールド部9は、蓋体部17によって形成される中空の空洞部25を介して半導体チップ5を覆うように構成されている。なお、図1において、樹脂モールド部9は、突出部19や連結部29によって分割して形成されているように図示されているが、実際には、これら突出部19や連結部29を1つの樹脂モールド部9により包み込んでおり、樹脂モールド部9は一体的に形成されている。

次に、以上のように構成された半導体装置1の製造方法について説明する。

なお、この製造方法においては、予め、半導体装置1を構成するための複数のパッド電極31、配線部35及びシールド部材39からなるユニットを複数形成した1枚の回路基板3を用意しておく。

そして、各シールド部材39を介して回路基板3の表面3aに半導体チップ5をそれぞれ接着する。この半導体チップ5の接着は、銀ペーストを介して半導体チップ5を回路基板3の表面3aに配し、この銀ペーストを硬化させることにより行われる。この接着終了後には、回路基板3や半導体チップ5の表面3a,5b、特に、パッド電極15,31に付着している汚れを落とすプラズマクリーニングを施す。その後、ワイヤボンディングによりワイヤー37を配して半導体チップ5及び回路基板3のパッド電極15,31を相互に電気接続する。

なお、この製造方法においては、予め、半導体装置1を構成するための複数のパッド電極31、配線部35及びシールド部材39からなるユニットを複数形成した1枚の回路基板3を用意しておく。

そして、各シールド部材39を介して回路基板3の表面3aに半導体チップ5をそれぞれ接着する。この半導体チップ5の接着は、銀ペーストを介して半導体チップ5を回路基板3の表面3aに配し、この銀ペーストを硬化させることにより行われる。この接着終了後には、回路基板3や半導体チップ5の表面3a,5b、特に、パッド電極15,31に付着している汚れを落とすプラズマクリーニングを施す。その後、ワイヤボンディングによりワイヤー37を配して半導体チップ5及び回路基板3のパッド電極15,31を相互に電気接続する。

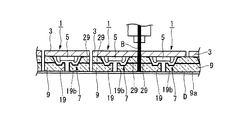

その後、図3に示すように、連結部29によって一体的に連結された複数の蓋体フレーム7を用意する(フレーム準備工程)。このフレーム準備工程では、耐熱性を有する熱硬化樹脂を用いてインジェクション成形法により相互に連結された複数の蓋体フレーム7を形成する。

次いで、各蓋体部17により各半導体チップ5を覆うように複数の蓋体フレーム7を回路基板3の表面3aに重ねて配する(フレーム配置工程)。ここで、各連結部29は、各蓋体フレーム7が各半導体チップ5を覆う所定位置に配されるように設定されているため、複数の半導体チップ5に対する各蓋体フレーム7の位置決めを容易に行うことができる。

次いで、各蓋体部17により各半導体チップ5を覆うように複数の蓋体フレーム7を回路基板3の表面3aに重ねて配する(フレーム配置工程)。ここで、各連結部29は、各蓋体フレーム7が各半導体チップ5を覆う所定位置に配されるように設定されているため、複数の半導体チップ5に対する各蓋体フレーム7の位置決めを容易に行うことができる。

そして、回路基板3の裏面3b側に平坦面E1を有する金型Eを配すると共に。回路基板3の表面3a側には、表面F1から窪んだ凹部F2を有する金型(一方の金型)Fを対向して配する。すなわち、これら一対の金型E,Fは、回路基板3をその厚さ方向から挟み込むように構成されている。

また、これら一対の金型E,Fを配置すると同時に、回路基板3及び蓋体フレーム7と金型Fとの間には、樹脂モールド部を形成する樹脂と金型Fとの離型性を良好とする薄膜状のシートSを配しておく(シート配設工程)。このシートSは、弾性変形可能となっており、例えばフッ素樹脂から形成されている。

また、これら一対の金型E,Fを配置すると同時に、回路基板3及び蓋体フレーム7と金型Fとの間には、樹脂モールド部を形成する樹脂と金型Fとの離型性を良好とする薄膜状のシートSを配しておく(シート配設工程)。このシートSは、弾性変形可能となっており、例えばフッ素樹脂から形成されている。

その後、金型Fを金型Eに近づける方向に移動させ、図4に示すように、これら一対の金型E,Fの平坦面E1及び表面F1により回路基板3を挟み込むと共に、金型Fの凹部F2の底面F3により突出部19の開口端19bを塞ぐように突出部19を回路基板3に向けて押圧する(押圧工程)。この押圧工程の際には、予めシートSを金型Fの底面F3に真空吸着(矢印a)させておく。

したがって、この押圧工程を行った状態においては、回路基板3の裏面3bが金型Eの平坦面E1に接触すると共に、回路基板3の表面3aがシートSを介して金型Fの表面F1に接触することになる。また、蓋体フレーム7の突出部19の開口端19bがシートSを介して金型Fの底面F3に当接する。この当接の際には、突出部19の開口端19bがシートSに押し付けられるため、シートSが弾性変形する。さらに、突出部19は、蓋体部17から回路基板3に対してさらに離間する方向に延びているため、金型Fと蓋体部17との間には隙間が形成されることになる。

したがって、この押圧工程を行った状態においては、回路基板3の裏面3bが金型Eの平坦面E1に接触すると共に、回路基板3の表面3aがシートSを介して金型Fの表面F1に接触することになる。また、蓋体フレーム7の突出部19の開口端19bがシートSを介して金型Fの底面F3に当接する。この当接の際には、突出部19の開口端19bがシートSに押し付けられるため、シートSが弾性変形する。さらに、突出部19は、蓋体部17から回路基板3に対してさらに離間する方向に延びているため、金型Fと蓋体部17との間には隙間が形成されることになる。

この押圧工程においては、突出部19を介して回路基板3に接する蓋体部17の先端部23aが回路基板3に押し付けられるため、蓋体部17の先端部23aと回路基板3との隙間を塞ぐことができる。

また、この押圧工程においては、突出部19が蓋体部17に対して弾性変形する。すなわち、突出部19の弾性力によって蓋体部17の先端部23aが回路基板3に適度な力で押さえつけられることになるため、蓋体部17の先端部23aと回路基板3との隙間を確実に塞ぐことができる。

さらに、突出部19の開口端19bも突出部19の弾性力によって金型Fに適度な力で押さえつけられ、かつ、金型Fの底面F3と突出部19の開口端19bとの間に配されたシートSが弾性変形するため、突出部19の開口端19bと金型Fの底面F3との隙間も確実に塞ぐことができる。以上のことから、空洞部25が外方に対して密閉されることになる。

また、この押圧工程においては、突出部19が蓋体部17に対して弾性変形する。すなわち、突出部19の弾性力によって蓋体部17の先端部23aが回路基板3に適度な力で押さえつけられることになるため、蓋体部17の先端部23aと回路基板3との隙間を確実に塞ぐことができる。

さらに、突出部19の開口端19bも突出部19の弾性力によって金型Fに適度な力で押さえつけられ、かつ、金型Fの底面F3と突出部19の開口端19bとの間に配されたシートSが弾性変形するため、突出部19の開口端19bと金型Fの底面F3との隙間も確実に塞ぐことができる。以上のことから、空洞部25が外方に対して密閉されることになる。

また、この押圧工程においては、一対の金型E,Fで蓋体フレーム7を回路基板3に押さえつけているため、蓋体フレーム7と回路基板3との相対的な位置が固定されることになる。

さらに、この押圧工程においては、突出部19が蓋体部17に対して弾性変形する。すなわち、金型Fにより蓋体部17を回路基板3に押さえつける力を突出部19の弾性変形によって吸収できる。このため、金型Fにより蓋体フレーム7を回路基板3に押さえつける力が、突出部19の弾性変形により蓋体部17に余剰に伝達されることを防いで蓋体部17が変形することを防止できる。

さらに、この押圧工程においては、突出部19が蓋体部17に対して弾性変形する。すなわち、金型Fにより蓋体部17を回路基板3に押さえつける力を突出部19の弾性変形によって吸収できる。このため、金型Fにより蓋体フレーム7を回路基板3に押さえつける力が、突出部19の弾性変形により蓋体部17に余剰に伝達されることを防いで蓋体部17が変形することを防止できる。

なお、押圧工程において突出部19の開口端19bがシートSに当接することを考慮すると、突出部19の開口端19bの形状は丸みを帯びた形状とすることが好ましい。すなわち、上記のように突出部19の開口端19bを構成することにより、突出部19の開口端19bがシートSに食い込んで、シートSに切欠が形成されること防ぎ、この切欠に基づくシートSの損傷を防止することができる。丸みを帯びた形状の開口端19bの形成は、例えば、フレーム準備工程において行えばよい。

その後、金型Fの底面F3により突出部19を押圧した状態で、金型Fの凹部F2、回路基板3、複数の蓋体部17及び突出部19により形成される1つの間隙に、エポキシ樹脂等の熱硬化樹脂を溶融した状態で注入し、回路基板3及び複数の蓋体フレーム7を一体的に固定する樹脂モールド部9を形成する(モールド工程)。なお、前述の間隙とは、樹脂モールド部9を形成するための樹脂形成空間を示している。また、この樹脂モールド部9は、1つの大きな樹脂形成空間の端部から順次溶融樹脂を注入するトランスファー成形法により形成される。

このモールド工程においては、蓋体部17の先端部23aと回路基板3との隙間が突出部19の押圧力により塞がれ、また、金型Fと突出部19の開口端19bとの隙間が突出部19の押圧力及びシートSの弾性変形により塞がれているため、樹脂形成空間に注入された溶融樹脂が空洞部25に流入することを防止できる。また、このモールド工程においては、蓋体フレーム7と回路基板3との相対的な位置が既に固定されているため、樹脂形成空間に注入される溶融樹脂によって蓋体フレーム7が回路基板3に対して動くことを防止できる。

なお、このモールド工程では、溶融樹脂を樹脂形成空間に充填した後に、樹脂を加熱して硬化させることで、図5に示すように、樹脂モールド部9が形成されることになる。

なお、このモールド工程では、溶融樹脂を樹脂形成空間に充填した後に、樹脂を加熱して硬化させることで、図5に示すように、樹脂モールド部9が形成されることになる。

このモールド工程の後には、樹脂モールド部9の表面9aの全体にシート状のダイシングテープ(目隠しシール)Dを貼付し、このダイシングテープDにより突出部19の開口端19bを塞ぐ(シール貼付工程)。その後、ブレードBにより個々の半導体装置1に切り分けるダイシング工程を行う。この際、樹脂モールド部9、回路基板3及び連結部29は切断するが、ダイシングテープDは切断しない。このダイシングテープDの切断は、ダイシング工程の終了後に行われる。

最後に、回路基板3の裏面3bに露出する配線部35に半田ボール33(図1)を取り付けることで、半導体装置1の製造が終了する。なお、ダイシングテープDは、携帯電話機やパーソナルコンピュータ等の各種電子機器の実装基板への半導体装置1の搭載が完了するまで貼付しておく。

半導体装置1を実装基板に搭載する場合には、回路基板3の裏面3bを実装基板の表面に対向させ、半田ボール33を実装基板の表面に形成されたランド部に配する。そして、半田ボール33を加熱しながら半導体装置1を実装基板の表面に押し付けることにより、半田ボール33がランド部に固定されると共に電気的に接続される。

半導体装置1を実装基板に搭載する場合には、回路基板3の裏面3bを実装基板の表面に対向させ、半田ボール33を実装基板の表面に形成されたランド部に配する。そして、半田ボール33を加熱しながら半導体装置1を実装基板の表面に押し付けることにより、半田ボール33がランド部に固定されると共に電気的に接続される。

上記の半導体装置1、半導体装置1の製造方法及びこれに使用する蓋体フレーム7によれば、一対の金型E,Fにより回路基板3及び蓋体フレーム7を挟み込むだけで、樹脂モールド部9を形成する際に溶融樹脂が空洞部25に流入することを防止できると共に、蓋体フレーム7が回路基板3に対して動くことを防止できる。したがって、半導体チップ5を覆う蓋体フレーム7を回路基板3に固定する工程や、回路基板3に貫通孔を形成する工程が不要となり、空洞部25に配された半導体チップ5を外方空間に連通させた半導体装置1の製造コスト削減、及び、製造効率の向上を図ることができる。

また、導電性を有する蓋体フレーム7のシールド部27及び回路基板3のシールド部材39が半導体チップ5を取り囲むため、半導体装置1の外方側において発生した電気的なノイズが、回路基板3及び樹脂モールド部9に侵入しても、蓋体フレーム7及びシールド部材39においてノイズが空洞部25や挿通孔19a内に侵入すること防ぐ。したがって、このノイズが半導体チップ5に到達することを確実に防止して、ノイズに基づく半導体チップ5の誤作動を確実に防止することができる。

さらに、押圧工程において凹部F2を有する金型Fにより蓋体フレーム7を回路基板3に押さえつける力が、突出部19の弾性変形により蓋体部17に余剰に伝達されることを防いで蓋体部17が変形することを防止するため、蓋体部17の変形に基づく空洞部25のばらつきを抑えることができる。

また、この突出部19の弾性力によって蓋体部17の先端部23aが回路基板3に適度な力で押さえつけられるため、蓋体部17の先端部23aと回路基板3との隙間を確実に塞ぐことができる。さらに、突出部19の開口端19bも突出部19の弾性力によって金型Fに適度な力で押さえつけられ、かつ、金型Fの底面F3と突出部19の開口端19bとの間に配されたシートSが弾性変形するため、突出部19の開口端19bと金型Fの底面F3との隙間も確実に塞ぐことができる。

また、この突出部19の弾性力によって蓋体部17の先端部23aが回路基板3に適度な力で押さえつけられるため、蓋体部17の先端部23aと回路基板3との隙間を確実に塞ぐことができる。さらに、突出部19の開口端19bも突出部19の弾性力によって金型Fに適度な力で押さえつけられ、かつ、金型Fの底面F3と突出部19の開口端19bとの間に配されたシートSが弾性変形するため、突出部19の開口端19bと金型Fの底面F3との隙間も確実に塞ぐことができる。

さらに、半導体装置1は、実装基板に対向する回路基板3の裏面3b側のみに半田ボール33を配した所謂表面実装型の構成となっているため、実装基板における半導体装置1の実装領域は回路基板3の裏面3bの面積のみとなる。したがって、実装基板に対する半導体装置1の搭載領域を小さくすることができ、実装基板の小型化を図ることができる。

また、複数の半導体装置1を製造する際には、複数の蓋体フレーム7を連結部29により連結しておくことにより、回路基板3に配された各半導体チップ5に対する各蓋体フレーム7の位置決めを容易に行うことができる。また、複数の半導体装置1を同時かつ容易に製造することができ、半導体装置1の製造効率の向上を図ることができる。

また、複数の半導体装置1を製造する際には、複数の蓋体フレーム7を連結部29により連結しておくことにより、回路基板3に配された各半導体チップ5に対する各蓋体フレーム7の位置決めを容易に行うことができる。また、複数の半導体装置1を同時かつ容易に製造することができ、半導体装置1の製造効率の向上を図ることができる。

さらに、押圧工程において、蓋体フレーム7の突出部19は、シートSを介して金型Fの底面F3に当接するため、突出部19の当接によって金型Fに傷がつくことを防止できる。また、金型Fの底面F3にシートSを配した状態でモールド工程を行うため、溶融樹脂によって金型Fが汚れることも防止できる。

また、モールド工程の終了後から各種電子機器に半導体装置1が搭載されるまでの間は、突出部19の開口端19bがダイシングテープDにより塞がれるため、ダイシング工程時や半導体装置1の搬送時や取付時に、開口端19bから空洞部25内に塵埃や水分が侵入することを防止して、これら塵埃や水分に基づく半導体チップ5の誤動作を予防することができる。

また、モールド工程の終了後から各種電子機器に半導体装置1が搭載されるまでの間は、突出部19の開口端19bがダイシングテープDにより塞がれるため、ダイシング工程時や半導体装置1の搬送時や取付時に、開口端19bから空洞部25内に塵埃や水分が侵入することを防止して、これら塵埃や水分に基づく半導体チップ5の誤動作を予防することができる。

なお、上記の実施の形態において、シールド部材39は、回路基板3の表面3aに配されるとしたが、これに限ることはなく、少なくとも蓋体部17と共に半導体チップ5を含んで空洞部25を囲むように形成されていればよい。すなわち、シールド部材39は、その一部が回路基板3の内部に配されるとしても構わない。

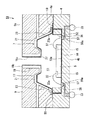

次に、本発明による第2の実施形態について図6を参照して説明する。なお、ここでは、第1の実施形態との相違点のみについて説明し、半導体装置1の構成要素と同一の部分については同一符号を付し、その説明を省略する。

図6に示すように、この実施形態に係る半導体装置51を構成する回路基板4には、その表面4aから厚さ方向に窪んで形成された断面視略矩形状の凹部53が形成されており、この凹部53の底面53aに半導体チップ5が配されている。

また、蓋体フレーム7は、この凹部53を跨いで配されている、すなわち、蓋体部17の先端部23aが凹部53の周縁に位置する回路基板4の表面4aに配されている。この状態においては、回路基板4の凹部53と、蓋体フレーム7の上端壁部21及び側壁部23とにより中空の空洞部55が画定される。

図6に示すように、この実施形態に係る半導体装置51を構成する回路基板4には、その表面4aから厚さ方向に窪んで形成された断面視略矩形状の凹部53が形成されており、この凹部53の底面53aに半導体チップ5が配されている。

また、蓋体フレーム7は、この凹部53を跨いで配されている、すなわち、蓋体部17の先端部23aが凹部53の周縁に位置する回路基板4の表面4aに配されている。この状態においては、回路基板4の凹部53と、蓋体フレーム7の上端壁部21及び側壁部23とにより中空の空洞部55が画定される。

凹部53の底面53aには、ワイヤー37により半導体チップ5のパッド電極15と電気的に接続する複数のパッド電極57が配されている。これらパッド電極57は、配線部35を介して回路基板4の裏面4bに配された複数の半田ボール33と、電気的に接続されている。

また、この回路基板4には、蓋体フレーム7のシールド部27と共に半導体チップ5を含んで空洞部55を囲むシールド部材59が設けられている。すなわち、シールド部材59は、凹部53の底面53aに配されると共に、この底面53aの周縁から回路基板4の内部を通って、凹部53の周縁に位置する回路基板4の表面4aまで延びて露出するように設けられている。したがって、蓋体フレーム7を回路基板4の表面4aに配した状態においては、シールド部材59が蓋体フレーム7のシールド部27に接触するようになっている。

また、この回路基板4には、蓋体フレーム7のシールド部27と共に半導体チップ5を含んで空洞部55を囲むシールド部材59が設けられている。すなわち、シールド部材59は、凹部53の底面53aに配されると共に、この底面53aの周縁から回路基板4の内部を通って、凹部53の周縁に位置する回路基板4の表面4aまで延びて露出するように設けられている。したがって、蓋体フレーム7を回路基板4の表面4aに配した状態においては、シールド部材59が蓋体フレーム7のシールド部27に接触するようになっている。

なお、以上のことから半導体チップ5は、このシールド部材59を介して回路基板4の表面4aに固定され、また、蓋体フレーム7の側壁部23の先端部23aも、このシールド部材59を介して回路基板4の表面4aに配されることになる。また、このシールド部材59には、回路基板4のパッド電極57が空洞部55に露出するように、この各パッド電極57を避ける孔59aが形成されており、シールド部材59とパッド電極57とは電気的に絶縁されている。

以上のように構成された半導体装置51は、第1の実施形態と同様の一対の金型E,Fを利用して製造することができる。

以上のように構成された半導体装置51は、第1の実施形態と同様の一対の金型E,Fを利用して製造することができる。

上記の半導体装置51によれば、第1の実施形態と同様の効果を奏する。

また、半導体チップ5と凹部53の底面53aに配されたパッド電極57とがワイヤー37により電気接続されるため、ワイヤー37が凹部53の外方に突出することを抑制できる。したがって、このワイヤー37を配した状態でフレーム配置工程や押圧工程を行う際に、ワイヤー37が蓋体フレーム7に触れることを防いでワイヤー37の変形を確実に防止することができる。したがって、半導体装置51を製造する際に、回路基板4と半導体チップ5との電気的な接続を容易に確保することができる。

また、半導体チップ5と凹部53の底面53aに配されたパッド電極57とがワイヤー37により電気接続されるため、ワイヤー37が凹部53の外方に突出することを抑制できる。したがって、このワイヤー37を配した状態でフレーム配置工程や押圧工程を行う際に、ワイヤー37が蓋体フレーム7に触れることを防いでワイヤー37の変形を確実に防止することができる。したがって、半導体装置51を製造する際に、回路基板4と半導体チップ5との電気的な接続を容易に確保することができる。

なお、上述した第1,第2の実施形態において、突出部19は、上端壁部21の中央部分から突出するとしたが、これに限ることはなく、少なくとも上端壁部21よりも回路基板3,4の表面3a,4aからさらに離間する方向に延び、空洞部25,55を樹脂モールド部9の表面9aから外方に開口させるように構成されていればよい。すなわち、突出部19は、蓋体部17の側壁部23から突出するとしてもよい。この構成であっても、突出部19を金型Fで押圧することができるため、半導体装置1,51を製造する際に、溶融した樹脂が空洞部25,55に流入したり、蓋体フレーム7が回路基板3,4に対して動くことを防止できる。

また、蓋体フレーム7のシールド部27は、蓋体部17を構成する上端壁部21及び側壁部23の内面21a,23b、並びに、突出部19の挿通孔19aの内面にわたって導電性ペーストを塗布して形成されるとしたが、これに限ることはなく、少なくとも蓋体部17を介して空洞部25,55内に電気的なノイズが侵入することを防止すればよい。すなわち、シールド部27は、例えば、上端壁部21及び側壁部23の外面、並びに、突出部19の外周面に導電性ペーストを塗布して形成されるとしてもよいし、導電性ペーストに漬け込んで形成されるとしても構わない。

さらに、例えば、導電性を有する樹脂により蓋体フレーム7を形成し、空洞部25,55に面する蓋体部17の内面21a,23b、及び、突出部19の挿通孔19aの内面に絶縁性の樹脂を塗布するとしても構わないし、また、これら内面21a,23bに前述の絶縁性樹脂及びシールド部27を重ねて塗布するとしてもよい。

また、蓋体部17及び突出部19が導電性を有するように構成されるとしたが、これに限ることはなく、少なくとも空洞部25,55を構成する蓋体部17が導電性を有していればよい。

また、蓋体部17及び突出部19が導電性を有するように構成されるとしたが、これに限ることはなく、少なくとも空洞部25,55を構成する蓋体部17が導電性を有していればよい。

さらに、蓋体フレーム7は、耐熱性を有する熱硬化樹脂からなるとしたが、少なくとも樹脂材料から形成されていればよい。ただし、モールド工程や半導体装置1,51の実装基板への実装時において、蓋体フレーム7が加熱されても熱変形しない程度の耐熱性を有している樹脂材料であることが好ましい。具体的には、170〜180℃程度の熱に耐えられるエンジニアプラスチック等の樹脂材料から蓋体フレーム7を形成することが好ましい。

また、空洞部25,55内への電気的なノイズの侵入防止を考慮する場合には、蓋体フレーム7を金属等の導電性材料から形成するとしても構わない。この構成の場合には、モールド工程や半導体装置1の実装基板への実装時において、蓋体フレーム7はより高温に耐えることができる。また、導電性材料は樹脂材料と比較して剛性が高いため、モールド工程において蓋体フレーム7の上端壁部21や側壁部23が撓んで変形することを防止し、空洞部25,55の確保を容易に行うことができる。

さらに、上述した樹脂材料や導電性材料から蓋体フレーム7を形成することに限らず、例えば、半導体チップ5の帯電を特に防止する場合には、カーボンを練り込んだ樹脂材料から蓋体フレーム7を形成することが好ましい。

さらに、上述した樹脂材料や導電性材料から蓋体フレーム7を形成することに限らず、例えば、半導体チップ5の帯電を特に防止する場合には、カーボンを練り込んだ樹脂材料から蓋体フレーム7を形成することが好ましい。

また、半導体装置1,51を製造する際には、連結部29によって連結された複数の蓋体フレーム7を回路基板3,4の表面3a,4aに配するとしたが、連結部29を有さない個別の蓋体フレーム7を用いるとしても構わない。

さらに、回路基板3,4の裏面3b,4bには、配線部35と電気的に接続された半田ボール33が設けられるとしたが、これに限ることはなく、少なくとも回路基板3,4の裏面3b,4bに実装基板45と電気的に接続するための電極部が露出していればよい。

すなわち、この電極部は、配線部35と一体的に形成されるとしても構わないし、配線部35が回路基板3,4の裏面3b,4bから突出するとしてもよい。

さらに、回路基板3,4の裏面3b,4bには、配線部35と電気的に接続された半田ボール33が設けられるとしたが、これに限ることはなく、少なくとも回路基板3,4の裏面3b,4bに実装基板45と電気的に接続するための電極部が露出していればよい。

すなわち、この電極部は、配線部35と一体的に形成されるとしても構わないし、配線部35が回路基板3,4の裏面3b,4bから突出するとしてもよい。

また、複数の半導体装置1,51にわたって1枚のダイシングテープDを貼付するとしたが、これに限ることはなく、例えば、別個の目隠しシールを個々の半導体装置1,51の樹脂モールド部9の表面9aに貼付して、突出部19の開口端19bを塞ぐとしても構わない。

さらに、突出部19の開口端19bを塞ぐように、ダイシングテープD等の目隠しシールを樹脂モールド部9の表面9aに貼付するとしたが、目隠しシールを貼付しなくても良い。すなわち、例えば、図7に示すように、製造を完了した半導体装置1,51を搬送する際に、半導体装置1,51を載置して搬送するための搬送トレイ(載置台)61の表面61aに、樹脂モールド部9の表面9aを対向配置させるとしてもよい。この構成の場合でも、半導体装置1,51の搬送時に、開口端19bから空洞部25,55内に塵埃や水分が侵入することを防止して、これら塵埃や水分に基づく半導体チップ5の誤動作を予防することができる。

さらに、突出部19の開口端19bを塞ぐように、ダイシングテープD等の目隠しシールを樹脂モールド部9の表面9aに貼付するとしたが、目隠しシールを貼付しなくても良い。すなわち、例えば、図7に示すように、製造を完了した半導体装置1,51を搬送する際に、半導体装置1,51を載置して搬送するための搬送トレイ(載置台)61の表面61aに、樹脂モールド部9の表面9aを対向配置させるとしてもよい。この構成の場合でも、半導体装置1,51の搬送時に、開口端19bから空洞部25,55内に塵埃や水分が侵入することを防止して、これら塵埃や水分に基づく半導体チップ5の誤動作を予防することができる。

また、半導体チップ5と回路基板3,4とは、ワイヤー37により電気接続されるとしたが、これに限ることはなく、少なくとも半導体チップ5と回路基板3,4とが電気接続されていればよい。すなわち、例えば、半導体チップ5及び回路基板3,4のパッド電極15,31,57が相互に対向するように、半導体チップ5を回路基板3,4の表面3aや凹部53の底面53aに配するとしても構わない。

さらに、半導体チップ5として音圧センサチップを一例に挙げたが、これに限ることはなく、半導体チップ5は、例えば、半導体装置1の外部空間の圧力や圧力変化を計測する圧力センサチップであっても構わない。

さらに、半導体チップ5として音圧センサチップを一例に挙げたが、これに限ることはなく、半導体チップ5は、例えば、半導体装置1の外部空間の圧力や圧力変化を計測する圧力センサチップであっても構わない。

以上、本発明の実施形態について図面を参照して詳述したが、具体的な構成はこの実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。

1,51・・・半導体装置、3,4・・・回路基板、5・・・半導体チップ、7・・・蓋体フレーム、9・・・樹脂モールド部、17・・・蓋体部、19・・・突出部、19b・・・開口端、21・・・上端壁部(上端部)、25,55・・・空洞部、31,57・・・パッド電極、33・・・半田ボール(電極部)、35・・・配線部、39,59・・・シールド部材、53・・・凹部、53a・・・底面、D・・・ダイシングテープ(目隠しシール)、E・・・金型、F・・・金型(一方の金型)、S・・・シート

Claims (5)

- 回路基板にその厚さ方向の一端側に重ねて固定されると共に電気的に接続された半導体チップを、中空の空洞部を介して樹脂により覆う構成の半導体装置に使用する蓋体フレームであって、

前記半導体チップを覆うように前記回路基板の一端側に設けて前記空洞部を形成する蓋体部と、該蓋体部から前記空洞部の外方側に突出すると共に前記空洞部を外方に開口させる筒状の突出部とを備え、

前記突出部が、前記蓋体部の上端部からさらに前記厚さ方向に延びており、

前記空洞部に対向する前記蓋体部の内面に、導電性のシールド部が形成されていることを特徴とする蓋体フレーム。 - 前記シールド部が、前記突出部の内面にも形成されていることを特徴とする請求項1に記載の蓋体フレーム。

- 熱硬化性樹脂によって形成され耐熱性を有することを特徴とする請求項1又は請求項2に記載の蓋体フレーム。

- 前記シールド部が、導電性材料からなることを特徴とする請求項1から請求項3のいずれか1項に記載の蓋体フレーム。

- 回路基板にその厚さ方向の一端側に重ねて固定されると共に電気的に接続された半導体チップを、中空の空洞部を介して樹脂により覆う構成の半導体装置に使用する蓋体フレームを製造する蓋体フレームの製造方法であって、

耐熱性を有する熱硬化性樹脂を用いてインジェクション成形法により、前記回路基板と共に前記空洞部を形成する蓋体部と、前記蓋体部の上端部からさらに前記厚さ方向に延びるように突出すると共に前記空洞部を外方に開口させる筒状の突出部とを一体に形成し、

前記空洞部に対向する前記蓋体部の内面に、導電性を有する導電性材料を塗布若しくは吹付して、導電性のシールド部を形成することを特徴とする蓋体フレームの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007268017A JP4609478B2 (ja) | 2007-10-15 | 2007-10-15 | 蓋体フレーム及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007268017A JP4609478B2 (ja) | 2007-10-15 | 2007-10-15 | 蓋体フレーム及びその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005138371A Division JP4049167B2 (ja) | 2005-03-16 | 2005-05-11 | 蓋体フレーム、半導体装置、及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008028427A JP2008028427A (ja) | 2008-02-07 |

| JP4609478B2 true JP4609478B2 (ja) | 2011-01-12 |

Family

ID=39118676

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007268017A Expired - Fee Related JP4609478B2 (ja) | 2007-10-15 | 2007-10-15 | 蓋体フレーム及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4609478B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013096994A (ja) * | 2011-10-28 | 2013-05-20 | Robert Bosch Gmbh | コンタクト手段を直接コンタクティングする装置および圧力測定セル用の付属の接続装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09304211A (ja) * | 1996-05-15 | 1997-11-28 | Omron Corp | 静電容量型圧力センサのパッケージング構造およびパッケージング方法 |

| JP3846094B2 (ja) * | 1998-03-17 | 2006-11-15 | 株式会社デンソー | 半導体装置の製造方法 |

| JP2002077346A (ja) * | 2000-09-01 | 2002-03-15 | Taiyo Yuden Co Ltd | 携帯通信端末器 |

| JP3835739B2 (ja) * | 2001-10-09 | 2006-10-18 | シチズン電子株式会社 | エレクトレットコンデンサマイクロフォン |

| JP2004053329A (ja) * | 2002-07-18 | 2004-02-19 | Hitachi Ltd | 半導体センサ組み立て体およびタイヤモニタセンサ |

-

2007

- 2007-10-15 JP JP2007268017A patent/JP4609478B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013096994A (ja) * | 2011-10-28 | 2013-05-20 | Robert Bosch Gmbh | コンタクト手段を直接コンタクティングする装置および圧力測定セル用の付属の接続装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008028427A (ja) | 2008-02-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4049160B2 (ja) | 蓋体フレーム、半導体装置、及びその製造方法 | |

| JP6671441B2 (ja) | 電子部品収納用パッケージ、多数個取り配線基板、電子装置および電子モジュール | |

| JP5277755B2 (ja) | 電子部品 | |

| US8902604B2 (en) | Component support and assembly having a MEMS component on such a component support | |

| JP6496865B2 (ja) | 電子部品収納用パッケージ、電子装置および電子モジュール | |

| US20090230487A1 (en) | Semiconductor device, semiconductor device manufacturing method and lid frame | |

| CN102342194B (zh) | 电子部件安装装置及其制造方法 | |

| JP6400509B2 (ja) | 電子部品の製造方法 | |

| CN109495831B (zh) | 一种mems麦克风的封装结构及其制造方法 | |

| JP5458517B2 (ja) | 電子部品 | |

| JP4049167B2 (ja) | 蓋体フレーム、半導体装置、及びその製造方法 | |

| JP2019192825A (ja) | 電子部品収納用パッケージ、電子装置、および電子モジュール | |

| JP4609478B2 (ja) | 蓋体フレーム及びその製造方法 | |

| CN104517926B (zh) | 制造半导体器件的方法 | |

| JP4742706B2 (ja) | 半導体装置及びその製造方法 | |

| KR102163037B1 (ko) | 적층 세라믹 커패시터 조립체 | |

| JP5346866B2 (ja) | 磁性体基板、及び、電子回路モジュール | |

| JP6813682B2 (ja) | 電子部品収納用パッケージ、電子装置および電子モジュール | |

| JP3705235B2 (ja) | 半導体装置の製造方法 | |

| JP2007071821A (ja) | 半導体装置 | |

| JP2016012692A (ja) | 電子部品の樹脂パッケージの形成方法 | |

| JP5039740B2 (ja) | 変速制御装置及び機電一体型電子制御装置 | |

| JP2008028428A (ja) | 蓋体フレーム及びその製造方法 | |

| WO2019021766A1 (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2012256761A (ja) | 電子装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100914 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100927 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131022 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |