JP4545397B2 - 画像表示装置 - Google Patents

画像表示装置 Download PDFInfo

- Publication number

- JP4545397B2 JP4545397B2 JP2003174235A JP2003174235A JP4545397B2 JP 4545397 B2 JP4545397 B2 JP 4545397B2 JP 2003174235 A JP2003174235 A JP 2003174235A JP 2003174235 A JP2003174235 A JP 2003174235A JP 4545397 B2 JP4545397 B2 JP 4545397B2

- Authority

- JP

- Japan

- Prior art keywords

- display device

- memory

- film

- tft

- memory element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

- G09G3/3611—Control of matrices with row and column drivers

- G09G3/3648—Control of matrices with row and column drivers using an active matrix

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2011—Display of intermediate tones by amplitude modulation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09K—MATERIALS FOR MISCELLANEOUS APPLICATIONS, NOT PROVIDED FOR ELSEWHERE

- C09K2323/00—Functional layers of liquid crystal optical display excluding electroactive liquid crystal layer characterised by chemical composition

-

- C—CHEMISTRY; METALLURGY

- C09—DYES; PAINTS; POLISHES; NATURAL RESINS; ADHESIVES; COMPOSITIONS NOT OTHERWISE PROVIDED FOR; APPLICATIONS OF MATERIALS NOT OTHERWISE PROVIDED FOR

- C09K—MATERIALS FOR MISCELLANEOUS APPLICATIONS, NOT PROVIDED FOR ELSEWHERE

- C09K2323/00—Functional layers of liquid crystal optical display excluding electroactive liquid crystal layer characterised by chemical composition

- C09K2323/05—Bonding or intermediate layer characterised by chemical composition, e.g. sealant or spacer

- C09K2323/051—Inorganic, e.g. glass or silicon oxide

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0847—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor being a dynamic memory without any storage capacitor, i.e. with use of parasitic capacitances as storage elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0857—Static memory circuit, e.g. flip-flop

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/088—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements using a non-linear two-terminal element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0264—Details of driving circuits

- G09G2310/027—Details of drivers for data electrodes, the drivers handling digital grey scale data, e.g. use of D/A converters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/04—Partial updating of the display screen

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2360/00—Aspects of the architecture of display systems

- G09G2360/12—Frame memory handling

- G09G2360/128—Frame memory using a Synchronous Dynamic RAM [SDRAM]

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2074—Display of intermediate tones using sub-pixels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of switching materials, e.g. deposition of layers

- H10N70/026—Formation of switching materials, e.g. deposition of layers by physical vapor deposition, e.g. sputtering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/061—Shaping switching materials

- H10N70/063—Shaping switching materials by etching of pre-deposited switching material layers, e.g. lithography

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/231—Multistable switching devices, e.g. memristors based on solid-state phase change, e.g. between amorphous and crystalline phases, Ovshinsky effect

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/823—Device geometry adapted for essentially horizontal current flow, e.g. bridge type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/828—Current flow limiting means within the switching material region, e.g. constrictions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

- H10N70/8828—Tellurides, e.g. GeSbTe

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T428/00—Stock material or miscellaneous articles

- Y10T428/13—Hollow or container type article [e.g., tube, vase, etc.]

- Y10T428/1352—Polymer or resin containing [i.e., natural or synthetic]

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Computer Hardware Design (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Nonlinear Science (AREA)

- Optics & Photonics (AREA)

- Mathematical Physics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Semiconductor Memories (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

- Liquid Crystal (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

Description

【発明の属する技術分野】

本発明は高画質化が容易な画像表示装置に係り、特に画像表示用メモリをTFTにより構成した低電力化が可能な画像表示装置に関する。

【0002】

【従来の技術】

第1の従来技術として、薄膜トランジスタ(Thin Film Transistor;以下、TFTと称する。)を用いたアクティブマトリクス型表示装置において、同一製造工程のTFTにより構成された不揮発性メモリを同一基板上に内蔵した表示装置があり、例えば特許文献1、特許文献2に開示されている。これらの表示装置の構成を図16に示す。表示部100には、画素104がマトリクス状に配置されている(図面の簡略化のため、画素104は1個だけ記載した)。いずれの公知例でも、不揮発性半導体メモリとして、電荷蓄積層とフローティングゲートを持ったEEPROM(Electrically Erasable and Programmable Read Only Memory)が用いられており、表示部100の周辺に、信号系回路101,走査系回路102,TFT−EEPROMよりなる不揮発性半導体メモリ103を配置した構成をとっている。このようにすることで、LSIを用いずに不揮発性メモリ機能を表示装置に内蔵することができる。

【0003】

また、第2の従来技術として同一製造工程のTFTにより構成された半導体メモリを同一基板上に内蔵し、フレームメモリに応用した液晶表示装置があり、例えば特許文献3等に詳しく記載されている。この表示装置の構成を図17に示す。画素115が表示領域110にマトリクス状に配置され、画素115はゲート線117、信号線116およびゲート線117を介してDA変換回路113および走査系回路114に接続され、DA変換回路113には、フレームメモリ112および信号系回路111が接続されている。このフレームメモリ112は、メモリセルが1トランジスタと1容量により構成されるDRAM(Dynamic Random Access Memory)であり、1フレームの表示情報を記憶しているため、外部からの表示データの書き込みが停止しても表示を継続することができる。

【0004】

別の第3の従来技術として、同一製造工程のTFTにより構成された半導体メモリを同一基板上に内蔵し、1ビット画素メモリに応用した液晶表示装置があり、例えば特許文献4等に詳しく記載されている。この表示装置の構成を図18に示す。画素123が表示部120にマトリクス状に配置され、画素123はゲート線126と交流駆動信号線127を介して走査系回路122に、および正信号線124と負信号線125を介して信号系回路121に接続されている。画素123には1ビットのSRAM(Static Random Access Memory) が設けられている。これによって本液晶表示パネルは、表示部へのデータ出力を停止しても、1ビットの画像表示を継続することができる。

【0005】

なおこれらの従来技術のメモリ回路は、Si半導体−TFTを用いて構成されている。以上のような従来技術によれば、多様なメモリ機能をSi半導体TFTにより内蔵することができ、表示装置の高機能化や消費電力の削減を可能にする。

【特許文献1】

特開2000-252373号公報

【特許文献2】

特開2001−326289号公報

【特許文献3】

特開平11−85065号公報

【特許文献4】

特開平8−286170号公報

【発明が解決しようとする課題】

今後、表示機能や表示システムを同一基板上に内蔵する平面表示装置の方向性として、内蔵する機能やシステムをLSIとTFT回路で分担し、画素メモリやフレームメモリなどのような画像表示用メモリをTFTにより構成するようになる。またその表示装置の特徴として、画素数の増大による高精細化と表示領域以外の周辺領域面積の縮小と低消費電力化が必要になるため、それに伴ってメモリ容量を増加しメモリの面積と消費電力を低減する必要が生ずる。さらにその製造プロセスの課題としては、LSIと比較するとかなり低いプロセス温度で、表示装置を製造することが必要である。ところが上記従来技術の延長上では、これらの課題を同時に満足して,記憶画像データの多ビット化を十分に両立させることは困難であった。

【0006】

すなわち、電荷蓄積を利用したSi半導体EEPROMを用いた第1の従来例においては、プロセス温度が低いために絶縁膜や多結晶Si中の電荷捕獲準位が多く、これに基づく記憶情報のバラツキが大きく、またTFT特性のバラツキもLSIに比べると大きいため、メモリの高容量化と低電圧化が難しい問題がある。

【0007】

また、Si半導体DRAMを用いた第2の従来例においては、画素数の増大に際してメモリセルの数が増大することによって、信号電圧の変化量は極めて小さなものになるため、より低S/Nの信号電圧を高性能な回路により増幅しなければならなくなる。しかし、TFTはLSIに比べてプロセス温度が低く、加工寸法も大きいためTFT回路の性能が低く、これで低S/Nの信号電圧を精度良く増幅することが難しくなる。また回路の複雑化や消費電力を増加させることになり、やがてはメモリセルの数に制限されて画素数の増加には限界が来てしまう問題がある。

【0008】

また、画素内にSRAMを設ける第3の従来例では、SRAMのトランジスタ数が多いために必然的に画素構造が複雑になってしまうという問題点を有する。画素構造が複雑化すると,画素の開口率低下による輝度低下をもたらし、液晶表示装置の場合には、反射モードで使用するときの低消費電力化と透過モードで使用するときの高輝度化の両立ができなくなる。さらに面積階調などの方法による多ビットの画素データ表示や、高精細化を困難にする問題がある。

【0009】

【課題を解決するための手段】

上記課題は、以下の手段により解決できる。すなわち、第1および第2の実施形態によれば、画像データを保持するメモリを有する画素をマトリクス上に配置した表示部と、画素に表示信号を入力するための信号系回路と、画素を走査する走査系回路を有する画像表示装置において、各画素メモリのデジタル画像データ保持手段は、電気抵抗の形で所定の時間以上記憶するための、1個以上のスイッチと記憶素子よりなる1ビットのデータ保持可能なメモリ回路で行う。この記憶素子は、低温な製造方法で形成することができる。こうすることにより、低温プロセスでのメモリ回路形成とメモリ機能部分の面積縮小が可能になり、上記課題を解決することができる。

【0010】

また第3および第4の実施形態によれば、画素をマトリクス上に配置した表示部と、画素に表示信号を入力するための信号系回路と、画像データを保持するフレームメモリと、DA変換回路と、画素を走査する走査系回路を有する画像表示装置において、フレームメモリのデジタル画像データ保持手段は、電気抵抗の形で所定の時間以上記憶するための1個以上のスイッチと記憶素子よりなる、1ビットのデータ保持可能な複数のメモリセルで行う。この記憶素子は、低温な製造方法で形成することができる。こうすることにより、低温プロセスでのメモリセル形成とメモリセルの面積縮小が可能になり、上記課題を解決することができる。

【0011】

更にこれらに加えて多ビットの画像データを表示するという上記課題は、以下の手段を用いることで、より効果的に解決できる。すなわち、上記デジタル画像データ保持を行うメモリセルや各画素内に、nビットの表示信号を電気抵抗の形で所定の時間以上記憶するための、多値の電気抵抗の形で記憶することができる1個の記憶素子を設ける。この記憶素子は、低温な製造方法で形成することができる。こうすることによって、低温プロセスでのメモリ回路やメモリセル形成とメモリ回路やメモリセルの面積縮小が可能になり、上記課題を解決することができる。

【0012】

【発明の実施の形態】

(第1の実施例)

以下に図1〜図5を用いて、本発明の第1の実施例を説明する。

始めに本実施例の全体構成に関して述べる。図1は、多結晶Si−TFT表示パネルの構成図であり、カルコゲナイド材料を用いた不揮発性相変化メモリよりなる画素メモリを有する。本実施例は、バックライトを用いた透過モード表示と、外光を利用した反射モード表示の双方の機能を兼ね備えた部分透過型液晶表示装置を例に取ったが、透過型液晶表示装置や、反射型液晶表示装置に、本発明を実施する場合は、反射領域のレイアウトを必要に応じて変更すればよい。また、他のTFT表示装置、例えば有機EL表示装置に本発明を実施する場合は、図1の液晶表示素子10を有機発光ダイオードに変えればよく、TFTおよびメモリ回路の製造方法やレイアウトは、本実施例とすべて同じである。

【0013】

図1において、メモリTFT8と記憶素子9と等価容量10であらわされる液晶表示部を有する画素2が、表示部にマトリクス状に配置され(図面の簡略化のため、図1には画素2を9個だけ記載した)、記憶素子9の他端は信号線SLに接続され,画素2はゲート線GLと画素線PLを介して走査系回路5に、および信号線SL、書き込み回路7を介して信号系回路4に接続されている。メモリTFT8と記憶素子9により構成される不揮発性メモリにより、各画素で1ビットの画像データを保持することができる。本実施例は、赤、緑、青を表示する画素が、それぞれ面積の異なる3画素で構成され、合計9画素でそれぞれの色の階調を表示する面積階調方式の液晶表示装置である。

【0014】

図2には、図1の画素2の平面構造を表した平面図であり、2つの画素の一部を示している。メモリTFT8は多結晶Si層PSとゲート電極GEとコンタクトホールCNからなり、ドレイン電極が局部配線LCにより、記憶素子9と液晶に電圧を印加するための透明画素電極PEに接続されている。この局部配線LCは必要に応じて面積を大きくし、反射板の機能を兼ねている。ビアホールVCは、局部配線LCと画素電極PEを接続するための開口部である。メモリTFT8のもう片方のソース電極は、局部配線LCを介して画素線PLに接続されている。ゲート電極GEは同一金属層で形成されるゲート線GLに接続されている。

【0015】

記憶素子9は、Te,Se,Sのうちの少なくとも一元素を含む、膜厚100nm前後のカルコゲナイド膜CHからなる可変抵抗であり、局部配線LCを介して片方の電極がメモリTFT8に、もう片方の電極が信号線SLに接続される。この記憶素子は、パルス電圧の印加によってカルコゲナイド膜を結晶化、および非晶質化させることができ、通常は高電圧短パルス(例えば20ns)によって高抵抗の非晶質状態にし、低電圧の長め(例えば50ns)のパルスによって低抵抗の結晶状態にするが、パルス幅か電圧を同じにしても良い。図2の平面図では、紙面の都合で記憶素子9の一部しか示されていないが、実際は画素領域の横一辺に沿うように記憶素子9が配置されている。本実施例の場合、記憶素子9の長さはほぼ20μm前後であり、記憶素子9の抵抗値が、結晶状態でほぼ100kΩ前後、非晶質状態でほぼ100MΩ前後であった。

【0016】

以下、本実施例の動作の概要を説明する。走査系回路5がゲート線GLを介して所定の画素行のメモリTFTを開閉することによって、信号系回路4が信号線SLに出力した画像データを、1ビット毎にメモリTFT8および記憶素子9で構成されるメモリに入力し,書き込み回路7により電気抵抗の形で書き込む。この記憶素子に書き込まれた画像データにより、液晶10に印加する電圧を制御することにより,画像の表示、すなわち光の透過か非透過かを制御することができる。この時,面積が異なる3個の画素の表示組み合わせを用いて、各色表示の階調に対応させることにより、フルカラー表示が可能になる。

次に、図2中にAA’と一点鎖線で示した、メモリTFTと記憶素子の部分の製造方法と断面構造を、図3の製造工程断面図により説明する。

まず図3(a)に示したように、ガラス基板20に、Si窒化膜やPドープSi酸化膜からなる第1のパシベーション膜21とSi酸化膜22とアモルファスSi膜をプラズマCVD(Chemical Vapor Deposition)法により堆積し、レーザアニール法や固相成長法により、このアモルファスSi膜を結晶化することにより多結晶Si膜PSを形成した。ここで、多結晶Si膜PSを形成する他の方法として、低温CVD法で直接多結晶Si膜を、Si酸化膜22の上に堆積することもできる。その後選択的に多結晶Si膜PSをエッチングすることにより、TFT形成領域に多結晶Si膜PSを島状に残し、ゲートSi酸化膜23をプラズマCVD法により堆積し、例えばMoを主成分としたゲート膜を堆積、選択エッチングを行い、ゲート電極GEとゲート線GLを形成した。

【0017】

次に図3(b)に示したように、イオン打ち込み法やイオンドーピング法などによる不純物イオンの導入と活性化のための熱処理を行い、ソース拡散層24およびドレイン拡散層25を形成した後、Si窒化膜やPドープSi酸化膜などを含んだ第2のパシベーション膜26をCVD法により堆積した。なおここでは、紙面の都合でn型チャネルのメモリTFTの断面図のみ示しているが、実際には必要に応じて、周辺回路にp型チャネルTFTや、LDD(Lightly Doped Drain)構造のTFTを形成した。その後、Te,Se,Sのうちの少なくとも一元素を含むカルコゲナイド材料からなる、膜厚100nm前後のカルコゲナイド膜CHを、例えば室温や室温に近い低温のスパッタリング法により堆積した。本実施例ではカルコゲナイド材料に、例えばZnとTeが主成分の材料を用いた。その後、カルコゲナイド膜CH上に、Si酸化膜27を堆積した。この時Si酸化膜27の上に、非晶質化するときのカルコゲナイド膜の蒸発や変形を防ぐための、膜厚50nm以上のCr2O3膜や、他の誘電体の層、または誘電体と金属との積層膜を、スパッタリング法により堆積することも可能である。また必要に応じて、例えばレーザアニールやRTA(Rapid Thermal Annealing)により、カルコゲナイド膜CHを結晶化することも可能である。さらにこれらの熱処理は、上記不純物イオン活性化のための熱処理を兼ねることも可能である。

【0018】

次に図3(c)に示したように、リソグラフィ法を用いて、記憶素子を形成する領域に選択的にレジスト膜28を残し、このレジスト膜28をマスクに用いて、ドライエッチング法によりカルコゲナイド膜CHを選択的に除去し、続いて同じレジスト膜28をマスクに用いて、ウエットエッチング法によりSi酸化膜27を選択的に除去した。この時Si酸化膜27は、サイドエッチングによりレジスト膜28より後退してエッチングされた。

【0019】

次に図3(d)に示したように、レジスト膜を除去し、ゲート電極材料と同じ例えばMoを主成分としたバリアメタル膜BMと、局部配線LCや信号線SLや反射板に用いるAl膜、あるいは例えばAlとTiの積層膜のようなAl膜を主材料とした金属積層膜を堆積した。このバリアメタル膜BMは、その他の材料、例えばWやTiNなどでも可能である。その後、配線および反射板として用いる領域以外の金属積層膜とバリアメタル膜BMを、例えばドライエッチング法やウエットエッチング法により選択的に除去した。この時、カルコゲナイド膜CHのSi酸化膜27と、配線LCのいずれにも覆われていない領域29が、同時にエッチングされた。このSi酸化膜27と配線を、図2の記憶素子の平面図で説明すると、Si酸化膜残存部が波線で示した領域11、配線が波線で示した領域LCおよびSLである。従って、斜線で示した領域12のカルコゲナイド膜が同時に除去されることになり、ドッグボーン形状の記憶素子が形成された。この製造方法ため、抵抗の長さや幅がリソグラフィの合わせずれの影響を受けることがなく、自己整合的に抵抗値が決定された。

【0020】

次に図3(e)に示したように、必要に応じて金属積層膜LCと同一膜よりなる反射板形成工程を経た後、Si窒化膜やPドープSi酸化膜からなる第3のパシベーション膜30と、例えば有機材料からなる低誘電率の第4のパシベーション膜31を堆積した。その後、水素アニールやプラズマ処理による水素化処理を行った。

【0021】

最後に、図2に示したビアホールVC(図3には示さず)を開口し、透明電極膜を堆積し、所望の形状になるように透明電極PE(図3には示さず)を形成し、配線層LCと透明電極PEを接続した。その後液晶工程に進み、透過モード表示と反射モード表示の双方の機能を兼ね備えた液晶表示装置を完成した。

【0022】

以上の製造工程では、基板に耐熱性の低いガラス基板を用いたため、製造中の温度を全て基板の耐熱温度以下(例えば600℃以下)あるいは、それより温度が高くても製造に不都合をもたらさないような非常に短時間な処理を行った。また自己整合プロセスを用いたため、1回のリソグラフィ工程の追加だけで、相変化画素メモリを表示装置に付加することができ、またリソグラフィ工程の合わせずれの影響を受けずに、記憶素子9の抵抗値を決めることができた。また、カルコゲナイド膜CHをバリアメタル膜BMや、Si酸化膜27で覆い、Alと接触しない構造にしたため、カルコゲナイド材料がAl材料の影響を受けることがなかった。またカルコゲナイド膜CHは、Si窒化膜やPドープSi酸化膜のような可動イオンの影響を排除できる膜からなる、第1のパシベーション膜21と第2のパシベーション膜26、および第3のパシベーション膜30に、上下から挟まれた構造を有するため、可動イオンの影響を受けずに、安定した抵抗値を有する記憶素子を形成することができた。この結果、メモリTFTのオン抵抗が〜500kΩ前後であるのに対して、記憶素子である相変化可変抵抗が、非晶質状態でほぼ100MΩ前後の高抵抗になり、安定したメモリ動作を実現できた。

【0023】

以上のような構成および動作を採用することによって、周辺回路の動作を止めて画像データの入出力を停止しても、各画素のメモリに保持された画像データに基づき表示を続けることができる。また、このメモリは不揮発性メモリであるため、リフレッシュと呼ばれる情報の定期的な再書き込み動作が不要である。さらに、本方式は保持データに従って常に液晶に電圧を印加し続けるので、液晶の表示を保持するための付加容量が必要ない。また1つのメモリTFT8と1つの記憶素子9でデータ保持を行い、その記憶素子9はブラックマトリクスと呼ばれる光を遮断する領域や、ゲート線GLの領域上に形成するので、メモリを付加するために必要な面積を縮小できる。そのために、画素の面積を縮小しながら各画素の開口率を大きくとれて、透過モードの表示に必要なバックライトの消費電力を低減できる。これらの発明の効果により、各色で階調を持ったフルカラーの高精細表示が可能となるだけでなく、反射モード表示と透過モード表示のいずれにおいても、消費電力を大幅に低減することが可能となる。

【0024】

以上に述べた本実施例においては、本発明の主旨を損なわない範囲でいくつもの変更が可能である。例えば、相変化可変抵抗記憶素子9を形成する材料としては、本実施例のZnとTeを主成分とする材料に限ったものではなく、Te,Se,Sのうちの少なくとも一元素を含むカルコゲナイド材料であればよい。例としては、Ge5Sb2Te8の組成を有する材料でもよい。また、これらの材料よりなるカルコゲナイド膜CHの少なくとも一部に、電極間を横切るように、すなわち導電パスを横切って遮断するように酸化物、窒化物、硫化物、炭化物などの誘電体とカルコゲナイド材料との混合膜を形成することにより、最初の低抵抗状態へのセット時にその領域の誘電体中に、カルコゲナイドのフィラメント状領域が形成されて細い導電パスとなり、そこだけに電流が流れるので高い抵抗値を得ることができる。好ましい誘電体材料は酸化ゲルマニウム、窒化ゲルマニウム、酸化シリコン、窒化シリコン、酸化タンタル、酸化モリブデン、炭化シリコン、硫化亜鉛である。代表的例として、カルコゲナイド:Ta2O5の混合比が3:7のもので、抵抗がほぼ1桁上昇する。この場合混合比としては、1:9から6:4の範囲が好ましい。この範囲よりカルコゲナイドが多いと、抵抗上昇効果が2倍未満であり、カルコゲナイドが少ないとフィラメント形成が困難になり、抵抗変化が1桁以下となり小さ過ぎる。この混合膜領域は、どちらかの電極に接して設けるのが好ましいが、両電極に接しない状態でも高い抵抗値を得ることが可能である。どちらかの電極に接して設ける場合は、プラスイオンによりフィラメントが形成されることから、マイナス電極に接して設けられるのがメモリ動作の安定性の点で最も好ましい。この場合、図3(e)のカルコゲナイド膜CHと、バリアメタル膜BMが接する部分に、上記混合膜領域を設けることで実現できる。

【0025】

また、本実施例ではTFT基板にガラス基板20を用いたが、これを石英基板や透明プラスチック基板等透明絶縁基板に変更することも可能であるし、また透過型液晶表示や反射型液晶表示のみに特化することも可能である。また、表示部分を有機発光ダイオードに変えることで、本発明を有機EL表示装置に実施する事も可能である。あるいはTFTに関しても、本実施例ではメモリTFTにnチャネル型TFTを用いたが、これをpチャネル型TFTに変更することも可能であるし、記憶素子の抵抗値をさらに大きくした場合には、メモリTFTにアモルファスSi−TFTを用いることも可能である。また、TFTの構造としては本実施例に限ったものではなく、例えばゲート電極GEが多結晶Si領域PSの下にある構造のTFTでも、本発明の効果を得られることは、いうまでもない。

(第2の実施例)

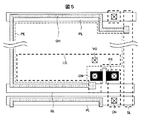

以下図4および図5を用いて、本発明の第2の実施例を説明する。

本実施例は、第1の実施例と同じ相変化画素メモリを有する、面積階調方式の部分透過型液晶表示装置において、記憶素子9の平面構造や断面構造を変えて、記憶素子の抵抗を大きくした実施例である。図4および図5は、記憶素子9の部分を拡大して示した平面図である。実際の画素メモリ回路は、第1の実施例には限らず種々の回路が可能であり、例えば複数の可変抵抗記憶素子と複数のTFTよりなるメモリ回路でも可能である。ここでは記憶素子9の構造を説明するのが目的であるので、図4および図5には簡略化して回路の一部を示した。図4の例では、カルコゲナイド膜CHからなる記憶素子9が、ゲート線GLおよび画素線PL上にまたがり、かつ折り返して配置されている。このため、第1の実施例と比較して、抵抗の長さをほぼ3倍前後長くすることができた。また図5の例も、メモリTFTの平面構造は第1の実施例と同じであるが、カルコゲナイド膜CHからなる記憶素子9が、画素の周辺に沿って配置されている。このため、第1の実施例と比較して、抵抗の長さをほぼ3〜4倍前後長くすることができた。これらの相変化抵抗は、いずれもブラックマトリクスと呼ばれる光を遮断する領域や、ゲート線GL、画素線PLの領域上に形成する。さらにこれらの例では、TFTおよび記憶素子9の製造方法は第1の実施例とほぼ同じであるが、カルコゲナイド膜CHの膜厚を50nm前後まで薄膜化し、また抵抗の幅を半分程度まで細くした。これらの理由により、メモリ付加に必要な面積を大きくせずに、非晶質状態の抵抗値を1GΩ以上にまで大きくすることができ、画素メモリの保持データに基づいて表示しているときの消費電力を、さらに低減することができた。

【0026】

これらの実施例では、平面構造や断面構造を変えることで抵抗値を大きくしたが、例えばさらに非晶質状態の抵抗率の高いカルコゲナイド材料を用いることでも、例えば非晶質状態の抵抗値を10GΩ以上にまで増やすことが可能である。また、カルコゲナイド膜CHの少なくとも一部に、電極間を横切るように、すなわち導電パスを横切って遮断するように酸化物、窒化物、硫化物、炭化物などの誘電体とカルコゲナイド材料との混合膜を形成することにより、高い抵抗値を得ることも可能である。この混合膜領域は、どちらかの電極に接して設けるのが好ましいが、両電極に接しない状態でも高い抵抗値を得ることが可能である。どちらかの電極に接して設ける場合は、マイナス電極に接して設けられるのが、メモリ動作の安定性の点で最も好ましい。この場合、図4および図5のカルコゲナイド膜CHと、局部配線LCが接続している領域(実際はバリアメタル膜BMが、カルコゲナイド膜CHに接する)に、上記混合膜領域を設けることで実現できる。

さらに、カルコゲナイド膜よりなるデータ保持用抵抗を本実施例以上の高抵抗にし、結晶状態を変えるためのジュール熱発生用抵抗素子をカルコゲナイドとは別の材料で低抵抗に形成して、データ保持用高抵抗素子とジュール熱発生用低抵抗素子を、薄膜絶縁膜により電気的に絶縁しながら積層することにより、データ保持状態の消費電力をさらに低減しながら、より低電圧で効率的に書き込み動作を行うことも可能である。

(第3の実施例)

以下図6〜図10を用いて、本発明の第3の実施例を説明する。

始めに本実施例の全体構成に関して述べる。図6は、本実施例である多結晶Si−TFT表示装置の構成図であり、カルコゲナイド材料を用いた相変化メモリよりなるフレームメモリを有する。本実施例では6ビット階調の有機EL表示素子を例に取った。なおここでは図面の簡略化のために画素は2画素のみ記載しているが、実際には精細度に応じて複数の画素が設けられている。各画素41は有機発光ダイオード50、有機発光ダイオード駆動TFT51、画素TFT52で構成されており、有機発光ダイオード駆動TFT51のゲート容量に書き込まれた信号電圧によって制御される駆動電流により、有機発光ダイオード50は駆動される。これによって本実施例では自発光可能な表示装置を実現しており、バックライトが不要であるために液晶表示装置よりも薄型化が可能である。なおここで用いた有機発光ダイオードは一般に知られている構造のものであり、その構造等に関しては、一例として公開特許広報/特開2001−159878等を参照することができる。また本実施例では画素の1列毎に、対応するDA変換回路45やフレームメモリ44を有している。表示領域42には画素41がマトリクス状に配置され、画素TFT52のゲートはゲート線GLを介して走査系回路46に、また画素TFT52の一端は信号線SLを介してDA変換回路45に接続されている。DA変換回路45にはデータ線DLを介してフレームメモリ44が接続されており、データ線DLは他端では信号系回路43に接続されている。

【0027】

ここで図7にフレームメモリ44の構成図を示す。メモリセルアレイ領域にはメモリセルMCがマトリクス状に配置されている。図7では図面の簡略化のために一部だけ記載してあるが、実際にはフレームメモリ44には、画素行数に対応する数分と、画素列数と階調ビット数に対応する数分のメモリセルMCが設けられている。メモリセルMCは、カルコゲナイド材料よりなる相変化可変抵抗記憶素子56と、メモリセルTFT55とからなる1トランジスタ+1記憶素子により構成される相変化メモリである。同一行のメモリセルMCは、ワード線WLを介してワード線走査回路に接続されている。記憶素子56の一端はデータ線DLに接続され、メモリセルTFT55のソース電極はコモン線CMに接続されている。上記のメモリセルTFT55、DA変換回路45、信号系回路43、走査系回路46、表示制御回路47は、多結晶Si−TFTを用いてガラス基板40上に設けられている。

【0028】

次に本実施例の動作を説明する。選択されたワード線WL上のTFT55が導通し、データ線DLから入力される表示データは、選択された所定の行のメモリセルMCの記憶素子56に、書き込み回路WCにより電気抵抗の形で書き込まれる。この時記憶素子56には、書き込み回路WCからパルス状の電流を流し,カルコゲナイド膜を結晶化、もしくは非晶質化させる。通常は高電圧短パルス(例えば20ns)によって高抵抗の非晶質状態にし、低電圧の長め(例えば50ns)のパルスによって低抵抗の結晶状態にすることにより、1ビットの表示データを書き込む。ここでパルス幅か電圧を同じにしても良い。以上がフレームメモリ44への書き込み動作である。

【0029】

次に、フレームメモリ44内にあるワード線走査回路が、ワード線WLを介してメモリセルMCを走査するのに従って、選択されたメモリセルMC内に電流経路が形成される。この時記憶素子56の抵抗値は、保持情報によって差があるので、データ線DLに出力される電圧は保持情報によって差が出る。この差を読み出し回路RCで判別することにより、保持された表示データが読み出され、順次データ線DLに出力される。この時表示データはDA変換回路45に入力され、DA変換回路45は表示データに対応する表示電圧信号を信号線SLに出力する。ここで走査系回路46はワード線走査回路と同期し、ゲート線GLを介して画素41を走査する。これによって選択された画素41の画素TFT52が開閉し、選択された有機発光ダイオード50を表示電圧信号に応じた階調で発光させる。このメモリは、電源が供給されなくても情報を保持できる不揮発性メモリであるので、表示データが変化しない間は、いわゆるリフレッシュと呼ばれる再書き込み動作を必要としない。これによって本有機EL表示装置は、外部から表示データの書込みが停止しても、表示を継続することが可能となる。

【0030】

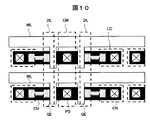

次に図8および図9を用いて本第3の実施例におけるフレームメモリ44の構造を、より詳しく説明する。図8は、フレームメモリのセルアレイの一部を示した平面構造図である。図9は、図8中にAA’と一点鎖線で示した、メモリTFTと記憶素子の部分の断面構造図である。メモリTFTは、多結晶Si層PSと、ワード線WLに接続されたゲート電極GEと、コンタクトホールCNからなり、ドレイン電極が局部配線LCにより、記憶素子を形成するカルコゲナイド膜CHに接続され、もう片方のソース電極は、隣のメモリセルのTFTと共通になっており、コモン線CMに接続される。記憶素子はワード線WL上に配置されており、片方の電極はデータ線DLに接続されている。可変抵抗記憶素子を形成するカルコゲナイド膜CHは、Te,Se,Sのうちの少なくとも一元素を含むカルコゲナイド材料よりなる膜厚100nm前後の膜である。本実施例の場合、カルコゲナイド材料はGe5Sb2Te8の組成のものとした。また、記憶素子56の抵抗として動作する部分の長さはほぼ2μm前後であり、抵抗値が結晶状態でほぼ10kΩ前後、非晶質状態でほぼ1MΩ前後であった。

TFTと記憶素子の製造方法が第1の実施例とほぼ同じであるため、断面構造も同じであり、第1の実施例と同じ効果を得ることができた。すなわち、自己整合プロセスを用いたため、リソグラフィ工程の合わせずれの影響を受けずに、記憶素子の抵抗値を決めることができた。また、カルコゲナイド膜CHをバリアメタル膜BMや、Si酸化膜27で覆う構造にしたため、Al材料の影響を受けない構造にすることができた。またカルコゲナイド膜CHは、Si窒化膜やPドープSi酸化膜のような可動イオンの影響を排除できる膜からなる、第1のパシベーション膜21と第2のパシベーション膜26、および第3のパシベーション膜30に、上下から挟まれた構造を有するため、可動イオンの影響を受けずに、安定した抵抗値を有する記憶素子を形成することができた。この結果、メモリセルTFTのオン抵抗がほぼ100kΩ前後であるのに対して、記憶素子において非晶質状態で1MΩ以上の抵抗になり、安定したメモリ動作を実現できた。

【0031】

以上のような構成および動作を採用することによって、周辺回路の動作を止めて画像データの入出力を停止しても、フレームメモリに保持された画像データに基づき、表示を続けることができる。また、このメモリは不揮発性メモリであるため、リフレッシュと呼ばれる情報の定期的な再書き込み動作が不要である。さらに本方式は、1つのメモリセルTFTと1つの記憶素子でデータ保持を行い、その記憶素子はワード線WLの領域上に形成するので、メモリセルアレイの面積を縮小できる。これらの発明の効果により、各色で階調を持ったフルカラーの高精細表示が可能となるだけでなく、消費電力を低減することや、周辺回路の面積縮小による、狭額縁の表示装置の実現が可能となる。

【0032】

以上に述べた本実施例においては、本発明の主旨を損なわない範囲でいくつもの変更が可能である。例えば、図8の平面構造とは異なる平面構造を、図10の平面図に示した。この例では、相変化可変抵抗記憶素子を、メモリセルTFTの多結晶Si領域PSの上に配置した。このような配置でも、メモリセルアレイ面積の縮小が可能であり、同様の効果が得られる。

また、相変化可変抵抗記憶素子56を形成する材料としては、本実施例のGe5Sb2Te8の組成を有する材料に限ったものではなく、Te,Se,Sのうちの少なくとも一元素を含むカルコゲナイド材料であればよい。GeTeとSb2Te3の混合組成のいずれか、またはそれに近い組成、であっても好ましい。他の例としては、ZnとTeを主成分とする材料がよい。ZnとTeを主成分とする材料の場合、GeまたはSbと、40原子%以上のTeと、20原子%以上50原子%以下の2b族、1b族、3aから7a族,および8族元素から選ばれた少なくとも一元素を含むものを用いることによって、好ましい特性が得られる。特にZnが好ましいが、Cdでもそれに近い効果が得られた。 ここで、40原子%以上のTeを含み、かつ、20原子%以上50原子%以下の2b族、1b族、3aから7a族,および8族元素から選ばれた少なくとも一元素を含むようにする理由は、高い結晶化温度と高い電気抵抗率を保つようにするためである。2b族、1b族、3aから7a族,および8族元素の代表としてZnを、GeまたはSbの代表としてGeを例にとって説明する。多くのZnを含む組成の場合には、結合力の強いZn-Teの非晶質ネットワーク中にGe-Teが取り込まれた形になり、安定な結晶系も互いに違うため、全体として高い結晶化温度を保つと考えられる。ここで、Geの添加で、イオン性が強いZnTeより共有結合性が増して非晶質ネットワーク(網目構造)が変形しにくくなり、一方、一旦結晶化が始まるとドミノ倒し式に高速結晶化される、と考えられる。Zn−Teに対して、ZnとTeの比率を保って添加するGeまたはSbの添加量を、5原子%以上40原子%以下とすると、添加量が多いほど融点、結晶化温度は低下するが、40原子%以下であれば、Ge5Sb2Te8よりも非晶質状態が安定であった。5原子%以上の添加によって、耐酸化性向上効果が得られた。添加量を25原子%以上35原子%以下とすれば、特に耐酸化性が高まった。このほか、第4の構成元素として、Au,Ag,Cu,のうちの少なくとも1者、周期律表の3族以上の元素が10原子%以下含まれても良い。

【0033】

また、これらの材料よりなるカルコゲナイド膜CHの少なくとも一部に、電極間を横切るように、すなわち導電パスを横切って遮断するように酸化物、窒化物、硫化物、炭化物などの誘電体とカルコゲナイド材料との混合膜を形成することにより、高い抵抗値を得ることも可能である。この混合膜領域は、どちらかの電極に接して設けるのが好ましいが、両電極に接しない状態でも高い抵抗値を得ることが可能である。どちらかの電極に接して設ける場合は、マイナス電極に接して設けられるのが、メモリ動作の安定性の点で最も好ましい。この場合、図9のカルコゲナイド膜CHと、バリアメタル膜BMが接する部分に、上記混合膜領域を設けることで実現できる。

【0034】

また、図9ではガラス基板20を用いたが、これを石英基板や透明プラスチック基板等透明絶縁基板に変更することも可能であるし、図6の表示部42を液晶表示方式に変えることで、本発明を液晶表示装置に実施する事も可能である。あるいはTFTに関しても、本実施例ではメモリセルTFTにnチャネル型TFTを用いたが、これをpチャネル型TFTに変更することも可能であるし、記憶素子の抵抗値をさらに大きくした場合には、メモリTFTにアモルファスSi−TFTを用いることも可能である。また、TFTの構造としては本実施例に限ったものではなく、例えばゲート電極GEが多結晶Si領域PSの下にある構造のTFTでも、本発明の効果を得られることはいうまでもない。さらには、本実施例では各回路を多結晶Si−TFT回路で構成したが、これらの周辺回路の一部分を単結晶LSI(Large Scale Integration)回路で構成して実装することも、本発明の範囲内で可能である。

【0035】

さらに、今回は表示信号を6ビットとしたが、例えばフレームメモリ容量を増加することで、より多階調の表示装置に対応することも可能である。メモリセルにおいては、記憶素子の材料の結晶化方向に、多値の抵抗値を取らせることも可能であり、表示の階調ビット数に対応させることもできる。その場合は、結晶化パルスの電圧をより小さな電圧刻みで変化させて、対応する抵抗値を取らせればよい。

(第4の実施例)

以下に図11〜図13を用いて、本発明の第4の実施例を説明する。

本実施例は、第3の実施例と同じフレームメモリを有する有機EL表示装置において、メモリセルの平面構造、断面構造、および製造方法を変えた実施例である。図6の表示装置構成や図7のフレームメモリ構成など、メモリセル以外の構造は第3の実施例と同じである。図11はメモリセルアレイの平面構造の一部を示す平面図であり、図12は図11のAA’と一点鎖線で示した部分の、メモリセルTFTと記憶素子の製造方法と断面構造を説明する、製造工程断面図である。第4の実施例では、カルコゲナイド膜CHよりなる記憶素子が、コンタクト開口部CCの中に形成されているため、1ビットのメモリセルの面積は、1つのメモリセルTFTの面積と同じであり、メモリセルアレイの面積をさらに縮小できた。

【0036】

本実施例の製造方法を説明すると以下の通りである。まず図12(a)に示したように、ガラス基板20に、Si窒化膜やPドープSi酸化膜からなる第1のパシベーション膜21とSi酸化膜22とアモルファスSi膜をプラズマCVD法により堆積し、連続発振固体レーザをパルス変調したレーザアニール法を用いて、このアモルファスSi膜を結晶化することにより、結晶性の優れた多結晶Si膜PSを形成した。ここで、多結晶Si膜PSを形成する他の方法として、固相成長法によりアモルファスSi膜を結晶化したり、低温CVD法で直接多結晶Si膜を、Si酸化膜22の上に堆積することもできる。その後、選択的にこの多結晶Si膜PSをエッチングすることによりTFT形成領域に多結晶Si膜PSを島状に残し、ゲートSi酸化膜23をプラズマCVD法により堆積し、例えばMoを主材料としたゲート膜を堆積、パターニングし、ゲート電極GEとワード線WLを形成した。

【0037】

次に図12(b)に示したように、イオン打ち込み法やイオンドーピング法などによる不純物イオンの導入と活性化のための熱処理を行い、ソース拡散層24およびドレイン拡散層25を形成した後、Si窒化膜やPドープSi酸化膜などを含んだ第2のパシベーション膜26をCVD法により堆積した。なおここでは、紙面の都合でn型チャネルのメモリTFTの断面図のみ示しているが、実際にはその他の周辺回路に必要に応じて、p型チャネルTFTやLDD構造のTFTを形成した。その後リソグラフィ法により、記憶素子を形成する領域CCを開口し、例えばZnとTeを主成分とするカルコゲナイド材料からなる、膜厚200nm前後のカルコゲナイド膜CHを、例えば室温や室温に近い低温のスパッタリング法により、開口部CCの多結晶Si上にバリアメタルを介さず直接堆積した。このようにバリアメタルを介さないことで、バリアメタルよりなる寄生低抵抗がカルコゲナイド膜に並列に付加されないので、記憶素子の抵抗値をより制御性よく形成することができた。ここで必要に応じて、例えばレーザアニールやRTAにより、カルコゲナイド膜CHを結晶化する。さらにこれらの熱処理は、上記不純物イオン活性化のための熱処理を兼ねることも可能である。

【0038】

次に図12(c)に示したように、リソグラフィ法を用いて、選択的にカルコゲナイド膜CHをエッチングし、記憶素子を形成する領域にカルコゲナイド膜CHを残し、続いてリソグラフィ法によりTFT用コンタクトホールCNを開口した。

【0039】

次に図12(d)に示したように、例えばMoを主成分としたバリアメタル膜BMと、データ線DLやコモン線CMに用いるAl膜、あるいは例えばAlとTiの積層膜のようなAl膜を主成分とした金属積層膜を堆積し、パターニングした。このバリアメタル膜BMは、その他の材料、例えばWやTiNなどでも可能である。以上の製造方法ため、記憶素子の抵抗長や断面積がカルコゲナイド膜厚と記憶素子用コンタクト開口部CCの開口面積で決定され、リソグラフィの合わせずれの影響を受けることがなく、自己整合的に抵抗値が決定された。ここで、非晶質化する時のカルコゲナイド膜の蒸発や変形を防ぐために、膜厚が50nm以上のCr2O3膜や他の誘電体の膜を、スパッタリング法により堆積することも可能である。

次に図12(e)に示したように、Si窒化膜やPドープSi酸化膜からなる第3のパシベーション膜30と、例えば有機材料からなる低誘電率の第4のパシベーション膜31を堆積した。その後、水素アニールやプラズマ処理による水素化処理を行った。

最後に、表示領域でビアホールを開口し(図12には示さず)、透明電極膜を堆積し、所望の形状になるように透明電極を形成し(図12には示さず)、配線層と透明電極を接続した。その後有機発光ダイオード形成工程に進み、有機EL表示装置を完成した

以上の製造方法によると、リソグラフィ工程の合わせずれの影響を受けずに、自己整合的に制御性よく記憶素子の抵抗値を決めることができた。また、カルコゲナイド膜CHをバリアメタル膜BMで覆ったため、Al材料の影響を受けない構造にすることができた。またカルコゲナイド膜CHは、Si窒化膜やPドープSi酸化膜のような可動イオンの影響を排除できる膜からなる、第1のパシベーション膜21と第2のパシベーション膜26、および第3のパシベーション膜30に、上下左右から囲まれた構造を有するため、可動イオンの影響を受けずに、安定した抵抗値を有する記憶素子を形成することができた。この結果、記憶素子において非晶質状態で1MΩ以上の抵抗を形成できた。一方で本実施例においては、結晶性の優れた多結晶Si膜PSを用いてメモリセルTFTを形成したため、メモリセルTFTのオン抵抗をほぼ20kΩ前後にまで下げることができた。このように、記憶素子の抵抗とメモリセルTFTのオン抵抗の差を、安定して大きくできたため、より安定したメモリ動作を実現できた。

【0040】

以上のような構成および動作を採用することによって、周辺回路の動作を止めて画像データの入出力を停止しても、フレームメモリに保持された画像データに基づき、表示を続けることができる。また、このメモリは不揮発性メモリであるため、リフレッシュと呼ばれる情報の定期的な再書き込み動作が不要である。さらに本方式は、1つのメモリセルTFTと1つの記憶素子でデータ保持を行い、その面積が1つのTFTの面積と同じであるので、メモリセルアレイの面積を縮小できる。これらの発明の効果により、各色で階調を持ったフルカラーの高精細表示が可能となるだけでなく、消費電力を低減することや、周辺回路の面積縮小による、狭額縁の表示装置の実現が可能となる。

【0041】

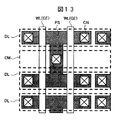

以上に述べた本実施例においては、本発明の主旨を損なわない範囲でいくつもの変更が可能である。例えば、図11の平面構造とは異なる平面構造を、図13の平面図に示した。この例では、ワード線WLとゲート電極GEを同一金属膜で形成し、データ線DLとコモン線CMを、Alを主成分とした配線層で形成した。このような配置でも、メモリセルアレイ面積の縮小が可能であり、同様の効果が得られる。

【0042】

また、相変化可変抵抗記憶素子56を形成する材料としては、本実施例のZnとTeを主成分とする材料に限ったものではなく、Te,Se,Sのうちの少なくとも一元素を含むカルコゲナイド材料であればよい。例としては、Ge5Sb2Te8の組成を有する材料でもよい。また、これらの材料よりなるカルコゲナイド膜CHの少なくとも一部に、電極間を横切るように、すなわち導電パスを横切って遮断するように酸化物、窒化物、硫化物、炭化物などの誘電体とカルコゲナイド材料との混合膜を形成することにより、高い抵抗値を得ることも可能である。この混合膜領域は、どちらかの電極に接して設けるのが好ましいが、両電極に接しない状態でも高い抵抗値を得ることが可能である。どちらかの電極に接して設ける場合は、マイナス電極に接して設けられるのが、メモリ動作の安定性の点で最も好ましい。この場合、図12(e)のカルコゲナイド膜CHと、バリアメタル膜BMが接する部分に、上記混合膜領域を設けることで実現できる。

【0043】

また、図12ではガラス基板20を用いたが、これを石英基板や透明プラスチック基板等透明絶縁基板に変更することも可能であるし、図6の表示部42を液晶表示方式に変えることで、本発明を液晶表示装置に実施する事も可能である。あるいはTFTに関しても、本実施例ではメモリセルTFTにnチャネル型TFTを用いたが、これをpチャネル型TFTに変更することも可能であるし、記憶素子の抵抗値をさらに大きくした場合には、メモリTFTにアモルファスSi−TFTを用いることも可能である。また、TFTの構造としては本実施例に限ったものではなく、例えばゲート電極GEが多結晶Si領域PSの下にある構造のTFTでも、本発明の効果を得られることはいうまでもない。さらには、本実施例では各回路を多結晶Si−TFT回路で構成したが、これらの周辺回路の一部分を単結晶LSI回路で構成して実装することも本発明の範囲内で可能である。

【0044】

さらに、今回は表示信号を6ビットとしたが、例えばフレームメモリ容量を増加することで、より多階調の表示装置に対応することも可能である。メモリセルにおいては、記憶素子の材料の結晶化方向に、多値の抵抗値を取らせることも可能であり、表示の階調ビット数に対応させることもできる。その場合は、結晶化パルスの電圧をより小さな電圧刻みで変化させて、対応する抵抗値を取らせればよい。

(第5の実施例)

以下に図14を用いて、本発明における第5の実施例に関して説明する。

第5の実施例は、本発明を携帯電話やデジタルスチルカメラに適用した例であり、図14は本装置に用いられている表示装置の構成図である。この表示装置は、対角長がほぼ2〜3インチ前後、精細度がQVGA(320×240画素)前後の表示部61を有する各色6ビットの面積階調部分透過型液晶表示装置であり、不揮発性相変化メモリよりなる画素メモリを兼ね備えている。表示制御回路64には、画像データの入力回路、電源変換回路、レベルシフト回路、タイミング制御回路など、画像表示に必要な回路機能が含まれており、ここから出力されたデータが、シフトレジスタ回路やバッファ回路などを含んだ信号系回路62および走査系回路63に送られ、画像が表示される。これらの回路は、多結晶Si−TFTにより構成されており、TFTと相変化記憶素子は同一ガラス基板60に製造されたため、表示部周辺の額縁幅を狭くすることができ、デザイン的に優れた表示装置を提供できた。なおこれらの周辺回路の一部は、LSIにより構成することも可能である。

【0045】

インターネットや地上波デジタル放送などから配信された動画像の観賞や、テレビ電話などの機能を使用するときは、主にバックライトを用いた透過モードで表示装置を使用するが、本表示装置は開口率を大きくとれるため、バックライトの消費電力を低減することができた。また、待ち受け状態や同じ静止画像を長時間見る時は、主に反射モードで表示装置を使用する。この時は、周辺回路の動作を止めて画像データの出力を停止しても、画素メモリの情報により表示を持続できるため、消費電力を2mW前後、あるいはそれ以下にまで大幅に下げながら、各色6ビット階調のフルカラー画像をみることができた。

(第6の実施例)

以下に図15を用いて、本発明における第6の実施例に関して説明する。

第6の実施例は、本発明を携帯情報サービス端末に適用した例であり、図15は本端末に用いられている表示装置の構成図である。表示装置は、対角長が5〜10インチ前後、精細度がSVGA(800×600画素)〜UXGA(1600×1200)前後、各色6ビット階調の軽量薄型有機EL表示装置であり、不揮発性相変化メモリよりなるフレームメモリを、信号系回路72の中に兼ね備えている。それ以外にも、無線通信回路RF、インターフェース回路IF、マイクロプロセッサMP、汎用メモリMM、アンテナAN、外光センサ回路LS、太陽電池などを含んだエネルギ制御回路EC、個人認証用センサ回路FP等が搭載されており、高機能を内蔵した表示装置を提供している。これらの回路は、多結晶Si−TFTとLSIにより構成されており、TFT、相変化記憶素子、アンテナ、各センサ、太陽電池は同一ガラス基板70に600℃以下の低温プロセスで製造され、またLSIはチップを直接ガラス基板に実装したため、表示部周辺の額縁幅を狭くすることができ、デザイン的に優れた表示装置を提供できた。また本実施例では、汎用メモリMMをLSIにより構成したが、例えばフレームメモリに用いた不揮発性相変化メモリにより、汎用メモリを構成することも可能である。このように、TFT回路、相変化記憶素子、アンテナ、センサ、太陽電池などを、同一ガラス基板70に製造し、搭載するLSIの数を極力減らしたことにより、軽量薄型でも耐衝撃性に優れた表示装置を提供することができた。

【0046】

画像データの表示方法を、以下に簡単に説明する。無線通信回路RFには、低雑音増幅回路、高出力増幅回路、インダクタ、容量などが含まれ、外部から圧縮された画像データ等が無線データとして入力する。この画像データは、インターフェース回路IFを経て、マイクロプロセッサMPに送られる。ここで画像データに必要に応じた処理を加えた後、電源変換回路、レベルシフト回路、タイミング制御回路など、画像表示に必要な回路機能が含まれた表示制御回路74と、フレームメモリを有する信号系回路72、および走査系回路73に送られ、画像が表示される。

【0047】

この端末により、インターネットや配信サービススポットなどから提供される画像の観賞や、画像情報を利用することができる。特に写真やニュース、各種案内、ショッピング情報、地図情報、地域情報などの静止画像や文字情報を利用する場合は、周辺回路やマイクロプロセッサMP、無線通信回路RFなどの動作を停止しても、フレームメモリに保持された画像情報により表示を持続できるため、消費電力を下げながら、各色6ビット階調のフルカラー画像をみることができる。また、外光センサ回路LSにより周囲の明るさを感知し、表示輝度を最適に制御することにより、表示のための消費電力を削減することができる。さらに、個人認証用センサ回路FPにより使用者を特定することにより、各種予約やショッピング、銀行などのサービスを利用することができる。また、本端末の表示部の少なくとも一部にタッチパネルの機能を持たせることにより、キーボードを表示してペン、指などによってタッチ入力を行うことができる。この場合、キーボードの表示は、少なくともキー配列またはキーボードの大きさ、または片手入力用か両手入力用かの2種類以上を用意しており、ユーザーの好みによって選ぶことができる。なお本実施例では、有機EL表示装置を例にとったが、透過型液晶表示装置など他の表示装置でも、本発明の効果を得られることはいうまでもない。

【0048】

【発明の効果】

本発明によれば、画像表示装置における画素数の増大と表示領域以外の周辺領域面積の縮小と低消費電力化を両立させることができる。また、多ビットの画像データを表示することも可能である。

【図面の簡単な説明】

【図1】第1の実施例である表示装置の構成図。

【図2】第1の実施例である表示装置の画素の平面構造図。

【図3】第1の実施例である表示装置の画素の製造工程断面図。

【図4】第2の実施例である表示装置の画素の平面構造図。

【図5】第2の実施例である表示装置の画素の平面構造図。

【図6】第3の実施例である表示装置の構成図。

【図7】第3の実施例である表示装置の記憶装置の構成図。

【図8】第3の実施例である表示装置の記憶装置の平面構造図。

【図9】第3の実施例である表示装置の記憶装置の断面構造図。

【図10】第3の実施例である表示装置の記憶装置の平面構造図。

【図11】第4の実施例である表示装置の記憶装置の平面構造図。

【図12】第4の実施例である表示装置の記憶装置の製造工程断面図。

【図13】第4の実施例である表示装置の記憶装置の平面構造図。

【図14】第5の実施例である表示装置の構成図。

【図15】第6の実施例である表示装置の構成図。

【図16】従来技術の表示装置の構成図。

【図17】従来技術の表示装置の構成図。

【図18】従来技術の表示装置の構成図。

【符号の説明】

1…表示基板、2…画素、3…表示部、4…信号系回路、5…走査系回路、6…表示制御回路、7…書き込み回路、8…メモリTFT、9…相変化可変抵抗、10…液晶、11…キャップSi酸化膜残存領域、12…カルコゲナイド膜エッチング領域、20…ガラス基板、21…第1のパシベーション膜、22…Si酸化膜、23…ゲートSi酸化膜、24…ソース拡散層、25…ドレイン拡散層、26…第2のパシベーション膜、27…キャップSi酸化膜、28…レジスト膜、29…カルコゲナイド膜エッチング領域、30…第3のパシベーション膜、31…第4のパシベーション膜、40…表示基板、41…画素、42…表示部、43…信号系回路、44…フレームメモリ、45…DA変換回路、46…走査系回路、47…表示制御回路、50…有機発光ダイオード、51…有機発光ダイオード駆動TFT、52…画素TFT、55…メモリセルTFT、56…相変化可変抵抗、60…表示基板、61…表示部、62…信号系回路、63…走査系回路、64…表示制御回路、70…表示基板、71…表示部、72…信号系回路、73…走査系回路、74…表示制御回路、100…表示部、101…信号系回路、102…走査系回路、103…不揮発性半導体メモリ、104…画素、105…信号線、106…ゲート線、110…表示部、111…信号系回路、112…フレームメモリ、113…DA変換回路、114…走査系回路、115…画素、116…信号線、117…ゲート線、120…表示部、121…信号系回路、122…走査系回路、123…画素、124…正信号線、125…負信号線、126…ゲート線、127…交流駆動信号線。

Claims (12)

- マトリクス状に配置された画素と、

走査系回路と、

信号系回路と、

書き込み回路と、

信号線と、

ゲート線と、

画素線を有し、

前記各画素は、メモリTFTと、カルコゲナイド膜から成る相変化記憶素子と、表示部とを有し、

前記走査系回路と前記メモリTFTのゲートの間は、前記ゲート線を介して接続され、

前記走査系回路と前記メモリTFTのソース−ドレイン経路の一端は、前記画素線を介して接続され、

前記メモリTFTのソース−ドレイン経路の他端は、前記表示部の一端に接続され、

前記信号系回路と前記相変化記憶素子の一端は、前記書き込み回路と前記信号線を介して接続され、

前記相変化記憶素子の他端は、前記表示部の一端に接続され、

前記相変化記憶素子が、前記ゲート線、および前記画素線の領域上にまたがり、かつその平面形状が折り返して配置されることを特徴とする画像表示装置。 - 前記各画素が、表示データを保持する機能を有することを特徴とする請求項1に記載の画像表示装置。

- 前記表示部が液晶により構成されることを特徴とする請求項1に記載の画像表示装置。

- 前記表示部が有機発光ダイオードにより構成されることを特徴とする請求項1に記載の画像表示装置。

- マトリクス状に配置された画素と、

走査系回路と、

信号系回路と、

書き込み回路と、

信号線と、

ゲート線と、

画素線を有し、

前記各画素は、メモリTFTと、カルコゲナイド膜から成る相変化記憶素子と、表示部とを有し、

前記走査系回路と前記メモリTFTのゲートの間は、前記ゲート線を介して接続され、

前記走査系回路と前記メモリTFTのソース−ドレイン経路の一端は、前記画素線を介して接続され、

前記メモリTFTのソース−ドレイン経路の他端は、前記表示部の一端に接続され、

前記信号系回路と前記相変化記憶素子の一端は、前記書き込み回路と前記信号線を介して接続され、

前記相変化記憶素子の他端は、前記表示部の一端に接続され、

前記相変化記憶素子が、ブラックマトリクス、前記ゲート線、前記画素線の少なくとも何れか一つの領域上、且つ、前記各画素の周辺に沿って配置されることを特徴とする画像表示装置。 - 前記相変化記憶素子が、Te、Se、Sのうちの、少なくとも1元素を含むカルコゲナイド材料よりなることを特徴とする請求項5に記載の画像表示装置。

- 前記相変化記憶素子が、Al以外の材料により覆われ、Al材料と直接接することがないことを特徴とする請求項5に記載の画像表示装置。

- 前記相変化記憶素子が、可動イオンの影響を抑制できる複数の保護膜により、上下から保護されることを特徴とする請求項5に記載の画像表示装置。

- 前記各画素が、表示データを保持する機能を有することを特徴とする請求項5に記載の画像表示装置。

- 前記表示部が液晶により構成されることを特徴とする請求項5に記載の画像表示装置。

- 前記表示部が有機発光ダイオードにより構成されることを特徴とする請求項5に記載の画像表示装置。

- 前記メモリTFTの導通時の抵抗が10kΩから1000kΩの間であり、前記相変化記憶素子の高抵抗状態が1000kΩ以上であることを特徴とする請求項5に記載の画像表示装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003174235A JP4545397B2 (ja) | 2003-06-19 | 2003-06-19 | 画像表示装置 |

| TW092132936A TWI284298B (en) | 2003-06-19 | 2003-11-24 | Image display device |

| US10/772,447 US7247357B2 (en) | 2003-06-19 | 2004-02-06 | Image display device |

| KR1020040008313A KR100979596B1 (ko) | 2003-06-19 | 2004-02-09 | 화상 표시 장치 |

| CN2004100055246A CN1573844B (zh) | 2003-06-19 | 2004-02-11 | 图像显示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003174235A JP4545397B2 (ja) | 2003-06-19 | 2003-06-19 | 画像表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005010448A JP2005010448A (ja) | 2005-01-13 |

| JP4545397B2 true JP4545397B2 (ja) | 2010-09-15 |

Family

ID=33516198

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003174235A Expired - Fee Related JP4545397B2 (ja) | 2003-06-19 | 2003-06-19 | 画像表示装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7247357B2 (ja) |

| JP (1) | JP4545397B2 (ja) |

| KR (1) | KR100979596B1 (ja) |

| CN (1) | CN1573844B (ja) |

| TW (1) | TWI284298B (ja) |

Families Citing this family (34)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4529493B2 (ja) * | 2004-03-12 | 2010-08-25 | 株式会社日立製作所 | 半導体装置 |

| DE102004029436B4 (de) * | 2004-06-18 | 2009-03-05 | Qimonda Ag | Verfahren zum Herstellen eines Festkörperelektrolytmaterialbereichs |

| KR101219750B1 (ko) * | 2004-12-07 | 2013-01-08 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제작방법 |

| JP2006210718A (ja) * | 2005-01-28 | 2006-08-10 | Renesas Technology Corp | 半導体装置の製造方法および半導体装置 |

| JP4843259B2 (ja) * | 2005-06-10 | 2011-12-21 | シャープ株式会社 | 可変抵抗素子の製造方法 |

| US8044882B1 (en) * | 2005-06-25 | 2011-10-25 | Nongqiang Fan | Method of driving active matrix displays |

| US7426128B2 (en) * | 2005-07-11 | 2008-09-16 | Sandisk 3D Llc | Switchable resistive memory with opposite polarity write pulses |

| JP4425878B2 (ja) | 2005-10-31 | 2010-03-03 | 韓國電子通信研究院 | カルコゲナイド系元素を含む光伝導層を有するフォト薄膜トランジスタ及びこれを用いたイメージセンサの単位セル |

| JP5084134B2 (ja) | 2005-11-21 | 2012-11-28 | 日本電気株式会社 | 表示装置及びこれらを用いた機器 |

| EP1792563A1 (de) * | 2005-12-02 | 2007-06-06 | F.Hoffmann-La Roche Ag | Analysesystem mit organischer Leuchtdiodenanzeige |

| JP2007225873A (ja) * | 2006-02-23 | 2007-09-06 | Hitachi Displays Ltd | 画像表示装置 |

| US7605410B2 (en) * | 2006-02-23 | 2009-10-20 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP2007294592A (ja) * | 2006-04-24 | 2007-11-08 | Sony Corp | 記憶装置の駆動方法 |

| CN101663770A (zh) * | 2007-04-20 | 2010-03-03 | Nxp股份有限公司 | 包含可转换结构的电子装置 |

| US7960916B2 (en) * | 2007-05-16 | 2011-06-14 | Advanced Lcd Technologies Development Center Co., Ltd. | Display device and electronic device using thin-film transistors formed on semiconductor thin films which are crystallized on insulating substrates |

| JP2008310298A (ja) * | 2007-05-16 | 2008-12-25 | Advanced Lcd Technologies Development Center Co Ltd | 表示装置および電子装置 |

| US20100177072A1 (en) * | 2007-06-14 | 2010-07-15 | Kazuyoshi Kawabe | Active matrix display device |

| CN101527167B (zh) * | 2008-02-01 | 2012-08-15 | 索尼株式会社 | 显示装置 |

| JP4596070B2 (ja) * | 2008-02-01 | 2010-12-08 | ソニー株式会社 | メモリ素子及びメモリ素子の製造方法、並びに表示装置及び表示装置の製造方法 |

| KR20090095313A (ko) * | 2008-03-05 | 2009-09-09 | 삼성전자주식회사 | 저항성 메모리 소자의 프로그래밍 방법 |

| JP2010054691A (ja) * | 2008-08-27 | 2010-03-11 | Renesas Technology Corp | 半導体装置 |

| JP2010055696A (ja) * | 2008-08-28 | 2010-03-11 | Elpida Memory Inc | 半導体記憶装置 |

| JP4751432B2 (ja) | 2008-09-26 | 2011-08-17 | シャープ株式会社 | 半導体記憶装置 |

| WO2011081011A1 (en) * | 2009-12-28 | 2011-07-07 | Semiconductor Energy Laboratory Co., Ltd. | Liquid crystal display device and manufacturing method thereof |

| KR101952733B1 (ko) * | 2010-11-05 | 2019-02-27 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 |

| CN102544050A (zh) * | 2011-12-28 | 2012-07-04 | 上海中科高等研究院 | 电荷存储单元以及图像传感器像素电路 |

| EP2860720A1 (en) * | 2013-10-10 | 2015-04-15 | Nederlandse Organisatie voor toegepast- natuurwetenschappelijk onderzoek TNO | Electro-optical unit for a picture element that can be programmed by electromagnetic radiation |

| JP6583812B2 (ja) * | 2015-06-24 | 2019-10-02 | 国立研究開発法人物質・材料研究機構 | 多層構成の薄膜トランジスタの製造方法 |

| US20170365209A1 (en) * | 2016-06-17 | 2017-12-21 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| US10650727B2 (en) * | 2016-10-04 | 2020-05-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, display device, and electronic device |

| CN106782311B (zh) * | 2017-03-03 | 2019-08-09 | 京东方科技集团股份有限公司 | 一种像素电路及其驱动方法、显示面板 |

| CN107706154B (zh) * | 2017-09-28 | 2020-06-30 | 京东方科技集团股份有限公司 | 一种存储元件、存储装置、制作方法及驱动方法 |

| FR3140470B1 (fr) * | 2022-09-29 | 2026-01-09 | Aledia | Dispositif optoélectronique |

| US20240402006A1 (en) * | 2023-06-02 | 2024-12-05 | International Business Machines Corporation | Flexible ultraviolet sensor |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0034796B1 (en) * | 1980-02-22 | 1987-09-16 | Kabushiki Kaisha Toshiba | Liquid crystal display device |

| JPS56117275A (en) * | 1980-02-22 | 1981-09-14 | Tokyo Shibaura Electric Co | Image display |

| US4868616A (en) * | 1986-12-11 | 1989-09-19 | Energy Conversion Devices, Inc. | Amorphous electronic matrix array for liquid crystal display |

| US5262987A (en) * | 1988-11-17 | 1993-11-16 | Seiko Instruments Inc. | Floating gate semiconductor nonvolatile memory having impurity doped regions for low voltage operation |

| JPH02138728U (ja) * | 1989-04-21 | 1990-11-20 | ||

| US5296716A (en) * | 1991-01-18 | 1994-03-22 | Energy Conversion Devices, Inc. | Electrically erasable, directly overwritable, multibit single cell memory elements and arrays fabricated therefrom |

| US5335219A (en) * | 1991-01-18 | 1994-08-02 | Ovshinsky Stanford R | Homogeneous composition of microcrystalline semiconductor material, semiconductor devices and directly overwritable memory elements fabricated therefrom, and arrays fabricated from the memory elements |

| JP2775040B2 (ja) * | 1991-10-29 | 1998-07-09 | 株式会社 半導体エネルギー研究所 | 電気光学表示装置およびその駆動方法 |

| US5821911A (en) * | 1993-09-07 | 1998-10-13 | Motorola | Miniature virtual image color display |

| US5738731A (en) * | 1993-11-19 | 1998-04-14 | Mega Chips Corporation | Photovoltaic device |

| US5523970A (en) * | 1993-12-29 | 1996-06-04 | International Business Machines Incorporated | Non-volatile memory utilizing a thin film, floating gate, amorphous transistor |

| US5694146A (en) * | 1994-10-14 | 1997-12-02 | Energy Conversion Devices, Inc. | Active matrix LCD array employing thin film chalcogenide threshold switches to isolate individual pixels |

| JP3630489B2 (ja) | 1995-02-16 | 2005-03-16 | 株式会社東芝 | 液晶表示装置 |

| US6717179B1 (en) * | 1997-08-19 | 2004-04-06 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and semiconductor display device |

| JP3724930B2 (ja) | 1997-09-12 | 2005-12-07 | 株式会社日立製作所 | 画像表示装置、その駆動方法及びこれを用いたデータ処理システム |

| JPH11204742A (ja) * | 1998-01-20 | 1999-07-30 | Sony Corp | メモリ及び情報機器 |

| JP2000252373A (ja) | 1999-03-04 | 2000-09-14 | Toshiba Corp | 不揮発性半導体メモリ、不揮発性半導体メモリを備えた表示装置及びその製造方法 |

| JP2001326289A (ja) | 2000-03-08 | 2001-11-22 | Semiconductor Energy Lab Co Ltd | 不揮発性メモリおよび半導体装置 |

| US6700813B2 (en) * | 2001-04-03 | 2004-03-02 | Canon Kabushiki Kaisha | Magnetic memory and driving method therefor |

| JP4809545B2 (ja) * | 2001-05-31 | 2011-11-09 | 株式会社半導体エネルギー研究所 | 半導体不揮発性メモリ及び電子機器 |

| US6549447B1 (en) * | 2001-10-31 | 2003-04-15 | Peter Fricke | Memory cell structure |

| US6703252B2 (en) * | 2002-01-31 | 2004-03-09 | Hewlett-Packard Development Company, L.P. | Method of manufacturing an emitter |

-

2003

- 2003-06-19 JP JP2003174235A patent/JP4545397B2/ja not_active Expired - Fee Related

- 2003-11-24 TW TW092132936A patent/TWI284298B/zh not_active IP Right Cessation

-

2004

- 2004-02-06 US US10/772,447 patent/US7247357B2/en not_active Expired - Fee Related

- 2004-02-09 KR KR1020040008313A patent/KR100979596B1/ko not_active Expired - Fee Related

- 2004-02-11 CN CN2004100055246A patent/CN1573844B/zh not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| CN1573844A (zh) | 2005-02-02 |

| CN1573844B (zh) | 2011-11-30 |

| TWI284298B (en) | 2007-07-21 |

| KR20040110074A (ko) | 2004-12-29 |

| JP2005010448A (ja) | 2005-01-13 |

| US20040258866A1 (en) | 2004-12-23 |

| US7247357B2 (en) | 2007-07-24 |

| KR100979596B1 (ko) | 2010-09-01 |

| TW200500977A (en) | 2005-01-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4545397B2 (ja) | 画像表示装置 | |

| JP6685369B2 (ja) | 表示装置 | |

| US7342615B2 (en) | Image display and manufacturing method of the same | |

| US20090032794A1 (en) | Phase change memory device and fabrication method thereof | |

| US20060202245A1 (en) | Phase-change memory device and manufacturing process thereof | |

| US8174023B2 (en) | Method of fabricating memory cell | |

| CN109087920B (zh) | Tft阵列基底、包括其的显示装置及其制造方法 | |

| CN101123260A (zh) | 显示装置及显示装置的制造方法 | |

| WO2010084725A1 (ja) | 半導体装置およびその製造方法ならびに表示装置 | |

| US8013325B2 (en) | Thin film transistor, organic light emitting device including thin film transistor, and manufacturing method thereof | |

| US7851801B2 (en) | Pixel structure | |

| JP5360756B2 (ja) | 有機電界発光表示装置及びその製造方法 | |

| US6864529B2 (en) | Thin film transistor memory device | |

| US7298355B2 (en) | Display device | |

| US7888679B2 (en) | Display device with rapidly crystallizing light blocking layer and method of manuacturing the same | |

| JP2004179610A (ja) | 薄膜トランジスタアレー及び駆動回路の構造 | |

| US7952098B2 (en) | Active matrix electronic array device | |

| US8816437B2 (en) | Semiconductor device and method for manufacturing same | |

| JP2000252373A (ja) | 不揮発性半導体メモリ、不揮発性半導体メモリを備えた表示装置及びその製造方法 | |

| US12009370B2 (en) | Display device | |

| JP2004151275A (ja) | 画像表示装置 | |

| WO2007138754A1 (ja) | 半導体装置、その製造方法、及び、表示装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20050310 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20060511 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060511 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060607 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20080229 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080403 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090707 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090904 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100202 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100329 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100610 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100629 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100630 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4545397 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 Free format text: JAPANESE INTERMEDIATE CODE: R313121 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130709 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |