JP4264635B2 - データ再生方法およびデータ再生装置 - Google Patents

データ再生方法およびデータ再生装置 Download PDFInfo

- Publication number

- JP4264635B2 JP4264635B2 JP2003101298A JP2003101298A JP4264635B2 JP 4264635 B2 JP4264635 B2 JP 4264635B2 JP 2003101298 A JP2003101298 A JP 2003101298A JP 2003101298 A JP2003101298 A JP 2003101298A JP 4264635 B2 JP4264635 B2 JP 4264635B2

- Authority

- JP

- Japan

- Prior art keywords

- sync

- block

- sync block

- blocks

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Television Signal Processing For Recording (AREA)

- Signal Processing For Digital Recording And Reproducing (AREA)

Description

【発明の属する技術分野】

この発明は、例えばデジタルビデオテープレコーダ等に適用して好適なデータ再生方法およびデータ再生装置に関する。

【0002】

詳しくは、この発明は、二次元ブロック単位で圧縮符号化されたビデオデータをパッキングする複数個のシンクブロックとして、変速再生時に単独で再生したとき、使用できるシンクブロックを第1のシンクブロックとし、使用できないシンクブロックを第2のシンクブロックとしたとき、同一の二次元ブロックに係る第1および第2のシンクブロックが順次連続して記録されてなるテープの傾斜トラックを再生ヘッドで走査して当該第1および第2のシンクブロックを再生することで、変速再生時に同一ブロックに係る第1、第2のシンクブロックをペアで容易に再生できるようにしたデータ再生方法およびデータ再生装置に係るものである。

【0003】

またこの発明は、変速再生時には、再生された第1のシンクブロックについては、付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第1のシンクブロックに対応するメモリのアドレス位置に当該第1のシンクブロックを書き込み、再生された第2のシンクブロックについては、直前に再生された第1のシンクブロックがエラー訂正でき、該第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第2のシンクブロックに対応するメモリのアドレス位置に当該第2のシンクブロックを書き込むものである。

【0004】

【従来の技術】

従来、ビデオデータを二次元ブロック単位で、例えばDCT(Discrete Cosine Transform)を用いた圧縮符号化を行い、各ブロックの圧縮符号化データをそれぞれ一個のシンクブロックにパッキングし、テープの傾斜トラックにシンクブロックを順次記録し、再生時には当該テープの傾斜トラックからシンクブロックを順次再生し、デパッキングの処理によって各ブロックの圧縮符号化データを得、データ伸長処理を行ってビデオデータを得る記録再生装置が提案されている(例えば、特許文献1参照)。

【0005】

このような記録再生装置では、再生時にバースト状のデータエラーが生じ、同一のECC(Error Correction Code)ブロックに多くのエラーが生じて、エラー訂正ができなくなることを防止するために、同一のECCブロックに含まれるシンクブロックの分布がテープの傾斜トラック上でランダムとなるように、シャフリング処理を行って記録するのが一般的である。

【0006】

また、このような記録再生装置では、テープの走行速度を通常再生時に比べて、速く、あるいは遅くして再生を行う変速再生時には、再生ヘッドが傾斜トラックに沿って走査せず、複数の傾斜トラックに跨って走査する。そのため、変速再生時には、各傾斜トラックに記録されたシンクブロックの全てを再生できず、一部のみが再生される。

【0007】

再生されたシンクブロックは、当該シンクブロックに対応したメモリのアドレス位置に順次書き込まれ、そのアドレス位置に記憶されるシンクブロックのみが更新される。そして、メモリに記憶されている1画面分のシンクブロックに基づき、デパッキング処理によって各ブロックの圧縮符号化データが順次取得され、データ伸長の処理が行われ、再生ビデオデータが得られる。

【0008】

【特許文献1】

特開平09−139910号公報

【0009】

【発明が解決しようとする課題】

上述した特許文献1のように、各ブロックの圧縮符号化データをそれぞれ一個のシンクブロックにパッキングするものにあっては、変速再生時に再生される全てのシンクブロックを使用することができる。

【0010】

ところで、圧縮率が低い場合には、各ブロックの圧縮符号化データをそれぞれ複数個のシンクブロックにパッキングすることとなる。その場合、テープの傾斜トラックに記録されているシンクブロックには、変速再生時に単独で再生したとき、使用できる第1のシンクブロックと、使用できない第2のシンクブロックが存在するようになる。例えば、上述したように直交変換を用いた圧縮符号化が行われる場合、第1のシンクブロックはDC係数を含むシンクブロックであり、第2のシンクブロックはDC係数を含まないシンクブロックである。

【0011】

すなわちこの場合、同一ブロックに係る第1のシンクブロックと第2のシンクブロックとをペアで取得できれば、第2のシンクブロックも使用できることから、画質の向上を図ることが可能となる。またこの場合、第2のシンクブロックを単独で再生した場合、当該第2のシンクブロックは使用できないので、このシンクブロックをメモリに書き込むものとすれば無駄となる。

【0012】

この発明の目的は、変速再生時に同一ブロックに係る第1、第2のシンクブロックをペアで容易に再生できるようにすることにある。また、この発明の他の目的は、使用不可能な第2のシンクブロックをメモリに書き込む無駄を防止することにある。

【0013】

【課題を解決するための手段】

この発明に係るデータ再生方法は、二次元ブロック単位で圧縮符号化されたビデオデータをパッキングする複数個のシンクブロックとして、テープの通常の走行速度に比べて速くあるいは遅くして再生を行う変速再生時に単独で再生したとき、使用できるシンクブロックを第1のシンクブロックとし、使用できないシンクブロックを第2のシンクブロックとしたとき、同一の二次元ブロックに係る第1および第2のシンクブロックが順次連続して記録されてなるテープの傾斜トラックを再生ヘッドで走査して当該第1および第2のシンクブロックを再生し、変速再生時には、再生された第1のシンクブロックについては、付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第1のシンクブロックに対応するメモリのアドレス位置に当該第1のシンクブロックを書き込み、再生された第2のシンクブロックについては、直前に再生された第1のシンクブロックがエラー訂正でき、該第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第2のシンクブロックに対応するメモリのアドレス位置に当該第2のシンクブロックを書き込むものである。

【0014】

また、この発明に係るデータ再生装置は、二次元ブロック単位で圧縮符号化されたビデオデータをパッキングする複数個のシンクブロックとして、テープの通常の走行速度に比べて速くあるいは遅くして再生を行う変速再生時に単独で再生したとき、使用できるシンクブロックを第1のシンクブロックとし、使用できないシンクブロックを第2のシンクブロックとしたとき、同一の二次元ブロックに係る第1および第2のシンクブロックが順次連続して記録されてなるテープの傾斜トラックを再生ヘッドで走査して当該第1および第2のシンクブロックを再生する再生手段と、再生手段で再生された第1および第2のシンクブロックを、メモリの当該第1および第2のシンクブロックに対応するアドレス位置に書き込むデータ書き込み手段とを備え、データ書き込み手段は、変速再生時には、再生された第1のシンクブロックについては、付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第1のシンクブロックに対応するメモリのアドレス位置に当該第1のシンクブロックを書き込み、再生された第2のシンクブロックについては、直前に再生された第1のシンクブロックがエラー訂正でき、該第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第2のシンクブロックに対応するメモリのアドレス位置に当該第2のシンクブロックを書き込むものである。

【0020】

この発明においては、ビデオデータが二次元ブロック単位で圧縮符号化され、各ブロックの圧縮符号化データがそれぞれ複数個のシンクブロックに渡ってパッキングされ、このシンクブロックが順次記録されてなるテープの傾斜トラックが、再生ヘッドで走査される。そして、再生されたシンクブロックが、当該シンクブロックに対応するメモリのアドレス位置に書き込まれる。

【0021】

例えば、同一のECCブロックに含まれるシンクブロックの分布がテープの傾斜トラック上でランダムとなるようにシャフリング処理されて記録されている場合、このように再生されたシンクブロックに対応するメモリのアドレス位置に書き込まれることで、デシャフリング処理が行われることとなる。

【0022】

この場合、各ブロックの圧縮符号化データをパッキングする複数個のシンクブロックとして、変速再生時に単独で再生したとき、使用できる第1のシンクブロックおよび使用できない第2のシンクブロックが存在する。また、同一のブロックに係る第1のシンクブロックおよび第2のシンクブロックは、傾斜トラックに連続して記録されている。

【0023】

変速再生時には、再生された第1のシンクブロックおよび第2のシンクブロックは以下のように処理される。つまり、再生された第1のシンクブロックについては、付加されているパリティによってエラー訂正できたとき、メモリに書き込まれる。一方、第2のシンクブロックについては、直前に再生された第1のシンクブロックがエラー訂正でき、この第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正できたとき、メモリに書き込まれる。

【0024】

第2のシンクブロックについては、同一のブロックに係る第1のシンクブロックとペアでのみ使用できる。直前に再生された第1のシンクブロックがエラー訂正できないとき、直前に再生された第1のシンクブロックと同一のブロックに係るものでないとき、および付加されているパリティによってエラー訂正できないとき、いずれも当該第2のシンクブロックは、同一のブロックに係る第1のシンクブロックとペアで使用できない。このような場合、第2のシンクブロックをメモリに書き込まないものであり、使用不可能な第2のシンクブロックをメモリに書き込む無駄を防止できる。

【0025】

なお、再生された第1のシンクブロックをメモリに書き込む際に、この第1のシンクブロックと同一のブロックに係る第2のシンクブロックをメモリに書き込まないときは、この第1のシンクブロックに後シンクエラーフラグを付加してメモリに書き込むことができる。その場合には、当該後シンクエラーフラグに基づいて、メモリ上でこの第1のシンクブロックとペアである第2のシンクブロックの圧縮符号化データを用いないようにでき、他のブロックの圧縮符号化データが混じることによる画質の劣化を防止できる。

【0026】

【発明の実施の形態】

以下、図面を参照しながら、この発明の実施の形態について説明する。図1は、実施の形態としての記録再生装置100の基本的構成を示している。なお、説明を簡単にするため、オーディオ系については省略している。

【0027】

まず、記録系を説明する。入力端子111に入力されるデジタルのビデオデータVinはビデオ圧縮回路112に供給される。このビデオ圧縮回路112では、ビデオデータVinが例えば8×8画素の二次元ブロックに分割され、DCT等のブロック符号化を用いたデータ圧縮処理が行われる。

【0028】

ビデオ圧縮回路112より出力されるビデオデータ(圧縮符号化データ)VDaは、ECCエンコーダ113に供給される。このECCエンコーダ113では、ビデオデータVDaに対して符号化単位毎に積符号を用いたエラー訂正符号化が行われる。このECCエンコーダ113より出力される記録ビデオデータ(エラー訂正符号化データ)VDbは、記録アンプ114を介して記録ヘッドHrに供給され、磁気テープ120の記録トラックに順次記録される。

【0029】

この場合、記録ビデオデータVDbはデジタル変調処理を経ることなく、NRZ(Non-Return-to-Zero)の形式のままで記録される。しかし、ビデオデータVDbに対してデジタル変調処理を施した後に記録するようにしてもよい。

【0030】

次に、再生系を説明する。磁気テープ120の記録トラックより再生ヘッドHpで再生された再生信号は再生アンプ131で増幅され、さらに等化回路132で波形等化された後に復号回路133に供給される。復号回路133では、波形等化後の再生信号に対して、例えばビタビアルゴリズムを利用した復号化の処理が行われ、上述した記録系のECCエンコーダ113から出力される記録ビデオデータVDbに対応した再生ビデオデータVDcが得られる。

【0031】

復号回路133より出力される再生ビデオデータVDcはECCデコーダ134に供給される。このECCデコーダ134では、ビデオデータVDcに付加されているパリティ(C1パリティ、C2パリティ)を用いてエラー訂正が行われる。

【0032】

ECCデコーダ134より出力されるエラー訂正後のビデオデータ(圧縮符号化データ)VDdはビデオ伸長回路135に供給される。このビデオ伸長回路135では、記録系のビデオ圧縮回路112とは逆の処理によってデータ伸長が行われる。そして、このビデオ伸長回路135より出力されるビデオデータVoutは出力端子136に出力される。

【0033】

図2は、磁気テープ120の記録フォーマットを示している。磁気テープ120には、その長手方向に対して傾斜したトラックTが順次形成される。この場合、互いに隣接する2本のトラックTにおける記録アジマスは異なるようにされる。

【0034】

トラックTの走査開始端側および走査終了端側の領域は、それぞれビデオデータ領域ARVL,ARVUに割り当てられている。このビデオデータ領域ARVL,ARVUには、上述したECCエンコーダ113より出力される記録ビデオデータVDbが記録される。また、トラックTのビデオ領域ARVL,ARVUに挟まれた領域は、オーディオデータ領域ARAに割り当てられている。このオーディオデータ領域ARAには、図1にはオーディオ系については図示していないが、記録オーディオデータが記録される。

【0035】

図3は、図1に示す記録再生装置100の回転ドラムの構成を示す略線図である。回転ドラム140には、180度の巻き付け角度をもって、磁気テープ120が斜めに巻き付けられる。磁気テープ120は、回転ドラム140にこのように巻き付けられた状態で、所定速度で走行するようにされる。

【0036】

また、回転ドラム140には、4個の記録ヘッドRECA〜RECDが配置されていると共に、これら4個の記録ヘッドRECA〜RECDに対して180度の角間隔をもって4個の記録ヘッドRECE〜RECHが配置されている。さらに、回転ドラム140には、記録ヘッドRECA〜RECHに対応する8個の再生ヘッドPBA〜PBHが、記録ヘッドRECA〜RECHに対してそれぞれ90度の角間隔をもって配置されている。

【0037】

図1に示す記録再生装置100の記録ヘッドHrは、実際には、上述したように8個の記録ヘッドRECA〜RECHからなっている。また、図1に示す記録再生装置100の再生ヘッドHpは、実際には、上述したように8個の再生ヘッドPBA〜PBHからなっている。1フィールドのビデオデータは、12トラックに記録される。記録時および再生時には、1回のスキャンでは4個のヘッドによって4トラックが同時に走査され、従って12トラックは3回のスキャンで走査される。

【0038】

12トラックのビデオデータ領域ARVL,ARVUには、図4に示すように、ブロック0〜ブロック35までの、36個のECCブロック(符号化単位のデータ)が記録される。1個のECCブロックは、以下のように構成されている。すなわち、226バイト×114バイトのデータ配列からなるビデオデータに対して、矢印bで示す外符号演算データ系列につき、各列のデータ(データ列)が例えば(126,114)リードソロモン符号によって符号化され、12バイトのC2パリティ(外符号パリティ)が生成される。さらに、これらビデオデータおよびC2パリティに対して、矢印aで示す内符号演算データ系列につき、各行のデータ(データ列)が例えば(242,226)リードソロモン符号によって符号化され、16バイトのC1パリティが生成される。また、各々のデータ行の先頭には、それぞれ2バイトの大きさを有するシンクデータおよびIDが配される。

【0039】

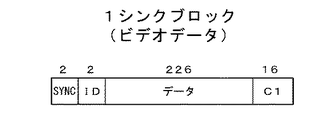

図5は、ECCブロックにおける1シンクブロックの構成を示している。先頭の2バイトはシンクデータである。続く2バイトはIDである。このIDには、当該1シンクブロックが12トラックのいずれに記録されたものかを識別するトラックID、当該1シンクブロックが一本の傾斜トラックに記録された複数のシンクブロックのいずれであるかを識別するシンクブロックIDが含まれる。

【0040】

例えば、シンクブロックIDは、9ビットのデータとして構成される。この場合、1ビットで、走査開始端側のビデオデータ領域ARVLに記録されるものか、走査終了端側のビデオデータ領域ARVUに記録されるものかを表すものとされる。また、残りの8ビットで、領域ARVL,ARVUのそれぞれに記録される189シンクブロックにそれぞれ対応して0〜188の数値が与えられる。

【0041】

また、12トラック毎に1セグメントが構成され、0〜3のセグメント番号が順次繰り返し付与されるが、上述の2バイトのIDには、当該1シンクブロックが記録されるセグメントのセグメント番号を示すセグメントIDも含まれる。

【0042】

また、このIDに、226バイトのビデオデータ(またはC2パリティ)および16バイトのC1パリティが続く。

【0043】

上述したように、磁気テープ120の12トラックに、36個のECCブロック(図4参照)が記録される。図6は、1セグメントを構成する12トラックのビデオデータ領域ARVL,ARVUにおける各ECCブロックのシンクブロックの配置を示している。

【0044】

図6Aに示すように、1回目にスキャンされる0〜3の4トラックに関しては、ビデオデータ領域ARVLには0〜35のECCブロックにおける0Row〜20Rowまでの21Rowのシンクブロックが記録され、ビデオデータ領域ARVUには0〜35のECCブロックにおける21Row〜41Rowまでの21Rowのシンクブロックが記録される。

【0045】

また、2回目にスキャンされる4〜7の4トラックに関しては、ビデオデータ領域ARVLには0〜35のECCブロックにおける42Row〜62Rowまでの21Rowのシンクブロックが記録され、ビデオデータ領域ARVUには0〜35のECCブロックにおける63Row〜83Rowまでの21Rowのシンクブロックが記録される。

【0046】

さらに、3回目にスキャンされる8〜11の4トラックに関しては、ビデオデータ領域ARVLには0〜35のECCブロックにおける84Row〜104Rowまでの21Rowのシンクブロックが記録され、ビデオデータ領域ARVUには0〜35のECCブロックにおける105Row〜125Rowまでの21Rowのシンクブロックが記録される。

【0047】

ここで、0Rowのシンクブロックは、0〜35のECCブロックのそれぞれにおける0番目のシンクブロックからなっており、これら36個のシンクブロックは、図6Bに示すように、0〜4のトラックに、9シンクブロックずつ振り分けられて記録される。つまり、0のトラックには0,18,1,19,2,20,3,21,4のECCブロックにおける0番目のシンクブロックが記録され、1のトラックには22,5,23,6,24,7,25,8,26のECCブロックにおける0番目のシンクブロックが記録され、2のトラックには9,27,10,28,11,29,12,30,13のECCブロックにおける0番目のシンクブロックが記録され、さらに3のトラックには31,14,32,15,33,16,34,17,35のECCブロックにおける0番目のシンクブロックが記録される。

【0048】

以下、同様に、1〜125Rowのシンクブロックは、それぞれ0〜35のECCブロックにおける1〜125番目のシンクブロックからなっており、各36個のシンクブロックは対応する4トラックに9シンクブロックずつ振り分けられて記録される。この場合、Row毎に、4トラックのそれぞれに記録される9シンクブロックが取り出されるECCブロックがローテーションされる。なお、1シンクブロックは、図6Cに示すように、2バイトのシンクデータ、2バイトのID、226バイトのビデオデータ(またはC2パリティ)および16バイトのC1パリティからなっている。

【0049】

ここで、0〜11の12トラックには、0Row〜125Rowのシンクブロックが順次記録される。この場合、0Row〜113Rowのシンクブロックは、内符号演算データ系列を構成するビデオデータのデータ列にC1パリティが付加されてなるものであるが、114Row〜125Rowのシンクブロックは、内符号演算データ系列を構成するC2パリティのデータ列にC1パリティが付加されてなるものである。

【0050】

つまり、本実施の形態においては、12トラックに0〜35の36個のECCブロックを記録する際に、図7に示すように、最初は内符号演算データ系列を構成するビデオデータのデータ列にC1パリティが付加されてなる第1のシンクブロックが順次記録され、この第1のシンクブロックの記録が終了した後に、内符号演算データ系列を構成するC2パリティのデータ列にC1パリティが付加されてなる第2のシンクブロックが順次記録される。

【0051】

次に、図1に示す記録再生装置100におけるECCエンコーダ113の詳細を説明する。図8は、ECCエンコーダ113の構成を示している。

【0052】

このECCエンコーダ113は、SDRAM(Synchronous Dynamic RAM)151と、このSDRAM151に対する書き込みおよび読み出しを行うためのインタフェースであるSDRAMインタフェース152とを有している。SDRAM151は、複数フィールドのビデオデータを記憶し得る容量を持っている。この場合、SDRAM151には、各フィールドについて、36個のECCブロック(図4参照)に対応したメモリ空間が用意されている。

【0053】

また、ECCエンコーダ113は、ビデオ圧縮回路112から供給されるビデオデータ(圧縮符号化データ)VDaをSDRAM151に書き込むためのバッファとなる入力書き込みバッファ153を有している。ここで、入力書き込みバッファ153は、パッキング手段も構成しており、ビデオ圧縮回路112から供給されるビデオデータ(圧縮符号化データ)VDaをシンクブロックにパッキングする。

【0054】

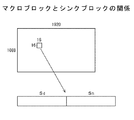

上述したようにビデオ圧縮回路112では、ビデオデータVinが例えば8×8画素の二次元ブロックに分割され、DCT等のブロック符号化を用いたデータ圧縮処理が行われる。上述せずも、有効画面は、1920画素×1088ラインで構成される。入力書き込みバッファ153では、図9に示すように、16×16画素のマクロブロック(8×8画素のDCTブロックが4個で構成される)の圧縮符号化データ毎に、2個のシンクブロックSd,Shにパッキングされる。

【0055】

ここで、シンクブロックSdは、第1のシンクブロックを構成しており、変速再生時に単独で再生したとき、使用できるシンクブロックである。このシンクブロックSdには、DC係数を含む低域周波数領域の係数がパッキングされる。また、シンクブロックShは、第2のシンクブロックを構成しており、変速再生時に単独で再生したとき、使用できないシンクブロックである。このシンクブロックShには、シンクブロックSdにパッキングされる係数を除く、高域周波数領域の係数がパッキングされる。

【0056】

SDRAM151には、各マクロブロックの圧縮符号化データがパッキングされたシンクブロックSd,Shが、各フィールドにつき、36個のECCブロックに対応したメモリ空間に順次書き込まれる。図6に示すように、36個のECCブロックの各シンクブロックがシャフリングされて傾斜トラックに記録される。各マクロブロックの圧縮符号化データがパッキングされたシンクブロックSd,ShをSDRAM151の36個のECCブロックに対応したメモリ空間に書き込む際に、図10に示すように、同一のマクロブロックに係るシンクブロックSd,Shが連続して記録されるように、SDRAM151における書き込みアドレスが制御される。なお、図10において、矢印SCNは、変速再生時における、再生ヘッドの走査軌跡の一例を示している。

【0057】

つまり、36個のECCブロックの各シンクブロックが図6Bに示すように記録される場合、0,18のECCブロックの0番目のシンクブロック、1,19のECCブロックの0番目のシンクブロック、2,20のECCブロックの0番目のシンクブロック、・・・に対応したメモリ空間には、それぞれ同一のマクロブロックに係るシンクブロックSd,Shが書き込まれる。

【0058】

図8に戻って、また、ECCエンコーダ113は、各フィールドについて、SDRAM151から読み出される36個のECCブロックに対応したビデオデータを後述するC2エンコーダ155に供給するためのバッファとなるC2読み出しバッファ154と、各フィールドについて、36個のECCブロックにおけるC2パリティ(外符号パリティ)を演算するC2エンコーダ155とを有している。

【0059】

この場合、C2エンコーダ155は、C2パリティを演算する演算器を例えば36個有しており、上述した36個のECCブロックにおけるC2パリティを並行して演算できる。そのため、C2読み出しバッファ154からC2エンコーダ155には、36個のECCブロックに対応したビデオデータが並行して供給される。

【0060】

また、ECCエンコーダ113は、各フィールドについて、C2エンコーダ155で演算された36個のECCブロックにおけるC2パリティをSDRAM151に書き込むためのバッファとなるC2書き込みバッファ156と、各フィールドについて、SDRAM151から読み出される、36個のECCブロックに対応したビデオデータおよびC2パリティを出力するためのバッファとなる出力バッファ157とを有している。

【0061】

また、ECCエンコーダ113は、出力バッファ157から記録順に出力される各シンクブロックのビデオデータ(またはC2パリティ)のデータ列に、シンクデータおよびIDを付加するSYNC・ID付加回路158と、このSYNC・ID付加回路158でシンクデータおよびIDが付加された各シンクブロックのビデオデータに対してC1パリティを演算して付加し、記録ビデオデータVDbとして出力するC1エンコーダ159とを有している。

【0062】

図8に示すECCエンコーダ113の動作を説明する。

ビデオ圧縮回路112(図1参照)より供給されるビデオデータ(圧縮符号化データ)VDaは、入力書き込みバッファ153およびSDRAMインタフェース152を介してSDRAM151に書き込まれる。この場合、16×16画素のマクロブロックの圧縮符号化データ毎に、2個のシンクブロックSd,Shにパッキングされ、これらシンクブロックSd,Shが、各フィールドにつき、36個のECCブロックに対応したメモリ空間に順次書き込まれる。

【0063】

この場合、同一のマクロブロックに係るシンクブロックSd,Shが傾斜トラックに連続して記録されるように(図10参照)、SDRAM151における書き込みアドレスが制御される。ここで、シンクブロックSdは、変速再生時に単独で再生したとき使用できる第1のシンクブロックを構成している。このシンクブロックSdには、DC係数を含む低域周波数領域の係数がパッキングされる。また、シンクブロックShは、変速再生時に単独で再生したとき使用できない第2のシンクブロックを構成している。このシンクブロックShには、シンクブロックSdにパッキングされる係数を除く、高域周波数領域の係数がパッキングされる。

【0064】

また、各フィールドについて、SDRAM151から読み出される36個のECCブロックに対応したビデオデータは、SDRAMインタフェース152およびC2読み出しバッファ154を介してC2エンコーダ155に供給される。この場合、C2読み出しバッファ154からC2エンコーダ155には、36個のECCブロックに対応したビデオデータが並行して供給される。

【0065】

C2エンコーダ155では、各フィールドについて、36個の演算器によって、36個のECCブロックにおけるC2パリティが並行して演算される。このように各フィールドについて、C2エンコーダ155で演算される、36個のECCブロックにおけるC2パリティは、C2書き込みバッファ156およびSDRAMインタフェース152を介して、SDRAM151の、対応する36個のECCブロックのメモリ空間におけるC2パリティ領域に書き込まれる。

【0066】

また、各フィールドについて、SDRAM151から読み出される36個のECCブロックに対応したビデオデータおよびC2パリティは、SDRAMインタフェース152を介して出力バッファ157に供給される。この出力バッファ157から記録順に出力される各シンクブロックのビデオデータ(またはC2パリティ)は、SYNC・ID付加回路158でシンクデータおよびIDが付加された後にC1エンコーダ159に供給される。

【0067】

C1エンコーダ159では、シンクデータおよびIDが付加された各シンクブロックのビデオデータに対してC1パリティが演算されて付加され、記録ビデオデータVDbとしての各シンクブロックが生成される。この記録ビデオデータVDbは、上述したように記録アンプ114(図1参照)に供給される。

【0068】

次に、図1に示す記録再生装置100におけるECCデコーダ134の詳細を説明する。図11は、ECCデコーダ134の構成を示している。

【0069】

このECCデコーダ134は、復号回路133から供給される再生ビデオデータVDcを構成する各シンクブロックのシンクデータを検出するSYNC検出回路161と、このSYNC検出回路161を通じて供給される各シンクブロック毎にC1パリティを用いてエラー訂正処理を行うC1デコーダ162とを有している。C1デコーダ162からは、エラー訂正処理後のビデオデータ列に、エラー訂正ができたか否かを示すエラー訂正フラグおよびIDが付加された状態で、各シンクブロックが出力される。エラー訂正フラグは、シンクデータの部分に挿入される。この場合、エラー訂正フラグがエラー訂正ができたことを示す状態にある場合、そのエラー訂正フラグが付加されているビデオデータ列にはエラーは含まれておらず、一方エラー訂正フラグがエラー訂正ができなかったことを示す状態にある場合、そのエラー訂正フラグが付加されているビデオデータ列にはエラーが含まれている。

【0070】

また、ECCデコーダ134は、SDRAM163と、このSDRAM163に対する書き込みおよび読み出しを行うためのインタフェースであるSDRAMインタフェース164とを有している。SDRAM163は、複数フィールドのビデオデータを記憶し得る容量を持っている。この場合、SDRAM163には、各フィールドについて、36個のECCブロック(図4参照)に対応したメモリ空間が用意されている。

【0071】

また、ECCデコーダ134は、C1デコーダ162から供給される各シンクブロックをSDRAM163に書き込むためのバッファとなる入力書き込みバッファ165を有している。

【0072】

ここで、入力書き込みバッファ165は、通常再生時には、後述するように、C2デコーダによってC2パリティを用いたエラー訂正処理が行われることから、付加されているエラー訂正フラグの状態によらず、全てのシンクブロックをSDRAM163に書き込む。この場合、各シンクブロックは、それに付加されているトラックIDおよびシンクブロックIDに基づいて、各フィールドにつき、36個のECCブロックに対応したメモリ空間の所定アドレス位置に書き込まれる。これにより、SDRAM163には、各フィールドにつき、それぞれ記録時と同様の126個のシンクブロックからなる、36個のECCブロックが生成される。

【0073】

また、入力書き込みバッファ165は、磁気テープ120の走行速度を通常再生時より速くあるいは遅くして再生を行う変速再生時には、C1デコーダ162から供給されるシンクブロックのうち、以下の選択処理で選択されたシンクブロックのみ、SDRAM163に書き込む。この場合も、各シンクブロックは、それに付加されているトラックIDおよびシンクブロックIDに基づいて、36個のECCブロックに対応したメモリ空間の所定アドレス位置に書き込まれる。この場合、各フィールドにおいて同一のメモリ空間に書き込みが行われ、記憶データが順次更新されていく。

【0074】

図12のフローチャートは、選択処理の手順を示している。

ステップST1で処理を開始し、ステップST2で、再生されたシンクブロックが、シンクブロックSd、Shのいずれかかを判定する。この判定は、シンクブロックIDに基づいて行われる。シンクブロックSdであると判定するときは、ステップST3で、当該シンクブロックがC1パリティによってエラー訂正できたものであるか否かを判定する。この判定は、エラー訂正フラグに基づいて行われる。

【0075】

エラー訂正できたものであるときは、ステップST4で、当該シンクブロックを書き込みシンクブロックとして選択し、ステップST5で処理を終了する。一方、エラー訂正できたものでないときは、ステップST6で、当該シンクブロックを書き込みシンクブロックとして選択しないこととし、ステップST5で処理を終了する。

【0076】

上述のステップST2でシンクブロックShであると判定するときは、ステップST7で、直前に再生されたシンクブロックSdが、エラー訂正できて書き込みシンクブロックとして選択されたか否かを判定する。書き込みシンクブロックとして選択されたときは、ステップST8で、当該シンクブロックが、直前に再生されたシンクブロックSdと同一のマクロブロックに係るものであるか否かを判定する。この判定はトラックIDおよびシンクブロックIDに基づいて行われる。

【0077】

すなわち、当該シンクブロックにおけるトラックIDが直前に再生されたシンクブロックSdにおけるトラックIDと同一であり、かつ当該シンクブロックにおけるシンクブロックIDが直前に再生されたシンクブロックSdにおけるシンクブロックIDに連続したものであるとき、当該シンクブロックは、直前に再生されたシンクブロックSdと同一のマクロブロックに係るものであると判定する。

【0078】

ステップST8で同一のマクロブロックに係るものであると判定するときは、ステップST9で、当該シンクブロックがC1パリティによってエラー訂正できたものであるか否かを判定する。この判定は、エラー訂正フラグに基づいて行われる。

【0079】

エラー訂正できたものであるときは、ステップST4で、当該シンクブロックを書き込みシンクブロックとして選択し、ステップST5で処理を終了する。ステップST7で直前に再生されたシンクブロックSdが書き込みブロックとして選択されなかったとき、ステップST8で当該シンクブロックが直前に再生されたシンクブロックSdと同一のマクロブロックに係るものでないとき、およびステップST9で当該シンクブロックがエラー訂正できたものでないときは、ステップST6で、当該シンクブロックを書き込みシンクブロックとして選択しないこととし、ステップST5で処理を終了する。

【0080】

また、入力書き込みバッファ165は、シンクブロックSdをSDRAM163に書き込む際に、このシンクブロックSdと同一のマクロブロックに係るシンクブロックShを書き込むことができないとき、当該シンクブロックSdに後シンクエラーフラグを付加してSDRAM163に書き込む。この状況は、再生されたシンクブロックSdが書き込みシンクブロックとして選択されるが、その直後に再生されたシンクブロックShが、当該シンクブロックSdと同一のマクロブロックに係るものでないか、あるいはエラー訂正できたものでなく、書き込みシンクブロックとして選択されなかった場合に、発生する。

【0081】

このようにシンクブロックSdに後シンクエラーフラグを付加してSDRAM163に書き込むのは、SDRAM163に記憶されている当該シンクブロックSdとペアになるべきシンクブロックShは、当該シンクブロックSdと同一のマクロブロックに係るものではなく、例えば後段のビデオ伸長回路135で、そのシンクブロックShに含まれる圧縮符号化データの使用を防止可能とするためである。

【0082】

図11に戻って、また、ECCデコーダ134は、各フィールドについて、SDRAM163から読み出される36個のECCブロックにおける各シンクブロックのデータを後述するC2デコーダ167に供給するためのバッファとなるC2読み出しバッファ166と、各フィールドについて、36個のECCブロックにおいてC2パリティを用いてエラー訂正処理を行うC2デコーダ167と、各フィールドについて、C2デコーダ167で訂正された36個のECCブロックにおけるビデオデータ(圧縮符号化データ)をSDRAM163に書き込むためのバッファとなるC2書き込みバッファ168とを有している。

【0083】

なお、これらバッファ166,168およびC2デコーダ167の部分は、通常再生時にのみ使用される。つまり、変速再生時には、C2パリティを用いたエラー訂正処理は行われない。

【0084】

また、ECCデコーダ134は、各フィールドについて、SDRAM163に記憶されている36個のECCブロックに基づいて、各マクロブロックの圧縮符号化データを出力するためのバッファとなる出力バッファ169を有している。この場合、出力バッファ169は、デパッキングの処理を行って、各マクロブロックの圧縮符号化データを対応するシンクブロックSd,Shから取得する。

【0085】

なお、出力バッファ169は、変速再生時には、所定のマクロブロックの圧縮符号化データを得るためのシンクブロックSdに後シンクエラーフラグが付加されている場合には、当該所定のマクロブロックの圧縮符号化データのうち、シンクブロックShから取得した圧縮符号化データに関しては、エラーフラグを付加して出力する。これにより、後段のビデオ伸長回路135では、エラーフラグが付加されている圧縮符号化データを誤って使用することを防止できる。

【0086】

図11に示すECCデコーダ134の動作を説明する。最初に通常再生時の動作を説明する。

【0087】

復号回路133から供給される再生ビデオデータVDcはSYNC検出回路161でシンクデータが検出され、その後にC1デコーダ162に供給される。C1デコーダ162では、各シンクブロックに対して、C1パリティを用いたエラー訂正処理が行われる。このC1デコーダ162からは、エラー訂正処理後のビデオデータ列に、エラー訂正ができたか否かを示すエラー訂正フラグおよびIDが付加された状態で、各シンクブロックが出力される。

【0088】

C1デコーダ162から出力される各シンクブロックは、入力書き込みバッファ165およびSDRAMインタフェース164を介して、SDRAM163に書き込まれる。この場合、各シンクブロックは、それに付加されているトラックIDおよびシンクブロックIDに基づいて、各フィールドについて、36個のECCブロックに対応したメモリ空間の所定アドレス位置に書き込まれる。これにより、SDRAM163には、各フィールドにつき、それぞれ記録時と同様の126個のシンクブロックからなる、36個のECCブロックが生成される。

【0089】

また、各フィールドについて、SDRAM163から36個のECCブロックにおける各シンクブロックのデータが読み出され、SDRAMインタフェース164およびC2読み出しバッファ166を介してC2デコーダ167に供給される。C2デコーダ167では、各フィールドにつき、36個のECCブロックにおいて、C2パリティを用いてエラー訂正処理が行われる。そして、各フィールドについて、C2デコーダ167で訂正された36個のECCブロックにおけるビデオデータ(圧縮符号化データ)は、C2書き込みバッファ168およびSDRAMインタフェース164を介して、SDRAM163に書き込まれる。

【0090】

また、各フィールドについて、SDRAM163に記憶されている36個のECCブロックに基づいて、各マクロブロックの圧縮符号化データが読み出され、出力バッファ169を介して出力される。この場合、出力バッファ169では、デパッキングの処理が行われ、各マクロブロックの圧縮符号化データが、対応するシンクブロックSd,Shから取得される。

【0091】

次に、変速再生時の動作を説明する。

復号回路133から供給される再生ビデオデータVDcはSYNC検出回路161でシンクデータが検出され、その後にC1デコーダ162に供給される。C1デコーダ162では、各シンクブロックに対して、C1パリティを用いたエラー訂正処理が行われる。このC1デコーダ162からは、エラー訂正処理後のビデオデータ列に、エラー訂正ができたか否かを示すエラー訂正フラグおよびIDが付加された状態で、各シンクブロックが出力される。

【0092】

C1デコーダ162から出力される各シンクブロックは、入力書き込みバッファ165およびSDRAMインタフェース164を介して、SDRAM163に書き込まれる。この場合、C1デコーダ162から供給されるシンクブロックのうち、選択されたシンクブロックのみ、SDRAM163に書き込まれる。つまり、シンクブロックSdに関しては、C1パリティによってエラー訂正できた場合には、書き込みシンクブロックとして選択される。また、シンクブロックShに関しては、直前に再生されたシンクブロックSdが書き込みブロックとして選択され、当該シンクブロックShが直前に再生されたシンクブロックSdと同一のマクロブロックに係るものであり、かつ当該シンクブロックShがC1パリティによってエラー訂正できた場合には、書き込みシンクブロックとして選択される。

【0093】

この場合、各シンクブロックは、それに付加されているトラックIDおよびシンクブロックIDに基づいて、36個のECCブロックに対応したメモリ空間の所定アドレス位置に書き込まれる。この場合、各フィールドにおいて同一のメモリ空間に書き込みが行われ、記憶データが順次更新されていく。

【0094】

またこの場合、シンクブロックSdがSDRAM163に書き込まれるが、このシンクブロックSdと同一のマクロブロックに係るシンクブロックShがSDRAM163に書き込まれないとき、当該シンクブロックSdに後シンクエラーフラグが付加されてSDRAM163に書き込まれる。

【0095】

また、各フィールドについて、SDRAM163に記憶されている36個のECCブロックに基づいて、各マクロブロックの圧縮符号化データが読み出され、SDRAMインタフェース164および出力バッファ169を介して出力される。この場合、各マクロブロックの圧縮符号化データは、対応するシンクブロックSd,Shから取得される。

【0096】

ここで、所定のマクロブロックの圧縮符号化データを得るためのシンクブロックSdに、後シンクエラーフラグが付加されている場合には、当該所定のマクロブロックの圧縮符号化データのうち、シンクブロックShから取得した圧縮符号化データに関しては、エラーフラグが付加されて出力される。この場合、SDRAM163上でシンクブロックSdとペアであるシンクブロックShには、実際には同一のマクロブロックに係る圧縮符号化データが含まれていない。これにより、後段のビデオ伸長回路135では、エラーフラグが付加されている圧縮符号化データを誤って使用することを防止でき、他のブロックの圧縮符号化データが混じることによる画質の劣化を防止できる。

【0097】

以上説明したように、本実施の形態においては、磁気テープ120の傾斜トラックTには、同一のマクロブロックに係るシンクブロックSd,Shが連続して記録される(図10参照)。したがって、変速再生時に、同一のマクロブロックに係るシンクブロックSd,Shをペアで容易に再生でき、画質の向上を図ることができる。

【0098】

また、本実施の形態においては、変速再生時において、再生されたシンクブロックShについては、直前に再生されたシンクブロックSdがSDRAM163に書き込まれないとき、当該シンクブロックShと直前に再生されたシンクブロックSdとが同一のマクロブロックに係るものでないとき、さらには当該シンクブロックShがC1パリティによってエラー訂正できないときは、SDRAM163に書き込まないものであり、使用不可能なシンクブロックShをSDRAM163に書き込む無駄を防止できる。

【0099】

なお、上述実施の形態においては、ブロック毎の圧縮符号化データが16×16画素のマクロブロック毎の圧縮符号化データであるものを示したが、これに限定されるものではない。例えば、ブロック毎の圧縮符号化データが、8×8のDCTブロックの圧縮画像データであってもよい。

【0100】

また、上記実施の形態においては、マクロブロック毎の圧縮符号化データを2個のシンクブロックSd,Shにパッキングするものを示したが、ブロック毎の圧縮符号化データをパッキングするシンクブロックの数は2個に限定されるものではない。

【0101】

また、上記実施の形態においては、DCT等のブロック符号化を用いたデータ圧縮処理が行われるものであるが、DCTの他にウォーブレット変換、離散サイン変換等の直交変換を用いた符号化処理、あるいはその他の符号化処理を行ってもよい。要は、ブロック毎の圧縮符号化データを複数個のシンクブロックにパッキングした場合、変速再生時に単独で再生したとき、使用できる第1のシンクブロックと、使用できない第2のシンクブロックとを、得ることができるものであればよい。

【0102】

【発明の効果】

この発明によれば、ビデオデータを二次元ブロック単位で分割して圧縮符号化し、各ブロックの圧縮符号化データを複数のブロックに渡ってパッキングし、テープの傾斜トラックに、同一のブロックに係る第1、第2のシンクブロック(変速再生時に単独で再生したとき、第1のシンクブロックは使用できるが、第2のシンクブロックは使用できない)を連続して記録するものであり、変速再生時に同一ブロックに係る第1、第2のシンクブロックをペアで容易に再生でき、画質の向上を図ることができる。

【0103】

また、この発明によれば、上述したように第1、第2のシンクブロックが記録されたテープの傾斜トラックからシンクブロックを再生する際に、第1のシンクブロックについてはエラー訂正できたときはメモリに書き込むが、第2のシンクブロックについては、直前に再生された第1のシンクブロックがエラー訂正でき、この第1のシンクブロックと同一のブロックに係るものであり、かつエラー訂正できたときメモリに書き込むものであり、使用不可能な第2のシンクブロックをメモリに書き込む無駄を防止できる。

【0104】

また、この発明によれば、再生された第1のシンクブロックをメモリに書き込む際に、この第1のシンクブロックと同一のブロックに係る第2のシンクブロックをメモリに書き込まないときは、この第1のシンクブロックに後シンクエラーフラグを付加してメモリに書き込むものであり、この後シンクエラーフラグに基づいて、メモリ上でこの第1のシンクブロックとペアである第2のシンクブロックの圧縮符号化データを用いないようにでき、他のブロックの圧縮符号化データが混じることによる画質の劣化を防止できる。

【図面の簡単な説明】

【図1】実施の形態としての記録再生装置の構成を示すブロック図である。

【図2】記録フォーマットを説明するための図である。

【図3】磁気ヘッドの配置を説明するための図である。

【図4】ビデオデータのECCブロックの構成を示す図である。

【図5】ビデオデータの1シンクブロックの構成を示す図である。

【図6】12トラック内のシンクブロックの配置を説明するための図である。

【図7】C2パリティの配置を示す図である。

【図8】ECCエンコーダの構成を示すブロック図である。

【図9】マクロブロックとシンクブロックとの関係を説明するための図である。

【図10】同一マクロブロックに係る2シンクブロックの配置を示す図である。

【図11】ECCデコーダの構成を示すブロック図である。

【図12】書き込みシンクブロックの選択処理の手順を示すフローチャートである。

【符号の説明】

100・・・記録再生装置、111・・・入力端子、112・・・ビデオ圧縮回路、113・・・ECCエンコーダ、114・・・記録アンプ、120・・・磁気テープ、131・・・再生アンプ、132・・・等化回路、133・・・復号回路、134・・・ECCデコーダ、135・・・ビデオ伸長回路、136・・・出力端子、140・・・回転ドラム、151・・・SDRAM、152・・・SDRAMインタフェース、153・・・入力書き込みバッファ、154・・・C2読み出しバッファ、155・・・C2エンコーダ、156・・・C2書き込みバッファ、157・・・出力バッファ、158・・・SYNC・ID付加回路、159・・・C1エンコーダ、161・・・SYNC検出回路、162・・・C1デコーダ、163・・・SDRAM、164・・・SDRAMインタフェース、165・・・入力書き込みバッファ、166・・・C2読み出しバッファ、167・・・C2デコーダ、168・・・C2書き込みバッファ、169・・・出力バッファ

Claims (4)

- 二次元ブロック単位で圧縮符号化されたビデオデータをパッキングする複数個のシンクブロックとして、テープの通常の走行速度に比べて速くあるいは遅くして再生を行う変速再生時に単独で再生したとき、使用できる上記シンクブロックを第1のシンクブロックとし、

使用できない上記シンクブロックを第2のシンクブロックとしたとき、

同一の二次元ブロックに係る上記第1および第2のシンクブロックが順次連続して記録されてなるテープの傾斜トラックを再生ヘッドで走査して当該第1および第2のシンクブロックを再生し、

上記変速再生時には、再生された上記第1のシンクブロックについては、付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第1のシンクブロックに対応するメモリのアドレス位置に当該第1のシンクブロックを書き込み、再生された上記第2のシンクブロックについては、直前に再生された上記第1のシンクブロックがエラー訂正でき、該第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第2のシンクブロックに対応するメモリのアドレス位置に当該第2のシンクブロックを書き込むデータ再生方法。 - 上記再生された第1のシンクブロックを上記メモリに書き込む際に、該第1のシンクブロックと同一のブロックに係る第2のシンクブロックを上記メモリに書き込まないときは、該第1のシンクブロックに後シンクエラーフラグを付加して上記メモリに書き込む請求項1に記載のデータ再生方法。

- 二次元ブロック単位で圧縮符号化されたビデオデータをパッキングする複数個のシンクブロックとして、テープの通常の走行速度に比べて速くあるいは遅くして再生を行う変速再生時に単独で再生したとき、使用できる上記シンクブロックを第1のシンクブロックとし、

使用できない上記シンクブロックを第2のシンクブロックとしたとき、

同一の二次元ブロックに係る上記第1および第2のシンクブロックが順次連続して記録されてなるテープの傾斜トラックを再生ヘッドで走査して当該第1および第2のシンクブロックを再生する再生手段と、

上記再生手段で再生された第1および第2のシンクブロックを、メモリの当該第1および第2のシンクブロックに対応するアドレス位置に書き込むデータ書き込み手段とを備え、

上記データ書き込み手段は、

上記変速再生時には、再生された上記第1のシンクブロックについては、付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第1のシンクブロックに対応するメモリのアドレス位置に当該第1のシンクブロックを書き込み、再生された上記第2のシンクブロックについては、直前に再生された上記第1のシンクブロックがエラー訂正でき、該第1のシンクブロックと同一のブロックに係るものであり、かつ付加されているパリティによってエラー訂正処理を行い、該エラー訂正できたとき、当該第2のシンクブロックに対応するメモリのアドレス位置に当該第2のシンクブロックを書き込むデータ再生装置。 - 上記データ書き込み手段は、

上記再生された第1のシンクブロックを上記メモリに書き込む際に、該第1のシンクブロックと同一ブロックに係る第2のシンクブロックを上記メモリに書き込まないときは、該第1のシンクブロックに後シンクエラーフラグを付加して上記メモリに書き込む請求項3に記載のデータ再生装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003101298A JP4264635B2 (ja) | 2003-04-04 | 2003-04-04 | データ再生方法およびデータ再生装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003101298A JP4264635B2 (ja) | 2003-04-04 | 2003-04-04 | データ再生方法およびデータ再生装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004312228A JP2004312228A (ja) | 2004-11-04 |

| JP4264635B2 true JP4264635B2 (ja) | 2009-05-20 |

Family

ID=33465140

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003101298A Expired - Fee Related JP4264635B2 (ja) | 2003-04-04 | 2003-04-04 | データ再生方法およびデータ再生装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4264635B2 (ja) |

-

2003

- 2003-04-04 JP JP2003101298A patent/JP4264635B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2004312228A (ja) | 2004-11-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3043268B2 (ja) | エラー訂正能力の向上されたデジタルビデオ記録方法及び再生方法 | |

| JP3004252B2 (ja) | 誤り訂正能力の改良されたディジタル記録/再生装置及びその方法 | |

| EP0683611A2 (en) | A digital recording and reproducing apparatus | |

| JPH09135423A (ja) | ディジタル信号の記録装置及び再生装置、ディジタル信号の記録方法及び再生方法 | |

| JPH0723333A (ja) | 映像信号の記録および再生装置 | |

| JP4264635B2 (ja) | データ再生方法およびデータ再生装置 | |

| CN1112699C (zh) | 声频和视频数据的记录和再现装置及其方法 | |

| JP3774929B2 (ja) | データ再生装置およびデータ再生方法 | |

| JPH04283473A (ja) | 映像音声デジタル記録/再生装置 | |

| JP3991905B2 (ja) | データ記録方法およびデータ記録装置 | |

| JP3991906B2 (ja) | データ再生方法およびデータ再生装置 | |

| JP4042610B2 (ja) | データ再生方法およびデータ再生装置 | |

| JP4107136B2 (ja) | 情報再生装置及び情報再生方法 | |

| JP4106713B2 (ja) | ディジタル情報信号記録装置およびその方法 | |

| JP3864924B2 (ja) | 情報記録装置、情報記録方法、情報再生装置、情報再生方法及び情報記録媒体 | |

| US7027715B2 (en) | Magnetic-tape recording apparatus, magnetic-tape recording method, magnetic tape, and recording medium | |

| JPWO1998044503A1 (ja) | ディジタル情報信号記録装置およびその方法 | |

| KR100213873B1 (ko) | 디지털 비디오 테이프 레코더의 트릭 모드를 구현하는 장치 및 방법 | |

| JP3861819B2 (ja) | 映像信号再生装置及び映像信号再生方法 | |

| JP3687428B2 (ja) | ディジタル信号の再生装置 | |

| JP3489223B2 (ja) | ディジタル信号記録装置および再生装置 | |

| JP3743309B2 (ja) | 記録方法および記録再生装置 | |

| JPH07105119B2 (ja) | Pcmプロセツサを用いたデ−タ記憶装置 | |

| JP2004310860A (ja) | 情報再生装置及び情報再生方法 | |

| JPH06302125A (ja) | ディジタル信号処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060314 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20060502 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20081104 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081219 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20090120 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20090202 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120227 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |