JP4042246B2 - 圧電発振器 - Google Patents

圧電発振器 Download PDFInfo

- Publication number

- JP4042246B2 JP4042246B2 JP04922799A JP4922799A JP4042246B2 JP 4042246 B2 JP4042246 B2 JP 4042246B2 JP 04922799 A JP04922799 A JP 04922799A JP 4922799 A JP4922799 A JP 4922799A JP 4042246 B2 JP4042246 B2 JP 4042246B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- collector

- oscillation

- circuit

- base

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03B—GENERATION OF OSCILLATIONS, DIRECTLY OR BY FREQUENCY-CHANGING, BY CIRCUITS EMPLOYING ACTIVE ELEMENTS WHICH OPERATE IN A NON-SWITCHING MANNER; GENERATION OF NOISE BY SUCH CIRCUITS

- H03B5/00—Generation of oscillations using amplifier with regenerative feedback from output to input

- H03B5/30—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator

- H03B5/32—Generation of oscillations using amplifier with regenerative feedback from output to input with frequency-determining element being electromechanical resonator being a piezoelectric resonator

Landscapes

- Oscillators With Electromechanical Resonators (AREA)

Description

【発明の属する技術分野】

本発明は圧電発振器に関し、特に、雑音特性やエージング特性に優れた圧電発振器に関する。

【0002】

【従来の技術】

通信機器の基準信号源等に用いられる水晶発振器としては、図3に示すような回路構成のものが知られている。

同図に於いて点線で囲まれた回路101は、一般的なコルピッツ型発振回路であって、水晶振動子102をトランジスタ103のベースに接続し、該トランジスタ103のベースとエミッタとをコンデンサ104を介して接続し、エミッタと接地とをコンデンサ105と抵抗106との並列回路を介して接続すると共に、コレクタを電源Vccに接続するよう構成し、更に、前記水晶振動子102の一方の端子は、コンデンサ107とトリマーコンデンサ108との直列回路を介し接地するように構成したものである。

尚、発振出力は前記トリマーコンデンサ108の両端から導出している。

【0003】

また、同図に於いて点線で囲まれた回路109の増幅回路は後述する整流回路と共にAGC回路の一部を成すものであって、トランジスタ110のエミッタを接地し、コレクタと電源Vccとを抵抗111を介して接続し、該コレクタとベースとを抵抗112をそれぞれ介し接続し、更に、該ベースと前記トランジスタ103のエミッタとをコンデンサ113を介して接続するように構成したものである。

更に、同図に於いて点線で囲まれた回路114は、前記整流回路であって、ダイオード115のアノードとダイオード116のカソードとを接続すると共に、該ダイオード115のカソードを接地し、前記ダイオード116のアノードと電源Vccとを抵抗117を介して接続し、該アノードと接地とをコンデンサ118とを介して接地し、更に、前記ダイオード116のカソードと前記トランジスタ110のコレクタとをコンデンサ119を介して接続し、前記ダイオード116のアノードと前記トランジスタ103のベースとを抵抗120を介し帰還接続するように構成したものである。

尚、同図に示すコンデンサ122はバイパスコンデンサである。

次にこのような構成の水晶発振器の動作について説明する。

前記発振回路101は先に説明した通り一般的なコルピッツ型発振回路であるので、その動作については説明を省略する。

前記発振回路101の設定条件に基づき前記トランジスタ103のエミッタより出力された周波数信号は、前記コンデンサ113を介し次段の前記増幅回路109に供給され所要のレベルに増幅されて前記トランジスタ110のコレクタより出力される。

【0004】

そして、増幅された該信号は、前記コンデンサ119を介し前記ダイオード115と前記ダイオード116とに供給される。

ここで、該信号のプラス側半サイクルの信号は、前記ダイオード115を通過するが、この時、前記コンデンサ119には前記ダイオード115のアノード側が低電位となるよう電荷がチャージされ、また、逆のマイナス側半サイクルの信号は、前記ダイオード116を介して流れ、結果的に該ダイオード116のアノードと接地間に負極性の電位が生じる。

【0005】

即ち、該電位は、前記マイナス側半サイクルの信号による電位と前記コンデンサ119のチャージ電荷により発生する電位とが加わった値であり、前記発振回路101のトランジスタ103のベースに印加される。

従って、前記発振回路101の出力信号のレベルが高くなると、前記増幅回路109から前記整流回路114に供給される信号の極小値と極大値との差(p−p値)が増加する為、これに伴い前整流回路114の出力に発生する前記負極性の電位の絶対値が大きくなると共に、その変動量に基づく該トランジスタ103のベースバイアス電圧の降下に伴いベース電流が減少する結果、コレクタ電流が減少し、前記発振回路101の出力信号のレベルが低下する。

【0006】

一方、前記発振回路101の出力信号のレベルが低下した場合は上記で説明した動作と逆の動作である為、説明を省略する。

従って、上記の動作を繰り返し行うことにより、水晶発振器はその設定条件に基づき安定なレベル信号を出力する。

【0007】

【本発明が解決しようとする課題】

しかしながら、前記水晶発振器は、上記のような特徴に加え前記整流回路114を利用し、前記水晶振動子102の励振信号を低レベルに保つよう制御することにより、良好なエージング特性を得ることが可能であるが、この時、出力信号の雑音特性が悪化してしまうという不具合が生じる。

【0008】

即ち、周知の通り、前記水晶振動子102を低レベルの励振電流で駆動させることにより、前記水晶発振器のエージング特性が良好となり、長期に亙り安定度の高い出力周波数が得られることから、極力、低レベルの励振電流に保つとその結果必然的に前記トランジスタ103のコレクタ電流が小さくなる。

しかし、図4のコレクタ電流と雑音指数との関係で示すように、コレクタ電流を極めて小さな値A点で設定した場合、トランジスタの雑音指数は極めて高い状態であると共に、更に、AGC機能により該コレクタ電流が減少すると、該雑音指数がより高い方向に急激に移行し、その結果、水晶発振器の雑音特性を悪化させてしまう。

【0009】

従って、上記のような構成の水晶発振器では、エージング特性を優先するのが一般的である為、雑音特性を犠牲にし励振電流を低く設定するのが一般的であった。

【0010】

【課題を解決するための手段】

上記課題を解決する為に本発明に係わる請求項1記載の発明は、圧電振動子と発振用トランジスタとを含むコルピッツ型発振器と、前記発振用トランジスタの出力を増幅し前記発振用トランジスタのコレクタにエミッタが接続された第二のトランジスタと、該第二のトランジスタの出力を整流する整流手段とを備え、該整流手段の出力を前記第二のトランジスタのベースに帰還することによって前記圧電振動子に流れる励振電流を一定に保つ圧電発振器であって、前記発振用トランジスタの動作点が飽和領域近傍となるよう前記第二のトランジスタのコレクタ電圧を設定し、前記励振電流が大きくなったときは前記第二のトランジスタのベースバイアス電圧が降下し、前記発振用トランジスタの動作点が飽和領域に近づくように前記コレクタ電圧が降下するものであり、前記励振電流が小さくなったときは前記第二のトランジスタのベースバイアス電圧が上昇し、前記発振用トランジスタの動作点が飽和領域から遠ざかるように前記コレクタ電圧が上昇するものであって、前記励振電流を低レベルに保つよう前記コレクタ電圧を制御したことを特徴としている。

【0011】

請求項2記載の発明は請求項1記載の発明に加え、前記第二のトランジスタのベースを交流的に接地し、第二のトランジスタのコレクタを電源に接続したことを特徴としている。

【0012】

請求項3記載の発明は、請求項1または請求項2において、前記発振用トランジスタの雑音指数が最小値近傍の値となるよう前記第二のトランジスタのコレクタ電流を設定したことを特徴としている。

【0015】

【本発明の実施の形態】

以下、図示した実施例に基づいて本発明を詳細に説明する。

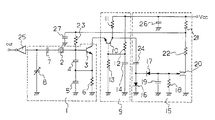

図1は本発明に基づく水晶発振器の一実施例を示す回路図である。

同図に於いて点線で囲まれた回路1は一般的なコルピッツ型発振回路であり、水晶振動子2をトランジスタ3のベースに接続すると共に、該トランジスタ3のベースとエミッタとをコンデンサ4を介し、該エミッタと接地とをコンデンサ5と抵抗6との並列回路を介しそれぞれ接続し、更に、前記水晶振動子2の一方の端子と接地とをコンデンサ7とトリマーコンデンサ8との直列回路を介し接続するよう構成したものである。

尚、発振出力は、例えば前記トリマーコンデンサ8の両端から導出している。

【0016】

また、同図に於いて点線で囲まれた増幅回路9は後述する整流回路と共にAGC回路の一部を成すものであって、トランジスタ10のエミッタと前記トランジスタ3のコレクタとを接続すると共に、該トランジスタ10のコレクタと電源Vccとを抵抗11を介して接続し、該電源Vccとベースとを抵抗12を介して接続し、更に、該ベースと接地とを抵抗13とコンデンサ14との並列回路を介して接続するように構成したものである。

【0017】

そして、同図の点線で囲まれた回路15は前記整流回路であって、ダイオード16のカソードを接地に、アノードをダイオード17のカソードにそれぞれ接続し、該ダイオード17のアノードと抵抗18とをコンデンサ19との並列回路を介して接地すると共に、ソース接地とするFET20のゲートと前記ダイオード17のアノードとを接続し、更に、該FET20のドレインと前記電源Vccとを抵抗21と抵抗22との直列回路とを介し接続すると共に、前記抵抗21と抵抗22との接続中間点と前記トランジスタ3のベースとを抵抗23を介して接続し、前記ダイオード17のカソードと前記トランジスタ10のコレクタとをコンデンサ24を介して接続するように構成したものである。

尚、コンデンサ26、27はバイパスコンデンサである。

【0018】

次にこのような構成の水晶発振器の動作について説明する。

前記発振回路1の前記トランジスタ3は、前記トランジスタ10とカスケード接続構成にしたものであり、前記トランジスタ3のコレクタ電流の値が前記トランジスタ10のコレクタ電流の設定値にのみ依存する為、トランジスタ3のベース電流による影響を受けることなく広範囲の設定条件よりその値を決定することが可能である。

そして、前記発振回路1の設定条件に基づき前記トランジスタ3のコレクタより出力された所望の周波数信号は、次段の前記増幅回路9に供給され所要のレベルに増幅された後、前記トランジスタ10のコレクタより出力され、更に、前記コンデンサ24を介し前記整流回路15に供給される。

【0019】

ここで、前記整流回路に供給された前記信号のプラス側半サイクルの信号は、前記ダイオード16を通過するが、この時、前記コンデンサ24を前記ダイオード16のアノード側が低電位となるよう電荷をチャージし、逆のマイナス側半サイクルの信号は、前記ダイオード17を介して流れ、結果的にそのアノードと接地間に負極性の電位が生じる。

即ち、該電位は、前記マイナス側半サイクルの信号による電位と前記コンデンサ24のチャージ電荷により発生する電位とが加わった値となる。

【0020】

そして更に、前記励振電流のレベルが増加した場合、これによる前記負極性の電位の絶対値の増加に伴ない、前記FET20のゲート・ソース間に電圧降下が生じてドレイン電流が減少することにより、前記トランジスタ3のベースバイアス電圧が上昇する為、これによるベース電流の増加によりエミッタ電圧が上昇し、該トランジスタ3のベース・コレクタ間電圧が降下する。

予め、前記トランジスタ3の動作点を飽和領域近傍であって、信号の一部が飽和領域に達するよう設定しておくことで、前記トランジスタ3のベース・コレクタ間の電圧の降下に伴い前記トランジスタ3の動作点が飽和領域に近づく為、励振レベルが低下することになる。

【0021】

一方、前記発振回路1の出力信号のレベルが低下した場合は上記で説明した動作と逆の動作である為、説明を省略する。

従って、上記の動作を繰り返し行うことにより、水晶発振器はその設定条件に基づき安定なレベル信号を出力する。

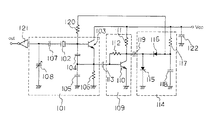

更に、図2に示す回路は本発明に基づく水晶発振器回路の他の実施例である。

該水晶発振器の構成及び動作について以下に説明する。

尚、図1に示す水晶発振器と同一構成の部分については同一の符号を付与すると共に、その説明を省略する。

【0022】

図2に於いて発振回路1は、トランジスタ3に前記抵抗23抵抗28とのベースバイアス回路を接続するよう構成したものである。

同図に於いて増幅回路9はトランジスタ10のベースをコンデンサ14を介して接地するよう構成したものである。

同図に於いて整流回路15はトランジスタ29のコレクタを抵抗30を介して電源Vccに接続すると共に、該トランジスタ29のエミッタを抵抗31を介して接地し、更に、該トランジスタ29のベースと前記トランジスタ10のコレクタとを前記コンデンサ24を介して接続すると共に、該ベースと接地との間にダイオード32をカソードが該ベース側に接続されるよう構成したものである。

【0023】

そして、このような構成の前記発振回路1は出力信号が増幅回路9を介して整流回路15に供給された後、該出力信号のプラス半サイクルの信号成分のみが前記整流回路15より直流信号化され前記トランジスタ10のベースに帰還供給されるよう動作する。その為、該出力信号のレベルが上昇した場合、前記トランジスタ29の出力が入力に対して位相が逆転することより、前記出力信号のレベルの上昇と共に前記整流回路15より前記トランジスタ10のベースに供給される直流電圧が降下し、更に、該ベース電位の降下と共に前記トランジスタ3のコレクタ電圧が降下する。予め、前記トランジスタ3の動作点を飽和領域近傍であって、信号の一部が飽和領域に達するよう設定しておくことで、前記トランジスタ10のコレクタ電圧の降下に伴い前記トランジスタ3の動作点が飽和領域に近づく為、励振レベルが低下する。一方、前記出力レベルが低下した場合は上記で説明した動作と逆の動作である為、説明を省略する。

【0024】

上記のような構成とすることにより、励振電流を低レベルに保つよう制御してもトランジスタ3には大きなコレクタ電流を流すことが可能である。

そして、例えば、図4に示すような雑音指数を呈するトランジスタを用いた場合、雑音が最も小さくなるB点近傍の値となるように前記トランジスタ10とその周辺回路により前記トランジスタ3のコレクタ電流を設定すれば十分に優れた特性が得られ、更に、図4から明らかなようにB点は極小値であるからAGC機能により前記コレクタ電流が変化しても雑音指数の変化量が小さく、結果、急激な雑音特性の悪化が生じない。

以上、本発明の一実施例では基本波発振とするコルピッツ発振回路を用いて水晶発振器を構成したが本発明はこれに限定されるものでなく、オーバートーン発振回路を用いて水晶発振器を構成した場合であっても構わない。

【0025】

更に、以上本発明を水晶振動子を用いた発振器を例に説明したが、本発明はこれに限定されるものではなく、 水晶以外の他の圧電振動子を用いたものに適用してもよいことは明らかである。

【0026】

【発明の効果】

以上説明したように本発明に基づく圧電発振器は、上述したように構成したものであるから、励振電流を低レベルに保つよう制御した場合であってもトランジスタのコレクタ電流を大電流に保つ、且つ、該トランジスタを雑音指数が最も小さくなる動作点に設定することが可能となる為、雑音特性、及び、エージング特性が共に優れた圧電発振器が実現される効果を奏する。

【図面の簡単な説明】

【図1】本発明に基づく水晶発振器の一実施例の回路図を示すものである。

【図2】本発明に基づく水晶発振器の他の実施例の回路図を示すものである。

【図3】従来の水晶発振器の回路図を示すものである。

【図4】トランジスタのコレクタ電流に対する雑音指数特性を示す図である。

【符号の説明】

1、101発振回路、2、102水晶振動子、3、10、29、103、110トランジスタ、4、5、7、14、19、24、104、105、107、113、118、119、121コンデンサ、6、11、12、13、18、21、22、23、28、30、31、106、111、112、117、120抵抗、8、108トリマーコンデンサ、9、109増幅回路、15、114整流回路、16、17、32、115、116ダイオード、20、117FET、25、121バッファ回路、26、27、122バイパスコンデンサ

Claims (3)

- 圧電振動子と発振用トランジスタとを含むコルピッツ型発振器と、前記発振用トランジスタの出力を増幅し前記発振用トランジスタのコレクタにエミッタが接続された第二のトランジスタと、該第二のトランジスタの出力を整流する整流手段とを備え、該整流手段の出力を前記第二のトランジスタのベースに帰還することによって前記圧電振動子に流れる励振電流を一定に保つ圧電発振器であって、前記発振用トランジスタの動作点が飽和領域近傍となるよう前記第二のトランジスタのコレクタ電圧を設定し、前記励振電流が大きくなったときは前記第二のトランジスタのベースバイアス電圧が降下し、前記発振用トランジスタの動作点が飽和領域に近づくように前記コレクタ電圧が降下するものであり、前記励振電流が小さくなったときは前記第二のトランジスタのベースバイアス電圧が上昇し、前記発振用トランジスタの動作点が飽和領域から遠ざかるように前記コレクタ電圧が上昇するものであって、前記励振電流を低レベルに保つよう前記コレクタ電圧を制御したことを特徴とする圧電発振器。

- 前記第二のトランジスタのベースを交流的に接地し、第二のトランジスタのコレクタを電源に接続したことを特徴とする請求項1記載の圧電発振器。

- 前記発振用トランジスタの雑音指数が最小値近傍の値となるよう前記第二のトランジスタのコレクタ電流を設定したことを特徴とする請求項1乃至請求項2記載の圧電発振器。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04922799A JP4042246B2 (ja) | 1999-02-26 | 1999-02-26 | 圧電発振器 |

| US09/506,466 US6271734B1 (en) | 1999-02-26 | 2000-02-17 | Piezoelectric oscillator |

| DE10009079A DE10009079B4 (de) | 1999-02-26 | 2000-02-25 | Piezoelektrischer Oszillator |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP04922799A JP4042246B2 (ja) | 1999-02-26 | 1999-02-26 | 圧電発振器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000252749A JP2000252749A (ja) | 2000-09-14 |

| JP2000252749A5 JP2000252749A5 (ja) | 2005-08-25 |

| JP4042246B2 true JP4042246B2 (ja) | 2008-02-06 |

Family

ID=12825043

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP04922799A Expired - Fee Related JP4042246B2 (ja) | 1999-02-26 | 1999-02-26 | 圧電発振器 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6271734B1 (ja) |

| JP (1) | JP4042246B2 (ja) |

| DE (1) | DE10009079B4 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001077628A (ja) * | 1999-09-01 | 2001-03-23 | Alps Electric Co Ltd | 水晶発振回路 |

| US8643445B1 (en) * | 2012-08-08 | 2014-02-04 | Texas Instruments Incorporated | Crystal oscillator circuit |

| JP6560077B2 (ja) * | 2015-09-18 | 2019-08-14 | 新日本無線株式会社 | 発振回路 |

| JP7028567B2 (ja) * | 2017-03-24 | 2022-03-02 | 日本電波工業株式会社 | 水晶発振器 |

| JP2018164124A (ja) * | 2017-03-24 | 2018-10-18 | 日本電波工業株式会社 | 水晶発振器 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3213390A (en) * | 1962-08-13 | 1965-10-19 | Varo | Crystal oscillator with amplitude control loop |

| DE1278524B (de) * | 1965-04-09 | 1968-09-26 | Standard Elektrik Lorenz Ag | Regelbare Transistorstufe zur Leistungsverstaerkung von Signalen |

| US3832653A (en) * | 1973-08-20 | 1974-08-27 | Westinghouse Electric Corp | Low noise rf signal generator |

| US3982210A (en) * | 1975-10-22 | 1976-09-21 | Motorola, Inc. | Automatic gain control circuit for a crystal oscillator |

| JPS5467358A (en) * | 1977-11-08 | 1979-05-30 | Kinsekisha Lab Ltd | Bias circuit for piezooelectric oscillator |

-

1999

- 1999-02-26 JP JP04922799A patent/JP4042246B2/ja not_active Expired - Fee Related

-

2000

- 2000-02-17 US US09/506,466 patent/US6271734B1/en not_active Expired - Lifetime

- 2000-02-25 DE DE10009079A patent/DE10009079B4/de not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| DE10009079B4 (de) | 2011-02-17 |

| DE10009079A1 (de) | 2000-08-31 |

| JP2000252749A (ja) | 2000-09-14 |

| US6271734B1 (en) | 2001-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100713169B1 (ko) | 스위칭 전원장치 | |

| JPH0669002B2 (ja) | 高周波増幅器 | |

| US6111466A (en) | Amplifier with feedback to provide bias adjustment | |

| JP4042246B2 (ja) | 圧電発振器 | |

| JP4271634B2 (ja) | 水晶発振回路 | |

| JP4407003B2 (ja) | 圧電発振器 | |

| JP3444468B2 (ja) | Dc−dcコンバータ | |

| JP2003134799A (ja) | 電圧供給回路 | |

| US5115211A (en) | Piezo-electric oscillator | |

| JP4042207B2 (ja) | 圧電発振器 | |

| JPS6260844B2 (ja) | ||

| US5825255A (en) | Oscillator starting circuit | |

| JP2000201025A (ja) | 発振器 | |

| JPH09275677A (ja) | 直流入力及び直流出力変換器 | |

| JP4175941B2 (ja) | 水晶発振回路 | |

| JPH0555828A (ja) | 発振器 | |

| JPH07240629A (ja) | 電圧制御圧電発振器 | |

| JP2576193B2 (ja) | 発振回路 | |

| JP2007028504A (ja) | 圧電発振器 | |

| JPH04407B2 (ja) | ||

| JP4190874B2 (ja) | 圧電発振回路 | |

| JPH0563442A (ja) | 発振回路 | |

| JPH0446870Y2 (ja) | ||

| JP2004304347A (ja) | 圧電発振器 | |

| JP2005260797A (ja) | 電圧制御発振器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050215 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070308 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070417 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070612 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20070612 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071023 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071105 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101122 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111122 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111122 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111122 Year of fee payment: 4 |

|

| R371 | Transfer withdrawn |

Free format text: JAPANESE INTERMEDIATE CODE: R371 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111122 Year of fee payment: 4 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111122 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121122 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121122 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131122 Year of fee payment: 6 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |