JP3745316B2 - 半導体集積回路及びその製造方法 - Google Patents

半導体集積回路及びその製造方法 Download PDFInfo

- Publication number

- JP3745316B2 JP3745316B2 JP2002183471A JP2002183471A JP3745316B2 JP 3745316 B2 JP3745316 B2 JP 3745316B2 JP 2002183471 A JP2002183471 A JP 2002183471A JP 2002183471 A JP2002183471 A JP 2002183471A JP 3745316 B2 JP3745316 B2 JP 3745316B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- inductor

- metal layer

- laminated film

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 94

- 238000004519 manufacturing process Methods 0.000 title claims description 22

- 230000005294 ferromagnetic effect Effects 0.000 claims description 108

- 239000002184 metal Substances 0.000 claims description 85

- 229910052751 metal Inorganic materials 0.000 claims description 85

- 239000010949 copper Substances 0.000 claims description 46

- 239000000758 substrate Substances 0.000 claims description 45

- 238000010030 laminating Methods 0.000 claims description 12

- 238000000034 method Methods 0.000 claims description 11

- 238000009792 diffusion process Methods 0.000 claims description 9

- 230000004888 barrier function Effects 0.000 claims description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 2

- 229910052782 aluminium Inorganic materials 0.000 claims description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 2

- 229910052802 copper Inorganic materials 0.000 claims description 2

- 238000000059 patterning Methods 0.000 claims description 2

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims 2

- 229910052759 nickel Inorganic materials 0.000 claims 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 12

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 8

- 238000012986 modification Methods 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000001039 wet etching Methods 0.000 description 6

- 239000004642 Polyimide Substances 0.000 description 4

- 239000003302 ferromagnetic material Substances 0.000 description 4

- 230000005291 magnetic effect Effects 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 238000009713 electroplating Methods 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 229910052681 coesite Inorganic materials 0.000 description 2

- 229910052906 cristobalite Inorganic materials 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910052682 stishovite Inorganic materials 0.000 description 2

- 229910052905 tridymite Inorganic materials 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000002500 effect on skin Effects 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 230000001771 impaired effect Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/20—Inductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5227—Inductive arrangements or effects of, or between, wiring layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F17/00—Fixed inductances of the signal type

- H01F17/0006—Printed inductances

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F27/00—Details of transformers or inductances, in general

- H01F27/34—Special means for preventing or reducing unwanted electric or magnetic effects, e.g. no-load losses, reactive currents, harmonics, oscillations, leakage fields

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F41/00—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties

- H01F41/02—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets

- H01F41/04—Apparatus or processes specially adapted for manufacturing or assembling magnets, inductances or transformers; Apparatus or processes specially adapted for manufacturing materials characterised by their magnetic properties for manufacturing cores, coils, or magnets for manufacturing coils

- H01F41/041—Printed circuit coils

- H01F41/046—Printed circuit coils structurally combined with ferromagnetic material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Coils Or Transformers For Communication (AREA)

- Manufacturing Cores, Coils, And Magnets (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Description

【発明の属する技術分野】

本発明はインダクタを備えた半導体集積回路及びその製造方法に関し、特に、インダクタのインダクタンス及びQ値の向上を図った半導体集積回路及びその製造方法に関する。

【0002】

【従来の技術】

図14は従来の半導体集積回路を示す平面図であり、図15は図14に示すE−E線による断面図である。図14及び図15に示すように、この従来の半導体集積回路においては、半導体基板(図示せず)上に多層配線層101が設けられており、この多層配線層101の最上層102に、スパイラルインダクタであるインダクタ103が設けられている。即ち、多層配線層101中に設けられたSiO2からなる絶縁層104上に、1本の配線が渦巻状に配置されたインダクタ103が設けられており、このインダクタ103を覆うようにSiO2からなる絶縁層105が設けられている。そして、絶縁層105上にはポリイミドからなる絶縁層106が設けられている。なお、図14においては、絶縁層105及び106は図示を省略されている。

【0003】

そして、インダクタ103を構成する配線は、銅又はアルミニウムからなる配線本体層107の上面及び下面に、TiW層108が被覆されて形成されている。このように、インダクタ103を多層配線層101の最上層102に設ける理由は、インダクタ103と半導体基板との間の寄生容量を可及的に少なくすると共に、インダクタ103の配線の厚さを可及的に厚くして直列抵抗を下げ、インダクタ103のQ値を向上させるためである。

【0004】

しかしながら、この従来の半導体集積回路においては、以下に示す問題点がある。インダクタ103を多層配線層101の最上層102に配置しても、最上層102の厚さは最大で10μm程度であるため、インダクタ103の厚さは数μmが上限である。このため、インダクタンスの損失が大きく、Q値が5乃至10程度と低かった。また、例えば10nHのインダクタンスを得るためには、インダクタ103の大きさを、一辺の長さが200乃至300μmの正方形のスパイラル(渦巻)とする必要があり、インダクタ103の占有面積が極めて大きくなった。これにより、半導体集積回路の微細化が阻害されていた。

【0005】

そこで、実開平3−28758号公報には、インダクタの上層に強磁性体層を設ける技術が開示されている。実開平3−28758号公報において、この強磁性体層は、配線がなす渦巻の内部に相当する領域の直上域に設けられている。また、実開平4−63653号公報には、インダクタの上方又は下方に、強磁性体層を設ける技術が開示されている。実開平4−63653号公報においては、基板の表面に垂直な方向から見て、強磁性体層はインダクタを覆うように設けられている。更に、特開昭61−161747号公報にも、インダクタの上方に強磁性体層を設ける技術が開示されている。特開昭61−161747号公報には、強磁性体層を設けることにより、インダクタのインダクタンスが増大すると記載されている。

【0006】

【発明が解決しようとする課題】

しかしながら、上述の従来の技術には以下に示すような問題点がある。実開平3−28758号公報、実開平4−63653号公報及び特開昭61−161747号公報に記載されている半導体集積回路においても、インダクタのインダクタンス及びQ値の大きさが不十分であり、所定のインダクタンスを得るためには大きな面積のインダクタを必要とする。この結果、半導体集積回路の微細化を十分に図ることができない。

【0007】

本発明はかかる問題点に鑑みてなされたものであって、インダクタのインダクタンス及びQ値が高く、小型化が可能な半導体集積回路及びその製造方法を提供することを目的とする。

【0008】

【課題を解決するための手段】

本発明に係る半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有することを特徴とする。

本発明に係る他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有することを特徴とする。

【0009】

本発明においては、インダクタの内部に、第1の金属層、強磁性体層及び第2の金属層からなる積層膜を設けている。そして、強磁性体層がインダクタの磁芯として作用し、インダクタのインダクタンス及びQ値を向上させることができる。また、強磁性体層を第1及び第2の金属層で被覆することにより、強磁性体層を形成する材料が半導体集積回路内の他の領域に拡散することを防止すると共に、この材料が半導体集積回路の製造装置を汚染することを防止できる。更に、強磁性体層の下面をインダクタの上面よりも低くし、強磁性体層の上面をインダクタの下面よりも高くすることにより、強磁性体層の少なくとも一部がインダクタと同層になり、インダクタのインダクタンス及びQ値をより一層向上させることができる。更にまた、積層膜の下面、即ち第1の金属層の下面が、インダクタの下面と同一高さ又はそれよりも低く、積層膜の上面、即ち第2の金属層の上面が、インダクタの上面と同一高さ又はそれよりも高いため、積層膜の上面及び下面とインダクタとの間に寄生容量が発生せず、インダクタのインダクタンス及びQ値をより一層向上させることができる。

【0010】

また、本発明に係る半導体集積回路においては、基板の表面に垂直な方向から見て、前記強磁性体層が複数の部分に分割されていてもよい。これにより、強磁性体層内に渦電流が流れることを抑制でき、渦電流によるインダクタンスの損失を抑制することができる。

【0011】

本発明に係る更に他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記基板の表面に垂直な方向から見て、前記積層膜が前記インダクタと重ならずに前記インダクタを囲むように設けられていることを特徴とする。

【0012】

本発明に係る更に他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、前記積層膜と同層に設けられたパッドと、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記パッドの積層構造が前記積層膜の積層構造と同じであることを特徴とする。

【0013】

本発明に係る更に他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記金属層がバリアメタル層を有することを特徴とする。

【0014】

本発明に係る更に他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、前記積層膜と同層に設けられたパッドと、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記金属層がバリアメタル層を有することを特徴とする。

【0015】

本発明に係る更に他の半導体集積回路は、基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層の下面を覆う第1の金属層と、前記強磁性体層の上面を覆う第2の金属層と、を有し、前記インダクタは前記第1の金属層及び前記第2の金属層が積層されたものであることを特徴とする。

【0016】

本発明に係る更に他の半導体集積回路は、基板上に設けられたスパイラル形状のインダクタと、前記基板の表面に垂直な方向から見て前記インダクタを構成する配線によって囲まれる領域に設けられた第1の金属層と、この第1の金属層上に選択的に設けられた強磁性体層と、この強磁性体層の上面及び側面を覆うように設けられた第2の金属層と、を有し、前記第1の金属層の下面は前記インダクタの下面と同一高さ又はそれよりも低く、前記第2の金属層の上面は前記インダクタの上面と同一高さ又はそれよりも高く、前記強磁性体層の下面は前記インダクタの上面よりも低く、前記インダクタの上面は前記インダクタの下面よりも高く、前記インダクタは、前記第1の金属層及び前記第2の金属層が積層されたものであることを特徴とする。

【0017】

本発明に係る更に他の半導体集積回路は、基板上に設けられたスパイラル形状のインダクタと、前記基板の表面に垂直な方向から見て前記インダクタを構成する配線によって囲まれる領域に設けられた第1の金属層と、この第1の金属層上に選択的に設けられた強磁性体層と、この強磁性体層の上面及び側面を覆うように設けられた第2の金属層と、を有し、前記第1の金属層の下面は前記インダクタの下面と同一高さ又はそれよりも低く、前記第2の金属層の上面は前記インダクタの上面と同一高さ又はそれよりも高く、前記強磁性体層の下面は前記インダクタの上面よりも低く、前記インダクタの上面は前記インダクタの下面よりも高いことを特徴とする。

【0019】

本発明に係る半導体集積回路の製造方法は、基板上に第1の金属層を形成する工程と、この第1の金属層上に選択的に強磁性体層を形成する工程と、この選択的に形成された強磁性体層を覆うように第2の金属層を形成する工程と、前記第1及び第2の金属層を選択的に除去してパターニングし、前記第1の金属層、前記強磁性体層及び前記第2の金属層が積層されてなる積層膜を形成すると共にこの積層膜と同層でありこの積層膜を囲むように配置されたインダクタを形成する工程と、を有することを特徴とする。

【0020】

また、本発明に係る半導体集積回路の製造方法は、前記第1の金属層を形成する工程の前に、前記基板の表面における前記積層膜を形成する予定の領域にその深さが前記第1の金属層と前記強磁性体層の合計膜厚よりも小さい凹部を形成する工程を有していてもよい。

【0022】

【発明の実施の形態】

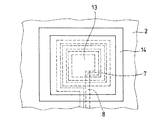

以下、本発明の実施例について添付の図面を参照して具体的に説明する。先ず、本発明の第1の実施例について説明する。図1は本実施例に係る半導体集積回路を示す平面図であり、図2(a)は図1に示すA−A線による断面図であり、(b)は図1に示すB−B線による断面図である。

【0023】

図1並びに図2(a)及び(b)に示すように、本実施例の半導体集積回路においては、半導体基板(図示せず)上に多層配線層1が設けられている。多層配線層1は複数の層が積層されて形成されており、この多層配線層1の最上層である絶縁層2上に、スパイラルインダクタであるインダクタ3が設けられている。インダクタ3は1本の配線3aがスパイラル状(渦巻状)に配置されて形成されている。絶縁層2の膜厚は例えば1.5μmであり、インダクタ3の外形は例えば一辺の長さが100μmの正方形であり、内形は例えば一辺の長さが40乃至60μmの正方形であり、配線3aの幅は例えば5乃至10μmであり、インダクタ3の巻き数は例えば3である。なお、図2(a)においては、便宜上、配線3aは片側2本ずつしか示していない。また、絶縁層2の下方には絶縁層4が設けられている。絶縁層2及び4は例えばSiO2により形成されている。

【0024】

また、絶縁層2におけるインダクタ3から離れた領域には配線5が埋め込まれており、絶縁層2における配線5の上方に相当する部分には、ビア6が形成されている。配線3aの一端は、インダクタ3の外側からこのビア6まで引き出され、ビア6を介して配線5に接続されている。また、絶縁層2におけるインダクタ3内の領域にはビア7が形成されており、配線3aの他端はこのビア7を介して、インダクタ3よりも下層に配置された配線8に接続されている。即ち、配線5、ビア6、配線3aにおける渦巻の外側、配線3aにおける渦巻の内側、ビア7及び配線8がこの順に接続されている。

【0025】

配線3a、5及び8は、下層側から順に、TiW層9、Cu層10、Cu層11及びTiW層12が積層されて形成されている。TiW層9及び12の膜厚は例えば0.05乃至0.1μmであり、Cu層10及び11の膜厚は例えば0.2乃至0.4μmであり、配線3a、5及び8の膜厚は例えば0.5乃至1.0μmである。なお、Cu層10及び11は配線本体層17を形成している。また、TiW層9及び12は配線本体層17のバリアメタルであり、TiW層9はCu層とSiO2からなる絶縁層2との間の密着性を向上させる機能がある。

【0026】

更に、絶縁層2上におけるインダクタ3の内部領域、即ち、配線3aがなす渦巻の内部(以下、内部領域13という)には、積層膜14が設けられている。内部領域13は例えば一辺の長さが40乃至60μmの正方形の領域であり、積層膜14の形状は、例えば一辺の長さが30乃至50μmの正方形である。積層膜14の下面及び配線3aの下面は同一平面上にあり、絶縁層2の上面に接している。この積層膜14においては、下層側から順に、TiW層9及びCu層10が設けられている。そして、Cu層10上における中央部には、Niからなる強磁性体層15が設けられており、この強磁性体層15の側面及び上面を覆うように、Cu層11及びTiW層12が設けられている。強磁性体層15の膜厚は例えば3乃至5μmである。

【0027】

このため、強磁性体層15の下面は配線層3aの上面よりも低くなっており、強磁性体層15の上面は配線層3aの下面よりも高くなっている。従って、強磁性体層15の下部は配線層3aと同層となっている。また、強磁性体層15の上面は配線層3aの上面よりも高くなっており、従って、積層膜14の上面は配線層3aの上面よりも高くなっている。

【0028】

更にまた、インダクタ3及び積層膜14を覆うように、例えばポリイミドからなる絶縁層16が設けられている。なお、図1においては、絶縁層16は図示を省略されている。なお、半導体基板(図示せず)の表面には、トランジスタ等の素子が形成されていてもよい。

【0029】

なお、本実施例においては、渦巻状の配線の巻き数が3である例を示したが、本発明はこれに限定されず、4以上又は2以下であってもよく、1以下であってもよい。また、渦巻の形状は正方形に限定されず、例えば、正方形以外の多角形又は円形であってもよい。更に、上述の各部の寸法は一例であり、本発明はこれに限定されない。更にまた、強磁性体層はNi以外の強磁性体、例えばCoにより形成されていてもよく、配線はCu以外の導電性材料、例えばAlにより形成されていてもよい。更にまた、絶縁膜2はSiONにより形成されていてもよい。

【0030】

次に、本実施例に係る半導体集積回路の製造方法について説明する。図3(a)乃至(e)は本実施例に係る半導体集積回路の製造方法をその工程順に示す断面図であり、図2(a)の一部に相当する部分を示す。先ず、図3(a)に示すように、半導体基板上に多層配線層1(図2(a)参照)を形成する。このとき、多層配線層1の最上層をなす絶縁層2の内部に、配線5(図2(b)参照)及び配線8(図1参照)を埋め込み、絶縁層2における配線5及び8の直上域に、エッチングにより夫々ビア6及び7(図1参照)を形成する。このとき、配線5及び8が、夫々ビア6及び7を形成する際のエッチングストッパ層となる。そして、絶縁膜2上の全面に、スパッタリング法によりTiW層9を形成する。次に、電気めっき法により、TiW層9上にCu層10を形成する。

【0031】

次に、図3(b)に示すように、Cu層10上にレジスト18を形成し、このレジスト18における後の工程において強磁性体層15を形成する予定の領域に、開口部18aを形成する。開口部18aにおいてはCu層10が露出している。

【0032】

次に、図3(c)に示すように、レジスト18をマスクとして、Niの電気めっきを行い、Cu層10上における開口部18aに相当する領域にNiからなる強磁性体層15を形成する。

【0033】

次に、図3(d)に示すように、レジスト18を除去し、Cu層10及び強磁性体層15上にCu層11を形成する。そして、このCu層11上にTiW層12を形成する。

【0034】

次に、図3(e)に示すように、TiW層12上にレジスト(図示せず)を形成し、このレジストをマスクとして、TiW層9、Cu層10、Cu層11及びTiW層12をウエットエッチングして選択的に除去してパターニングする。Cu層10及び11のウエットエッチングは硫酸と過酸化水素との混合液である硫酸過水を使用すればよく、TiW層9及び12のウエットエッチングは過酸化水素水により行うことができる。

【0035】

これにより、半導体基板の表面に垂直な方向、即ち、絶縁層2の表面に垂直な方向から見て、正方形状となる積層膜14と、この積層膜14の周囲に渦巻状に配置され、ビア6及び7により夫々配線5及び8に接続された配線3aとを形成する。積層膜14はTiW層9、Cu層10、強磁性体層15、Cu層11及びTiW層12が積層されて構成されており、配線3aはTiW層9、Cu層10、Cu層11及びTiW層12が積層されて構成されている。そして、絶縁層2上の全面に、積層膜14及び配線3aを埋め込むように、ポリイミドからなる絶縁層16を形成する。これにより、本実施例に係る半導体集積回路を製造することができる。

【0036】

本実施例においては、配線3aを渦巻状に配置することにより、スパイラルインダクタであるインダクタ3が形成されている。そして、このインダクタ3の内部領域13に設けられた強磁性体層15が、インダクタ3の磁芯として作用し、インダクタ3のインダクタンス及びQ値を向上させることができる。実際に実験した結果、図1に示す本実施例の半導体集積回路は、図14に示す従来の半導体集積回路と比較して、Q値が約2倍になった。

【0037】

また、強磁性体層15をCu層9及び10で被覆することにより、強磁性体層15を形成するNiが半導体集積回路内の他の領域に拡散することがなく、また、半導体集積回路の製造工程において、製造装置を汚染することがない。

【0038】

更に、強磁性体層15の下部は配線層3aと同層となっているため、インダクタ3のインダクタンス及びQ値をより一層向上させることができる。更にまた、積層膜14の下面が配線3aの下面と同一平面にあり、積層膜14の上面が配線層3aの上面よりも高くなっているため、積層膜14の上面及び下面と配線3aとの間に寄生容量が発生せず、インダクタ3のインダクタンス及びQ値をより一層向上させることができる。

【0039】

次に、前述の第1の実施例の変形例について説明する。本変形例に係る半導体集積回路を示す平面図は図1と同様な図である。また、図4(a)及び(b)は本変形例に係る半導体集積回路を示す断面図であり、(a)は図1に示すA−A線による断面図に相当し、(b)は図1に示すB−B線による断面図に相当する。図4(a)及び(b)に示すように、本変形例においては、絶縁層2における積層膜14の直下域に金属層19が設けられており、絶縁層2における金属層19の直上域に開口部2aが形成されている。そして、この開口部2aに、絶縁膜14の下部が埋め込まれている。金属層19は配線5と同層であり、同じ材料により形成されている。金属層19は配線5と同時に形成され、開口部2aは、ビア6及び7と同時に形成される。開口部2aの形成に際しては、金属層19がエッチングストッパ層となる。本変形例における上記以外の構成及び製造方法は、前述の第1の実施例と同様である。

【0040】

本変形例においては、前述の第1の実施例と比較して、積層膜14を配線3aに対して相対的に低くすることができるため、強磁性体層15における配線3aと同層となる部分が拡大する。これにより、インダクタ3のインダクタンス及びQ値をより一層向上させることができる。

【0041】

次に、本発明の第2の実施例について説明する。図5は、本実施例に係る半導体集積回路を示す平面図である。図5に示すように、本実施例に係る半導体集積回路においては、前述の第1の実施例と比較して、積層膜14が複数の部分14aから構成されている。絶縁層2の表面に垂直な方向から見て、部分14aは例えば1辺の長さが5乃至10μmの矩形であり、インダクタ3の内部領域13に例えばマトリクス状に配列されている。本実施例における上記以外の構成は前述の第1の実施例と同様である。

【0042】

本実施例においては、前述の第1の実施例と比較して、積層膜14が複数の部分14aに分割されているため、積層膜14と配線3aとの間の容量を低減できると共に、積層膜14内に渦電流が発生することを抑制できる。これにより、インダクタ3のインダクタンス及びQ値がより一層向上する。

【0043】

次に、本発明の第3の実施例について説明する。図6は、本実施例に係る半導体集積回路を示す平面図である。図6に示すように、本実施例に係る半導体集積回路においては、前述の第1の実施例と比較して、インダクタ3が絶縁層2内に埋め込まれている。従って、絶縁層2にビア6(図1参照)は形成されておらず、配線3aは配線5(図1参照)に同層で接続されている。また、インダクタ3の内部領域13には積層膜が設けられておらず、絶縁層2上におけるインダクタ3の周囲に相当する領域に、インダクタ3の直上域を囲むように積層膜14が環状に設けられている。本実施例における上記以外の構成は前述の第1の実施例と同様である。なお、本実施例においては、積層膜14はインダクタ3の上方に設けられているが、積層膜14をインダクタ3の下方に配置してもよい。

【0044】

本実施例においては、前述の第1の実施例と比較して、積層膜14がインダクタ3の周囲に設けられているため、積層膜14と配線3aとの間の容量を低減すると共に、積層膜14内に渦電流が流れることを抑制することができる。これにより、インダクタンスの損失を低減することができる。なお、強磁性体層15はインダクタ3が発生させる磁力線の経路に配置されていればよいため、強磁性体層15がインダクタ3の周囲に設けられていても、内部領域13に設けられている場合と比較して、強磁性体によるインダクタンスの向上効果が損なわれることはない。

【0045】

次に、本発明の第4の実施例について説明する。図7は、本実施例に係る半導体集積回路を示す平面図である。図7に示すように、本実施例に係る半導体集積回路においては、前述の第3の実施例と比較して、積層膜14の一部が除去されて断絶部14bが形成されている。また、本実施例においては、インダクタ3を絶縁層2内ではなく、前述の第1の実施例と同様に絶縁層2上に形成し、インダクタ3における渦巻の外側から引き出された配線3aが、断絶部14bを通過するようにしてもよい。本実施例における上記以外の構成は前述の第1の実施例と同様である。

【0046】

本実施例においては、前述の第3の実施例と比較して、積層膜14に断絶部14bが形成されているため、積層膜14を周回するような渦電流が発生することがない。このため、渦電流による損失をより一層低減し、Q値を向上させることができる。

【0047】

次に、本発明の第5の実施例について説明する。図8は、本実施例に係る半導体集積回路を示す平面図である。図8に示すように、本実施例に係る半導体集積回路においては、前述の第3の実施例と同様に、インダクタ3が絶縁層2内に埋め込まれている。また、インダクタ3の内部領域13には積層膜が設けられておらず、絶縁層2上におけるインダクタ3及びその周囲の領域の直上域に相当する領域に、複数の矩形部分14cからなる積層膜14が設けられている。積層膜14の矩形部分14cの幅は例えば10μmである。また、絶縁層2の表面に垂直な方向から見て、矩形部分14cはその長手方向が渦巻形のインダクタ3の中心から周囲に向かう方向に沿うように放射状に配置されている。本実施例における上記以外の構成は前述の第1の実施例と同様である。なお、本実施例においては、積層膜14はインダクタ3の上方に設けられているが、積層膜14をインダクタ3の下方に配置してもよい。

【0048】

本実施例においては、前述の第1の実施例と比較して、積層膜14を複数の矩形部分14cに分割しているため、積層膜14と配線3aとの間の容量を低減すると共に、積層膜14がインダクタ3の周回方向において断続的に配置されているため、積層膜14内に渦電流が流れることを抑制することができる。これにより、インダクタンスの損失を低減することができる。

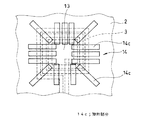

【0049】

次に、本発明の第6の実施例について説明する。図9は本実施例に係る半導体集積回路を示す平面図であり、図10は図9に示すC−C線による断面図である。図9及び図10に示すように、本実施例の半導体集積回路においては、半導体基板(図示せず)上に多層配線層1が設けられている。多層配線層1は複数の層が積層されて形成されており、この多層配線層1の最上層である絶縁層2内に、スパイラルインダクタであるインダクタ3が設けられている。インダクタ3は1本の配線3aがスパイラル状(渦巻状)に配置されて形成されており、配線3aはTiW層22、Cu層23及びTiW層24がこの順に積層されて形成されている。前述の第1の実施例と同様に、インダクタ3の巻き数は例えば3であるが、図10においては、便宜上、配線3aは片側2本ずつしか示していない。

【0050】

また、絶縁層2上におけるインダクタ3の内部領域13の直上域に相当する領域には、積層膜14が設けられている。積層膜14の構成は前述の第1の実施例と同様である。

【0051】

更に、絶縁層2上におけるインダクタ3の形成領域から外れた領域には、パッド21が形成されている。パッド21は、例えば、フリップチップのバンプが形成されるものである。絶縁層2の表面に垂直な方向から見て、パッド21の形状は例えば八角形であり、その外径は例えば100μmである。パッド21は、積層膜14と同様に、TiW層9及びCu層10が積層され、Cu層10上の中央部分にNiからなる強磁性体層15が積層され、強磁性体層15の上面及び側面を覆うように、Cu層11及びTiW層12が積層されて形成されている。即ち、パッド21は積層膜14と同層に形成されている。

【0052】

次に、本実施例に係る半導体集積回路の製造方法について説明する。図11(a)乃至(e)は本実施例に係る半導体集積回路の製造方法をその工程順に示す断面図である。先ず、図10に示すように、半導体基板上に多層配線層1を形成する。このとき、SiO2からなる絶縁層4上に、TiW層22、Cu層23及びTiW層24をこの順に積層し、これらの積層膜をパターニングして、渦巻状の配線3aを形成する。即ち、配線3aはTiW層22、Cu層23及びTiW層24がこの順に積層されて形成されている。これにより、スパイラルインダクタであるインダクタ3が形成される。次に、絶縁層4上にSiO2からなる絶縁層2を形成し、インダクタ3を埋め込む。

【0053】

次に、図11(a)に示すように、絶縁膜2上の全面に、スパッタリング法によりTiW層9を形成する。次に、電気めっき法により、TiW層9上にCu層10を形成する。

【0054】

次に、図11(b)に示すように、Cu層10上にレジスト25を形成し、このレジスト25に開口部25a及び25bを形成する。開口部25aは、後の工程において積層膜14の強磁性体層15を形成する予定の領域に相当し、開口部25bは、後の工程においてパッド21の強磁性体層15を形成する予定の領域に相当する。開口部25a及び25bにおいてはCu層10が露出している。

【0055】

次に、図11(c)に示すように、レジスト25をマスクとして、Niの電気めっきを行い、Cu層10上における開口部25a及び25bに相当する領域にNiからなる強磁性体層15を形成する。

【0056】

次に、図11(d)に示すように、レジスト25を除去し、Cu層10及び強磁性体層15上にCu層11を形成する。そして、このCu層11上にTiW層12を形成する。

【0057】

次に、図11(e)に示すように、TiW層12上にレジスト(図示せず)を形成し、このレジストをマスクとして、TiW層12、Cu層11、Cu層10及びTiW層9をウエットエッチングすることにより、選択的に除去してパターニングする。Cu層10及び11のウエットエッチングは硫酸と過酸化水素との混合液である硫酸過水を使用すればよく、TiW層9及び12のウエットエッチングは過酸化水素水により行うことができる。

【0058】

これにより、図9に示すように、絶縁層2の表面に垂直な方向から見て、正方形状となる積層膜14と、この積層膜14の形成領域から外れた領域に、八角形状となるパッド21とを形成する。積層膜14及びパッド21は、TiW層9、Cu層10、強磁性体層15、Cu層11及びTiW層12が積層されて構成されている。そして、絶縁層2上の全面に、積層膜14及びパッド21を埋め込むように、ポリイミドからなる絶縁層16(図10参照)を形成する。これにより、本実施例に係る半導体集積回路を製造することができる。本実施例における上記以外の構成及び製造方法は、前述の第1の実施例と同様である。

【0059】

本実施例においては、配線3aを渦巻状に配置することにより、スパイラルインダクタであるインダクタ3を形成することができる。そして、このインダクタ3の内部領域13に設けられた強磁性体層15が、インダクタ3の磁芯として作用し、インダクタ3のインダクタンス及びQ値を向上させる。

【0060】

また、積層膜14を、パッド21と同層且つ同材料により形成することにより、この積層膜14とパッド21とを同一工程にて形成することができる。このため、積層膜14を形成するための特別な工程が不要になる。これにより、半導体集積回路の製造が容易になり、製造コストを低減することができる。

【0061】

次に、本発明の第7の実施例について説明する。図12は、本実施例に係る半導体集積回路を示す平面図であり、図13は図12に示すD−D線による断面図である。図12及び図13に示すように、本実施例に係る半導体集積回路は、前述の第6の実施例に係る半導体集積回路と比較して、積層膜14がインダクタ3の内部領域13の直上域のみならず、インダクタ3の直上域全体に形成されている点が異なっている。即ち、絶縁層2の表面に垂直な方向から見て、積層膜14はインダクタ3を覆うように形成されている。本実施例における上記以外の構成及び製造方法は、前述の第6の実施例と同様である。

【0062】

本実施例においては、インダクタ3を小型化した場合においても、十分な大きさの強磁性体層15を設けることができる。また、積層膜14を設けないと、表皮効果によりインダクタ3の半導体基板側の表面、即ち、下面に電流が集中して流れてしまい、インダクタ3の抵抗値が大きくなる。これに対して、本実施例においては、インダクタ3の直上域全体に積層膜14が形成されているため、インダクタ3の上面にも電流が流れるようになり、インダクタ3の抵抗値が低下する。これにより、インダクタ3のQ値がより一層向上する。

【0063】

【発明の効果】

以上詳述したように、本発明によれば、強磁性体層の下面を配線の上面よりも低くし、強磁性体層の上面を配線の下面よりも高くすることにより、強磁性体層の少なくとも一部が配線と同層になり、スパイラルインダクタのインダクタンス及びQ値をより一層向上させることができる。また、積層膜の下面を配線の下面以下の位置とし、積層膜の上面を配線の上面以上の位置とすることにより、積層膜の上面及び下面と配線との間に寄生容量が発生せず、スパイラルインダクタのインダクタンス及びQ値をより一層向上させることができる。これにより、インダクタのインダクタンス及びQ値が高く、小型化が可能な半導体集積回路を得ることができる。

【図面の簡単な説明】

【図1】本発明の第1の実施例に係る半導体集積回路を示す平面図である。

【図2】(a)は図1に示すA−A線による断面図であり、(b)は図1に示すB−B線による断面図である。

【図3】(a)乃至(e)は、本実施例に係る半導体集積回路の製造方法をその工程順に示す断面図であり、図2(a)の一部に相当する部分を示す。

【図4】(a)及び(b)は本発明の第1の実施例の変形例に係る半導体集積回路を示す断面図であり、(a)は図1に示すA−A線による断面図に相当し、(b)は図1に示すB−B線による断面図に相当する。

【図5】本発明の第2の実施例に係る半導体集積回路を示す平面図である。

【図6】本発明の第3の実施例に係る半導体集積回路を示す平面図である。

【図7】本発明の第4の実施例に係る半導体集積回路を示す平面図である。

【図8】本発明の第5の実施例に係る半導体集積回路を示す平面図である。

【図9】本発明の第6の実施例に係る半導体集積回路を示す平面図である。

【図10】図9に示すC−C線による断面図である

【図11】(a)乃至(e)は本実施例に係る半導体集積回路の製造方法をその工程順に示す断面図である。

【図12】本発明の第7の実施例に係る半導体集積回路を示す平面図である。

【図13】図12に示すD−D線による断面図である

【図14】従来の半導体集積回路を示す平面図である。

【図15】図14に示すE−E線による断面図である。

【符号の説明】

1;多層配線層

2、4;絶縁層

2a;開口部

3;インダクタ

3a、5、8;配線

6、7;ビア

9、12;TiW層

10、11;Cu層

13;内部領域

14;積層膜

14a;部分

14b;断絶部

14c;矩形部分

15;強磁性体層

16;絶縁層

17;配線本体層

18;レジスト

18a;開口部

19;金属層

21;パッド

22、24;TiW層

23;Cu層

25;レジスト

25a、25b;開口部

101;多層配線層

102;最上層

103;インダクタ

104、105、106;絶縁層

107;配線本体層

108;TiW層

Claims (23)

- 基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有することを特徴とする半導体集積回路。

- 前記インダクタがスパイラル形状を有し、前記基板の表面に垂直な方向から見て、前記積層膜が前記インダクタを構成する配線によって囲まれる領域に配置されていることを特徴とする請求項1に記載の半導体集積回路。

- 前記基板の表面に垂直な方向から見て、前記強磁性体層が相互に離隔した複数の部分に分割されていることを特徴とする請求項2に記載の半導体集積回路。

- 前記基板上に設けられた多層配線層を有し、前記インダクタ及び前記積層膜は前記多層配線層の最上層に設けられていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有することを特徴とする半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記基板の表面に垂直な方向から見て、前記積層膜が前記インダクタと重ならずに前記インダクタを囲むように設けられていることを特徴とする半導体集積回路。

- 前記基板上に設けられた多層配線層を有し、前記インダクタ及び前記積層膜は前記多層配線層における相互に異なる層に設けられていることを特徴とする請求項5に記載の半導体集積回路。

- 前記積層膜と同層に設けられたパッドを有することを特徴とする請求項5又は7に記載の半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、前記積層膜と同層に設けられたパッドと、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記パッドの積層構造が前記積層膜の積層構造と同じであることを特徴とする半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記金属層がバリアメタル層を有することを特徴とする半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの上方に設けられた積層膜と、前記積層膜と同層に設けられたパッドと、を有し、前記積層膜は、強磁性体層と、この強磁性体層を覆いこの強磁性体層の拡散を防止する金属層と、を有し、前記金属層がバリアメタル層を有することを特徴とする半導体集積回路。

- 前記金属層が第1層及び第2層を有し、前記強磁性体層の下面は前記第1層により覆われており、前記強磁性体層の上面及び側面は前記第2層により覆われていることを特徴とする請求項1乃至4のいずれか1項に記載の半導体集積回路。

- 前記第1層及び前記第2層が夫々バリアメタル層を有することを特徴とする請求項12に記載の半導体集積回路。

- 基板上に設けられたインダクタと、前記インダクタの側方に設けられた積層膜と、を有し、前記積層膜は、強磁性体層と、この強磁性体層の下面を覆う第1の金属層と、前記強磁性体層の上面を覆う第2の金属層と、を有し、前記インダクタは前記第1の金属層及び前記第2の金属層が積層されたものであることを特徴とする半導体集積回路。

- 基板上に設けられたスパイラル形状のインダクタと、前記基板の表面に垂直な方向から見て前記インダクタを構成する配線によって囲まれる領域に設けられた第1の金属層と、この第1の金属層上に選択的に設けられた強磁性体層と、この強磁性体層の上面及び側面を覆うように設けられた第2の金属層と、を有し、前記第1の金属層の下面は前記インダクタの下面と同一高さ又はそれよりも低く、前記第2の金属層の上面は前記インダクタの上面と同一高さ又はそれよりも高く、前記強磁性体層の下面は前記インダクタの上面よりも低く、前記強磁性体層の上面は前記インダクタの下面よりも高く、前記インダクタは、前記第1の金属層及び前記第2の金属層が積層されたものであることを特徴とする半導体集積回路。

- 基板上に設けられたスパイラル形状のインダクタと、前記基板の表面に垂直な方向から見て前記インダクタを構成する配線によって囲まれる領域に設けられた第1の金属層と、この第1の金属層上に選択的に設けられた強磁性体層と、この強磁性体層の上面及び側面を覆うように設けられた第2の金属層と、を有し、前記第1の金属層の下面は前記インダクタの下面と同一高さ又はそれよりも低く、前記第2の金属層の上面は前記インダクタの上面と同一高さ又はそれよりも高く、前記強磁性体層の下面は前記インダクタの上面よりも低く、前記強磁性体層の上面は前記インダクタの下面よりも高いことを特徴とする半導体集積回路。

- 前記基板の表面に垂直な方向から見て、前記強磁性体層が複数の部分に分割されていることを特徴とする請求項16に記載の半導体集積回路。

- 前記基板上に多層配線層が設けられており、前記インダクタ並びに前記第1の金属層、強磁性体層及び第2の金属層からなる積層膜は、前記多層配線層の最上層に形成されていることを特徴とする請求項16又は17に記載の半導体集積回路。

- 前記インダクタ、前記第1の金属層及び前記第2の金属層が銅又はアルミニウムにより形成されていることを特徴とする請求項16乃至18のいずれか1項に記載の半導体集積回路。

- 前記インダクタがスパイラルインダクタであることを特徴とする請求項16乃至19のいずれか1項に記載の半導体集積回路。

- 前記強磁性体層がニッケルにより形成されていることを特徴とする請求項16乃至20のいずれか1項に記載の半導体集積回路。

- 基板上に第1の金属層を形成する工程と、この第1の金属層上に選択的に強磁性体層を形成する工程と、この選択的に形成された強磁性体層を覆うように第2の金属層を形成する工程と、前記第1及び第2の金属層を選択的に除去してパターニングし、前記第1の金属層、前記強磁性体層及び前記第2の金属層が積層されてなる積層膜を形成すると共にこの積層膜と同層でありこの積層膜を囲むように配置されたインダクタを形成する工程と、を有することを特徴とする半導体集積回路の製造方法。

- 前記第1の金属層を形成する工程の前に、前記基板の表面における前記積層膜を形成する予定の領域にその深さが前記第1の金属層と前記強磁性体層の合計膜厚よりも小さい凹部を形成する工程を有することを特徴とする請求項22に記載の半導体集積回路の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002183471A JP3745316B2 (ja) | 2002-06-24 | 2002-06-24 | 半導体集積回路及びその製造方法 |

| TW092115175A TWI224854B (en) | 2002-06-24 | 2003-06-05 | Semiconductor integrated circuit and method of manufacturing the same |

| US10/600,104 US7053165B2 (en) | 2002-06-24 | 2003-06-20 | Semiconductor integrated circuit including an inductor and method of manufacturing the same |

| FR0350243A FR2841381B1 (fr) | 2002-06-24 | 2003-06-23 | Circuit integre a semi-conducteur et un procede de fabrication du circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002183471A JP3745316B2 (ja) | 2002-06-24 | 2002-06-24 | 半導体集積回路及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2004031520A JP2004031520A (ja) | 2004-01-29 |

| JP2004031520A5 JP2004031520A5 (ja) | 2005-09-29 |

| JP3745316B2 true JP3745316B2 (ja) | 2006-02-15 |

Family

ID=29720212

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002183471A Expired - Fee Related JP3745316B2 (ja) | 2002-06-24 | 2002-06-24 | 半導体集積回路及びその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7053165B2 (ja) |

| JP (1) | JP3745316B2 (ja) |

| FR (1) | FR2841381B1 (ja) |

| TW (1) | TWI224854B (ja) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7259639B2 (en) | 2002-03-29 | 2007-08-21 | M/A-Com Eurotec, B.V. | Inductor topologies and decoupling structures for filters used in broadband applications, and design methodology thereof |

| US6856003B2 (en) * | 2002-09-05 | 2005-02-15 | Industrial Technology Research Institute | Microelectronic 3-D solenoid of circular cross-section and method for fabrication |

| US7126443B2 (en) * | 2003-03-28 | 2006-10-24 | M/A-Com, Eurotec, B.V. | Increasing performance of planar inductors used in broadband applications |

| JP4464127B2 (ja) * | 2003-12-22 | 2010-05-19 | Necエレクトロニクス株式会社 | 半導体集積回路及びその製造方法 |

| JP4291164B2 (ja) * | 2004-01-08 | 2009-07-08 | 富士通メディアデバイス株式会社 | 弾性表面波装置 |

| US7410894B2 (en) * | 2005-07-27 | 2008-08-12 | International Business Machines Corporation | Post last wiring level inductor using patterned plate process |

| EP2061531B1 (en) | 2006-09-14 | 2016-04-13 | CircuLite, Inc. | Intravascular blood pump and catheter |

| US20080186123A1 (en) * | 2007-02-07 | 2008-08-07 | Industrial Technology Research Institute | Inductor devices |

| KR100946753B1 (ko) * | 2007-10-18 | 2010-03-11 | 엘아이지넥스원 주식회사 | 수중 음향센서 |

| US9269485B2 (en) * | 2007-11-29 | 2016-02-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of creating spiral inductor having high Q value |

| US20090140383A1 (en) * | 2007-11-29 | 2009-06-04 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of creating spiral inductor having high q value |

| US7666688B2 (en) * | 2008-01-25 | 2010-02-23 | Taiwan Semiconductor Manufacturing Co., Ltd. | Method of manufacturing a coil inductor |

| JP2010160142A (ja) | 2008-12-09 | 2010-07-22 | Renesas Electronics Corp | 信号送受信方法、半導体装置の製造方法、半導体装置、およびテスタ装置 |

| EP2337063B1 (en) * | 2009-12-17 | 2013-10-23 | Nxp B.V. | On chip integrated inductor and manufacturing method therefor |

| TWI499011B (zh) * | 2011-02-10 | 2015-09-01 | Nat Univ Tsing Hua | 封裝結構及其製作方法 |

| DE102011016159B3 (de) * | 2011-04-05 | 2012-10-18 | Micronas Gmbh | Anordnung aus einem integrierten passiven Bauelement und einem auf einem Metallträger angeordneten Halbleiterkörper |

| US9219106B2 (en) * | 2011-08-05 | 2015-12-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated inductor |

| CN102569032B (zh) * | 2012-01-16 | 2014-05-28 | 中国科学院上海微系统与信息技术研究所 | 多层金属化薄膜叠加制作电感元件的方法 |

| JP2012209278A (ja) * | 2012-08-03 | 2012-10-25 | Toshiba Lighting & Technology Corp | 点灯回路および照明装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CA2072277A1 (en) * | 1991-07-03 | 1993-01-04 | Nobuo Shiga | Inductance element |

| US5738931A (en) | 1994-09-16 | 1998-04-14 | Kabushiki Kaisha Toshiba | Electronic device and magnetic device |

| TW362222B (en) | 1995-11-27 | 1999-06-21 | Matsushita Electric Ind Co Ltd | Coiled component and its production method |

| US6492705B1 (en) | 1996-06-04 | 2002-12-10 | Intersil Corporation | Integrated circuit air bridge structures and methods of fabricating same |

| US5793272A (en) | 1996-08-23 | 1998-08-11 | International Business Machines Corporation | Integrated circuit toroidal inductor |

| JP3661380B2 (ja) | 1997-12-12 | 2005-06-15 | 富士電機デバイステクノロジー株式会社 | 平面型インダクタ |

| JP4200631B2 (ja) | 2000-03-29 | 2008-12-24 | 沖電気工業株式会社 | オンチップ・コイルとその製造方法 |

| JP2002043520A (ja) | 2000-07-19 | 2002-02-08 | Sony Corp | 半導体装置及びその製造方法 |

| FR2813987B1 (fr) * | 2000-09-12 | 2003-01-10 | Memscap | Microcomposant du type micro-inductance ou micro-transformateur |

| JP2002123915A (ja) | 2000-10-16 | 2002-04-26 | Alps Electric Co Ltd | スピンバルブ型薄膜磁気素子及び薄膜磁気ヘッド及び浮上式磁気ヘッド並びにスピンバルブ型薄膜磁気素子の製造方法 |

| US6752447B2 (en) | 2000-12-19 | 2004-06-22 | Bombardier Recreational Products Inc. | Windshield assembly for an all terrain vehicle |

| US6593838B2 (en) * | 2000-12-19 | 2003-07-15 | Atheros Communications Inc. | Planar inductor with segmented conductive plane |

-

2002

- 2002-06-24 JP JP2002183471A patent/JP3745316B2/ja not_active Expired - Fee Related

-

2003

- 2003-06-05 TW TW092115175A patent/TWI224854B/zh not_active IP Right Cessation

- 2003-06-20 US US10/600,104 patent/US7053165B2/en not_active Expired - Lifetime

- 2003-06-23 FR FR0350243A patent/FR2841381B1/fr not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7053165B2 (en) | 2006-05-30 |

| TW200405547A (en) | 2004-04-01 |

| TWI224854B (en) | 2004-12-01 |

| US20040004266A1 (en) | 2004-01-08 |

| JP2004031520A (ja) | 2004-01-29 |

| FR2841381B1 (fr) | 2008-03-28 |

| FR2841381A1 (fr) | 2003-12-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3745316B2 (ja) | 半導体集積回路及びその製造方法 | |

| JP6935343B2 (ja) | インダクタ部品およびその製造方法 | |

| JP3983199B2 (ja) | 半導体装置及びその製造方法 | |

| TW200427057A (en) | High performance system-on-chip inductor using post passivation process | |

| JP4464127B2 (ja) | 半導体集積回路及びその製造方法 | |

| JP2004022906A (ja) | 半導体集積回路用インダクタ及びその製造方法 | |

| CN112908611A (zh) | 线圈部件 | |

| CN112562966A (zh) | 电感部件 | |

| TWI721771B (zh) | 積體電路及其形成方法 | |

| JP2009021495A (ja) | 半導体デバイスおよびその製造方法 | |

| US7676922B1 (en) | Method of forming a saucer-shaped half-loop MEMS inductor with very low resistance | |

| US9532467B2 (en) | Circuit substrate | |

| US20230071379A1 (en) | Coil component and manufacturing method therefor | |

| US11557425B2 (en) | Coil component | |

| JP2007281230A (ja) | 半導体装置およびその製造方法 | |

| JP2008210828A (ja) | 半導体装置およびその製造方法 | |

| CN114303210A (zh) | 硅变压器集成芯片 | |

| TWI640062B (zh) | 半導體元件及其製造方法 | |

| JP7411590B2 (ja) | インダクタ部品およびその製造方法 | |

| TWI299215B (en) | Method for fabricating transformer intergrated with semiconductor structure | |

| US7714410B2 (en) | Semiconductor device | |

| JP4867206B2 (ja) | 半導体装置 | |

| JPH10270248A (ja) | スパイラルインダクタ | |

| JP2005259969A (ja) | 半導体装置およびその製造方法 | |

| CN119314776A (zh) | 电子部件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040415 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050506 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050607 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050805 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051025 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051116 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3745316 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091202 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091202 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101202 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101202 Year of fee payment: 5 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101202 Year of fee payment: 5 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111202 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111202 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121202 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121202 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131202 Year of fee payment: 8 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |