本発明を実施するための形態について、以下に詳細に説明する。なお、以下に示すすべての形態におけるリモコン受信回路は、前述した図21及び図22に示されるリモコン信号を受信するものとし、該リモコン信号のデータ部は、32ビットであるものとする。

(実施の形態1)

以下、図1〜図5を用いて、本実施の形態1におけるリモコン受信回路及びリモコン受信システムについて説明する。

まず、図1を用いて、本実施の形態1にかかるリモコン受信システムの構成について説明する。図1は、本実施の形態1におけるリモコン受信システムの構成を示す図である。

図1において、本実施の形態1にかかるリモコン受信システムは、送信機(図示せず)から発行されたリモコン信号を受信するリモコン受信回路100と、該リモコン受信回路100の各種レジスタに任意の値を設定し、リモコン受信回路100を制御すると共に、リモコン信号をデコードするCPU190とからなるものであり、前記リモコン受信回路100は、エッジ検出回路110と、カウンタ回路120と、ヘッダ検出回路130と、データ判別回路140と、シフトレジスタ150と、ヘッダ割り込み生成回路160と、データ割り込み生成回路170と、モードレジスタ180と、スイッチ111とから構成される。そして、前記CPU190は、リモコン受信機能を実現するために必要な割り込みポートとして、前記リモコン受信回路100からの割り込み信号S111を受信する割り込みポート191を備えるものである。

以下、前記リモコン受信回路100の構成を詳述する。

前記エッジ検出回路110は、カウンタ回路120及び、データ判別回路140と接続されており、受信したリモコン信号の立上りエッジと立下りエッジを検出して、前記カウンタ回路120とデータ判別回路140に、その検出したエッジを通知する。

前記カウンタ回路120は、ロングロウカウンタ(以下、「LLC」と称す。)121と、ロングハイカウンタ(以下、「LHC」と称す。)122を有し、前記エッジ検出回路110、ヘッダ検出回路130、データ判別回路140と接続されている。そして、前記カウンタ回路120内のLLC121は、前記エッジ検出回路110からのエッジ検出通知に対して、立下りエッジでカウント値をリセットしてカウントを開始し、立上りエッジでカウントをストップするものであり、また前記カウンタ回路120内のLHC122は、立上りエッジでカウントを開始し、立下りエッジでカウントをストップしてカウンタ値をリセットするものである。

前記ヘッダ検出回路130は、ロングロウ閾値レジスタ(以下、「THLレジスタ」と称す。)131と、ロングハイ閾値レジスタ(以下、「THHレジスタ」と称す。)132とを有し、前記カウンタ回路120、データ判別回路140、ヘッダ割り込み生成回路160と接続されている。なお、前記ヘッダ検出回路130内のTHLレジスタ131及びTHHレジスタ132は、CPU190により値が設定可能なレジスタであり、前記THLレジスタ131には、リモコン信号のヘッダ部のロウ区間の閾値が、またTHHレジスタ132には、ヘッダ部のハイ区間の閾値が設定される。そして、前記ヘッダ検出回路130は、前記データ判別回路140、及びヘッダ割り込み生成回路160に対して、前記カウンタ回路120内のLLC121の出力値がTHLレジスタ131の設定値を上回り、且つ前記カウンタ回路120内のLHC122の出力値がTHHレジスタ132の設定値を上回っているとき、ヘッダ検出信号S130“1”を、それ以外のとき、ヘッダ検出信号“0”を出力する。

前記ヘッダ割り込み生成回路160は、前記ヘッダ検出回路130、及びデータ判別回路140に接続されるものであり、またスイッチ111を介して、前記CPU190の割り込みポート191に接続される。そして、前記ヘッダ割り込み生成回路160は、ヘッダ検出回路130からのヘッダ検出信号S130の立上りエッジを検出すると、前記スイッチ111に対し、ヘッダ割り込み信号S160として、1サイクルのパルスを1回出力する。

前記データ判別回路140は、データ待ちフラグ141と、データ長レジスタ(以下、「DLレジスタ」と称す。)142と、データカウンタ143と、D1フラグ144と、D0フラグ145とを有し、前記カウンタ回路120、シフトレジスタ150、及びデータ割り込み生成回路170に接続されている。なお、前記ヘッダ判別回路140内のDLレジスタ142は、CPU190により値が設定可能なレジスタである。そして、前記データ判別回路140内のデータ待ちフラグ141は、ヘッダ検出信号S130の立下りエッジを検出すると“1”にセットされ、前記DLレジスタ142の設定値と前記データカウンタ143の出力値とが一致すると“0”にクリアされる。また、前記データ判別回路140内のデータカウンタ143は、前記ヘッダ検出回路130からのヘッダ検出信号S130の立上りエッジを検出するとリセットされ、シフトレジスタ150が1ビットシフトするとインクリメントされる。さらに、前記データ判別回路140内の前記D0フラグ145は、前記データ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122の出力値が1となったときに“1”にセットされ、一方、前記データ待ちフラグ141が“0”になるか、または前記エッジ検出回路110から立上りエッジが検出されるか、または前記カウンタ回路120内のLHC122の出力値が2Tを上回るか、またはヘッダ検出回路130からヘッダ検出信号S130の立上りを検出すると“0”にリセットされる。そして、前記D1フラグ144は、前記データ待ちフラグ141が“1”で、且つ前記カウンタ回路120内のLHC122の出力値が2Tを上回ったときに“1”にセットされ、一方、前記データ待ちフラグ141が“0”になるか、または前記エッジ検出回路110から立上りエッジが検出されるか、または前記ヘッダ検出回路130からのヘッダ検出信号S130の立上りエッジを検出すると“0”にリセットされるものである。さらに、データ判別回路140は、前記エッジ検出回路110から立下りエッジの検出が通知されると、その際該データ判別回路140内のD0フラグ145が“1”であったら、シフトレジスタ150を1ビットシフトさせて“0”を追加し、一方、該データ判別回路140内のD1フラグ144が“1”であったら、シフトレジスタ150を1ビットシフトさせて“1”を追加する。そして、前記データ判別回路140は、該データ判別回路140内のDLレジスタ142の設定値とデータカウンタ143の出力値とが一致すると、シフトレジスタ150にリモコン信号のデータ部に相当するデータが書き込まれたとして、データ割り込み生成回路170に対して、データ受信完了信号S140“1”を出力し、それ以外はデータ受信完了信号S140“0”を出力する。

前記データ割り込み生成回路170は、前記データ判別回路140と接続されており、またスイッチ111を介して、CPU190の割り込みポート191に接続される。そして、データ割り込み生成回路170は、前記データ判別回路140からのデータ受信完了信号S140の立上りエッジを検出すると、データ割り込み信号S170として、スイッチ111に対し、1サイクルのパルスを1回出力する。

前記モードレジスタ180は、前記CPU190により値が設定可能なレジスタで、スイッチ111と接続される。このモードレジスタ180に“0”が設定されていると、スイッチ111は、ヘッダ割り込み生成回路160とCPU190とを接続し、一方、モードレジスタ180に“1”が設定されていると、スイッチ111は、データ割り込み生成回路160とCPU190とを接続する。

次に、図2〜図4を用いて、前述した構成を有するリモコン受信システムにおいて、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の処理の流れを説明する。図2は、本実施の形態1におけるリモコン受信システムにおいて、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、リモコン受信回路及びCPUのタイミングチャートを示す図であり、図3は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態1におけるCPU側での処理を示すフローチャートを示す図であり、図4は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態1におけるリモコン受信回路での処理を示すフローチャートを示す図である。

まず、CPU190は、動作開始時に、ヘッダ検出回路130内のTHLレジスタ131とTHHレジスタ132、データ判別回路140内のDLレジスタ142、及びモードレジスタ180の値を設定する(F301,F302)。以下、前記各レジスタに設定される値について具体的に説明する。

前記ヘッダ検出回路130内のTHLレジスタ131の設定値は、リモコン信号のヘッダ部のロウ区間検出の閾値として用いられるので、リピートヘッダのロウ区間である16T未満の適当な値に設定する。ここでは6Tとする。また、THHレジスタ132の設定値は、リモコン信号のヘッダ部のハイ区間検出の閾値として用いられるので、リピートヘッダのハイ区間である4T未満の適当な値に設定する。ここでは3Tとする。そして、DLレジスタ143には、データ部のデータ長を設定する。ここでは32を設定する。そして、モードレジスタ180には、データ割り込み生成回路170とCPU190とが接続されるように、“1”を設定する。

以上のように各レジスタに値を設定した後、CPU190は、リモコン受信回路100からデータ割り込みが発行されるのを待つ。

リモコン受信回路100側では、動作開始時に、カウンタ回路120及びデータ判別回路140内のデータカウンタ143を初期化する(F401)。

リモコンのボタンが押下されると、まずリモコン受信回路100にはリモコン信号のヘッダ部が到着する。ヘッダ部の最初の立下りエッジをエッジ検出回路110が検出した時刻を時刻0とすると(F402)、時刻0において、カウンタ回路120内のLLC121とLHC122とがリセットされる(F403)。このとき、データ判別回路140内のD0フラグ145、及びD1フラグは共に“0”であるため(F404,F406)、シフトレジスタ150にはデータが格納されることなく、カウンタ回路120のみがカウントアップされる(F414)。

そして、時刻6Tにおいて、リモコン信号のヘッダ部のロウ区間をカウントしているLLC121の出力値がTHLレジスタ131の値を上回る。

さらに、時刻16Tに、立上りエッジが検出され(F413)、カウンタ回路120内のLLC121は16Tをカウントしてストップし、LHC122がカウントを開始する(F425)。

そして、時刻19Tに、前記LHC122の出力値は、ヘッダ検出回路130のTHHレジスタ132の設定値を上回る。このとき、カウンタ回路120内のLLC121の出力値は16Tでストップしているため、THLレジスタの設定値を上回っている(F415)。従って、このとき、ヘッダ検出回路130は、データ判別回路140及びヘッダ割り込み生成回路160に対して、ヘッダ検出信号S130“1”を出力する。

このヘッダ検出信号S130の立上りエッジを検出したデータ判別回路140は、該データ判別回路140内のデータカウンタ143をリセットし、データ待ちフラグを“1”にセットし、さらに、D0フラグ145、及びD1フラグ144を“0”にリセットする(F416)。

このように、本リモコン受信システムでは、ヘッダ検出回路130のTHHレジスタ132及びTHLレジスタ131に設定された値と、カウンタ回路120のLHC122及びLLC121の値とを比較するステップ(図4のF415)を、立上がりエッジ及び立下りエッジを検出するたびに行い、該F415の条件が満たされれば、リモコン信号のヘッダ部が検出されたと判断して、ヘッダ検出信号を“1”にすると共に、その際シフトレジスタ150に格納されているデータのビット数に関係なく、データ判別回路140内のデータカウンタ143をリセットするようにしている(図4のF416)。これは、本リモコン受信システムでは、データ待ち状態よりヘッダ検出を優先して処理していることを示している。つまり、本リモコン受信回路では、例えば、リモコン信号のデータ部のデータのうち30ビット受信し、残りの2ビットを待っている状況で、リモコン信号の次のヘッダ部を受信した場合、該シフトレジスタ150に格納されていた30ビットのデータを破棄し、前記次のリモコン信号のヘッダ部とデータ部に対する処理に移行される。このようにヘッダ検出を優先して行うようすれば、送信機(リモコン)と受信機(リモコン受信回路)との間を人が通過する等して、リモコンからの信号が途絶えた場合であっても、次のリモコン信号のヘッダ部を受信した場合には、リモコン受信回路が、来るはずのない残りの2ビット分のデータを待つデータ待ち状態から、CPUの処理によるのではなく自力でヘッダ部検出処理に復帰することができる。

そしてこの後、前記ヘッダ検出信号S130の立上りエッジを検出したヘッダ割り込み生成回路160は、ヘッダ割り込み信号S160として1サイクルのパルスを1回出力する。ただし、このとき、モードレジスタ180には“1”が設定されているので、ヘッダ割り込み生成回路160はCPU190の割り込みポート191に接続されておらず、このヘッダ割り込み信号S160は、CPU190には通知されない(F417)。

そして、時刻24Tにおいて、エッジ検出回路110が立下りエッジを検出し(F402)、カウンタ回路120内のLLC121,LHC122がともにリセットされ(F403)、この結果、前記LLC121及びLHC122それぞれの値は、ヘッダ検出回路130のTHLレジスタ131、及びTHHレジスタ132の値を下回るため(F415)、ヘッダ検出信号S130“0”が出力される(F419)。この時、データ判別回路140のデータ待ちフラグ141には“1”がセットされているので(F420)、これによって、データ判別回路140内のD1フラグ144とD0フラグ145とがセット可能になる。

そして、時刻25Tにおいて、エッジ検出回路110が立上りエッジを検出し(F413)、カウンタ回路120内のLLC121は、1Tをカウントしてストップする(F425)。

時刻25T+1において、カウンタ回路120内のLHC122の出力値は、“1”と等しくなる。このとき、データ判別回路140内のデータ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“1”を達成したため(F421)、前記データ判別回路140内のD0フラグ145が“1”にセットされる(F422)。

次に、時刻26Tにおいて、エッジ検出回路110が立下りを検出すると(F402)、前記データ判別回路140は、D0フラグ145が“1”である状況下で、エッジ検出回路110から立下りエッジを通知されたため、前記カウンタ回路120内のLLC121,LHC122をリセットすると共に(F403)、シフトレジスタ150を1ビットシフトさせて、シフトレジスタ150に“0”を追加する(F405)。このとき、データカウンタ143はインクリメントされて“1”になる(F408)。このとき、データカウンタ143の値はまだ指定ビット数には達していないので(F409)、カウンタ回路120がカウントアップされる(F414)。

そして、時刻27Tにおいて、エッジ検出回路110は立上りエッジを検出し(F413)、データ判別回路140内のD0フラグ145、D1フラグ144はともに“0”にリセットされる(F425)。

そして、時刻27T+1において、前述した時刻25T+1の際の動作同様に、前記D0フラグ145が“1”にセットされる(F422)。

時刻29Tにおいて、カウンタ回路120内のLHC122は2Tをカウントし、データ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“2T”を達成するため(F420,421,423)、D0フラグ145が“0”、D1フラグ144が“1”にセットされる(F424)。

時刻30Tにおいて、エッジ検出回路110が立下りエッジを検出する(F402)。この時、カウンタ回路120内のLLC121とLHC122はリセットされる(F403)。そして、データ判別回路140は、D1フラグ144が“1”の状況下で、エッジ検出回路110から立下りエッジの検出を通知されたため(F406)、シフトレジスタ150を1ビットシフトさせ、シフトレジスタ150に“1”を追加する(F407)。このとき、データカウンタ143はインクリメントされて“2”になる(F408)。この後、該データカウンタ143の値は指定ビットには達していないので(F409)、カウンタ回路120がカウントアップする(F414)。

時刻31Tにおいて、エッジ検出回路110が立上りエッジを検出すると(F413)、データ判別回路140内のD0フラグ145とD1フラグ144はともに“0”にリセットされる(F425)。以下、同様にして、リモコン信号のデータ部のデータが1ビットずつシフトレジスタ150に格納されていく。

そして、前述した動作を繰り返してデータ判別回路140内のデータカウンタ143の出力値がインクリメントされて“31”になった時刻を時刻Nとする時、時刻N+1Tにおいてエッジ検出回路110が立上りエッジを検出し、さらに時刻N+2Tにおいて立下りエッジを検出すると(F402)、シフトレジスタ150に“0”が追加され(F405)、データ判別回路140内のデータカウンタ143の出力値がインクリメントされて“32”となり(F408)、該データ判別回路140内のデータカウンタ143の値とDLレジスタ142の設定値とが等しくなる(F409)。このとき、前記データ判別回路140内のデータ待ちフラグ141は“0”にリセットされる(F410)と同時に、データ判別回路140からデータ割り込み生成回路170に対して、データ受信完了信号S140“1”が出力される。

前記データ割り込み生成回路170は、前記データ受信完了信号S140の立上りを検出すると、データ割り込み信号S170として、1サイクルのパルスを1回出力する。この時、モードレジスタ180は“1”に設定されているので(F411)、スイッチ111により、前記データ割り込み生成回路170とCPU190とが接続されている。よって、CPU190の割り込みポート191に、データ割り込み信号S170である割り込み信号S111が出力され、データ割り込みが発生する(F412)。

CPU190側では、前記リモコン受信回路100からの前記割り込み信号S111を受けて(F303)、シフトレジスタ150の値を読み出す(F304)。そして、CPU190は、シフトレジスタ150から読み出したデータの正当性を評価して(F305)、該データが無効であればF302に戻り、該シフトレジスタ150から読み出したデータが有効であれば、押下されたボタンの情報を得、対応する処理を開始する(F306)。なお、このデータの正当性の評価は、押下されたリモコンボタンに対応するデータであるか否かを調べるものであり、その評価において対応するデータでなければデータが無効であると判断され、対応するデータであれば有効であると判断される。

この後、CPU190は、モードレジスタ180に“0”を設定し(F307)、CPU190に内蔵されたタイマ(図示せず)に任意の値Mを設定し(F308)、該タイマのダウンカウントを開始する(F309)。

そして、時刻N+3Tにおいて、再びリモコン受信回路100のエッジ検出回路110が立上りエッジを検出したとき(F413)、データ判別回路140内のD0フラグ145とD1フラグ144はともに“0”にリセットされる(F425)。そして、この時、データ判別回路140内のデータ待ちフラグ141は、既に“0”にリセットされているので(F420)、カウンタ回路120内のLHC122の出力値が1、または2Tになっても、前記データ判別回路140内のD0フラグ145とD1フラグ144は“1”にセットされず、カウンタ回路120がカウントアップされていくのみである(F414)。

そして、リモコンのボタンが連続的に押下されている場合には、時刻192Tにおいてリピートヘッダ部が到着する。

時刻192Tにおいて、エッジ検出回路110は立下りエッジを検出し(F402)、カウンタ回路120内のLLC121とLHC122がリセットされる(F403)。

時刻198Tにおいて、リピートヘッダ部のロウ区間をカウントしているLLC121の出力値が、ヘッダ検出回路130内のTHLレジスタ131の値を上回る。

さらに、時刻208Tに、立上りエッジが検出され(F413)、カウンタ回路120内のLLC121は16Tをカウントしてストップし、LHC122がカウントを開始する(F425)。

そして、時刻211Tに、前記LHC122の出力値は、ヘッダ検出回路130のTHHレジスタ132の設定値を上回る。このとき、カウンタ回路120内のLLC121の出力値は16Tでストップしているため、THLレジスタの設定値を上回っている(F415)。従って、ヘッダ検出回路130は、データ判別回路140及びヘッダ割り込み生成回路160に対して、ヘッダ検出信号S130“1”を出力する。

このヘッダ検出信号S130の立上りエッジを検出したデータ判別回路140は、該データ判別回路140内のデータカウンタ143をリセットし、またデータ待ちフラグを“1”に設定し、さらに、D0フラグ145、及びD1フラグ144を“0”にリセットする(F416)。また、前記データカウンタ143がリセットされた時点で、該データ判別回路140内のデータカウンタ143の値とDLレジスタ142の設定値とが一致しなくなるので、データ受信完了信号S140“0”が出力される。

一方、前記ヘッダ検出信号S130の立上りエッジを検出したヘッダ割り込み生成回路160は、ヘッダ割り込み信号S160として1サイクルのパルスを1回出力する。この時、モードレジスタ180には“0”が設定されているので(F417)、ヘッダ割り込み生成回路160は、スイッチ111によりCPU190と接続されている。よって、前記CPU190の割り込みポート191に、ヘッダ割り込み信号S160である割り込み信号S111が出力され、ヘッダ割り込みが発生する(F418,F311)。

前記CPU190側でヘッダ割り込みが発生すると、先に押下された同じボタンが連続押下されたと判断して、該連続押下されたボタンに対応する処理を行う(F312)。そして、CPU190に内蔵されたタイマに再び任意の値Mを設定し(F308)、ダウンカウントを開始する(F309)。

以後、リモコンのボタンが連続押下されている間は、同様にして192Tの間隔でヘッダ割り込みが発行されつづける。そして、使用者がリモコンのボタンをリリースすると、リピートヘッダ部は到着しなくなり、リモコン受信回路100はヘッダ割り込みを発行しなくなる。

そして、CPU190側では、内蔵タイマがダウンカウントを経て、アンダーフロー割り込みを発行したときに(F310)、リモコンのボタンがリリースされたと判断する。

前述のようにしてリモコンのボタンのリリース判断がなされると、CPU190は、モードレジスタ180を“1”に設定し(F302)、再び、リモコン受信回路100からのデータ割り込みを待つ状態に入る。

このように、本実施の形態1のリモコン受信システムによれば、リモコン受信回路100に、モードレジスタ180及びスイッチ111を設け、該モードレジスタ180に設定された値に応じて、前記スイッチ111により、CPU190に出力する割り込み信号を選択して出力するようにしたので、リモコン受信機能を実現するために必要なCPU190側の割り込みポートを1つに抑えることができ、複数の割り込みポートを使用する従来手法よりも少ないCPUのリソースを使用して、リモコン信号の受信を実現することが可能となる。

また、本実施の形態1に係るリモコン受信システムによれば、前記リモコン受信回路100にトレーラ割り込みを発行する回路を設けず、データ割り込み信号にトレーラ割り込み信号と同様の意味を持たせるようにしたので、リモコン受信回路100の装置規模を小さくでき、且つCPU190側にはトレーラ割り込みが発行されないので、CPU190のトレーラ割り込みに対応するコードも、またその割り込みによる処理負荷も削減することができる。

さらに、本実施の形態1のリモコン受信システムによれば、前記リモコン受信回路100に、前記ヘッダ割り込み生成回路160あるいはデータ割り込み生成回路170とCPU190との接続を選択するスイッチ111と、該スイッチを切り替えるモードレジスタ180とを備え、動作開始時に前記スイッチ111がCPU190と前記データ割り込み生成回路170とを接続するようにしたので、仮に、時刻0にリモコン受信回路100に入力されたヘッダがノイズによるエラーヘッダであり、該エラーヘッダにより前記リモコン受信回路100においてヘッダ割り込み信号S160が生成されたとしても、該ヘッダ割り込み信号S160はCPU190には出力されないため、CPU190側にそのエラーヘッダにより生成されたヘッダ割り込み信号S160を回避するためのコードを設けなくても、CPUにエラーヘッダによるヘッダ割り込みの発生を防止することができる。

さらに、本実施の形態1にかかるリモコン受信システムによれば、リモコン信号を受信する一連の流れのなかで、立上がりエッジ及び立下りエッジを検出するたびにヘッダ検出を確認するステップ(図4のF415)を設けるようにしたので、リモコン信号のデータ部を受信している際に何らかの原因で信号が途切れ、シフトレジスタ150に予め設定されたビット数のデータが格納される前に、次のリモコン信号のヘッダ部を受信したとしても、該ヘッダ部の検出を優先して行い、該ヘッダ部に続く新しいデータ部の待ち状態に移行することができ、これにより、リモコン信号のデータ部の一部が欠落するアクシデントが起きても、CPUに負担をかけることなく、リモコン信号の受信処理を続行することが可能となる。

さらに、本実施の形態1にかかるリモコン受信システムによれば、前記リモコン受信回路100のデータ判別回路140内に、フラグが立ち上がっているときにのみシフトレジスタ150にデータを書き込み可能とするデータ待ちフラグ141を設け、該データ待ちフラグ141は、ヘッダ検出回路130によるヘッダ部の検出後に立ち上がり、シフトレジスタ150にリモコン信号のデータ部に相当するデータが格納されてデータ受信完了信号S140が出力された後に立ち下がるものとしたので、CPU190側にデータ割り込みが発行された後に該シフトレジスタ150をホールド可能にし、当該リモコン受信回路100にデータと誤検出される波形が入力されたとしても、該シフトレジスタ150にデータが書き込まれるのを防止して、該シフトレジスタ150に格納されたリモコン信号のデータが破損することをなくすことができる。そしてこれにより、CPU190では、従来のように、データ割り込みを受信した後の前記シフトレジスタ150の読み出しにリアルタイム性が厳しく要求されなくなり、該CPU190の割り込みポート191の割り込み優先度を低く設定することができる。そして割り込みポートの優先度を低く設定できれば、CPUが本来制御しようとするシステムの処理が圧迫されなくなり、動作の遅延が生じないという効果も得られる。

なお、前述の説明においては、リモコン受信回路100が、ボタンを連続押下された際に図22(a)に示されるようなデータを伴わないヘッダ部からなるリモコン信号を受信する場合について説明したが、当該リモコン受信回路100において受信するリモコン信号は、ボタンを連続押下された際に図22(b)に示されるような同じ波形が繰り返し続くリモコン信号であってもよい。

以下、図5及び図4を用いて、前述した構成を持つリモコン受信回路100において、繰り返しデータ型の送信機から発信されたリモコン信号を受信した場合の処理の流れを説明する。図5は、繰り返しデータ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態1におけるCPU側での処理を示すフローチャート図である。

まず時刻N+2Tまでの動作は、前述のシーケンスと同様であるので、省略する。

時刻N+2Tにおいて、CPU190側では、前述したように、データ割り込み信号S170である割り込み信号S111を受けて(F503)、シフトレジスタ150の値を読み出し(F504)、該シフトレジスタ150から読み出したデータの正当性を評価して、データの有効性を判断した後(F505)、押下されたボタンに対応する処理を行う(F506)。そしてこの後、リピートヘッダ部を受信した際には、前述したようにモードレジスタ180の値を“0”にセットしたが、ここでは、モードレジスタ180の値を再設定せず、“1”のままにしておく。すなわち、CPU190は、ヘッダ割り込み待ちの状態に入らず、データ割り込み待ちの状態を続ける。

この後、CPU190は、内蔵されたタイマに任意の値Mを設定し(F507)、タイマのダウンカウントを開始する(F508)。

リモコンのボタンが連続的に押下されている場合、時刻192Tにおいて、繰り返しデータのヘッダ部が到着する。その後、時刻0〜N+2Tと同様の動作を経て、リモコン受信回路100からCPU190へ、再びデータ割り込みが発行される(F510)。

前記データ割り込みを受信したCPU190は、シフトレジスタ150の値を読み出し(F511)、データの有効性判断を行う(F512)。そして、データが無効と判断されればF503へ遷移し、次のデータ割り込み待ち状態となる。一方、有効であると判断されると、CPU190は、前回のデータ割り込みで取得したデータと、今回のデータ割り込みで取得したデータとが同一であるか否かを比較する(F513)。そして、これらのデータが一致していたら、リモコンボタンの連続押下中と判断して、その連続押下されたボタンに対応する処理を行い(F514)、データが一致していなければ、新たに別のボタンが押下されたものと判断して、CPU190の内蔵タイマをストップし(F515)、その新たに押下されたボタンに対応する処理を行う(F506)。

そして、リモコンボタンがリリースされると、それ以上、CPU190にはデータ割り込みが入らなくなる。

CPU190では、内蔵タイマがダウンカウントを経て、アンダーフロー割り込みを発行したとき(F509)、リモコンのボタンがリリースされたと判断して、F503に遷移し、新たなボタン押下を待つ状態になる。

このように本実施の形態にかかるリモコン受信システムは、繰り返しデータを送信するタイプの送信機にも対応しうる。

(実施の形態2)

以下、図6から図12を用いて、本実施の形態2にかかるリモコン受信システムについて説明する。

前記実施の形態1においては、送信機から発行されるリモコン信号のデータ部が、ヘッダ部とデータ部とで構成される場合について説明したが、本実施の形態2においては、該リモコン信号のデータ部が、メインデータ部と、該メインデータ部の0と1を反転させた反転データ部とで構成されているものとし、また、本実施の形態2のリモコン受信回路に、前記メインデータ部と前記反転データ部とを比較した結果によって、該リモコン信号のデータ部の有効性を判断する有効性判別回路と、使用者によるリモコンボタンのリリースを検出するOFF検出回路とをさらに備えて、前記実施の形態1より、少ないCPUのリソース、及び少ないCPUの処理能力で、リモコン受信機能を実現できるようにするものである。

なお、本実施の形態2においては、前記リモコン信号のデータ部が、前記実施の形態1と同様32ビットであって、その32ビットのデータ部が、図6に示されるように、8ビットのカスタマコード部と、該カスタマコード部の0と1を反転させた8ビットの反転カスタマコード部と、8ビットのコマンド部と、該コマンド部の0と1を反転させた8ビットの反転コマンド部とからなる場合を例に挙げる。

まず、図7及び図8を用いて、本実施の形態2にかかるリモコン受信システムの構成について説明する。図7は、本実施の形態2におけるリモコン受信システムの構成を示す図であり、図8は、本実施の形態2におけるリモコン受信回路内の有効性判別回路の詳細な構成を示す図である。

図7において、本実施の形態2に係るリモコン受信システムは、送信機(図示せず)から発行されたリモコン信号を受信するリモコン受信回路200と、該リモコン受信回路200の各種レジスタに任意の値を設定し、リモコン受信回路200を制御するCPU290とからなるものであり、リモコン受信回路200は、エッジ検出回路110と、カウンタ回路120と、ヘッダ検出回路130と、データ判別回路140と、シフトレジスタ250と、ヘッダ割り込み生成回路160と、データ割り込み生成回路270と、モードレジスタ280と、スイッチ111と、有効性判別回路210と、OFF検出回路220とを備えるものである。そして、前記CPU290は、前記リモコン受信回路200からの割り込み信号S111を受信する割り込みポート291を備えるものである。

以下、前記リモコン受信回路200の構成を詳述する。本実施の形態2にかかるリモコン受信回路200は、前記実施の形態1にかかるリモコン受信回路100に、有効性判別回路210とOFF検出回路220とを追加した構成である。

前記有効性判別回路210は、シフトレジスタ250と、データ割り込み生成回路270と接続されており、前記シフトレジスタ250に格納されたリモコン信号のデータを受け、該データが有効か否かを示すデータ有効信号S210を出力する。この有効性判別回路210は、例えば図8のような構成で実現でき、前記データ有効信号S210は、前記シフトレジスタ250に格納されたデータのカスタマコード部8ビットと、反転カスタマコード部8ビットの対応する各ビットとの排他的論理和をとって、その出力8ビットの論理積をとったものと、前記シフトレジスタ250に格納されたデータのコマンド部8ビットと、反転コマンド部8ビットの対応する各ビットとの排他的論理和をとって、その出力8ビットの論理積をとったものとの論理積である。

前記OFF検出回路220は、前記リモコン信号の発信元である送信機(図示せず)のリモコンボタンがリリースされたか否かを検出するものであり、OFF極性レジスタ221と、OFF閾値レジスタ222と、OFFフラグレジスタ223とを有し、前記カウンタ回路120、及びモードレジスタ280と接続されている。そして、前記OFF極性レジスタ221、及びOFF閾値レジスタ222は、前記CPU290から設定可能なレジスタであり、また前記OFFフラグレジスタ223は、前記CPU290から読み出しのみ可能なレジスタである。そして、前記OFF閾値レジスタ222には、前記リモコンボタンのリリース検出に用いる閾値が設定され、前記OFF検出回路220は、前記OFF極性レジスタ221の設定値が“0”なら、カウンタ回路120内のLLC121の出力値と前記OFF閾値レジスタ222の設定値とを比較し、前記OFF極性レジスタ221の設定値が“1”なら、前記カウンタ回路120内のLHC122の出力値と前記OFF閾値レジスタ222の設定値とを比較し、それぞれの比較において、両者が等しければOFFフラグレジスタ223を“1”にセットし、一方、モードレジスタ280の設定値が“1”である状況下で、前記カウンタ回路120内のLLC121,LHC122の出力値が前記OFF閾値レジスタ222の設定値より小さければOFFフラグレジスタ223を“0”にリセットする。つまり、ここでは、前記OFFフラグレジスタ223の値が“1”であれば、前記リモコンボタンがリリースされたことを意味し、“0”であれば、リモコンボタンがリリースされておらず、連続押下されている状態にあることを意味する。

データ割り込み生成回路270は、前記データ判別回路140と前記有効性判別回路210と接続されており、該有効性判別回路210からのデータ有効信号S210が“1”を出力している状況下において、前記データ判別回路140からのデータ受信完了信号S140の立上りを検出すると、データ割り込み信号S270として1サイクルのパルスを1回出力する。

前記モードレジスタ280は、前記スイッチ111と、前記OFF検出回路220に接続されている。そして、前記実施の形態1と同様、前記CPU290により値が設定可能なレジスタであり、このモードレジスタ280に“0”が設定されていると、スイッチ111は、ヘッダ割り込み生成回路160とCPU290とを接続し、一方、モードレジスタ280に“1”が設定されていると、スイッチ111は、データ割り込み生成回路160とCPU290とを接続する。

そして、CPU290は、後述する1つのタスクT110をラウンドロビンのタスクとして持っている。なお、このほかの構成については、前記実施の形態1と同様であるため、ここでは説明を省略する。

次に、図9〜図11を用いて、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、前述した構成を有するリモコン受信システムの処理の流れを説明する。図9は、本実施の形態2におけるリモコン受信システムが、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合のリモコン受信回路及びCPUのタイミングチャート図であり、図10(a)は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態2におけるCPU側での処理を示すフローチャート図であり、図10(b)は、本実施の形態2におけるCPUのタスクT110の処理のフローチャート図であり、図11は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態2におけるリモコン受信回路での処理を示すフローチャート図である。

まず、CPU290は、動作開始時に初期の設定として、前記実施の形態1と同様、ヘッダ検出回路130内のTHLレジスタ131とTHHレジスタ132、データ判別回路140内のDLレジスタ143、及びモードレジスタ280に値を設定するのに加え、OFF極性レジスタ221と、OFF閾値レジスタ222に値を設定する(F1001,F1002)。以下、前記各レジスタに設定される値について具体的に述べると、前記OFF極性レジスタ221には“1”を設定し、前記OFF検出回路220内のOFF閾値レジスタ222には200Tを設定する。なお、そのほかの各レジスタには、前記実施の形態1において設定した同様の値を設定する。つまり、前記ヘッダ検出回路130内のTHLレジスタ131には6Tを設定し、THHレジスタ132には3Tを設定し、また、データ判別回路140内のDLLレジスタ143には32を設定し、モードレジスタ280には“1”を設定するものとする。

以上のように各レジスタに値を設定した後、CPU290は、リモコン受信回路200からデータ割り込み信号S270が発行されるのを待つ。

また、リモコン受信回路200側では、動作開始時に、カウンタ回路120及びデータ判別回路140内のデータカウンタ143を初期化する(F1101)。

そして、リモコンのボタンが押下されると、まずリモコン受信回路200にはリモコン信号のヘッダ部が到着する。ヘッダ部の最初の立下りエッジをエッジ検出回路110が検出した時刻を時刻0とすると(F1102)、時刻0において、カウンタ回路120内のLLC121とLHC122とがリセットされる(F1103)。このとき、データ判別回路140内のD0フラグ145、及びD1フラグ144は共に“0”であるため(F1104,F1106)、シフトレジスタ250にはデータが格納されることなく、カウンタ回路120のみがカウントアップされる(F1115)。

そして、時刻6Tにおいて、リモコン信号のヘッダ部のロウ区間をカウントしているLLC121の出力値がTHLレジスタ131の値を上回る。

さらに、時刻16Tに、立上りエッジが検出され(F1114)、カウンタ回路120内のLLC121は16Tをカウントしてストップし、LHC122がカウントを開始する(F1130)。

そして、時刻19Tに、前記LHC122の出力値は、ヘッダ検出回路130のTHHレジスタ132の設定値を上回る。このとき、カウンタ回路120内のLLC121の出力値は16Tでストップしているため、THLレジスタ131の設定値を上回っている(F1116)。従って、このとき、ヘッダ検出回路130は、データ判別回路140及びヘッダ割り込み生成回路160に対して、ヘッダ検出信号S130“1”を出力する。

このヘッダ検出信号S130の立上りエッジを検出したデータ判別回路140は、該データ判別回路140内のデータカウンタ143をリセットし、データ待ちフラグを“1”にセットし、さらに、D0フラグ145、及びD1フラグ144を“0”にリセットする(F1117)。また、前記ヘッダ検出信号S130の立上りエッジを検出したヘッダ割り込み生成回路160は、ヘッダ割り込み信号S160として1サイクルのパルスを1回出力する。ただし、このとき、モードレジスタ280には“1”が設定されているので、ヘッダ割り込み生成回路160はCPU290の割り込みポート291に接続されておらず、このヘッダ割り込み信号S160は、CPU290には通知されない(F1118)。

そして、時刻24Tにおいて、エッジ検出回路110が立下りエッジを検出し(F1102)、カウンタ回路120内のLLC121,LHC122がともにリセットされ(F1103)、この結果、前記LLC121及びLHC122それぞれの値は、ヘッダ検出回路130のTHLレジスタ131、及びTHHレジスタ132の値を下回るため(F1116)、ヘッダ検出信号S130“0”が出力される(F1120)。そしてこの後、前記OFF検出回路220内のOFF極性レジスタ221に“1”が設定されているので、該OFF検出回路220において、前記カウンタ回路120内のLHC122の値と、前記OFF閾値レジスタ222の設定値とが比較され、この時、前記カウンタ回路120内のLHC122の値は“3T”で、モードレジスタ280は“0”がセットされているので(F1121,F1122)、OFFフラグレジスタは“0”にリセットされない。さらにこの時、前記データ判別回路140内のデータ待ちフラグ141は“1”にセットされているので(F1124)、これによって、データ判別回路140内のD1フラグ144とD0フラグ145とがセット可能になる。

そして、時刻25Tにおいて、エッジ検出回路110が立上りエッジを検出し(F1114)、カウンタ回路120内のLLC121は、1Tをカウントしてストップする(F1130)。

時刻25T+1において、カウンタ回路120内のLHC122の出力値は、“1”と等しくなる。このとき、データ判別回路140内のデータ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“1”を達成したため(F1125)、前記データ判別回路140内のD0フラグ145が“1”にセットされる(F1126)。

次に、時刻26Tにおいて、エッジ検出回路110が立下りを検出すると(F1102)、前記データ判別回路140は、D0フラグ145が“1”である状況下で、エッジ検出回路110から立下りエッジを通知されたため(F1102)、前記カウンタ回路120内のLLC121,LHC122をリセットすると共に(F1103)、シフトレジスタ250を1ビットシフトさせて、シフトレジスタ250に“0”を追加する(F1105)。このとき、データカウンタ143はインクリメントされて“1”になる(F1108)。該データカウンタ143の値は指定ビット数には達していないので(F1109)、カウンタ回路120がカウントアップされる(F1115)。

そして、時刻27Tにおいて、エッジ検出回路110は立上りエッジを検出し(F1114)、データ判別回路140内のD0フラグ145、D1フラグ144はともに“0”にリセットされる(F1130)。

そして、時刻27T+1において、前述した時刻25T+1の際の動作同様に、前記D0フラグ145が“1”にセットされる(F1126)。

時刻29Tにおいて、カウンタ回路120内のLHC122は2Tをカウントし、データ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“2T”を達成したため(F1124,1125,1127)、D0フラグ145が“0”、D1フラグ144が“1”にセットされる(F1128)。

時刻30Tにおいて、エッジ検出回路110が立下りエッジを検出する(F1102)。この時、カウンタ回路120内のLLC121とLHC122はリセットされる(F1103)。そして、データ判別回路140は、D1フラグ144が“1”の状況下で、エッジ検出回路110から立下りエッジの検出を通知されたため(F1104)、シフトレジスタ250を1ビットシフトさせ、シフトレジスタ250に“1”を追加する(F1107)。このとき、データカウンタ143はインクリメントされて“2”になる(F1108)。この後、該データカウンタ143の値は指定ビットには達していないので(F1109)、カウンタ回路120がカウントアップする(F1115)。

時刻31Tにおいて、エッジ検出回路110が立上りエッジを検出すると(F1114)、データ判別回路140内のD0フラグ145とD1フラグ144はともに“0”にリセットされる(F1130)。以下、同様にして、リモコン信号のデータ部のデータが1ビットずつシフトレジスタ250に格納されていく。

そして、前述した動作を繰り返してデータ判別回路140内のデータカウンタ143の出力値がインクリメントされて“31”になった時刻を時刻Nとする時、時刻N+1Tにおいてエッジ検出回路110が立上りエッジを検出し、さらに時刻N+2Tにおいて立下りエッジを検出すると(F1102)、シフトレジスタ250に“0”が追加され(F1105)、データ判別回路140内のデータカウンタ143の出力値がインクリメントされて“32”となり(F1108)、該データ判別回路140内のデータカウンタ143の値と、DLレジスタ142の設定値とが等しくなる(F1109)。このとき、前記データ判別回路140内のデータ待ちフラグ141は“0”にリセットされ(F1110)、前記データ判別回路140からデータ受信完了信号S140が出力されると同時に、前記データ有効性判別回路210において、前記シフトレジスタ250に格納されたデータの有効性が判断される。

例えば、前記シフトレジスタ250内のデータが、受信時のノイズ等によって1ビットだけ破損していると、前記データ有効性判別回路210からはデータ有効信号S210“0”が出力され(F1112)、データ割り込み生成回路270は、前記データ判別回路140からのデータ受信完了信号S140の立上りエッジを検出しても、データ割り込み信号S270を出力しない。これにより、前記CPU290は、エラーデータによるデータ割り込みを受けなくすることができ、使用者がリモコンボタンを新たに押しなおすことによって、当該リモコン受信回路200がデータを伴う新たなリモコン信号を受信するまで、前記CPU290は、該リモコン受信回路200からの無駄な割り込みを受けることなく、動作することができる。

また、前記有効性判別回路210において、前記シフトレジスタ250に格納されたデータが有効であると判断された場合、前記有効性判別回路210は、データ有効信号S210 “1”を出力する。そして、前記データ割り込み生成回路270は、該有効性判別回路210からデータ有効信号S210“1”が出力されている状況下において、前記データ判別回路140からのデータ受信完了信号S140の立上りを検出すると、データ割り込み信号S270として1サイクルのパルスを1回出力する。この時、モードレジスタ280は“1”に設定されているので(F1111)、スイッチ111により、前記データ割り込み生成回路270とCPU290とが接続されている。よって、CPU290の割り込みポート291に、データ割り込み信号S270である割り込み信号S111が出力され、データ割り込みが発生する(F1113)。

CPU290側では、前記リモコン受信回路200からのデータ割り込み信号S270である割り込み信号S111を受けると(F1003)、シフトレジスタ250から読み出したデータの正当性を評価し(F1005)、該データが無効であればF1002に戻り、該シフトレジスタ250から読み出したデータが有効であれば、押下されたボタンの情報を得、該ボタンに対応する処理を開始する(F1006)。なお、このデータの正当性の評価は、リモコンボタンに対応するデータであるか否かを調べるものであり、その評価において、対応するデータがなければデータが無効であると判断され、対応するデータがあれば有効であると判断される。

この後、前記CPU290は、モードレジスタ280に“0”を設定し(F1007)、さらにCPU290は、ラウンドロビンのタスクとして、図10(b)に示されるタスクT110を起動する(F1008)。

以後、リモコンボタンが連続押下されている間は、192Tの間隔でリピートヘッダが到着し、ヘッダ割り込みが発行されつづける。CPU290は、ヘッダ割り込みが通知されると(F1010)先に押下されたボタンが連続押下されたと判断し、その連続押下されたボタンに対応する処理を行う(F1011)。

この間、図10(b)に示すように、CPU290内に設けられたタスクT110は実行順序が来るたびに(F1018)、OFFフラグレジスタ223を読み出すが(F1028)、該OFFフラグレジスタの値が“0”であれば(F1038)、再びラウンドロビンのキューに入る(F1018)。

そして、使用者がリモコンボタンをリリースすると、リピートヘッダ部はCPU290側に到着しなくなり、リモコン信号には長いハイ区間が現れる。そして、最後のリピートヘッダから200T後、LHC122の出力値は200Tに達し(F1121)、OFFフラグレジスタ223は“1”にセットされる(F1129)。

やがて、CPU290側では、タスクT110によって、OFFフラグレジスタ223から“1”が読み出されると(F1028,1038)、CPU290側ではタスクT110が終了する(F1009)。このタスクT110の終了により、CPU290はリモコンボタンのリリースを検知し、モードレジスタ280に“1”を設定し(F1010)、再び、前記リモコン受信回路200からのデータ割り込みを待つ状態になる。

このように、本実施の形態2のリモコン受信システムによれば、前記リモコン受信回路200で受信するリモコン信号のデータ部が、メインデータ部と、該メインデータ部の0と1を反転させた反転データ部とで構成されている場合に、該リモコン受信回路200に前記メインデータ部と前記反転データ部とを比較することで該リモコン信号のデータ部の有効性を判断する有効性判別回路210を備え、データ割り込み生成回路270が、該有効性判別回路210において前記リモコン信号のデータが有効であると判断され、且つ前記データ判別回路140からデータ受信完了信号S140が出力されたときに、データ割り込み信号S270を出力するようにしたので、CPU290側にエラーデータによる不要なデータ割り込み信号が発行されなくなり、これにより、リモコン受信機能に使用するCPU290の処理能力をさらに軽減することができる。

さらに、本実施の形態2のリモコン受信システムによれば、前記リモコン受信回路200にリモコンボタンのリリースを検出するOFF検出回路220を備えると共に、CPU290が、押下されたリモコンボタンに対応する処理を行った後に開始されるラウンドロビンのタスクT110のコードを持つようにし、前記OFF検出回路220によって検出されたリモコンボタンがリリースされたか否かの判断結果を、CPU290が前記タスクT110のフローにおいて読み出すようにしたので、CPU290側において、内蔵タイマを用いることなく使用者がリモコンボタンをリリースしたことを検知することが可能となり、リモコン受信機能に使用するCPU290のリソースをさらに少なくすることができる。

さらに、前述の説明においては、リモコン受信回路200が、ボタンを連続押下された際に図22(a)に示されるようなデータを伴わないリピートヘッダ部からなるリモコン信号を受信する場合について説明したが、当該リモコン受信回路200において受信するリモコン信号は、ボタンを連続押下された際に図22(b)に示されるような同じ波形が繰り返し続くリモコン信号であってもよい。

以下、図11及び図12を用いて、前述した構成を持つリモコン受信回路200において、繰り返しデータ型の送信機から発信されたリモコン信号を受信した場合の処理の流れを説明する。図12(a)は、繰り返しデータ型のリモコン信号を受信した場合の、本実施の形態2におけるCPU側での処理を示すフローチャート図であり、図12(b)は、本実施の形態2におけるCPUのタスクT110の処理のフローチャート図である。

まず、時刻N+2Tまでの動作は、前述のシーケンスと同様であるので、省略する。

時刻N+2Tにおいて、CPU290側では、前述したように、前記有効性判別回路210により有効と判断されたデータを読み出して(F1204)、押下されたリモコンボタンに対応する処理をする(F1206)。そしてこの後、リピートヘッダ部を受信した際には、前述したようにモードレジスタ280の値を“0”にセットしたが、ここでは、モードレジスタ280の値を再設定せず、“1”のままでタスクT110を起動する(F1207)。

リモコンボタンが連続的に押下されている場合、時刻192Tにおいて、繰り返しデータのヘッダ部が到着する。その後、時刻0〜N+2Tと同様の動作を経て、リモコン受信回路200からCPU290へ、再びデータ割り込みが発行される(F1209)。

前記データ割り込みを受信したCPU290は、シフトレジスタ250の値を読み出し(F1209)、データの有効性の判断する(F1211)。そして、データが無効と判断されればF1203へ遷移し、次のデータ割り込み待ち状態となる。一方、有効であると判断されると、CPU290は、前回のデータ割り込みで取得したデータと、今回のデータ割り込みで取得したデータとが同一であるか否かを比較する(F1212)。そして、これらのデータが一致していたら、リモコンボタンの連続押下中と判断して、その連続押下されたボタンに対応する処理を行い(F1213)、データが一致していなければ、タスクT110を停止し(F1214)、新たに別のボタンが押下されたものと判断して、その新たに押下されたボタンに対応する処理を行う(F1206)。

リモコンボタンが連続押下される限り、192Tおきにデータ割り込みが発生し、同一のデータがF1210で読み出される。この間、図12(b)に示すように、CPU290が持つタスクT110は実行順序が来るたびに(F1217)、OFFフラグレジスタ223の値を読み出すが(F1227)、該OFFフラグレジスタ223の値が“0”であれば(F1237)、再びラウンドロビンのキューに入る(F1208)。

そして、使用者がリモコンボタンをリリースすると、リピートヘッダ部はCPU290側に到着しなくなり、リモコン信号には長いハイ区間が現れる。そして、最後のリピートヘッダから200T後、LHC122の出力値は200Tに達し(F1121)、OFFフラグレジスタ223は“1”にセットされる(F1129)。

やがて、CPU290側では、タスクT110によって、OFFフラグレジスタ223から“1”が読み出されると(F1227,1237)、CPU290側ではタスクT110が終了する(F1208)。このタスクT110の終了により、CPU290はリモコンボタンのリリースを検知し、F1203に遷移して新たなボタン押下を待つ状態になる。

このように本実施の形態にかかるリモコン受信システムは、繰り返しデータを送信するタイプの送信機にも対応しうる。

(実施の形態3)

以下、図13から図17を用いて、本実施の形態3にかかるリモコン受信システムについて説明する。

本実施の形態3のリモコン受信システムにおいては、前記実施の形態2と同様、該リモコン信号のデータ部が、メインデータ部と、該メインデータ部の0と1を反転させた反転データ部とで構成されているものとし、また、本実施の形態3のリモコン受信回路には、ヘッダ割り込み生成回路、及びデータ割り込み生成回路を設けず、該リモコン受信回路からCPUに割り込みが発行されないようにしてCPUの割り込みポートを全く使わず、CPUが持つラウンドロビンタスクのみでリモコン受信機能を実現するものである。さらに、前記実施の形態2では、リモコンボタンのリリースをカウンタ回路120のレジスタの値とOFF検出回路220内のOFF閾値レジスタ222の設定値とを比較することで判断していたが、本実施の形態3では、OFF検出回路内にある値まで常にカウントアップするOFFカウンタを設け、該OFFカウンタの値とOFF閾値レジスタの値を比較することで、ノイズによってリモコンボタンのリリースの検出が遅延されるのを回避できるようにするものである。

なお、本実施の形態3においては、送信機(図示せず)から発行されるリモコン信号のデータ部が、前記実施の形態2と同様、図6に示されるような、8ビットのカスタマコード部と、該カスタマコードの0と1を反転させた8ビットの反転カスタマコード部と、8ビットのコマンド部と、該コマンド部の0と1を反転させた8ビットの反転コマンド部とからなる場合を例に挙げる。

まず、図13を用いて、本実施の形態3にかかるリモコン受信回路の構成について説明する。図13は、本実施の形態3におけるリモコン受信システムの構成を示す図である。

図13において、本実施の形態3に係るリモコン受信システムは、送信機(図示せず)から発行されたリモコン信号を受信するリモコン受信回路300と、該リモコン受信回路300の各種レジスタに任意の値を設定し、リモコン受信回路300を制御するCPU390とからなるものであり、リモコン受信回路300は、エッジ検出回路110と、カウンタ回路120と、ヘッダ検出回路130と、データ判別回路140と、シフトレジスタ250と、モードレジスタ180と、スイッチ311と、ANDゲート312と、OFF検出回路320と、データ/ヘッダフラグレジスタ(以下、「DHフラグレジスタ」と称す。)330と、を備えるものである。そして、前記CPU390には、前記リモコン受信回路300からの割り込みが発行されることがないので、割り込みポートが設けられていない。

以下、前記リモコン受信回路300の構成を詳述する。本実施の形態3にかかるリモコン受信回路300は、前記実施の形態2にかかるリモコン受信回路200から、データ割り込み生成回路と、ヘッダ割り込み生成回路とを削除し、DHフラグレジスタ330を追加した構成となっている。

DHフラグレジスタ330は、スイッチ311と、OFF検出回路320と接続されており、CPU390から読み出しと書き込みが可能なレジスタである。そして、前記DHフラグレジスタ330は、前記スイッチ311からのOFFカウントリセット信号S311を受信し、該OFFカウントリセット信号S311の立上りを検出すると“1”がセットされ、CPU390に“0”を書き込まれることによってのみ、“0”にリセットされるものである。

前記スイッチ311は、ANDゲート312を介してデータ判別回路140と、有効性データ判別回路210と接続され、ヘッダ検出回路130と、DHフラグレジスタ330と、モードレジスタ180とが接続される。前記スイッチ311は、前記モードレジスタ180の設定値が“1”ならば、前記データ判別回路140からのデータ受信完了信号S140と前記有効性判別回路210からのデータ有効信号S210との論理積を前記DHフラグレジスタ330に出力し、一方、前記モードレジスタ180の設定値が“0”ならば、前記ヘッダ検出回路130からのヘッダ検出信号S130を前記DHフラグレジスタ330に出力するものである。

前記OFF検出回路320は、DHフラグレジスタ330と接続され、OFF閾値レジスタ222と、OFFカウンタ321と、ONフラグレジスタ323とを有するものである。そして、前記OFFカウンタ321は、常にカウントアップしており、前記DHフラグレジスタ330の値が“1”になると、リセットされる。また、前記ONフラグレジスタ323は、DHフラグレジスタ330の値が“1”になると“1”にセットされ、OFFカウンタ321の出力値とOFF閾値レジスタ222の設定値とが等しくなると“0”にリセットされる。

そして、前記CPU390は、後述する2つのタスクT120,T121をラウンドロビンのタスクとして持っている。なお、このほかの前記実施の形態において説明したものと同じ番号が付されたものについては、前述した実施の形態において説明したものと同じであるため、ここでは説明を省略する。

次に、図14〜図16を用いて、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、前述した構成を有するリモコン受信システムの処理の流れを説明する。図14は、本実施の形態3におけるリモコン受信システムが、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合のリモコン受信回路及びCPUのタイミングチャート図であり、図15(a)は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態3におけるCPU側での処理を示すフローチャート図であり、図15(b)は、本実施の形態3におけるCPUのタスクT120の処理のフローチャート図であり、図15(c)は、本実施の形態3におけるCPUのタスクT121の処理のフローチャート図であり、図16は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態3におけるリモコン受信回路での処理を示すフローチャート図である。

まず、CPU390は、動作開始時に初期の設定として、前記実施の形態2と同様、ヘッダ検出回路130内のTHLレジスタ131とTHHレジスタ132、データ判別回路140内のDLレジスタ143、前記OFF検出回路320内のOFF閾値レジスタ222及びモードレジスタ180に値を設定する(F1501,F1502)。以下、前記各レジスタに設定される値について具体的に述べると、前記ヘッダ検出回路130内のTHLレジスタ131には6Tを設定し、THHレジスタ132には3Tを設定し、データ判別回路140内のDLLレジスタ143には32を設定し、OFF検出回路140内のOFF閾値レジスタ222には200Tを設定し、また、モードレジスタ180には“1”を設定するものとする。

以上のように各レジスタに値を設定した後、CPU390は、ラウンドロビンのタスクとしてタスクT120を開始する(F1503)。

また、リモコン受信回路300側では、動作開始時に、カウンタ回路120及びデータ判別回路140内のデータカウンタ143を初期化する(F1601)。

リモコンのボタンが押下されると、まずリモコン受信回路300にはリモコン信号のヘッダ部が到着する。ヘッダ部の最初の立下りエッジをエッジ検出回路110が検出した時刻を0とすると(F1602)、時刻0において、カウンタ回路120内のLLC121とLHC122とがリセットされる(F1603)。このとき、データ判別回路140内のD0フラグ145、及びD1フラグは共に“0”であるため(F1604,F1606)、シフトレジスタ250にはデータが格納されることなく、カウンタ回路120のみがカウントアップされる(F1605)。

そして、時刻6Tにおいて、リモコン信号のヘッダ部のロウ区間をカウントしているLLC121の出力値がTHLレジスタ131の値を上回る。

さらに、時刻16Tに、立上りエッジが検出され(F1614)、カウンタ回路120内のLLC121は16Tをカウントしてストップし、LHC122がカウントを開始する(F1627)。

そして、時刻19Tに、前記LHC122の出力値は、ヘッダ検出回路130のTHHレジスタ132の設定値を上回る。このとき、カウンタ回路120内のLLC121の出力値は16Tでストップしているため、THLレジスタ131の設定値を上回っている(F1616)。このとき、前記実施の形態では、前記ヘッダ検出回路130がデータ判別回路140及びヘッダ割り込み生成回路160に対して、ヘッダ検出信号S130“1”を出力し、ヘッダ割り込み生成回路160の動作が発生したが、本実施の形態3では、以下の動作が発生する。

すなわち、前記ヘッダ検出回路130から、データ判別回路140及びスイッチ311に対してヘッダ検出信号S130“1”が出力され、このヘッダ検出信号S130の立ち上がりエッジを検出した前記データ判別回路140は、データ待ちフラグを“1”にセットし、前記データカウンタ143をリセットし、さらにD1フラグ144及び、D0フラグ145を“0”にリセットする(F1617)。また、前記ヘッダ検出回路130からのヘッダ検出信号S130“1”は、スイッチ311に伝えられるが、このときモードレジスタ180が“1”に設定されているため(F1618)、前記ヘッダ検出回路130はDHフラグレジスタ330とは接続されないため、このヘッダ検出信号S130の立ち上がりは、DHフラグレジスタ330には伝えられず、ONフラグレジスタ323は“0”のままであり、この結果OFFカウンタ321もリセットされない。

そして、時刻24Tにおいて、エッジ検出回路110が立下りエッジを検出し(F1602)、カウンタ回路120内のLLC121,LHC122がともにリセットされ(F1603)、この結果、前記LLC121及びLHC122それぞれの値は、ヘッダ検出回路130のTHLレジスタ131、及びTHHレジスタ132の値を下回るため(F1616)、ヘッダ検出信号S130“0”が出力される(F1620)。そして、OFF検出回路320内のOFFカウンタ321の値とOFF閾値レジスタ222との値が比較される(F1621)。そして、この時、データ判別回路140のデータ待ちフラグ141には“1”がセットされているので(F1622)、これによって、データ判別回路140内のD1フラグ144とD0フラグ145とがセット可能になる。

そして、時刻25Tにおいて、エッジ検出回路110が立上りエッジを検出し(F1614)、カウンタ回路120内のLLC121は、1Tをカウントしてストップする(F1628)。

時刻25T+1において、カウンタ回路120内のLHC122の出力値は、“1”と等しくなる。このとき、データ判別回路140内のデータ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“1”を達成したため(F1623)、前記データ判別回路140内のD0フラグ145が“1”にセットされる(F1624)。

次に、時刻26Tにおいて、エッジ検出回路110が立下りを検出すると(F1602)、前記データ判別回路140は、D0フラグ145が“1”である状況下で、エッジ検出回路110から立下りエッジを通知されたため、前記カウンタ回路120内のLLC121,LHC122をリセットすると共に(F1603)、シフトレジスタ250を1ビットシフトさせて、シフトレジスタ250に“0”を追加する(F1605)。このとき、データカウンタ143はインクリメントされて“1”になる(F1608)。該データカウンタ143の値は指定ビット数には達していないので(F1609)、カウンタ回路120がカウントアップされる(F1615)。

そして、時刻27Tにおいて、エッジ検出回路110は立上りエッジを検出し(F1614)、データ判別回路140内のD0フラグ145、D1フラグ144はともに“0”にリセットされる(F1628)。

そして、時刻27T+1において、前述した時刻25T+1の際の動作同様に、前記D0フラグ145が“1”にセットされる(F1624)。

時刻29Tにおいて、カウンタ回路120内のLHC122は2Tをカウントし、データ待ちフラグ141が“1”で、且つカウンタ回路120内のLHC122が“2T”を達成したため(F1622,1623,1625)、D0フラグ145が“0”、D1フラグ144が“1”にセットされる(F1626)。

時刻30Tにおいて、エッジ検出回路110が立下りエッジを検出する(F1602)。この時、カウンタ回路120内のLLC121とLHC122はリセットされる(F1603)。そして、データ判別回路140は、D1フラグ144が“1”の状況下で、エッジ検出回路110から立下りエッジの検出を通知されたため(F1606)、シフトレジスタ250を1ビットシフトさせ、シフトレジスタ250に“1”を追加する(F1607)。このとき、データカウンタ143はインクリメントされて“2”になる(F1608)。この後、該データカウンタ143の値は指定ビットには達していないので(F1609)、カウンタ回路120がカウントアップする(F1615)。

時刻31Tにおいて、エッジ検出回路110が立上りエッジを検出すると(F1614)、データ判別回路140内のD0フラグ145とD1フラグ144はともに“0”にリセットされる(F1628)。以下、同様にして、リモコン信号のデータ部のデータが1ビットずつシフトレジスタ250に格納されていく。

そして、前述した動作を繰り返してデータ判別回路140内のデータカウンタ143の出力値がインクリメントされて“31”になった時刻を時刻Nとする時、時刻N+1Tにおいてエッジ検出回路110が立上りエッジを検出し、さらに時刻N+2Tにおいて立下りエッジを検出すると(F1602)、シフトレジスタ250に“0”が追加され(F1605)、データ判別回路140内のデータカウンタ143の出力値がインクリメントされて“32”となり(F1608)、該データ判別回路140内のデータカウンタ143の値とDLレジスタ142の設定値とが等しくなる(F1609)。このとき、前記データ判別回路140内のデータ待ちフラグ141は“0”にリセットされる(F1610)と同時に、データ判別回路140からデータ割り込み生成回路170に対して、データ受信完了信号S140“1”が出力される。さらに、このとき、モードレジスタ180が“1”であるので(F1611)、スイッチ311はデータ判別回路140からのデータ受信完了信号S140と有効性判別回路S210からのデータ有効信号S210との論理積のほうを選択している。そして、この後、有効性判別回路210にて、前記シフトレジスタ250に格納されたデータが有効か否かを判断し(F1612)、データが有効と判断されれば、データ有効信号S210“1”が出力され、DHフラグレジスタ330には、データ受信完了信号S140“1”とデータ有効信号S210“1”との論理積“1”であるOFFカウントリセット信号S311が出力され、これによりDHフラグレジスタ330が“1”にセットされ、さらに、DHフラグレジスタ330の立上りエッジを前記OFF検出回路320が検出するので、該OFF検出回路320内のOFFカウンタ321がリセットされ、ONフラグレジスタ323が“1”にセットされる(F1613)。

前述のF1613が発生するまでの間、CPU390側では、タスクT120が実行されており、実行順序が来るたびにDHフラグレジスタ330の値を読み出すが(F1505)、該DHフラグレジスタ330の値が“0”であるため(F1506)、再びラウンドロビンのキューに入る(F1504)。

そして、前記F1613発生後、CPU390側では、やがてタスクT120によってDHフラグレジスタ330から“1”が読み出される(F1506)。そして、CPU390は、シフトレジスタ250の値を読み出し(F1507)、該シフトレジスタ250から読み出したデータの正当性を評価して(F1508)、該データが有効でなければ再びラウンドロビンのキューに入り(F1504)、一方該データが有効であれば、押下されたボタンの情報を得、対応する処理を開始する(F1509)。

そして、CPU390は、モードレジスタ180に“0”を設定し(F1510)、DHフラグレジスタ330を“0”にリセットした後(F1511)、タスクT121をラウンドロビンのタスクとして起動して(F1512)、現在実行中のタスクT120をラウンドロビンタスクから外す。

そして、時刻N+3T以降は、データ判別回路140内のデータ待ちフラグ141が“0”にセットされていることから、カウンタ回路120内のLHC122の出力値が1、または2Tになっても、前記データ判別回路140内のD0フラグ145とD1フラグ144は“1”にセットされず、カウンタ回路120がカウントアップされていくのみである。

そして、リモコンボタンが連続押下されている場合には、時刻192Tにおいてリピートヘッダ部が到着する。

時刻192Tにおいて、エッジ検出回路110は立下りエッジを検出し(F1602)、カウンタ回路120内のLLC121とLHC122がリセットされる(F1603)。

時刻198Tにおいて、リピートヘッダ部のロウ区間をカウントしているLLC121の出力値が、ヘッダ検出回路130内のTHLレジスタ131の値を上回る。

さらに、時刻208Tに、立上りエッジが検出され(F1614)、カウンタ回路120内のLLC121は16Tをカウントしてストップし、LHC122がカウントを開始する(F1628)。

そして、時刻211Tに、前記LHC122の出力値は、ヘッダ検出回路130のTHHレジスタ132の設定値を上回る。このとき、カウンタ回路120内のLLC121の出力値は16Tでストップしているため、THLレジスタの設定値を上回っている(F1616)。従って、ヘッダ検出回路130は、データ判別回路140及びヘッダ割り込み生成回路160に対して、ヘッダ検出信号S130“1”を出力する(F1617)。

このとき、モードレジスタ180は“0”に設定されているので(F1618)、スイッチ311は、ヘッダ検出回路130からのヘッダ検出信号S130を選択し、これにより、DHフラグレジスタ330にOFFカウントリセット信号S311“1”が出力され、DHフラグレジスタ330が“1”にセットされ、さらに、前記DHフラグレジスタ330の立上りエッジを受けて、OFF検出回路140内のOFFカウンタ321がリセットされる(F1619)。

この時、CPU390側では、タスクT120がラウンドロビンタスクから外されてタスクT121が実行されている。そして、前述のF1619が発生する前まで、前記DHフラグレジスタ330には“0”が設定されており、且つ前記OFF検出回路140内のONフラグレジスタ323には“1”が設定されているため(F1513〜F1517)、この間、CPU390は、実行順序が来るたびに再びラウンドロビンのキューに入る(F1513)ことを繰り返している。

そして、前記F1619において、前述のようにDHフラグレジスタ330が“1”にセットされたので、やがてCPU390は、DHフラグレジスタ330から“1”を読み出す(F1515)。

CPU390は、DHフラグレジスタ330を“0”にリセットし(F1520)、前述のタスクT120のF1507で読み出したデータに対応する処理を行う(F1521)。

以後、リモコンボタンが連続押下されている間は、192Tの間隔で当該リモコン受信回路400にリピートヘッダ部が到着し、そのたびに前述したように、DHフラグレジスタ330は“1”にセットされ、前記OFF検出回路320内のOFFカウンタ321は0にリセットされる(F1619)。

そしてCPU390は、タスクT121のF1515においてDHフラグレジスタ330から“1”を読み出すたびに、DHフラグレジスタ330を“0”にリセットし(F1520)、その連続押下されているボタンに対応する処理を行う(F1521)。

そして、使用者がリモコンボタンをリリースすると、リピートヘッダ部は到着しなくなり、リモコン信号に長いハイ区間が現れる。最後のリピートヘッダから200T後、OFFカウンタ321の出力値は200Tに達し(F1621)、ONフラグレジスタ323は“0”にリセットされる(F1623)。

やがて、CPU390側は、DHフラグレジスタ330とONフラグレジスタ323から“0”を読み出すと(F1515、F1517)、CPU390は、モードレジスタ180に“1”を設定し(F1518)、タスクT120をラウンドロビンのタスクとして起動し(F1519)、現在実行中のタスクT121をラウンドロビンのタスクから外す。すなわち、最初にCPU390がタスクT120を起動させた時点と同じ状態に戻る(F1503)。

従って、使用者によってリモコンボタンがリリースされた後に、当該リモコン受信回路300にパルスノイズが入り、前記エッジ検出回路110から立上りエッジや立下りエッジの検出が通知されても、前記OFF検出回路140内のOFFカウンタ321は、ヘッダ検出を受けない限りリセットされない。従って、リモコンのボタンリリースは、OFF閾値レジスタ222に設定された時間どおりに判定される。

このように、本実施の形態3のリモコン受信システムによれば、前記実施の形態2と同様、当該リモコン受信回路300で受信するリモコン信号のデータ部が、メインデータ部と、該メインデータ部の0と1を反転させた反転データ部とで構成されている場合に、該リモコン受信回路300から割り込み生成回路を削除してCPU390に割り込みを発行しないようにし、またCPU390に割り込みポートを設けず、ラウンドロビンのタスクを持たせるようにしたので、リモコン受信機能に使用するCPU390のリリースをさらに少なくすることができる。

さらに、本実施の形態3のリモコン受信システムによれば、OFF検出回路320内にONフラグレジスタ323と、OFFカウンタ321とを設け、前記ONフラグレジスタ323の値は、前記OFFカウンタ321の値が、OFF閾値レジスタ222に設定されたリモコンボタンのリリース検出に用いる閾値(ここでは200T)と一致すれば“0”にリセットされ、該ONフラグレジスタ323が“0”になれば、リモコンボタンがリリースされたと判断するものとし、さらに、前記OFF閾値レジスタ222の設定値と比較される前記OFFカウンタ321は、常にカウントアップし前記DHフラグレジスタ330の値が“1”、つまりヘッダ検出を検知しないとリセットされないものであるようにしたので、リモコン信号の最後のリピートヘッダ部を受信してからある期間(ここでは200T)をカウントアップしている際に、ノイズによりエッジが発生してカウンタがリセットされることを防止でき、これにより、リモコンボタンのリリースの検出がノイズにより遅延されるのを回避することができる。

なお、前述の説明においては、リモコン受信回路300が、ボタンを連続押下された際に図22(a)に示されるようなデータを伴わないリピートヘッダ部からなるリモコン信号を受信する場合について説明したが、当該リモコン受信回路200において受信するリモコン信号は、ボタンを連続押下された際に図22(b)に示されるような同じ波形が繰り返し続くリモコン信号であってもよい。

以下、図16及び図17を用いて、前述した構成を持つリモコン受信回路300において、繰り返しデータ型の送信機から発信されたリモコン信号を受信した場合の処理の流れを説明する。図17(a)は、繰り返しデータ型のリモコン信号を受信した場合の、本実施の形態3におけるCPU側での処理を示すフローチャート図であり、図17(b)は、本実施の形態3におけるCPUのタスクT123の処理のフローチャート図であり、図17(c)は、本実施の形態3におけるCPUのタスクT124の処理のフローチャート図である。

まず、時刻N+2Tまでの動作は、前述のシーケンスと同様であるので、省略する。

時刻N+2Tにおいて、CPU390側では、前述したように、前記有効性判別回路210により有効と判断されたデータを読み出して(F1707)、押下されたリモコンボタンに対応する処理をする(F1709)。そしてこの後、リピートヘッダ部を受信した際には、前述したようにモードレジスタ180の値を“0”にセットしたが、ここでは、モードレジスタ180の値を再設定せず、“1”のままでタスクT124を起動する(F1711)。

リモコンボタンが連続的に押下されている場合、時刻192Tにおいて繰り返しデータのヘッダ部が到着する。その後、時刻0〜N+2Tと同様の動作を経て、DHフラグレジスタ330が“1”にセットされる(F1613)。この前記タスクT124が開始されてから、前述のF1613の発生前までの間、CPU390側では、そのタスクT124の実行順序が来るたびにDHフラグレジスタ330“0”を読み出し(F1714)、ONフラグレジスタ323から“1”を読み出すので(F1716)、再びタスクT124のラウンドロビンのキューに入る(F1712)。そして、前記F1613の発生後、CPU390側は、やがてDHフラグレジスタ330から“1”を読み出す。そしてシフトレジスタ250からデータを読み出し(F1718)、そのデータの正当性を判断する(F1719)。そして、データが無効であれば、DHフラグレジスタ330をクリアして(F1723)再びラウンドロビンのキューに入り(F1712)、一方、該データが有効であれば、前回取得したデータと今回のデータとが同一であるかを比較する(F1720)そして、これらのデータが一致していたら、リモコンボタンの連続押下中と判断して、その連続押下されたボタンに対応する処理を行い(F1721)、データが一致してなければ、新たに別のボタンが押下されたものと判断して、その新たに押下されたボタンに対応する処理を行った後(F1722)、DHフラグレジスタ330の値を“0”にセットして、再びラウンドロビンのキューに入る(F1712)。

そして、使用者がリモコンボタンをリリースすると、繰り返しデータは到着しなくなり、リモコン信号には長いハイ区間が現れる。そして、最後の繰り返しデータから200T後、OFFカウンタ321の出力値は200Tに達し(F1621)、ONフラグレジスタ323は“0”にリセットされる(F1627)。

やがて、CPU390側では、タスクT124によって、DHフラグレジスタ330とONフラグレジスタ323から“0”を読み出すと(F1714、F1716)、CPU390は、タスクT123を起動し(F1717)、現在実行中のタスクT124をラウンドロビンのタスクから外す。すなわち、最初にCPU390がタスクT123を起動させた時点と同じ状態に戻る(F1703)。

このように本実施の形態にかかるリモコン受信システムは、繰り返しデータを送信するタイプの送信機にも対応しえ、またこの繰り返しデータ受信の場合においても、使用者によってリモコンボタンがリリースされた後に、当該リモコン受信回路300において、ノイズ等の原因によってヘッダと認識できる波形や、データと認識できる波形が現れたとしても、前記OFF検出回路140内のOFFカウンタ321は、ヘッダ部と有効なデータ部を検出しない限りリセットされない。従って、リモコンのボタンリリースは、OFF閾値レジスタ222に設定された時間どおりに判定される。

(実施の形態4)

以下、図18〜図20を用いて、本実施の形態4におけるリモコン受信回路及びリモコン受信システムについて説明する。

本実施の形態4においては、リモコン信号のヘッダ部の検出精度を改善するものである。

まず、図18を用いて、本実施の形態4にかかるリモコン受信システムの構成について説明する。図18は、本実施の形態4におけるリモコン受信システムの構成を示す図である。

図18において、本実施の形態4にかかるリモコン受信システムは、送信機(図示せず)から発行されたリモコン信号を受信するリモコン受信回路400と、該リモコン受信回路400の各種レジスタに任意の値を設定し、リモコン受信回路400を制御するCPU490とからなるものであり、前記リモコン受信回路400は、エッジ検出回路110と、カウンタ回路420と、ヘッダ検出回路430と、データ判別回路140と、シフトレジスタ150と、ヘッダ割り込み生成回路160と、データ割り込み生成回路170と、モードレジスタ180と、スイッチ111とから構成される。そして、前記CPU490は、で、前記リモコン受信回路400からの割り込み信号S111を受信する、1つの割り込みポート491を備えるものである。

以下、前記リモコン受信回路400の構成を詳述すると、前記カウンタ回路420は、LLC121,LHC422に加え、ノイズ閾値レジスタ(以下、「THNレジスタ」と称す。)423を有するものであり、該THNレジスタ423はCPU490から値を設定されるレジスタである。そして、前記カウンタ回路420内のLHC422が“0”にリセットされる条件は、データ待ちフラグ141が“1”であるか、ヘッダ検出信号S430が“1”であるならば、前記エッジ検出回路110が立下りエッジを検出するときであり、前記データ待ちフラグ141とヘッダ検出信号S430が共に“0”であるならば、前記LLC121の値とTHNレジスタ423の値とが等しくなるときである。

前記ヘッダ検出回路430は、THHレジスタ132及びTHLレジスタ131に加え、ロングロウフラグ433(以下、「LLF」と称す。)を有する。そして、前記LLF433は、LLC121の値がTHLレジスタ131の値と等しくなると“1”にセットされ、データ待ちフラグ141が“1”になるか、もしくはLLC121の出力値がTHNレジスタ423の値と等しくなると“0”にリセットされる。そして、前記ヘッダ検出回路430は、LLF433が“1”で、かつ、LHC422の出力値がTHHレジスタ132の設定値を上回っているときに、ヘッダ検出信号S430“1”を出力し、それ以外のときにヘッダ検出信号S430“0”を出力する。なお、そのほかの構成は、前記実施形態1と同様であるため、ここでは説明を省略する。

次に、図3、図19及び図20を用いて、前述した構成を有するリモコン受信システムの動作について説明する。図19は、本実施の形態4にかかるリモコン受信システムがリモコン信号のヘッダ部を受信した場合のリモコン受信回路及びCPUのタイミングチャート図であり、図20は、リピートヘッダ型の送信機から発信されたリモコン信号を受信した場合の、本実施の形態4におけるリモコン受信回路での処理を示すフローチャート図である。

まず、CPU490は、動作開始時に、ヘッダ検出回路430内のTHLレジスタ131とTHHレジスタ132、データ判別回路140内のDLレジスタ142、及びモードレジスタ180の値に加え、前記カウンタ回路420内のTHNレジスタ423に値を設定する(F301,F302)。

以下、前記各レジスタに設定される値について具体的に説明すると、前記実施の形態1と同様、前記THLレジスタ131には6T、前記THHレジスタ132には3T、前記DLレジスタには32T、そして前記モードレジスタ180には1を設定する。

そしてここでは、例えば前記THNレジスタ423に1Tを設定するものとする。すなわち、リモコン信号のヘッダ部のロングハイ区間に、前記THNレジスタ423に設定した1T以下のロウ区間が現れた場合、そのロウ区間をノイズとして無視する設定とする。

そして以上のように各レジスタに値を設定した後、CPU490は、リモコン受信回路400からデータ割り込みが発行されるのを待つ。

なお、リモコン受信回路400側のヘッダ検出回路430以外の動作については、前記実施の形態1と同様であるので、ここでは省略し、以下の動作説明においては、リモコン信号のヘッダ部の波形にノイズが発生した状況下での前記ヘッダ検出回路430の動作のみ説明する。

リモコンのボタンが押下されると、まずリモコン受信回路400にはリモコン信号のヘッダ部が到着する。ヘッダ部の最初の立下りエッジをエッジ検出回路110が検出した時刻を時刻0とすると、時刻0において、カウンタ回路420内のLLC121がリセットされる(F2005)。

時刻1Tにおいて、前記データ待ちフラグ141及びヘッダ検出信号S430が共に“0”であり(F2029)、そして前記カウンタ回路420内のLLC121の出力値が前記THNレジスタ423と一致するので(F2030)、前記カウンタ回路420内のLHC422の値がリセットされる(F2031)。

そして、時刻6Tにおいて、カウンタ回路420内のLLC121の出力値と、前記ヘッダ検出回路430内のTHLレジスタ131の値が等しくなり(F2017)、この時、前記ヘッダ検出回路430内のLLF433が“1”にセットされる(F2018)。

そして、時刻16Tにおいて、前記エッジ検出回路110は立上りエッジを検出し(F2015)、そして、時刻17Tにおいて、ノイズによる立下りが、エッジ検出回路110において検出される(F2002)。この時、データ待ちフラグ141の値もヘッダ検出信号S430も“0”であるため(F2003)、前記カウンタ回路420内のLLC121がリセットされ、LLC121のカウントが始まる(F2005)。しかしこの時、LHC422はリセットされず、そのときのカウント値“1T”を保つ。

そして、時刻17.5Tにおいて、ノイズによる負のパルスが終了し、エッジ検出回路110が立上りエッジを検出する(F2015)。これにより、前記LLC121がストップし、前記LHC422がカウントを開始するが(F2032)、前述した時刻17Tにおいて前記LHC422はリセットされず、それまでのカウント値“1T”を保持しているので、その1Tからのカウントとなる。

そして、時刻19.5Tにおいて、前記LHC422の出力値は、前記ヘッダ検出回路430内のTHHレジスタ132と等しくなり(F2019)、ヘッダ検出信号S430“1”が出力されると同時に、データ判別回路140内のデータ待ちフラグ141が“1”にセットされ、前記ヘッダ検出回路430内のLLF433は“0”にリセットされる(F2020)。

そして時刻24Tに、前記エッジ検出回路110が立ち下がりエッジを検出すると(F2002)、LHC422の値がリセットされて(F2004)、THHレジスタ132の値より小さくなるので、ヘッダ検出信号S430が立下る(F2023)。以後の動作は、実施の形態1と同様である。

このように、本実施の形態4によれば、リモコン受信回路400が、図19に示すように、CPU490において予め指定された期間以内のノイズ、ここでは期間1T以下のノイズを含むリモコン信号を受信した場合は、そのノイズをノイズと判断して無視することができ、リモコン信号のヘッダ部を検出する際に、ノイズの影響を受けにくくすることができる。

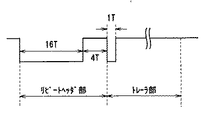

なお、前述の全ての実施の形態においては、リモコン受信回路に入力されるリモコン信号が、図22(a)に示されるように、リモコン信号のヘッダ部がロウ区間が16Tでハイ区間が8Tで、リピートヘッダ部のロウ区間が16Tでハイ区間が4Tであり、また、リモコン信号のデータ部が32ビットで、データ部のLongLowとLongHighのデューティが1:1ならばデータ“0”に、1:3ならばデータ“1”に対応するものとし、これにより、当該リモコン受信回路のDLレジスタ142に32、THHレジスタ132に3T、THLレジスタ131に6Tを設定し、D1フラグ144が、LHCが“1T”になれば立ち上がってシフトレジスタ150に“1”が格納され、D0フラグ145が、LHCが2Tになれば立ち上がってシフトレジスタ150に“0”が格納されるものとして説明したが、前記各レジスタの設定値や、各フラグの立ち上がり、立下りタイミングは、前述したものに限るものではなく、当該リモコン受信システムに入力されるリモコン信号に応じた値を各レジスタに設定し、また前記リモコン信号に応じたタイミングで各フラグの立下り、立ち上がりタイミングを設定して制御するようにすれば、どのようなリモコン信号を受信しても対応可能である。