JP3604635B2 - 回路コンポーネントを有する電気回路、および回路コンポーネントのテスト方法 - Google Patents

回路コンポーネントを有する電気回路、および回路コンポーネントのテスト方法 Download PDFInfo

- Publication number

- JP3604635B2 JP3604635B2 JP2001017347A JP2001017347A JP3604635B2 JP 3604635 B2 JP3604635 B2 JP 3604635B2 JP 2001017347 A JP2001017347 A JP 2001017347A JP 2001017347 A JP2001017347 A JP 2001017347A JP 3604635 B2 JP3604635 B2 JP 3604635B2

- Authority

- JP

- Japan

- Prior art keywords

- bus

- circuit

- output

- test

- data

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/26—Testing of individual semiconductor devices

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/28—Testing of electronic circuits, e.g. by signal tracer

- G01R31/317—Testing of digital circuits

- G01R31/3181—Functional testing

- G01R31/3185—Reconfiguring for testing, e.g. LSSD, partitioning

- G01R31/318505—Test of Modular systems, e.g. Wafers, MCM's

-

- H10P74/00—

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- Tests Of Electronic Circuits (AREA)

- Test And Diagnosis Of Digital Computers (AREA)

Description

【発明の属する技術分野】

本発明は、バスを介して接続された回路コンポーネントを有する電気回路に関する。本発明はまた、バスを介して接続された複数の回路コンポーネントのうち1つの回路コンポーネントをテストする方法に関する。

【0002】

【従来の技術】

テストすべき回路コンポーネントは例えば集積回路のいわゆるマクロである。集積回路をテストする際には所定のマクロを個々に、すなわち集積回路の他の回路コンポーネントから独立にテストしなければならない。

【0003】

この種のテストでは集積回路の比較的小さい部分のみがテストされるが、この種のテストは特にテスト中この集積回路を通って流れるきわめて高い電流とこれに関連した極端な温度上昇とのためにしばしば大きなコストがかかる。さらに前述の理由から実際の状態に相応しないテスト結果が得られることもある。

【0004】

【発明が解決しようとする課題】

本発明の課題は、テストすべき回路コンポーネントを最小のコストで確実にテストできるようにすることである。

【0005】

【課題を解決するための手段】

この課題は、少なくとも1つの回路コンポーネントは他の回路コンポーネントとは独立にテスト可能であり、他の回路コンポーネントとは独立にテスト可能な少なくとも1つの回路コンポーネントは当該の回路コンポーネントの通常動作中にもテスト中にもデータを形成し、このデータはバスへ出力することもできるし、また回路コンポーネントのテストのために設けられたテストユニットへバスを介さずに供給することもでき、当該の回路コンポーネントの通常動作中はデータはバスへ出力され、当該の回路コンポーネントのテスト中はデータはバスへは出力されない構成の電気回路により解決される。

【0006】

課題はまた、少なくとも1つの回路コンポーネントを他の回路コンポーネントとは独立にテスト可能であり、テストされる回路コンポーネントは通常動作中にもテスト中にもデータを形成し、このデータはバスへ出力することもできるし、また当該の回路コンポーネントのテストのために設けられたテストユニットへバスを介さずに供給することもでき、当該の回路コンポーネントの通常動作中はデータをバスへ出力し、当該の回路コンポーネントのテスト中はデータをバスへは出力しないことにより解決される。

【0007】

【発明の実施の形態】

本発明の特徴により、テストすべき回路コンポーネントの出力ドライバがエネルギを全く消費しないか、またはきわめて僅かしか消費しない状態が達成される。このことはテストすべき回路コンポーネントを介してデータがバスへ出力されないケースで明らかであるが、データがバスへ出力されるケースでも相当する。すなわちテストすべき回路コンポーネントのテスト中にバスへ出力されるデータは当該の回路コンポーネントが通常動作中にバスへ出力するデータと同一ではなく、出力ドライバのエネルギ消費が最小となるように選定されて出力されるのである。

【0008】

出力ドライバは、バスへ出力されるデータが変更されないか、またはきわめてまれにしか変更されない場合、特に僅かなエネルギ消費しか有さない。ここで相当の容量を有するバス線路のローディング切換は特にクロック周波数が高い場合には比較的大きな電流を必要とするが、本発明ではこのローディング切換(アップロード/ダウンロード切換)を全く行わなくてよくなるか、またはほとんど行わなくてよくなる。このようにバス線路のローディングが全くまたはほとんど必要ないことは、出力ドライバからの大きな電流の送出が全く必要ないかほとんど必要なくなるので有利である。さらにこれにより当該の回路コンポーネントはテストの際に必要な処置を採用しなかった場合と比べて格段に小さな温度上昇で済む。

【0009】

出力ドライバの小さな電流消費、ひいてはこれに結びついた利点は、付加的または選択的にバスへ出力すべきデータのタスクをテスト中は出力ドライバを回避して行うことにより達成される。出力ドライバはテスト中遮断されるか、または不活性化される。

【0010】

テストすべき回路コンポーネントは、テスト中、通常であれば出力されるデータをバスへ出力しないか、および/または通常のデータと異なるデータを出力するが、テスト結果には影響はない。テストすべき回路コンポーネントは別の回路コンポーネントとは独立にテストされるので、これによりバスを介して回路コンポーネントと電気回路との間のデータ交換を行う必要はない。

【0011】

独立請求項記載の特徴を有する電気回路およびテスト方法によれば、テストすべき回路コンポーネントを最小コストで確実にテストすることができる。

【0012】

本発明の有利な実施形態は、従属請求項、以下の説明および図から得られる。

【0013】

【実施例】

本発明を以下に実施例に則して図に関連して詳細に説明する。

【0014】

以下に説明する電気回路は集積回路である。しかしこれは何ら限定されるものでないことを指摘しておく。この電気回路は任意の別の電気回路であってよい。

【0015】

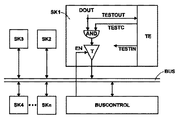

この電気回路の第1の実施例は図1に示されている。

【0016】

図1に示された電気回路は回路コンポーネント(マクロ)SK1,SK2,...,SKn、これらの回路コンポーネントSK1,SK2,...,SKnに接続されたバスBUS、およびバスBUSの制御(特にアービトレーション)を担当するバス制御装置BUSCONTROLから成る。

【0017】

回路コンポーネントSK1,SK2,...,SKnのなかに、個々に、すなわち他の回路コンポーネントとは独立に、電気回路によってテストされる少なくとも1つの回路コンポーネントが存在する。これは、この実施例では、SK1で示された回路コンポーネントである。

【0018】

回路コンポーネントSK1はこの実施例ではメモリモジュールであり、より正確に言えばDRAMマクロである。ただしこれも何ら限定されるものではないことを指摘しておく。以下に説明するテスト可能な回路コンポーネントは任意の回路部分であってよい。

【0019】

回路コンポーネントSK1をテストするためにテストユニットTEが設けられている。このテストユニットはこの実施例ではテストすべき回路コンポーネントSK1の構成部分である。ただしこれも限定されるものではない。テストユニットTEをテストすべき回路コンポーネントSK1の外部に設けることもできる。この場合、ユニットを電気回路内部の任意の位置に配置してもよいし、その外部に配置してもよい。

【0020】

テストユニットTEはa)テストデータTESTINをテストすべき回路コンポーネントSK1へ入力結合し、b)テストデータTESTOUTをテストすべき回路コンポーネントSK1から出力し、c)テストすべき回路コンポーネントSK1をテスト制御信号TESTCにより制御し、d)テストデータTESTIN、TESTOUTに基づいてテストすべき回路コンポーネントSK1が正しく動作しているか否かを検査する。

【0021】

回路コンポーネントSK1の通常動作時、すなわち回路コンポーネントSK1がテストされていない場合には、a)回路コンポーネントSK1にバスBUSと図1には示されていないデータ受信装置とを介してデータが供給され、b)回路コンポーネントSK1により複数の出力ドライバ(このうち図1には唯一の出力ドライバTのみが示されている)を介してデータがバスBUSへ出力される。

【0022】

出力ドライバTはこの実施例ではいわゆるトライステートドライバであり、バス制御装置BUSCONTROLによって制御される。より正確に言えば出力ドライバは出力されたイネーブル信号ENによって活性化ないし不活性化される。出力ドライバTが活性化されている場合、すなわちこの実施例のEN=1である場合、出力ドライバは個々に供給されるデータをバスBUSへ出力する。出力ドライバTが不活性状態である場合、すなわちこの実施例のEN=0である場合、データはバスBUSへは出力されない。出力ドライバはその場合高オーム状態にある。

【0023】

回路コンポーネントSK1のテスト中には、a)回路コンポーネントSK1によりバスBUSを介して供給されるデータの代わりにテストユニットTEのテストデータTESTINが使用され、b)このデータがテストユニットTEのテストデータTESTOUTとして使用される。つまりc)通常動作でバスBUSへ出力されるデータに代えて、別のデータがバスへ出力される。

【0024】

回路コンポーネントSK1のテスト中にバスBUSへ出力されるデータは、この実施例では、本来バスへ出力すべきデータとは無関係に形成される。このデータは全く変更されないか、またはきわめてまれにしか変更されないという特殊性を有する。

【0025】

この実施例では、回路コンポーネントSK1のテスト中、持続的にレベル“0”を表すデータをバスBUSへ出力する。

【0026】

いつどんなデータがバスBUSへ出力されるかは、この実施例では出力ドライバTの前方に接続された論理素子により定められる。

【0027】

論理素子はこの実施例ではAND素子ANDから成り、回路コンポーネントSK1の通常動作中にバスBUSへ出力すべきデータDOUTおよびテスト制御信号TESTCを入力信号として受け取る。論理素子の出力信号は出力ドライバTに入力信号として供給される。

【0028】

テスト制御信号TESTCは回路コンポーネントSK1の通常動作中は値“1”を有する。これによりAND素子の出力信号DOUTはAND素子の入力信号に相応する。これにより回路コンポーネントSK1の通常動作中は本来バスBUSへ出力すべきデータDOUTがバスへ出力される。

【0029】

回路コンポーネントSK1のテスト中、テスト制御信号は値“0”を有する。これによりAND素子の出力信号はAND素子の他の入力信号の値には無関係に値“0”を取る。これにより回路コンポーネントSK1のテスト中は持続的に値“0”がバスへ出力される。

【0030】

回路コンポーネントSK1のテスト中には全く変更されないかまたはほとんど変更されないデータがバスBUSへ出力されることにより、バス線路がローディング切換を全く行わなくてよいか、またはほとんど行わなくてよいという有利な効果が得られる。これはa)出力ドライバTが僅かなエネルギしか消費せず、b)出力ドライバTおよび回路コンポーネントSK1が過剰に加熱されないので有利である。

【0031】

電気回路がテスト中わずかなエネルギしか消費せず、これにより電気回路のテスト中比較的低い温度が維持されることにより、テストすべき回路コンポーネントSK1を最小のコストで確実にテストできる。これは特にa)電気回路にテスト中エネルギを供給する部材(ニードル)の数およびサイズを小さく維持でき、b)比較的簡単に低温テストを行えることにより達成される。

【0032】

回路コンポーネントSK1のテスト中には本来バスBUSへ出力すべきデータDOUTでなく別のデータがバスへ出力されるが、負の影響がテスト結果に作用することはない。テストすべき回路コンポーネントSK1は他の回路コンポーネントから独立して電気回路によってテストされるので、回路コンポーネントSK1からバスへデータが出力されるか否か、または出力されるデータがどんなものであるかということは重要な意味を持たない。

【0033】

回路コンポーネントSK1がデータをバスBUSへ出力しない構成は有利であると判明している。仮に回路コンポーネントSK1が出力ドライバをテスト中自動的に不活性化する(すなわち高オーム状態へ移行させる)ように構成したとすると、問題が発生する可能性がある。一般にはバスBUSに接続されている全てのコンポーネントは短時間であっても同時に高オーム状態へ移行する出力ドライバを有してはならないからである。バスBUSはつねに接続されているコンポーネントによって終端していなければならない。

【0034】

ただし本発明によればこの問題は発生しない。このためバス制御装置は回路コンポーネントSK1のテスト中変更されずに更に処理され、唯一の制御はバスBUSを介して行われる。更にこれにより複数の回路コンポーネントを電気回路によって同時にテスト可能となる。

【0035】

回路コンポーネントSK1のテスト中必ずしも持続的にレベル“0”を表すデータをバスBUSへ出力しなくともよいことがわかる。ここでは持続的にレベル“1”を表すデータをバスBUSへ出力することもできる。さらに回路コンポーネントSK1のテスト中、持続的に所定のレベルを有するデータをバスBUSへ出力するのではなく、バスへ出力されるデータを変更することもできる。ただしバスへ出力されるデータはまれにしか変更できない。このようにして不変のデータをバスへ出力する場合とほぼ同じ有利な効果を達成することができる。

【0036】

同様に、バスへ出力すべきデータを形成する論理素子が必ずしも前述のように構成ないし配置されたAND素子でなくともよい。これに対しては多数の他の手段が考えられる。例えばAND素子に代えてNAND素子を使用してもよいし、また選択的に通常動作で出力すべきデータDOUTまたはテスト中の出力データを出力ドライバTへ導通するマルチプレクサを使用してもよい。

【0037】

電気回路はテストすべき回路コンポーネントがテスト中にデータをバスへ出力しないように構成することもできる。

【0038】

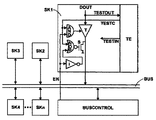

この種の電気回路の実施例を図2に示し、以下にこれを参照しながら説明する。

【0039】

図2に示されている電気回路は図1に示された電気回路に完全に相応する。図2に示された電気回路は図1に示された電気回路と同様に、回路コンポーネント(マクロ)SK1,SK2,...,SKn、これらの回路コンポーネントSK1,SK2,...,SKnに接続されたバスBUS、およびこのバスBUSの制御(特にアービトレーション)を担当するバス制御装置BUSCONTROLから成る。またここに存在している回路コンポーネントSK1,SK2,...,SKnのなかに、個々にすなわち他の回路コンポーネントから独立して電気回路によってテストされる参照番号SK1で示された回路コンポーネントが存在する。テストすべき回路コンポーネントのテストは図1の電気回路内に設けられているテストユニットTEと同様に、テストすべき回路コンポーネントすなわち回路コンポーネントSK1内に含まれているテストユニットTEによって行われる。ここまでは図1の電気回路と図2の電気回路とは一致している。

【0040】

図1の回路コンポーネントSK1とは異なって、図2の回路コンポーネントSK1はテスト中にバスBUSへデータを出力しない。

【0041】

この実施例では、図2の回路コンポーネントSK1に設けられている出力ドライバTの(制御)端子にはバス制御装置BUSCONTROLから出力されるイネーブル信号ENではなく、制御端子に前置接続されている論理素子の出力信号が印加される。出力ドライバは制御端子を介して活性化ないし不活性化される。

【0042】

この論理素子はこの実施例ではAND素子ANDから成っており、この論理素子はイネーブル信号ENおよび図2の電気回路に設けられているテスト制御信号TESTCを入力信号として受け取る。論理素子の出力信号は出力ドライバTの制御に使用される。

【0043】

テスト制御信号TESTCは回路コンポーネントSK1の通常動作中に値“1”を有する。これにより回路コンポーネントSK1の通常動作中、出力ドライバの制御に使用されるこの信号はイネーブル信号ENに相応する。

【0044】

回路コンポーネントSK1のテスト中、テスト制御信号TESTCは値“0”を有する。したがって回路コンポーネントSK1のテスト中、出力ドライバTの制御に使用される信号は持続的に値“0”を有する。これにより出力ドライバTは不活性化され、データはバスBUSへ出力されない。

【0045】

図1の電気回路とは異なり、図2の電気回路ではテスト制御信号TESTCはテストすべき回路コンポーネントSK1のみにではなく、バスターミネーション論理素子BTLにも供給される。この論理素子はこの実施例ではバス制御装置BUSCONTROLの構成部分である。

【0046】

バスターミネーション論理素子BTLは、バスBUSが回路コンポーネントSK1のテスト中(テスト制御信号TESTCによって回路コンポーネントSK1のテストが信号化されている間)バスBUSに接続された他のコンポーネントによって終端されるように制御する。この実施例では、バスターミネーション論理素子BTLはバスBUSを必要に応じてそれ自体で終端させる。これに代えてバスターミネーション論理素子BTLが回路コンポーネントSK1のテスト中に、バスBUSに接続された他の1つの回路コンポーネントの出力ドライバを活性化し、当該のコンポーネントをバスに終端させるように構成してもよい。

【0047】

論理素子を使用して出力ドライバTを制御する制御信号が形成されるが、これは必ずしも前述のように構成ないし配置されたAND素子でなくともよい。このために多数の別の手段がある。すなわち例えばAND素子に代えてNAND素子を使用してもよいし、また選択的にイネーブル信号ENまたは出力ドライバTの制御端子を制御するテスト制御信号TESTCを導通するマルチプレクサを使用してもよい。

【0048】

回路コンポーネントSK1のテスト中データがバスBUSへ出力されないことにより、出力ドライバTがエネルギを全く消費しないか、または無視できる程度に小さいエネルギ消費しか有さず、これにより温度上昇は全く生じないか、きわめて僅かしか生じないという有利な作用が得られる。

【0049】

電気回路がテスト中僅かしかエネルギを消費せず、したがってこの電気回路はテスト中比較的低温に維持されることにより、テストすべき回路コンポーネントSK1は最小のコストで確実にテストされる。これは特にa)電気回路にテスト中エネルギを供給する部材(ニードル)の数およびサイズが小さく維持され、b)比較的簡単に低温テストが実行できることにより達成される。

【0050】

これらの利点は図2の電気回路で図1の電気回路よりもさらに際立っている。

【0051】

図3に示された参照番号にしたがって以下に説明する電気回路によれば、図1の電気回路の利点、すなわちテストすべき回路コンポーネントのテスト中、場合により必要なバスのターミネーションがテストすべき回路コンポーネント自体により行われる利点と、図2の電気回路の利点、すなわちテストすべき回路コンポーネントの出力ドライバがテスト中全くエネルギを消費しないか、または無視できる程度に小さなエネルギしか消費しない利点とが同時に得られる。

【0052】

図3に示された電気回路はその大部分が図1、図2に示された電気回路に相応する。図3に示された電気回路は図1、図2に示された電気回路と同様に回路コンポーネント(マクロ)SK1,SK2,...,SKn、これらの回路コンポーネントSK1,SK2,...,SKnに接続されたバスBUS、およびバスBUSの制御(特にアービトレーション)を担当するバス制御装置BUSCONTROLから成る。またここに存在している回路コンポーネントSK1,SK2,...,SKnのなかに、個々にすなわち他の回路コンポーネントから独立して電気回路によってテストされる参照番号SK1で示された回路コンポーネントが存在する。テストすべき回路コンポーネントのテストは図1、図2の電気回路内に設けられているテストユニットTEと同様にテストすべき回路コンポーネントすなわち回路コンポーネントSK1内に含まれているテストユニットTEによって行われる。ここまでの点では図1、図2の電気回路と図3の電気回路とは一致している。

【0053】

図1の回路コンポーネントSK1と同様に、ただし図2の回路コンポーネントSK1とは異なって、図3の回路コンポーネントSK1はテスト中必要に応じて(特に回路コンポーネントSK1がバス制御装置BUSCONTROLによりバスパターンとして定められている場合に)データをバスBUSへ出力する。

【0054】

このことはこの実施例では、図3の回路コンポーネントSK1に設けられている出力ドライバTを介してではなく、出力ドライバTの出力端子とバスBUSとの間に存在する位置に所定の電位または所定の電圧特性を印加することにより行われる。

【0055】

ここでの所定の電位はこの実施例ではアース電位である。ただしこれは任意の他の電位であってもよいし、また時間的に変化する電位であってもよい。

【0056】

出力ドライバTの出力端子とバスBUSとの間に存在する位置への所定の電位または所定の電圧特性の印加は、この実施例ではスイッチング装置Sを介して行われ、このスイッチング装置はここではトランジスタによって形成される。この場合基本的にトランジスタの形態は重要な意味を有さない。トランジスタに代えて任意の他のスイッチング装置、例えばいわゆるトランスミッションゲートを使用することもできる。

【0057】

スイッチング装置Sは論理素子により制御される。論理素子はこの実施例ではNOR素子NORおよびインバータIから成っており、NOR素子はテスト制御信号TESTCを入力信号として受け取り、インバータIは反転されたイネーブル信号ENを入力信号として受け取る。NOR素子の出力信号はスイッチング装置Sを制御するために使用される。

【0058】

テスト制御信号TESTCおよびイネーブル信号ENは図1、図2の電気回路での同名の信号に相応する。

【0059】

テストすべき回路コンポーネントSK1の出力ドライバTはテスト中は不活性化されている。不活性化はこの実施例では、出力ドライバTを活性化ないし不活性化するこのドライバの制御端子に対して、図2の電気回路での場合と同様に、この制御端子に前置接続された論理素子の出力信号が印加されることにより達成される。

【0060】

論理素子はこの実施例では図2の電気回路での場合と同様にAND素子から成っており、テスト制御信号TESTCおよびイネーブル信号ENを入力信号として受け取る。この論理素子の出力信号は出力ドライバTを制御するために使用される。

【0061】

バスBUSのターミネーションを制御するスイッチング装置Sと出力ドライバTとは論理素子AND、I、NORによって制御され、その結果次の関係が得られる。

【0062】

【表1】

【0063】

図3の電気回路はa)図1の電気回路に比べて、通常動作でデータDOUTが出力される経路に付加的な論理素子が存在せず、これによりデータ出力を迅速に行うことができ、また出力ドライバがテストすべき回路コンポーネントのテスト中に不活性化されているので、テスト中に僅かなエネルギしか消費せず、したがって僅かしか温度が上昇しない利点を有しており、b)図2の電気回路に比べて、テストすべき回路コンポーネント自体がバスを終端するため、バスターミネーション論理素子BTLまたは同様の装置を省略できる利点を有する。またこの電気回路によって図1、図2の電気回路に比べて重大な欠点を甘受しなければならないということもない。

【0064】

出力ドライバTおよびスイッチング装置Sを制御する制御信号の形成に使用される論理素子は必ずしも前述のように構成ないし配置しなくてもよい。これに対して多数の別の手段が可能である。

【0065】

出力ドライバTが回路コンポーネントSK1のテスト中不活性化されていることにより、このドライバはエネルギを全く消費しないか、または無視できる程度に小さいエネルギしか消費しないので有利である。したがって温度上昇も全く生じないか、またはほとんど生じない。

【0066】

電気回路がテスト中僅かしかエネルギを消費せず、したがってこの電気回路はテスト中比較的低温に維持されることにより、テストすべき回路コンポーネントSK1は最小のコストで確実にテストされる。これは特にa)電気回路にテスト中エネルギを供給する部材(ニードル)の数およびサイズが小さく維持され、b)比較的簡単に低温テストが実行できることにより達成される。

【0067】

テストすべき回路コンポーネントをテストするための当該の手段は通常動作中にも格別の影響を有さない。特にテストすべき回路コンポーネントの動作速度や他の主要な特性に対して影響を与えるおそれは全くない。

【0068】

前述の電気回路は実際の実現形態での個々の独立性とは無関係に驚くほど簡単に構成できる。これによりテストすべき回路コンポーネントを最小のコストで確実にテストすることができる。

【図面の簡単な説明】

【図1】電気回路の第1の実施例を説明するための図である。

【図2】電気回路の第2の実施例を説明するための図である。

【図3】電気回路の第3の実施例を説明するための図である。

【符号の説明】

SK1,SK2,...,SKn 回路コンポーネント

BUS バス

BUSCONTROL バス制御装置

T 出力ドライバ

TE テストユニット

AND AND素子

NOR NOR素子

I インバータ

S スイッチング装置

TESTIN,TESTOUT テストデータ

TESTTC テスト制御信号

EN イネーブル信号

DOUT 出力データ

Claims (21)

- バス(BUS)を介して接続された回路コンポーネント(SK1〜SKn)を有する電気回路において、

少なくとも1つの回路コンポーネント(SK1)は他の回路コンポーネント(SK2〜SKn)とは独立にテスト可能であり、

他の回路コンポーネント(SK2〜SKn)とは独立にテスト可能な少なくとも1つの回路コンポーネント(SK1)は当該の回路コンポーネントの通常動作中にもテスト中にもデータ(DOUT)を形成し、

該データはバスへ出力することもできるし、また回路コンポーネントのテストのために設けられたテストユニット(TE)へバスを介さずに供給することもでき、

当該の回路コンポーネントの通常動作中はデータはバスへ出力され、

当該の回路コンポーネントのテスト中はデータはバス(BUS)へは出力されない

ことを特徴とする回路コンポーネントを有する電気回路。 - 他の回路コンポーネント(SK2〜SKn)とは独立にテスト可能な少なくとも1つの回路コンポーネント(SK1)はバス(BUS)へのデータの出力に用いられる出力ドライバ(T)を有しており、該出力ドライバは当該の回路コンポーネントのテスト中は供給されたデータをバス(BUS)へ出力しない状態へ移される、請求項1記載の電気回路。

- 供給されたデータをバス(BUS)へ出力しない状態への出力ドライバ(T)の遷移はテストユニット(TE)によりトリガされる、請求項2記載の電気回路。

- 供給されたデータをバス(BUS)へ出力しない状態への出力ドライバ(T)の遷移は該出力ドライバの制御端子の前方に接続された論理素子または選択回路を使用して行われ、前記出力ドライバにはバス(BUS)を制御するバス制御装置(BUSCONTROL)で形成されたイネーブル信号(EN)が供給され、前記論理素子により、他の回路コンポーネント(SK2〜SKn)とは独立にテスト可能な少なくとも1つの回路コンポーネント(SK1)のテスト中、イネーブル信号は当該の回路コンポーネントの出力ドライバには供給されず、テストユニットで形成されたテスト制御信号(TESTC)に依存して出力ドライバへのイネーブル信号の供給を行うか否かが定められる、請求項2または3記載の電気回路。

- 論理素子の出力信号はイネーブル信号(EN)およびテスト制御信号(TESTC)の論理結合の結果である、請求項4記載の電気回路。

- 選択回路はマルチプレクサによって形成されており、該マルチプレクサによって選択的にイネーブル信号(EN)またはテスト制御信号(TESTC)が出力ドライバ(T)の制御端子へ導通される、請求項4記載の電気回路。

- テストすべき回路コンポーネント(SK1)のテストがバス(BUS)を制御するバス制御装置(BUSCONTROL)に対してシグナリングされる、請求項1から6までのいずれか1項記載の電気回路。

- バス制御装置(BUSCONTROL)はテストすべき回路コンポーネント(SK1)のテスト中、他の回路コンポーネント(SK2−SKn)のうちの1つまたはバス制御装置(BUSCONTROL)そのものによって終端される、請求項7記載の電気回路。

- 他の回路コンポーネント(SK2−SKn)とは独立にテスト可能な少なくとも1つの回路コンポーネント(SK1)の通常動作中は当該の回路コンポーネントからバス(BUS)へ出力されるデータとテストユニット(TE)へ供給されるデータ(DOUT)とは同一であり、当該の回路コンポーネント(SK1)のテスト中にはバスへ出力されるデータとテストユニット(TE)から供給されるデータとは異なっている、請求項1記載の電気回路。

- テストすべき回路コンポーネント(SK1)のテスト中にバス(BUS)へ出力されるデータは全く変更されない、請求項9記載の電気回路。

- 他の回路コンポーネント(SK2−SKn)とは独立にテスト可能な少なくとも1つの回路コンポーネント(SK1)はバス(BUS)へのデータの出力に用いられる出力ドライバ(T)を有しており、該出力ドライバの入力端子の前方に論理素子または選択回路が接続されており、該論理素子によりテストユニットで形成されたテスト制御信号(TESTC)に依存してテストユニット(TE)へ供給されたデータ(DOUT)が出力ドライバへ供給されるかまたは他のデータが供給されるかが定められる、請求項9記載の電気回路。

- 論理素子の出力信号はテストユニットへ供給されたデータ(DOUT)とテスト制御信号(TESTC)との論理結合の結果であり、該出力信号を用いてテストユニット(TE)はテストすべき回路コンポーネント(SK1)がその時点でテストされていることをシグナリングする、請求項11記載の電気回路。

- 選択回路はマルチプレクサによって形成されており、該マルチプレクサにより選択的に、テストユニット(TE)へ供給されたデータ(DOUT)またはテストユニット(TE)からテストすべき回路コンポーネント(SK1)へ供給されたテスト制御信号(TESTC)がテストすべき回路コンポーネントの出力ドライバ(T)の入力端子へ導通される、請求項11記載の電気回路。

- 各出力ドライバ(T)に対して固有の論理素子または選択回路が設けられている、請求項4または11記載の電気回路。

- 論理素子または選択回路の出力信号は配属されている出力ドライバ(T)の入力信号である、請求項11記載の電気回路。

- テストすべき回路コンポーネント(SK1)のテスト中、当該の回路コンポーネントにより出力ドライバ(T)の出力端子とバス(BUS)との間に存在する位置へデータが供給される、請求項1から6までのいずれか1項記載の電気回路。

- 前記供給はスイッチング装置(S)を介して行われる、請求項16記載の電気回路。

- スイッチング装置(S)は論理素子により制御される、請求項15記載の電気回路。

- 前記論理素子の出力信号はバス制御装置で形成されたドライバ駆動のためのイネーブル信号(EN)とテスト制御信号(TESTC)との論理結合の結果である、請求項15記載の電気回路。

- スイッチング装置(S)はテスト動作中、論理回路(I,NOR)によって制御された状態で、バス(BUS)へ出力すべきデータが供給される位置と所定の電位を有する点とを接続する、請求項17から19までのいずれか1項記載の電気回路。

- バス(BUS)を介して接続された複数の回路コンポーネント(SK1〜SKn)のうち1つの回路コンポーネント(SK1)をテストする方法において、

少なくとも1つの回路コンポーネント(SK1)を他の回路コンポーネント(SK2〜SKn)とは独立にテスト可能であり、

テストされる回路コンポーネント(SK1)は通常動作中にもテスト中にもデータ(DOUT)を形成し、

該データはバスへ出力することもできるし、また当該の回路コンポーネントのテストのために設けられたテストユニット(TE)へバスを介さずに供給することもでき、

当該の回路コンポーネントの通常動作中はデータをバスへ出力し、

当該の回路コンポーネントのテスト中はデータをバス(BUS)へは出力しない

ことを特徴とする回路コンポーネントをテストする方法。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE10003260 | 2000-01-26 | ||

| DE10003260.5 | 2000-01-26 | ||

| DE10016127A DE10016127A1 (de) | 2000-01-26 | 2000-03-31 | Elektrische Schaltung und Verfahren zum Testen einer Schaltungskomponente der elektrischen Schaltung |

| DE10016127.8 | 2000-03-31 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001235518A JP2001235518A (ja) | 2001-08-31 |

| JP3604635B2 true JP3604635B2 (ja) | 2004-12-22 |

Family

ID=26004033

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001017347A Expired - Fee Related JP3604635B2 (ja) | 2000-01-26 | 2001-01-25 | 回路コンポーネントを有する電気回路、および回路コンポーネントのテスト方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6701473B2 (ja) |

| EP (1) | EP1132750B1 (ja) |

| JP (1) | JP3604635B2 (ja) |

| KR (1) | KR100437556B1 (ja) |

| DE (1) | DE50015199D1 (ja) |

| TW (1) | TW503322B (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7308439B2 (en) | 2001-06-06 | 2007-12-11 | Hyperthink Llc | Methods and systems for user activated automated searching |

| JP2019045960A (ja) * | 2017-08-30 | 2019-03-22 | 株式会社東芝 | ディスク装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2713724B2 (ja) | 1988-04-19 | 1998-02-16 | 株式会社日立製作所 | 半導体集積回路 |

| JP2827229B2 (ja) * | 1988-10-14 | 1998-11-25 | 日本電気株式会社 | 半導体集積回路 |

| JPH04138388A (ja) | 1990-09-29 | 1992-05-12 | Fuji Electric Co Ltd | 半導体集積回路およびその制御方法 |

| JP2806075B2 (ja) * | 1991-06-06 | 1998-09-30 | 日本電気株式会社 | マイクロコンピュータ |

| US5136185A (en) * | 1991-09-20 | 1992-08-04 | Hewlett-Packard Company | Local tristate control circuit |

| JPH0696599A (ja) | 1992-02-26 | 1994-04-08 | Nec Corp | 半導体集積回路 |

| EP0640919B1 (de) * | 1993-08-30 | 2003-03-05 | Infineon Technologies AG | Prozessorschaltung mit Testeinrichtung |

| US6041427A (en) * | 1997-10-27 | 2000-03-21 | Vlsi Technology | Scan testable circuit arrangement |

| JPH11248802A (ja) | 1998-03-06 | 1999-09-17 | Sony Corp | 半導体装置 |

| EP0992115B1 (en) * | 1998-04-23 | 2006-09-27 | Koninklijke Philips Electronics N.V. | Testable ic having analog and digital circuits |

| US6499124B1 (en) * | 1999-05-06 | 2002-12-24 | Xilinx, Inc. | Intest security circuit for boundary-scan architecture |

-

2000

- 2000-12-21 DE DE50015199T patent/DE50015199D1/de not_active Expired - Lifetime

- 2000-12-21 EP EP00128175A patent/EP1132750B1/de not_active Expired - Lifetime

-

2001

- 2001-01-20 TW TW090101508A patent/TW503322B/zh not_active IP Right Cessation

- 2001-01-25 JP JP2001017347A patent/JP3604635B2/ja not_active Expired - Fee Related

- 2001-01-26 KR KR10-2001-0003725A patent/KR100437556B1/ko not_active Expired - Fee Related

- 2001-01-26 US US09/771,391 patent/US6701473B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001235518A (ja) | 2001-08-31 |

| TW503322B (en) | 2002-09-21 |

| US20020008538A1 (en) | 2002-01-24 |

| US6701473B2 (en) | 2004-03-02 |

| KR20010078080A (ko) | 2001-08-20 |

| EP1132750A3 (de) | 2003-07-02 |

| KR100437556B1 (ko) | 2004-06-26 |

| EP1132750A2 (de) | 2001-09-12 |

| DE50015199D1 (de) | 2008-07-24 |

| EP1132750B1 (de) | 2008-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7034565B2 (en) | On-die termination circuit and method for reducing on-chip DC current, and memory system including memory device having the same | |

| US6275077B1 (en) | Method and apparatus for programmable adjustment of bus driver propagation times | |

| US20080276140A1 (en) | Semiconductor chip with a plurality of scannable storage elements and a method for scanning storage elements on a semiconductor chip | |

| JP2008524598A (ja) | 被試験デバイスのための電源としてパラメトリック測定ユニットを使用する方法及び装置 | |

| US5617040A (en) | Programmable output device with integrated circuit | |

| CN101009142A (zh) | 用于选择性地存取和配置半导体晶片的各个芯片的方法和装置 | |

| JP3604635B2 (ja) | 回路コンポーネントを有する電気回路、および回路コンポーネントのテスト方法 | |

| US7533208B2 (en) | Hot plug control apparatus and method | |

| JP3950646B2 (ja) | 負荷電流出力回路一体形ドライバ回路及、それを備えたピンエレクトロニクスic及びicテスタ | |

| JP2008524597A (ja) | パラメトリック測定ユニットを用いて被試験デバイスにおける電圧を検出する回路及び方法 | |

| US7057397B1 (en) | Output impedance measurement techniques | |

| US8395406B2 (en) | Integrated circuit architecture for testing variable delay circuit | |

| WO2020217925A1 (ja) | 半導体集積回路装置および半導体集積回路装置の検査方法 | |

| JP3857757B2 (ja) | 集積回路テスト装置 | |

| JPH08507610A (ja) | プリング抵抗を備える接続部をテストする装置 | |

| JP2007317345A (ja) | 半導体集積回路装置 | |

| US20240319260A1 (en) | State transition control for parametric measurement unit | |

| US8209571B2 (en) | Valid-transmission verifying circuit and a semiconductor device including the same | |

| CN1763555B (zh) | 半导体集成电路 | |

| KR100321177B1 (ko) | 메모리모듈의 인쇄회로기판 | |

| JP2001215463A (ja) | Lcdドライバのコモン出力設定回路及び設定方法並びにlcdドライバ用半導体装置 | |

| US20060170450A1 (en) | Integrated circuit with programmable-impedance output buffer and method therefor | |

| JP2021141204A (ja) | 半導体集積回路装置および半導体集積回路装置の検査方法 | |

| KR20070017651A (ko) | 입력핀에 터미네이션 저항을 갖는 반도체 메모리 장치 및방법 | |

| JP3093685B2 (ja) | 集積回路およびその機能試験方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040518 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040903 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040929 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20071008 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081008 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091008 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091008 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101008 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101008 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111008 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121008 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121008 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131008 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |