JP2022029308A - 配線基板及び配線基板の製造方法 - Google Patents

配線基板及び配線基板の製造方法 Download PDFInfo

- Publication number

- JP2022029308A JP2022029308A JP2020132588A JP2020132588A JP2022029308A JP 2022029308 A JP2022029308 A JP 2022029308A JP 2020132588 A JP2020132588 A JP 2020132588A JP 2020132588 A JP2020132588 A JP 2020132588A JP 2022029308 A JP2022029308 A JP 2022029308A

- Authority

- JP

- Japan

- Prior art keywords

- seed layer

- thin film

- oxide thin

- layer

- wiring board

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims description 30

- 238000004519 manufacturing process Methods 0.000 title claims description 20

- 239000010409 thin film Substances 0.000 claims abstract description 140

- 229910052751 metal Inorganic materials 0.000 claims abstract description 26

- 239000002184 metal Substances 0.000 claims abstract description 26

- 238000005530 etching Methods 0.000 claims description 61

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 claims description 32

- 238000004544 sputter deposition Methods 0.000 claims description 32

- 238000000231 atomic layer deposition Methods 0.000 claims description 18

- 238000001312 dry etching Methods 0.000 claims description 17

- 229910052786 argon Inorganic materials 0.000 claims description 16

- 229910000449 hafnium oxide Inorganic materials 0.000 claims description 9

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims description 9

- 230000000149 penetrating effect Effects 0.000 claims description 9

- 239000010408 film Substances 0.000 claims description 8

- 229910052735 hafnium Inorganic materials 0.000 claims description 8

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 8

- 238000009413 insulation Methods 0.000 claims description 3

- 229910044991 metal oxide Inorganic materials 0.000 abstract description 5

- 230000015556 catabolic process Effects 0.000 abstract 1

- 238000006731 degradation reaction Methods 0.000 abstract 1

- 238000000151 deposition Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 283

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 36

- 229910052802 copper Inorganic materials 0.000 description 36

- 239000010949 copper Substances 0.000 description 36

- 239000004020 conductor Substances 0.000 description 34

- 238000010586 diagram Methods 0.000 description 23

- 239000000463 material Substances 0.000 description 17

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 15

- MCMNRKCIXSYSNV-UHFFFAOYSA-N Zirconium dioxide Chemical compound O=[Zr]=O MCMNRKCIXSYSNV-UHFFFAOYSA-N 0.000 description 10

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- 229910052719 titanium Inorganic materials 0.000 description 8

- 238000001039 wet etching Methods 0.000 description 8

- 238000009713 electroplating Methods 0.000 description 7

- 230000006866 deterioration Effects 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- ZKATWMILCYLAPD-UHFFFAOYSA-N niobium pentoxide Inorganic materials O=[Nb](=O)O[Nb](=O)=O ZKATWMILCYLAPD-UHFFFAOYSA-N 0.000 description 5

- URLJKFSTXLNXLG-UHFFFAOYSA-N niobium(5+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Nb+5].[Nb+5] URLJKFSTXLNXLG-UHFFFAOYSA-N 0.000 description 5

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 5

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 5

- 229910001928 zirconium oxide Inorganic materials 0.000 description 5

- 239000004642 Polyimide Substances 0.000 description 4

- GNTDGMZSJNCJKK-UHFFFAOYSA-N divanadium pentaoxide Chemical compound O=[V](=O)O[V](=O)=O GNTDGMZSJNCJKK-UHFFFAOYSA-N 0.000 description 4

- 238000010030 laminating Methods 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 239000012790 adhesive layer Substances 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 239000012528 membrane Substances 0.000 description 3

- 239000000758 substrate Substances 0.000 description 3

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- WGLPBDUCMAPZCE-UHFFFAOYSA-N Trioxochromium Chemical compound O=[Cr](=O)=O WGLPBDUCMAPZCE-UHFFFAOYSA-N 0.000 description 2

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 2

- 229910000410 antimony oxide Inorganic materials 0.000 description 2

- 229910000423 chromium oxide Inorganic materials 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 2

- VTRUBDSFZJNXHI-UHFFFAOYSA-N oxoantimony Chemical compound [Sb]=O VTRUBDSFZJNXHI-UHFFFAOYSA-N 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 238000007747 plating Methods 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 238000000992 sputter etching Methods 0.000 description 2

- XOLBLPGZBRYERU-UHFFFAOYSA-N tin dioxide Chemical compound O=[Sn]=O XOLBLPGZBRYERU-UHFFFAOYSA-N 0.000 description 2

- 229910001887 tin oxide Inorganic materials 0.000 description 2

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- 230000001464 adherent effect Effects 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 239000000945 filler Substances 0.000 description 1

- 239000003365 glass fiber Substances 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 239000005011 phenolic resin Substances 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 230000001568 sexual effect Effects 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 150000003624 transition metals Chemical class 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/0011—Working of insulating substrates or insulating layers

- H05K3/0017—Etching of the substrate by chemical or physical means

- H05K3/002—Etching of the substrate by chemical or physical means by liquid chemical etching

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/10—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern

- H05K3/108—Apparatus or processes for manufacturing printed circuits in which conductive material is applied to the insulating support in such a manner as to form the desired conductive pattern by semi-additive methods; masks therefor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

- H05K1/115—Via connections; Lands around holes or via connections

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/02—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding

- H05K3/06—Apparatus or processes for manufacturing printed circuits in which the conductive material is applied to the surface of the insulating support and is thereafter removed from such areas of the surface which are not intended for current conducting or shielding the conductive material being removed chemically or electrolytically, e.g. by photo-etch process

- H05K3/061—Etching masks

- H05K3/064—Photoresists

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/42—Plated through-holes or plated via connections

- H05K3/423—Plated through-holes or plated via connections characterised by electroplating method

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

- H05K3/4673—Application methods or materials of intermediate insulating layers not specially adapted to any one of the previous methods of adding a circuit layer

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0154—Polyimide

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/01—Dielectrics

- H05K2201/0137—Materials

- H05K2201/0179—Thin film deposited insulating layer, e.g. inorganic layer for printed capacitor

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/38—Improvement of the adhesion between the insulating substrate and the metal

- H05K3/388—Improvement of the adhesion between the insulating substrate and the metal by the use of a metallic or inorganic thin film adhesion layer

Abstract

【課題】電極間の短絡及び信頼性の低下を防止すること。【解決手段】配線基板は、絶縁層と、前記絶縁層の表面に金属又は半金属の酸化物を成膜して形成された絶縁性の酸化物薄膜と、前記酸化物薄膜に積層された金属からなるシード層と、前記シード層上に形成された金属からなる電極とを有し、前記酸化物薄膜及び前記シード層は、前記電極と重ならない領域から除去されて前記絶縁層を露出させる。【選択図】図1

Description

本発明は、配線基板及び配線基板の製造方法に関する。

一般に、微細配線を有する配線基板は、例えばポリイミドなどの絶縁性の基材の表面に陰極となるシード層を形成し、シード層上に例えば電解めっきによって銅などの金属の電極を形成することにより製造される。シード層は、電極と同様に銅などの金属からなる層であり、基材の表面全体を被覆する。また、シード層と基材との密着性を高めるために、シード層と基材の間に、例えばチタンなどの金属を用いた密着層が形成されることがある。

シード層及び密着層は、いずれも例えばスパッタリングによって形成される。すなわち、基材の表面にチタンのスパッタリングが行われることにより密着層が形成され、密着層の表面に銅のスパッタリングが行われることによりシード層が形成される。密着層としては、例えばチタン及びハフニウムなどの遷移金属の酸化物が用いられることもあり、この場合には、絶縁性の密着層が形成されることになる。

ところで、シード層上に電極が形成された後、隣接する電極間においては、例えばエッチングによりシード層が除去される。すなわち、例えばシード層が銅を用いて形成されている場合、銅のエッチング液(エッチング液A)を用いるウェットエッチングによって電極間のシード層が除去される。

しかしながら、基材に密着層、シード層及び電極が順に積層される配線基板においては、電極間の短絡及び信頼性の低下が発生することがあるという問題がある。具体的には、シード層上に銅の電解めっきによって電極が形成された状態の中間構造体から、電極間のシード層と密着層をウェットエッチングによって除去する際、エッチング液(エッチング液A)に中間構造体を浸漬する時間が長いと、シード層と同様に銅を用いて形成される電極の側面がエッチングされるサイドエッチングが発生する。このため、過度に長時間エッチング液(エッチング液A)に中間構造体を浸漬することはない。しかし、サイドエッチングを軽減させるためにエッチング時間を短くし過ぎると、密着層上にシード層の残渣が残留することがある。結果として、たとえ密着層が絶縁性であっても、密着層の表面に残留するシード層の残渣によって、隣接する電極間の短絡及び信頼性の低下が発生してしまう。

また、密着層がチタンなどの金属を用いて形成されている場合には、シード層のエッチングの後、密着層のエッチングが行われるが、チタンのエッチング液(エッチング液B)はチタンよりも銅を早くエッチングするため、銅のエッチングレートが高くなる。このため、密着層のエッチング時に、電極の側面がエッチングされるサイドエッチングが発生する。サイドエッチングを抑制するために、中間構造体をチタンのエッチング液(エッチング液B)に浸漬する時間を過度に短時間にすると、導体であるチタンが電極間に残留し、電極間の短絡及び信頼性の低下が発生する。このような電極間の短絡及び信頼性の低下は、隣接する電極間の距離が小さい微細配線を有する配線基板では、特に発生する可能性が高い。

開示の技術は、かかる点に鑑みてなされたものであって、電極間の短絡及び信頼性の低下を防止することができる配線基板及び配線基板の製造方法を提供することを目的とする。

本願が開示する配線基板は、1つの態様において、絶縁層と、前記絶縁層の表面に金属又は半金属の酸化物を成膜して形成された絶縁性の酸化物薄膜と、前記酸化物薄膜に積層された金属からなるシード層と、前記シード層上に形成された金属からなる電極とを有し、前記酸化物薄膜及び前記シード層は、前記電極と重ならない領域から除去されて前記絶縁層を露出させる。

本願が開示する配線基板及び配線基板の製造方法の1つの態様によれば、電極間の短絡及び信頼性の低下を防止することができるという効果を奏する。

以下、本願が開示する配線基板及び配線基板の製造方法の実施の形態について、図面を参照して詳細に説明する。なお、この実施の形態により本発明が限定されるものではない。

(実施の形態1)

図1は、実施の形態1に係る配線基板100の構成を示す断面図である。図1においては、配線を含む電極が形成される配線基板100の表面付近の断面を示す。図1に示す配線基板100は、絶縁層110、酸化物薄膜120、シード層130及び電極141、142を有する。

図1は、実施の形態1に係る配線基板100の構成を示す断面図である。図1においては、配線を含む電極が形成される配線基板100の表面付近の断面を示す。図1に示す配線基板100は、絶縁層110、酸化物薄膜120、シード層130及び電極141、142を有する。

絶縁層110は、例えばポリイミドなどの絶縁性樹脂を用いて形成される配線基板100の基材である。絶縁層110は、無機材料フィラーやガラス繊維にエポキシ樹脂を含浸させたものや、紙にフェノール樹脂を含浸させたものや、テフロン(登録商標)などであっても良い。絶縁層110の厚さは、例えば50μm程度である。

酸化物薄膜120は、絶縁層110の表面に形成される絶縁性の薄膜であり、絶縁層110に対するシード層130の密着性を向上させる層である。酸化物薄膜120は、金属又は半金属の酸化物を用いたプラズマCVD(Chemical Vapor Deposition)又はALD(Atomic Layer Deposition)などの成膜技術によって形成され、厚さが例えば1~500nm、より望ましくは1~100nmの薄膜とすることができる。酸化物薄膜120が例えばALDによって成膜される薄膜であるため、酸化物薄膜120が絶縁層110に密着する密着強度が高く、また、例えばスルーホールなどの立体的な構造及び側壁に対しても被着性が高い。結果として、例えばHAST(Highly Accelerated Stress Test)のように配線基板100が高温高湿の条件下にさらされる信頼性試験が行われても、シード層130の絶縁層110に対する密着性低下を抑制することができる。

酸化物薄膜120の材料としては、例えば酸化ハフニウム(ハフニア)、酸化チタン(チタニア)、酸化ジルコニウム(ジルコニア)又は五酸化ニオブなどを用いるのが好ましい。また、五酸化バナジウム、酸化クロム、酸化アルミニウム(アルミナ)、酸化ケイ素、酸化インジウム、酸化スズ又は酸化アンチモンなどを酸化物薄膜120の材料とすることもできる。

酸化物薄膜120は、電極141、142が形成される位置において絶縁層110の表面に形成されており、電極141、142の間においては、酸化物薄膜120が除去されている。具体的には、酸化物薄膜120は、シード層130がエッチングされた後に、例えばアルゴン逆スパッタリング、イオンミリング又はレーザ加工などによってドライエッチングされ、電極141、142と重ならない領域から除去される。結果として、電極141、142の間の領域では、絶縁層110が露出する。

これにより、電極141、142の間の領域では、酸化物薄膜120とともに、酸化物薄膜120の表面に残留するシード層130の残渣が除去され、電極141、142間の短絡及び信頼性の低下を防止することができる。また、酸化物薄膜120は、絶縁性の酸化物を材料とする薄膜であるため、たとえ絶縁層110の表面に酸化物薄膜120の残渣が残留しても、電極141、142間の短絡及び信頼性の低下が発生することはない。

さらに、上述したように、酸化物薄膜120の除去は、例えばアルゴン逆スパッタリングなどのドライエッチングによって行われるため、シード層130及び電極141、142のサイドエッチングを抑制することができるとともに、電極141、142と重ならない領域で露出する絶縁層110の表面の損傷も低減することができる。

シード層130は、酸化物薄膜120の表面に形成される導電性の層であり、電極141、142に対する陰極となる層である。シード層130は、例えば銅などの金属のスパッタリングによって形成され、厚さを例えば30~3000nmとすることができる。

電極141、142は、配線基板100の表面に形成される配線及び電極であり、例えば銅の電解めっきによってシード層130の表面に形成される。電極141、142のシード層130表面からの高さは、例えば1~500μmとすることができる。電極141、142は互いに隣接するが、電極141、142の間の領域の酸化物薄膜120及びシード層130が除去されているため、電極141、142は絶縁されている。

次いで、上記のように構成される配線基板100の製造方法について、具体的に例を挙げながら図2のフロー図を参照して説明する。

まず、例えばポリイミドからなる絶縁層110の表面に、ALDなどの成膜技術によって酸化物薄膜120が形成される(ステップS101)。具体的には、例えば図3に示すように、厚さ50μm程度の絶縁層110の表面に、厚さ1~500nmの酸化物薄膜120が形成される。酸化物薄膜120は、例えば酸化ハフニウム(ハフニア)、酸化チタン(チタニア)、酸化ジルコニウム(ジルコニア)又は五酸化ニオブなどの金属又は半金属の酸化物を材料とし、薄膜を形成可能なALDなどの成膜技術によって形成される。ALDによって酸化物薄膜120を形成することにより、例えばHASTなどの信頼性試験後にも酸化物薄膜120の密着強度の低下を抑制することができる。

そして、酸化物薄膜120の表面に、スパッタリングによってシード層130が形成される(ステップS102)。すなわち、例えば図4に示すように、酸化物薄膜120の表面に、例えば銅のスパッタリングによって厚さ30~3000nmのシード層130が形成される。

シード層130が形成されると、配線を含む電極が形成される領域を除く領域にレジストが形成される(ステップS103)。すなわち、例えば図5に示すように、電極141、142が形成される領域に開口部を有するレジスト150が形成される。そして、レジスト150をマスクとして、例えば銅の電解めっきが行われる(ステップS104)。すなわち、例えば図6に示すように、レジスト150の開口部に銅が析出し、電極141、142が形成される。

電極141、142が形成されると、レジスト150が剥離され(ステップS105)、例えば図7に示すように、絶縁層110の表面に積層された酸化物薄膜120及びシード層130上に電極141、142を有する中間構造体が得られる。この中間構造体では、隣接する電極141、142が導体のシード層130を介して短絡しているため、銅のエッチングにより、電極141、142の間の領域のシード層130が除去される(ステップS106)。すなわち、例えば図8に示すように、電極141、142をエッチングマスクとして、銅のエッチング液(エッチング液A)に中間構造体を浸漬することにより、電極141、142と重ならない領域121のシード層130が除去される。銅のエッチング液(エッチング液A)としては、例えば、主成分として硫酸と過酸化水素を混合したものを用いることができる。

このとき、中間構造体を銅のエッチング液(エッチング液A)に浸漬するウェットエッチングが行われるため、銅を材料として形成されている電極141、142の側面がエッチングされるサイドエッチングが発生する。このため、エッチング液(エッチング液A)に中間構造体を浸漬する時間を過度に長くすることなく、サイドエッチングを抑制するのが好ましい。結果として、領域121にシード層130の残渣が残留することがあるが、これらの残渣は、以下の酸化物薄膜120のエッチング時に同時に除去される。

すなわち、シード層130のウェットエッチングの後、例えばアルゴン逆スパッタリングなどのドライエッチングによって、領域121の酸化物薄膜120が除去される(ステップS107)。酸化物薄膜120が除去されることにより、酸化物薄膜120の表面に残留するシード層130の残渣も同時に除去され、電極141、142の間の領域では、絶縁層110が露出する。結果として、シード層130の残渣による電極141、142間の短絡及び信頼性の低下を防止することができる。また、アルゴン逆スパッタリングなどのドライエッチングが行われるため、シード層130及び電極141、142のサイドエッチングが抑制され、シード層130及び電極141、142の側面の損傷を低減することができる。さらに、アルゴン逆スパッタリングなどのドライエッチングでは、絶縁層110がエッチング液に浸漬されるウェットエッチングとは異なり、電極141、142と重ならない領域で露出する絶縁層110の表面の損傷を低減することができる。

以上のように、本実施の形態によれば、絶縁層の表面に密着層として絶縁性の酸化物薄膜を形成し、酸化物薄膜の表面にシード層を形成し、シード層上に電極を形成する。そして、電極と重ならない領域のシード層を除去した後、ドライエッチングによって酸化物薄膜を除去する。このため、電極が形成されていない領域にシード層の残渣が残留しても、これらの残渣が酸化物薄膜とともに除去され、隣接する電極間の短絡及び信頼性の低下を防止することができる。また、酸化物薄膜がアルゴン逆スパッタリングなどのドライエッチングによって除去されるため、シード層及び電極のサイドエッチングを抑制することができるとともに、単に逆スパッタにより残渣除去するよりも絶縁層の表面の損傷を低減することができる。

(実施の形態2)

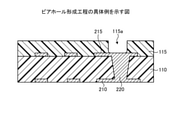

図9は、実施の形態2に係る配線基板100の構成を示す断面図である。図9において、図1と同じ部分には同じ符号を付す。図9においては、配線を含む電極が形成される配線基板100の表面付近の断面を示す。図9に示す配線基板100は、絶縁層110、115、酸化物薄膜120、シード層130、電極141、142、導体層210、215、ビア220、第2シード層230及びビア240を有する。

図9は、実施の形態2に係る配線基板100の構成を示す断面図である。図9において、図1と同じ部分には同じ符号を付す。図9においては、配線を含む電極が形成される配線基板100の表面付近の断面を示す。図9に示す配線基板100は、絶縁層110、115、酸化物薄膜120、シード層130、電極141、142、導体層210、215、ビア220、第2シード層230及びビア240を有する。

実施の形態2に係る配線基板100は、複数の絶縁層110、115及び複数の導体層210、215を積層して得られる積層基板である。なお、図9に示す導体層210の下層に他の絶縁層及び導体層がさらに積層されていても良い。

絶縁層110、115は、例えばポリイミドなどの絶縁性樹脂を材料とする絶縁層である。絶縁層110は、下層の絶縁層の表面に形成される導体層210を被覆し、絶縁層110の表面には導体層215が形成される。そして、導体層215は、絶縁層115によって被覆される。このように、配線基板100は、絶縁層110、115と導体層210、215とを積層して得られるビルドアップ層を有する。

導体層210、215は、例えば銅などの金属をパターニングすることにより、各絶縁層の上面に形成される。互いに異なる絶縁層の上面に形成される導体層210及び導体層215は、絶縁層110を貫通するビア220によって電気的に接続される。また、絶縁層110の上面に形成される導体層215と絶縁層115の上面に形成される電極141とは、絶縁層115を貫通するビア240によって電気的に接続される。

酸化物薄膜120は、絶縁層115の表面に形成される絶縁性の薄膜であり、絶縁層115に対するシード層130の密着性を向上させる層である。酸化物薄膜120は、金属又は半金属の酸化物を用いたプラズマCVD又はALDなどの成膜技術によって形成され、厚さが例えば1~500nmの薄膜とすることができる。酸化物薄膜120が例えばALDによって成膜される薄膜であるため、酸化物薄膜120が絶縁層115に密着する密着強度が高く、例えばHASTのように配線基板100が高温高湿の条件下にさらされる信頼性試験が行われても、シード層130の絶縁層115に対する密着性低下を抑制することができる。

酸化物薄膜120の材料としては、例えば酸化ハフニウム(ハフニア)、酸化チタン(チタニア)、酸化ジルコニウム(ジルコニア)又は五酸化ニオブなどを用いるのが好ましい。また、五酸化バナジウム、酸化クロム、酸化アルミニウム(アルミナ)、酸化ケイ素、酸化インジウム、酸化スズ又は酸化アンチモンなどを酸化物薄膜120の材料とすることもできる。

酸化物薄膜120は、電極141、142が形成される位置において絶縁層110の表面に形成されており、電極141、142の間においては、酸化物薄膜120が除去されている。また、本実施の形態においては、酸化物薄膜120は、ビア240の位置においても除去されている。具体的には、酸化物薄膜120は、シード層130がエッチングされた後に、例えばアルゴン逆スパッタリング、イオンミリング又はレーザ加工などによってドライエッチングされ、電極141、142の間の領域及びビア240が形成される領域から除去される。

シード層130は、酸化物薄膜120の表面に形成される導電性の層であり、電極141、142に対する陰極となる層である。シード層130は、例えば銅などの金属のスパッタリングによって形成され、厚さを例えば30~3000nmとすることができる。

電極141、142は、配線基板100の表面に形成される配線及び電極であり、例えば銅の電解めっきによって第2シード層230の表面に形成される。電極141、142の第2シード層230表面からの高さは、例えば1~500μmとすることができる。電極141、142は互いに隣接するが、電極141、142の間の領域の酸化物薄膜120、シード層130及び第2シード層230が除去されているため、電極141、142は絶縁されている。電極141は、ビア240によって導体層215と電気的に接続される。

第2シード層230は、シード層130の表面及びビア240の外周に形成される導電性の層であり、シード層130とともに電極141、142に対する陰極となる層である。第2シード層230は、シード層130と同様に、例えば銅などの金属のスパッタリングによって形成される。

ビア240は、絶縁層115を貫通するビアホール内に第2シード層230及び電極141が形成されることにより、電極141と導体層215を電気的に接続する。すなわち、ビアホールの内面に形成される第2シード層230が導体層215に接触し、第2シード層230の内側の凹部に電極141が延伸している。

次いで、上記のように構成される配線基板100の製造方法について、具体的に例を挙げながら図10のフロー図を参照して説明する。なお、図10において、図2と同じ部分には同じ符号を付す。

まず、絶縁層及び導体層の積層によりビルドアップ層が形成される(ステップS201)。具体的には、例えば図11に示すように、絶縁層の上面に導体層210が形成されると、導体層210を被覆するように絶縁層110が積層される。そして、絶縁層110を貫通するビア220が形成されるとともに、絶縁層110の上面に導体層215が形成される。さらに、導体層215を被覆するように絶縁層115が積層される。

そして、絶縁層115の表面に、ALDなどの成膜技術によって酸化物薄膜120が形成される(ステップS101)。具体的には、例えば図12に示すように、ビルドアップ層の最上層である絶縁層115の表面に、厚さ1~500nmの酸化物薄膜120が形成される。酸化物薄膜120は、例えば酸化ハフニウム(ハフニア)、酸化チタン(チタニア)、酸化ジルコニウム(ジルコニア)又は五酸化ニオブなどの金属又は半金属の酸化物を材料とし、薄膜を形成可能なALDなどの成膜技術によって形成される。ALDによって酸化物薄膜120を形成することにより、例えばHASTなどの信頼性試験後にも酸化物薄膜120の密着強度の低下を抑制することができる。

そして、酸化物薄膜120の表面に、スパッタリングによってシード層130が形成される(ステップS102)。さらに、シード層130の上面には、ビア240が形成される領域を除く領域にレジストが形成される(ステップS202)。すなわち、例えば図13に示すように、酸化物薄膜120の表面に、例えば銅のスパッタリングによって厚さ30~3000nmのシード層130が形成される。その後、ビア240が形成される領域に開口部を有するレジスト250が形成される。

そして、レジスト250をエッチングマスクとして、シード層130のエッチングが行われる(ステップS203)。具体的には、例えば図14に示すように、レジスト250の開口部のシード層130が除去され、ビア240が形成される領域122において、酸化物薄膜120が露出する。

領域122のシード層130が除去されると、レジスト250が剥離され(ステップS204)、例えば図15に示すように、領域122では酸化物薄膜120が露出し、領域122以外の領域では酸化物薄膜120がシード層130によって被覆された状態となる。そこで、シード層130をエッチングマスクとして、酸化物薄膜120のエッチングが行われる(ステップS205)。具体的には、例えば図16に示すように、例えばアルゴン逆スパッタリングなどのドライエッチングによって、領域122の酸化物薄膜120が除去される。ここでは、アルゴン逆スパッタリングなどのドライエッチングが行われるため、酸化物薄膜120のみが除去され、シード層130及び絶縁層115の損傷を低減することができる。

そして、酸化物薄膜120が除去されることにより露出する絶縁層115に対して、例えば異方性エッチング又はレーザ加工などが施され、絶縁層115を貫通するビアホールが形成される(ステップS206)。すなわち、例えば図17に示すように、酸化物薄膜120及びシード層130が除去された領域において、絶縁層115にビアホール115aが形成される。ビアホール115aは、絶縁層115を貫通して導体層215まで到達し、底面に導体層215を露出させる。

ビアホール115aが形成されると、シード層130の上面及びビアホール115aの内面に、スパッタリングによって第2シード層230が形成される(ステップS207)。さらに、第2シード層230の上面には、配線を含む電極が形成される領域を除く領域にレジストが形成される(ステップS103)。すなわち、例えば図18に示すように、シード層130の表面及びビアホール115aの内面に、例えば銅のスパッタリングによって厚さ30~3000nmの第2シード層230が形成される。その後、電極141、142が形成される領域に開口部を有するレジスト260が形成される。

そして、レジスト260をマスクとして、例えば銅の電解めっきが行われる(ステップS104)。すなわち、例えば図19に示すように、レジスト260の開口部に銅が析出し、電極141、142が形成される。このとき、ビアホール115aの内面に形成された第2シード層230の内側の凹部まで電極141が延伸し、電極141と導体層215を電気的に接続するビア240が形成される。

電極141、142が形成されると、レジスト260が剥離され(ステップS105)、例えば図20に示すように、絶縁層115の表面に積層された酸化物薄膜120、シード層130及び第2シード層230上に電極141、142を有し、電極141と導体層215を接続するビア240を有する中間構造体が得られる。この中間構造体では、隣接する電極141、142が導体のシード層130及び第2シード層230を介して短絡しているため、銅のエッチングにより、電極141、142の間の領域のシード層130及び第2シード層230が除去される(ステップS208)。すなわち、例えば図21に示すように、電極141、142をエッチングマスクとして、銅のエッチング液に中間構造体を浸漬することにより、電極141、142と重ならない領域121のシード層130及び第2シード層230が除去される。

このとき、中間構造体を銅のエッチング液に浸漬するウェットエッチングが行われるため、銅を材料として形成されている電極141、142の側面がエッチングされるサイドエッチングが発生する。このため、エッチング液に中間構造体を浸漬する時間を過度に長くすることなく、サイドエッチングを抑制するのが好ましい。結果として、領域121にシード層130又は第2シード層230の残渣が残留することがあるが、これらの残渣は、以下の酸化物薄膜120のエッチング時にも除去される。

すなわち、シード層130及び第2シード層230のウェットエッチングの後、例えばアルゴン逆スパッタリングなどのドライエッチングによって、領域121の酸化物薄膜120が除去される(ステップS107)。酸化物薄膜120が除去されることにより、酸化物薄膜120の表面に残留するシード層130又は第2シード層230の残渣も同時に除去され、電極141、142間の短絡及び信頼性の低下を防止することができる。また、アルゴン逆スパッタリングなどのドライエッチングが行われるため、シード層130、第2シード層230及び電極141、142のサイドエッチングが抑制され、シード層130、第2シード層230及び電極141、142の側面の損傷を低減することができる。さらに、アルゴン逆スパッタリングなどのドライエッチングでは、絶縁層115がエッチング液に浸漬するウェットエッチングとは異なり、絶縁層115の表面の損傷を低減することができる。

以上のように、本実施の形態によれば、絶縁層の表面に酸化物薄膜及びシード層を形成した後、電極が形成される位置の酸化物薄膜及びシード層を除去してビアを形成し、ビアを介して内層配線と接続される電極を形成する。そして、電極と重ならない領域のシード層を除去した後、ドライエッチングによって酸化物薄膜を除去する。このため、密着層として酸化物薄膜を有する積層基板を製造することができるとともに、電極が形成されていない領域にシード層の残渣が残留しても、これらの残渣が酸化物薄膜とともに除去され、隣接する電極間の短絡及び信頼性の低下を防止することができる。また、酸化物薄膜がアルゴン逆スパッタリングなどのドライエッチングによって除去されるため、シード層及び電極のサイドエッチングを抑制することができるとともに、単独でシード層残渣をドライエッチングする場合と比べて絶縁層の表面の損傷を低減することができる。

(実施の形態3)

上記実施の形態2においては、絶縁層115の表面に酸化物薄膜120及びシード層130が形成された後、ビア240が形成される領域の酸化物薄膜120及びシード層130を除去し、ビアホール115aが形成されるものとした。しかしながら、ビアホール115aは、酸化物薄膜120及びシード層130が形成される前の初期段階で形成することも可能である。そこで、実施の形態3においては、初期段階でビアホール115aが形成される場合の配線基板100の製造方法について説明する。

上記実施の形態2においては、絶縁層115の表面に酸化物薄膜120及びシード層130が形成された後、ビア240が形成される領域の酸化物薄膜120及びシード層130を除去し、ビアホール115aが形成されるものとした。しかしながら、ビアホール115aは、酸化物薄膜120及びシード層130が形成される前の初期段階で形成することも可能である。そこで、実施の形態3においては、初期段階でビアホール115aが形成される場合の配線基板100の製造方法について説明する。

実施の形態3に係る配線基板100の構成は、実施の形態2(図9)と同様であるため、その説明を省略する。実施の形態3においては、配線基板100の製造方法が実施の形態2とは異なる。そこで、実施の形態3に係る配線基板100の製造方法について、具体的に例をあげながら図22に示すフロー図を参照して説明する。なお、図22において、図2及び図10と同じ部分には同じ符号を付し、その詳しい説明を省略する。

まず、絶縁層及び導体層の積層によりビルドアップ層が形成される(ステップS201)。すなわち、積層された絶縁層110、115及び導体層210、215を有し、導体層210、215を電気的に接続するビア220を有するビルドアップ層が形成される。

そして、ビルドアップ層の最上層の絶縁層115に対して、例えば異方性エッチング又はレーザ加工などが施され、絶縁層115を貫通するビアホールが形成される(ステップS301)。すなわち、例えば図23に示すように、ビア240が形成される領域において、絶縁層115にビアホール115aが形成される。ビアホール115aは、絶縁層115を貫通して導体層215まで到達し、底面に導体層215を露出させる。

そして、絶縁層115の表面及びビアホール115aの内面に、ALDなどの成膜技術によって酸化物薄膜120が形成される(ステップS101)。具体的には、例えば図24に示すように、絶縁層115の表面及びビアホール115aの内面に、厚さ1~500nmの酸化物薄膜120が形成される。酸化物薄膜120は、例えば酸化ハフニウム(ハフニア)、酸化チタン(チタニア)、酸化ジルコニウム(ジルコニア)又は五酸化ニオブなどの金属又は半金属の酸化物を材料とし、薄膜を形成可能なALDなどの成膜技術によって形成される。ALDによって酸化物薄膜120を形成することにより、例えばHASTなどの信頼性試験後にも酸化物薄膜120の密着強度の低下を抑制することができる。

そして、酸化物薄膜120の表面に、スパッタリングによってシード層130が形成される(ステップS102)。すなわち、例えば図25に示すように、酸化物薄膜120の表面に、例えば銅のスパッタリングによって厚さ30~3000nmのシード層130が形成される。ビアホール115aにおいては、ビアホール115aの内面及び導体層215の上面に沿って酸化物薄膜120及びシード層130が形成されるため、凹部が形成される。

シード層130が形成されると、シード層130の上面のビアホール115aの領域を除く領域にレジストが形成される(ステップS202)。すなわち、例えば図26に示すように、ビアホール115aの領域に開口部を有するレジスト250が形成される。そして、レジスト250をエッチングマスクとして、シード層130のエッチングが行われる(ステップS203)。具体的には、例えば図27に示すように、レジスト250の開口部のシード層130が除去され、ビアホール115a内の凹部を含む領域において、酸化物薄膜120が露出する。

ビアホール115aの領域のシード層130が除去されると、レジスト250が剥離され(ステップS204)、例えば図28に示すように、ビアホール115aの領域では酸化物薄膜120が露出し、ビアホール115aの領域以外の領域では酸化物薄膜120がシード層130によって被覆された状態となる。そこで、シード層130をエッチングマスクとして、酸化物薄膜120のエッチングが行われる(ステップS205)。これにより、実施の形態2においてビアホール115aが形成された状態(図17)と同一の状態になるため、以下、実施の形態2と同様に、電極141、142及びビア240が形成される。

すなわち、シード層130の上面及びビアホール115aの内面に、スパッタリングによって第2シード層230が形成され(ステップS207)、第2シード層230の上面の電極141、142が形成される領域を除く領域にレジストが形成される(ステップS103)。そして、レジストをマスクとして、例えば銅の電解めっきが行われることにより(ステップS104)、電極141、142及びビア240が形成され、レジストが剥離される(ステップS105)。その後、銅のエッチングにより、電極141、142と重ならない領域のシード層130及び第2シード層230が除去され(ステップS208)、例えばアルゴン逆スパッタリングなどのドライエッチングによって、電極141、142と重ならない領域の酸化物薄膜120が除去される(ステップS107)。

以上のように、本実施の形態によれば、絶縁層にビアホールを形成した後、絶縁層の表面及びビアホールの内面に酸化物薄膜及びシード層を形成し、ヒアホールの領域の酸化物薄膜及びシード層を除去して電極及びビアを形成する。そして、電極と重ならない領域のシード層を除去した後、ドライエッチングによって酸化物薄膜を除去する。このため、密着層として酸化物薄膜を有する積層基板を製造することができるとともに、電極が形成されていない領域にシード層の残渣が残留しても、これらの残渣が酸化物薄膜とともに除去され、隣接する電極間の短絡及び信頼性の低下を防止することができる。また、酸化物薄膜がアルゴン逆スパッタリングなどのドライエッチングによって除去されるため、シード層及び電極のサイドエッチングを抑制することができるとともに、絶縁層の表面の損傷を低減することができる。

110、115 絶縁層

115a ビアホール

120 酸化物薄膜

130、230 シード層

141、142 電極

150、250、260 レジスト

210、215 導体層

220、240 ビア

115a ビアホール

120 酸化物薄膜

130、230 シード層

141、142 電極

150、250、260 レジスト

210、215 導体層

220、240 ビア

Claims (11)

- 絶縁層と、

前記絶縁層の表面に金属又は半金属の酸化物を成膜して形成された絶縁性の酸化物薄膜と、

前記酸化物薄膜に積層された金属からなるシード層と、

前記シード層上に形成された金属からなる電極とを有し、

前記酸化物薄膜及び前記シード層は、

前記電極と重ならない領域から除去されて前記絶縁層を露出させる

ことを特徴とする配線基板。 - 前記酸化物薄膜は、

ハフニウムの酸化物である酸化ハフニウムを成膜して形成されることを特徴とする請求項1記載の配線基板。 - 前記酸化物薄膜は、

ALD(Atomic Layer Deposition)を用いて成膜された厚さが1~100nmの酸化ハフニウムの薄膜であることを特徴とする請求項2記載の配線基板。 - 前記電極と重なる領域において前記絶縁層を貫通するビアをさらに有し、

前記シード層は、

前記ビアが形成される領域を除く領域において前記酸化物薄膜に積層される第1シード層と、

前記第1シード層に積層されるとともに、前記ビアの外周に形成される第2シード層とを有することを特徴とする請求項1記載の配線基板。 - 絶縁層の表面に金属又は半金属の酸化物を成膜して絶縁性の酸化物薄膜を形成し、

前記酸化物薄膜に金属からなるシード層を積層し、

前記シード層上に金属からなる電極を形成し、

前記電極と重ならない領域から前記シード層を除去し、

前記シード層が除去された領域において前記酸化物薄膜を除去し、前記絶縁層を露出させる

工程を有することを特徴とする配線基板の製造方法。 - 前記酸化物薄膜を形成する工程は、

ハフニウムの酸化物である酸化ハフニウムを成膜することを特徴とする請求項5記載の配線基板の製造方法。 - 前記酸化物薄膜を形成する工程は、

ALD(Atomic Layer Deposition)を用いて厚さが1~100nmの酸化ハフニウムの薄膜を形成することを特徴とする請求項6記載の配線基板の製造方法。 - 前記酸化物薄膜を除去する工程は、

前記シード層をエッチングマスクとしたドライエッチングによって前記酸化物薄膜を除去することを特徴とする請求項5記載の配線基板の製造方法。 - 前記酸化物薄膜を除去する工程は、

アルゴン逆スパッタリングによって前記酸化物薄膜を除去することを特徴とする請求項8記載の配線基板の製造方法。 - 一部の領域において前記シード層及び前記酸化物薄膜を除去し、

前記シード層及び前記酸化物薄膜が除去された領域に、前記絶縁層を貫通するビアホールを形成し、

前記シード層の表面及び前記ビアホールの内面に第2シード層を形成する工程をさらに有し、

前記電極を形成する工程は、

前記第2シード層上に前記電極を形成し、

前記シード層を除去する工程は、

前記シード層及び前記第2シード層を除去する

ことを特徴とする請求項5記載の配線基板の製造方法。 - 前記絶縁層を貫通するビアホールを形成する工程をさらに有し、

前記酸化物薄膜を形成する工程は、

前記絶縁層の表面及び前記ビアホールの内面に前記酸化物薄膜を形成し、

前記電極を形成する工程は、

前記ビアホールの領域において前記シード層及び前記酸化物薄膜を除去し、

前記シード層の表面及び前記ビアホールの内面に第2シード層を形成し、

前記第2シード層上に前記電極を形成する工程を含む

ことを特徴とする請求項5記載の配線基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020132588A JP2022029308A (ja) | 2020-08-04 | 2020-08-04 | 配線基板及び配線基板の製造方法 |

| US17/381,746 US11659667B2 (en) | 2020-08-04 | 2021-07-21 | Wiring board and method of manufacturing wiring board |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2020132588A JP2022029308A (ja) | 2020-08-04 | 2020-08-04 | 配線基板及び配線基板の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2022029308A true JP2022029308A (ja) | 2022-02-17 |

| JP2022029308A5 JP2022029308A5 (ja) | 2023-03-17 |

Family

ID=80114449

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020132588A Pending JP2022029308A (ja) | 2020-08-04 | 2020-08-04 | 配線基板及び配線基板の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US11659667B2 (ja) |

| JP (1) | JP2022029308A (ja) |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5921198B2 (ja) | 1978-06-23 | 1984-05-18 | 株式会社東芝 | 導体パタ−ンの形成方法 |

| US6740221B2 (en) * | 2001-03-15 | 2004-05-25 | Applied Materials Inc. | Method of forming copper interconnects |

| JP2002373957A (ja) * | 2001-06-14 | 2002-12-26 | Shinko Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP4494873B2 (ja) | 2004-06-02 | 2010-06-30 | 株式会社アルバック | プリント配線板、プリント配線板の製造方法およびその製造装置 |

| JP4224434B2 (ja) * | 2004-06-30 | 2009-02-12 | パナソニック株式会社 | 半導体装置及びその製造方法 |

| US7956465B2 (en) * | 2006-05-08 | 2011-06-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Reducing resistivity in interconnect structures of integrated circuits |

| US9142501B2 (en) * | 2013-03-14 | 2015-09-22 | International Business Machines Corporation | Under ball metallurgy (UBM) for improved electromigration |

| KR20200056833A (ko) * | 2018-11-15 | 2020-05-25 | 삼성전기주식회사 | 인쇄회로기판 |

-

2020

- 2020-08-04 JP JP2020132588A patent/JP2022029308A/ja active Pending

-

2021

- 2021-07-21 US US17/381,746 patent/US11659667B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US11659667B2 (en) | 2023-05-23 |

| US20220046800A1 (en) | 2022-02-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5344197B2 (ja) | 誘電体薄膜素子及びその製造方法 | |

| KR20030040083A (ko) | 박막 커패시터를 일체로 형성한 다층 배선 기판의 제조 방법 | |

| JP4649198B2 (ja) | 配線基板の製造方法 | |

| JP2008251751A (ja) | 電子部品およびその製造方法 | |

| JP3775129B2 (ja) | 半導体チップの接続方法 | |

| JP5299158B2 (ja) | 誘電体薄膜素子 | |

| JP4584700B2 (ja) | 配線基板の製造方法 | |

| JP5781877B2 (ja) | 配線基板の製造方法 | |

| JP2023179675A (ja) | 配線構造体 | |

| JP2022029308A (ja) | 配線基板及び配線基板の製造方法 | |

| TWI477217B (zh) | 具有包覆銅層之印刷電路板的製造方法 | |

| US11917751B2 (en) | Multilayer wiring board and method of producing the same | |

| JP2010534949A (ja) | 電子モジュールの製造方法、および電子モジュール | |

| JP2018120932A (ja) | 貫通電極基板及び貫通電極基板を備える実装基板並びに貫通電極基板の製造方法 | |

| JP2019117875A (ja) | 配線基板、および配線基板を有する半導体装置 | |

| JP6676370B2 (ja) | 配線基板及び配線基板の製造方法 | |

| JP2011066331A (ja) | 実装基板及びその製造方法並びに電子機器 | |

| JP7125679B2 (ja) | キャパシタ及びその製造方法 | |

| WO2024090336A1 (ja) | 配線基板およびそれを用いた実装構造体 | |

| WO2023157426A1 (ja) | 薄膜キャパシタ及びその製造方法、並びに、薄膜キャパシタを備える電子回路基板 | |

| WO2023162406A1 (ja) | 薄膜キャパシタ及びこれを備える電子回路基板 | |

| JP4775753B2 (ja) | 誘電体薄膜キャパシタの製造方法 | |

| JP6232845B2 (ja) | 配線接続構造およびこの配線接続構造を有する誘電体薄膜キャパシタ | |

| JP2023159219A (ja) | 配線基板とその作製方法 | |

| JP2018107337A (ja) | 電子部品およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230308 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230308 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20231227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240123 |