JP2017529696A - 導電性の多層基板スタックを製造するための方法 - Google Patents

導電性の多層基板スタックを製造するための方法 Download PDFInfo

- Publication number

- JP2017529696A JP2017529696A JP2017509716A JP2017509716A JP2017529696A JP 2017529696 A JP2017529696 A JP 2017529696A JP 2017509716 A JP2017509716 A JP 2017509716A JP 2017509716 A JP2017509716 A JP 2017509716A JP 2017529696 A JP2017529696 A JP 2017529696A

- Authority

- JP

- Japan

- Prior art keywords

- substrate

- semiconductor substrate

- contact

- substrates

- conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000000758 substrate Substances 0.000 title claims abstract description 218

- 238000000034 method Methods 0.000 title claims abstract description 58

- 238000004519 manufacturing process Methods 0.000 title claims description 11

- 239000004065 semiconductor Substances 0.000 claims abstract description 51

- 239000002105 nanoparticle Substances 0.000 claims description 33

- 230000003287 optical effect Effects 0.000 claims description 7

- 230000004927 fusion Effects 0.000 claims description 6

- 239000000919 ceramic Substances 0.000 claims description 5

- 239000011159 matrix material Substances 0.000 claims description 5

- 239000002245 particle Substances 0.000 claims description 4

- 230000035945 sensitivity Effects 0.000 claims description 3

- 238000003980 solgel method Methods 0.000 claims description 3

- 239000002131 composite material Substances 0.000 claims description 2

- 229910052710 silicon Inorganic materials 0.000 claims description 2

- 239000010703 silicon Substances 0.000 claims description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims 1

- 230000001590 oxidative effect Effects 0.000 claims 1

- 230000008569 process Effects 0.000 description 24

- 239000011370 conductive nanoparticle Substances 0.000 description 8

- 238000010438 heat treatment Methods 0.000 description 7

- 230000003647 oxidation Effects 0.000 description 7

- 238000007254 oxidation reaction Methods 0.000 description 7

- 238000005304 joining Methods 0.000 description 6

- 239000000463 material Substances 0.000 description 6

- 230000015572 biosynthetic process Effects 0.000 description 5

- 241000724291 Tobacco streak virus Species 0.000 description 4

- 239000000126 substance Substances 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000007517 polishing process Methods 0.000 description 3

- 238000001228 spectrum Methods 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000010521 absorption reaction Methods 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 238000000149 argon plasma sintering Methods 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 230000005670 electromagnetic radiation Effects 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000000605 extraction Methods 0.000 description 2

- 230000001788 irregular Effects 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 230000005855 radiation Effects 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 238000005507 spraying Methods 0.000 description 2

- 229910001020 Au alloy Inorganic materials 0.000 description 1

- 229910001369 Brass Inorganic materials 0.000 description 1

- 229910000906 Bronze Inorganic materials 0.000 description 1

- 229910000881 Cu alloy Inorganic materials 0.000 description 1

- 229910016347 CuSn Inorganic materials 0.000 description 1

- 238000004220 aggregation Methods 0.000 description 1

- 230000002776 aggregation Effects 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 239000010951 brass Substances 0.000 description 1

- 238000001246 colloidal dispersion Methods 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 239000010949 copper Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000018109 developmental process Effects 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 238000001879 gelation Methods 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 239000003353 gold alloy Substances 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 229910052745 lead Inorganic materials 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- 238000013507 mapping Methods 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000011148 porous material Substances 0.000 description 1

- 239000002243 precursor Substances 0.000 description 1

- 230000002028 premature Effects 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000010944 silver (metal) Substances 0.000 description 1

- 238000005245 sintering Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/042—PV modules or arrays of single PV cells

- H01L31/043—Mechanically stacked PV cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/185—Joining of semiconductor bodies for junction formation

- H01L21/187—Joining of semiconductor bodies for junction formation by direct bonding

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/041—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L31/00

- H01L25/043—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/02—Details

- H01L31/0224—Electrodes

- H01L31/022408—Electrodes for devices characterised by at least one potential jump barrier or surface barrier

- H01L31/022425—Electrodes for devices characterised by at least one potential jump barrier or surface barrier for solar cells

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L31/00—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof

- H01L31/04—Semiconductor devices sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation; Processes or apparatus specially adapted for the manufacture or treatment thereof or of parts thereof; Details thereof adapted as photovoltaic [PV] conversion devices

- H01L31/042—PV modules or arrays of single PV cells

- H01L31/05—Electrical interconnection means between PV cells inside the PV module, e.g. series connection of PV cells

- H01L31/0504—Electrical interconnection means between PV cells inside the PV module, e.g. series connection of PV cells specially adapted for series or parallel connection of solar cells in a module

- H01L31/0512—Electrical interconnection means between PV cells inside the PV module, e.g. series connection of PV cells specially adapted for series or parallel connection of solar cells in a module made of a particular material or composition of materials

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Manufacturing & Machinery (AREA)

- Life Sciences & Earth Sciences (AREA)

- Sustainable Development (AREA)

- Sustainable Energy (AREA)

- Photovoltaic Devices (AREA)

- Laminated Bodies (AREA)

Abstract

Description

−可能な限り最小の面積での可能な限り大量の電流の形成、

−可能な限り最小限のコストでの大量生産、

−電流形成の長期間の安定性、

−特に接続箇所における、環境の影響に対する安定性、

−確実な電流形成。

−少なくとも部分的に導電性の誘電層を、半導体基板のうちの少なくとも1つの半導体基板の少なくとも1つの基板表面に設けるステップ、及び、

−半導体基板を別の半導体基板に接触接続させ、それらの半導体基板間に導電性の接続部を形成するステップ。

本方法の第1の実施の形態の第1のステップにおいては、電気的なナノ粒子が、接合されるべき基板の表面に施与され、特に太陽電池の表面に施与され、特に表面にのみ施与される。ナノ粒子を可能な限り良質に分散させるために、施与は有利には、スピンコーティングプロセス、有利にはスプレーコーティングプロセスによって塗布される溶液によって行われる。

・純金属、特に、

○Cu、Ag、Au、Al、Pt、Pb、Zn、Sn、W、Nb、Ta、Te及び/又はNb、

・合金、特に、

○青銅合金、有利にはCuSn、及び/又は

○黄銅合金、及び/又は

○金合金、及び/又は

○銅合金、特にCuAg、CuAg及び/又はCuAgSn。

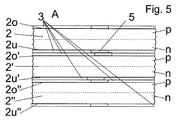

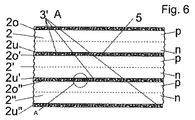

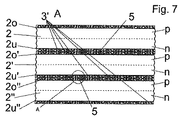

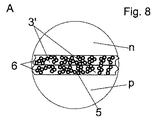

2、2’、2’’ 基板

2o、2o’、2o’’ 基板表面

2u、2u’、2u’’ 基板表面

3、3’ 誘電層

4 ビア

5、5’、5’’ コンタクト箇所

6 ナノ粒子

p 半導体基板のp型ドープ層

n 半導体基板のn型ドープ層

D 平均直径

f 平均アライメント誤差

Claims (13)

- 波長感応性の半導体基板(2)と、少なくとも1つの別の波長感応性の半導体基板(2’、2’’)と、から成る多層基板スタックを製造するための方法において、

−少なくとも部分的に導電性の誘電層(3、3’)を、前記半導体基板(2、2’、2’’)のうちの少なくとも1つの半導体基板の少なくとも1つの基板表面(2o、2o’、2o’’、2u、2u’、2u’’)に設けるステップと、

−前記半導体基板(2)を前記別の半導体基板(2’、2’’)に接触接続させ、前記半導体基板(2、2’、2’’)間に導電性の接続部を形成するステップと、

を備えていることを特徴とする方法。 - 各半導体基板(2、2’、2’’)は、n型ドープ層及びp型ドープ層を有しており、隣接し合っている半導体基板(2、2’、2’’)は、それぞれ、n型ドープ層によって、隣接する半導体基板(2、2’、2’’)のp型ドープ層に接している、

請求項1に記載の方法。 - 前記誘電層(3、3’)を、ゾルゲルプロセスによって、マトリクス複合材料として形成し、特に、導電性の粒子が混合された、有利にはナノ粒子が混合されたセラミック層として、有利には酸化ケイ素層として形成する、

請求項1又は2に記載の方法。 - 前記誘電層(3、3’)を、ナノ粒子を少なくとも部分的に施与し、続いて、天然酸化物により前記誘電層(3、3’)を酸化させることによって形成する、

請求項1又は2に記載の方法。 - 前記半導体基板(2、2’、2’’)は、太陽電池として形成されている、

請求項1乃至4のいずれか1項に記載の方法。 - 前記半導体基板(2、2’、2’’)は、異なる波長領域において、特に少なくとも部分的に異なる波長領域において、有利には大部分が異なる波長領域において、更に有利には完全に異なる波長領域において、波長感応性に形成されている、

請求項1乃至5のいずれか1項に記載の方法。 - 前記誘電層(3、3’)を、それぞれ、対向する2つの基板表面(2o、2o’、2o’’、2u、2u’、2u’’)に設ける、

請求項1乃至6のいずれか1項に記載の方法。 - 前記半導体基板(2、2’、2’’)のアライメントを、特に純粋に機械的なアライメントを、光学手段を用いずに、及び/又は、前記半導体基板(2、2’、2’’)における光学的なアライメントマークを用いずに、前記接触接続前又は前記接触接続時に行う、

請求項1乃至7のいずれか1項に記載の方法。 - 前記半導体基板(2、2’、2’’)の前記接触接続後又は前記接触接続時に、前記半導体基板(2、2’、2’’)間の接合部を形成し、特に永続的な接合部を形成し、有利には直接接合部又はフュージョンボンディング部を形成する、

請求項1乃至8のいずれか1項に記載の方法。 - 前記半導体基板(2、2’、2’’)は、各半導体基板(2、2’、2’’)の、それぞれ相互に背中合わせに位置する基板表面(2o、2o’、2o’’、2u、2u’、2u’’)を導電的に接合させるための導電性のビア(4)を有している、

請求項1乃至9のいずれか1項に記載の方法。 - 前記誘電層(3、3’)を、部分的に、導電性のコンタクト箇所(5)を備えた前記ビア(4)にのみ形成する、

請求項10に記載の方法。 - 前記接触接続時に、平均アライメント誤差fと少なくとも同じ大きさの直径Dを有する、有利には平均アライメント誤差fよりも大きい直径Dを有するコンタクト箇所(5)を形成する、

請求項11に記載の方法。 - 半導体基板(2)、特に波長感応性の半導体基板(2)と、少なくとも1つの別の半導体基板(2’、2’’)、特に波長感応性の別の半導体基板(2’、2’’)と、から成り、

前記半導体基板(2、2’、2’’)のうちの少なくとも1つの半導体基板の少なくとも1つの基板表面(2o、2o’、2o’’、2u、2u’、2u’’)に、少なくとも部分的に導電性の誘電層(3、3’)を備えており、且つ、

前記半導体基板(2)と前記別の半導体基板(2’、2’’)との接触接続によって形成される、前記半導体基板(2、2’、2’’)間の導電性の接続部を備えていることを特徴とする、

多層基板スタック。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102014112430.8A DE102014112430A1 (de) | 2014-08-29 | 2014-08-29 | Verfahren zur Herstellung eines leitenden Mehrfachsubstratstapels |

| DE102014112430.8 | 2014-08-29 | ||

| PCT/EP2015/064975 WO2016030053A1 (de) | 2014-08-29 | 2015-07-01 | Verfahren zur herstellung eines leitenden mehrfachsubstratstapels |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2017529696A true JP2017529696A (ja) | 2017-10-05 |

Family

ID=53540732

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017509716A Pending JP2017529696A (ja) | 2014-08-29 | 2015-07-01 | 導電性の多層基板スタックを製造するための方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US10243094B2 (ja) |

| JP (1) | JP2017529696A (ja) |

| CN (1) | CN106796932A (ja) |

| AT (1) | AT520249B1 (ja) |

| DE (1) | DE102014112430A1 (ja) |

| WO (1) | WO2016030053A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102014112430A1 (de) | 2014-08-29 | 2016-03-03 | Ev Group E. Thallner Gmbh | Verfahren zur Herstellung eines leitenden Mehrfachsubstratstapels |

| JP6759464B2 (ja) * | 2018-03-20 | 2020-09-23 | 株式会社東芝 | 多接合型太陽電池モジュール及び太陽光発電システム |

| CN112349801B (zh) * | 2020-10-16 | 2023-12-01 | 泰州隆基乐叶光伏科技有限公司 | 叠层电池的中间串联层及生产方法、叠层电池 |

| FR3121544B1 (fr) * | 2021-03-31 | 2023-11-24 | St Microelectronics Crolles 2 Sas | Structure d'isolation thermique et électrique |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008034609A (ja) * | 2006-07-28 | 2008-02-14 | Kyocera Corp | 太陽電池素子及びこれを用いた太陽電池モジュール、並びに、これらの製造方法 |

| JP2008208442A (ja) * | 2007-02-28 | 2008-09-11 | Hitachi Ltd | 金属化合物粒子を用いた接合方法 |

| WO2008108990A1 (en) * | 2007-03-06 | 2008-09-12 | Sunlight Photonics Inc. | Spectrally adaptive multijunction photovoltaic thin film device and method of producing same |

| JP2010118473A (ja) * | 2008-11-12 | 2010-05-27 | PVG Solutions株式会社 | 太陽電池セルおよびその製造方法 |

| JP2011508424A (ja) * | 2007-12-20 | 2011-03-10 | シーマ ナノ テック イスラエル リミティド | ナノ粒子で形成された透明電極を有する光起電力デバイス |

| JP2012531052A (ja) * | 2009-07-17 | 2012-12-06 | ソイテック | 亜鉛、シリコン、および、酸素に基づいた結合層を用いて結合する方法および対応する構造 |

| WO2013058291A1 (ja) * | 2011-10-17 | 2013-04-25 | 独立行政法人産業技術総合研究所 | 半導体素子の接合方法および接合構造 |

| JP2014003272A (ja) * | 2012-05-24 | 2014-01-09 | Napura:Kk | 積層基板 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4338480A (en) * | 1980-12-29 | 1982-07-06 | Varian Associates, Inc. | Stacked multijunction photovoltaic converters |

| FR2690278A1 (fr) * | 1992-04-15 | 1993-10-22 | Picogiga Sa | Composant photovoltaïque multispectral à empilement de cellules, et procédé de réalisation. |

| US20050217717A1 (en) * | 2002-01-02 | 2005-10-06 | Sadeg Faris | Photovoltaic cell and method of manufacture of photovoltaic cells |

| US7122734B2 (en) * | 2002-10-23 | 2006-10-17 | The Boeing Company | Isoelectronic surfactant suppression of threading dislocations in metamorphic epitaxial layers |

| US20070107773A1 (en) * | 2005-11-17 | 2007-05-17 | Palo Alto Research Center Incorporated | Bifacial cell with extruded gridline metallization |

| TWI335059B (en) * | 2007-07-31 | 2010-12-21 | Siliconware Precision Industries Co Ltd | Multi-chip stack structure having silicon channel and method for fabricating the same |

| KR100909562B1 (ko) | 2007-12-21 | 2009-07-27 | 주식회사 동부하이텍 | 반도체 소자 및 그 제조방법 |

| DE102008017312B4 (de) | 2008-04-04 | 2012-11-22 | Universität Stuttgart | Verfahren zur Herstellung einer Solarzelle |

| US8097955B2 (en) * | 2008-10-15 | 2012-01-17 | Qimonda Ag | Interconnect structures and methods |

| WO2010140522A1 (en) * | 2009-06-05 | 2010-12-09 | Semiconductor Energy Laboratory Co., Ltd. | Photoelectric conversion device and manufacturing method thereof |

| CN102460722B (zh) * | 2009-06-05 | 2015-04-01 | 株式会社半导体能源研究所 | 光电转换装置及其制造方法 |

| US20120152340A1 (en) * | 2009-08-27 | 2012-06-21 | Mitsubishi Heavy Industries, Ltd. | Multi-junction photovoltaic device, integrated multi-junction photovoltaic device, and processes for producing same |

| TW201145493A (en) * | 2010-06-01 | 2011-12-16 | Chipmos Technologies Inc | Silicon wafer structure and multi-chip stack structure |

| US20130240027A1 (en) * | 2010-06-07 | 2013-09-19 | Solarno, Inc. | Multijunction hybrid solar cell with parallel connection and nanomaterial charge collecting interlayers |

| US20130206219A1 (en) * | 2010-08-06 | 2013-08-15 | Juanita N. Kurtin | Cooperative photovoltaic networks and photovoltaic cell adaptations for use therein |

| KR102430673B1 (ko) | 2011-01-25 | 2022-08-08 | 에베 그룹 에. 탈너 게엠베하 | 웨이퍼들의 영구적 결합을 위한 방법 |

| WO2012115602A1 (en) | 2011-02-21 | 2012-08-30 | Bedjukh Oleksandr | Photovoltaic converter (variants) and solar battery based thereon |

| US10825793B2 (en) | 2011-04-08 | 2020-11-03 | Ev Group E. Thallner Gmbh | Method for permanently bonding wafers |

| SG193407A1 (en) | 2011-04-08 | 2013-10-30 | Ev Group E Thallner Gmbh | Method for permanent bonding of wafers |

| SG193903A1 (en) | 2011-04-08 | 2013-11-29 | Ev Group E Thallner Gmbh | Method for permanent bonding of wafers |

| JP5936968B2 (ja) * | 2011-09-22 | 2016-06-22 | 株式会社東芝 | 半導体装置とその製造方法 |

| EP3035370A1 (de) | 2012-07-24 | 2016-06-22 | EV Group E. Thallner GmbH | Vorrichtung zum permanenten bonden von wafern |

| KR101739210B1 (ko) | 2012-07-26 | 2017-05-23 | 에베 그룹 에. 탈너 게엠베하 | 기판을 본딩하기 위한 방법 |

| US10158032B2 (en) * | 2012-10-12 | 2018-12-18 | Heraeus Deutschland GmbH & Co. KG | Solar cells produced from high Ohmic wafers and halogen containing paste |

| DE102014112430A1 (de) | 2014-08-29 | 2016-03-03 | Ev Group E. Thallner Gmbh | Verfahren zur Herstellung eines leitenden Mehrfachsubstratstapels |

-

2014

- 2014-08-29 DE DE102014112430.8A patent/DE102014112430A1/de not_active Withdrawn

-

2015

- 2015-07-01 JP JP2017509716A patent/JP2017529696A/ja active Pending

- 2015-07-01 US US15/505,280 patent/US10243094B2/en active Active

- 2015-07-01 AT ATA9277/2015A patent/AT520249B1/de active

- 2015-07-01 CN CN201580045190.1A patent/CN106796932A/zh active Pending

- 2015-07-01 WO PCT/EP2015/064975 patent/WO2016030053A1/de active Application Filing

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008034609A (ja) * | 2006-07-28 | 2008-02-14 | Kyocera Corp | 太陽電池素子及びこれを用いた太陽電池モジュール、並びに、これらの製造方法 |

| JP2008208442A (ja) * | 2007-02-28 | 2008-09-11 | Hitachi Ltd | 金属化合物粒子を用いた接合方法 |

| WO2008108990A1 (en) * | 2007-03-06 | 2008-09-12 | Sunlight Photonics Inc. | Spectrally adaptive multijunction photovoltaic thin film device and method of producing same |

| JP2011508424A (ja) * | 2007-12-20 | 2011-03-10 | シーマ ナノ テック イスラエル リミティド | ナノ粒子で形成された透明電極を有する光起電力デバイス |

| JP2010118473A (ja) * | 2008-11-12 | 2010-05-27 | PVG Solutions株式会社 | 太陽電池セルおよびその製造方法 |

| JP2012531052A (ja) * | 2009-07-17 | 2012-12-06 | ソイテック | 亜鉛、シリコン、および、酸素に基づいた結合層を用いて結合する方法および対応する構造 |

| WO2013058291A1 (ja) * | 2011-10-17 | 2013-04-25 | 独立行政法人産業技術総合研究所 | 半導体素子の接合方法および接合構造 |

| JP2014003272A (ja) * | 2012-05-24 | 2014-01-09 | Napura:Kk | 積層基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102014112430A1 (de) | 2016-03-03 |

| AT520249A5 (de) | 2019-02-15 |

| CN106796932A (zh) | 2017-05-31 |

| US20170256663A1 (en) | 2017-09-07 |

| US10243094B2 (en) | 2019-03-26 |

| WO2016030053A1 (de) | 2016-03-03 |

| AT520249B1 (de) | 2022-09-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5533199B2 (ja) | 素子の基板実装方法、および、その基板実装構造 | |

| TWI745567B (zh) | 積層裝置、積層體及積層裝置的製造方法 | |

| JP2017529696A (ja) | 導電性の多層基板スタックを製造するための方法 | |

| JP7120402B2 (ja) | 半導体装置及びその製造方法 | |

| TW201044546A (en) | A three-dimensional electronics package | |

| CN102723306B (zh) | 一种利用穿硅通孔的微波多芯片封装结构及其制作方法 | |

| KR102370046B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| JP6220063B2 (ja) | 太陽電池及び太陽電池の製造方法 | |

| JP6017297B2 (ja) | 半導体装置の製造方法 | |

| JPWO2014109139A1 (ja) | 樹脂多層基板およびその製造方法 | |

| CN105140253A (zh) | 一种背照式影像芯片晶圆级3d堆叠结构及封装工艺 | |

| CN107112314A (zh) | 多层基板 | |

| JP2015095499A (ja) | 半導体装置の製造方法 | |

| JP2017141328A (ja) | 透明導電性接着剤、積層体、及び基板の接合方法 | |

| Klein et al. | Lamination of transparent conductive adhesives for tandem solar cell applications | |

| CN104620385A (zh) | 半导体装置、半导体装置的制造方法和电子装置 | |

| US20130069232A1 (en) | Damascene process for aligning and bonding through-silicon-via based 3d integrated circuit stacks | |

| JP2013046036A (ja) | 基材 | |

| Désières et al. | Strong light extraction enhancement using TiO2 nanoparticles-based microcone arrays embossed on III-Nitride light emitting diodes | |

| WO2016139794A1 (ja) | 半導体装置および半導体装置の製造方法 | |

| TW201240057A (en) | Wafer-level electromagnetic interference shielding structure and manufacturing method thereof | |

| WO2016170901A1 (ja) | 回路基板の製造方法、電子デバイスの製造方法、および、電子デバイス | |

| TW201915222A (zh) | 金屬填充微細結構體的製造方法及絕緣性基材 | |

| JP2008306129A (ja) | 光電変換装置の製造方法 | |

| WO2021193357A1 (ja) | 熱電変換モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A529 Effective date: 20170217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190524 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190603 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200114 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20200811 |