[0032]「例示的」という単語は、本明細書では「例、事例、または例示の働きをすること」を意味するために使用する。「例示的」として本明細書で説明するいかなる態様も、必ずしも他の態様よりも好適または有利なものと解釈されるべきであるとは限らない。2つの要素に関して「結合される」という用語は、本明細書では0個以上の中間要素が2つの要素間の電気回路中に挿入されることを意味するために使用する。0個の中間要素を介して互いに結合された2つの要素は、互いに直接接続される。

[0033]本開示の例示的な実施形態は、等電位ノード間の電圧不平衡、等電位ノード間のキャパシタンス不平衡、またはその両方の最小化を促進することによって高線形性を促進するスイッチスタックデバイスを対象とする。当業者によって理解されるように、および例示的な実施形態に関して以下でさらに説明するように、等電位ノードは「理想的な場合」では互いと同じRF電圧を有する。本開示では、「理想的な場合」は、最大線形性を有するスイッチスタックデバイスを指す。電圧不平衡が、バイアスネットワークによってもたらされ得、寄生キャパシタンスと、バイアス抵抗を通るコモンモード電流との複合効果によって引き起こされ得る。寄生キャパシタンスによってキャパシタンス不平衡が引き起こされ得る。以下で説明する例示的な実施形態は、RF等電位ノードの維持を促進するゲートノードまたはボディノードフィルタ処理回路を含む。以下で説明する様々な例示的な実施形態を通して示されるように、そのようなフィルタ処理回路は、容量ベース(capacitive-based)(「Cベース」)または抵抗容量ベース(resistive-capacitive-based)(「RCベース」)であり得る。以下で説明する様々な例示的な実施形態を通して示されるように、フィルタ処理回路は、デバイスの各単位セル中に、またはデバイスのすべての単位セルに共通するゲートまたはボディバイアスネットワーク中に含まれ得る。寄生キャパシタンスなど、FET中に本質的に存在し得るものに加えて、以下で説明するフィルタ処理回路のキャパシタンスがあることを理解されたい。

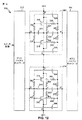

[0034]図3に示されているように、第1の例示的な実施形態では、スイッチスタックデバイス36は、チェーン中の連続するFET単位セル回路のペアのうちの一方のセルソースノード(「S」)が、チェーン中の連続するFET単位セル回路のペアのうちの他方のセルドレインノード(「D」)に直接接続されるスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路38、第2のFET単位セル回路40など〜第NのFET単位セル回路42を含む。たとえば、第1のFET単位セル回路38のセルソースノードは、第2のFET単位セル回路40のセルドレインノードに直接接続される。明快のために図示されていない、第2のFET単位セル回路40と第NのFET単位セル回路42との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。第NのFET単位セル回路42のセルソースノードは第1のRF信号ノード(「RF1」)に接続され、第1のFET単位セル回路38のセルドレインノードは第2のRF信号ノード(「RF2」)に接続される。FET単位セル回路38〜42の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス36は、シリコンオンインシュレータ(SOI)基板上か、または他の好適な様式で形成され得る。

[0035]FET用語に関して、本明細書で説明する例示的な実施形態では、第1のRF信号ノードにより近いFETノードが「ソース」と呼ばれ、反対のノードが「ドレイン」と呼ばれるが、これは要件でない。当業者によって理解されるように、FETは、様々な設計および極性(たとえば、NチャネルFETおよびPチャネルFET、拡張およびデプレッションモード、様々なしきい値電圧など)において実装され得る。さらに、FETが採用される回路は、本明細書で従うものとは異なる記号規則を使用して示され得る。いくつかの事例におけるFET極性およびドレインソースノード配向は、回路の動作原理を著しく変更することなしに交換され得る。例示規則、FET極性、およびFET設計の多数の可能な置換を示すのではなく、本明細書で示す例示的な説明および図は、すべてのそのような代替回路記述および等価デバイス設計を包含することが当業者によって理解されるべきである。FET回路接続に関する「ドレインノード」という用語は、それの意味の範囲内にソースノードをも含み、FET回路接続に関する「ソースノード」という用語は、それの意味の範囲内にドレインノードをも含むことが特に理解されるべきである。

[0036]図3に示されている例示的な実施形態では、FET単位セル回路38〜42の各々のセルゲートノード(「G」)は、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路44に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。

[0037]ゲートバイアスネットワークフィルタ回路44はまた、入力として従来のスイッチ制御信号を受信し、図示されていないが、1つまたは複数の従来のバイアス電圧のソースに接続される。スイッチ制御信号に応答して、スイッチスタックデバイス36は、RF1とRF2との間の回路を開くまたは閉じる。そのようなスイッチ制御信号が、そのような切替え機能を与えるために、ゲートバイアス回路に結合され得る様式は、当業者によってよく知られているので、この従来の態様について本明細書でさらに詳細に説明しない。

[0038]図3に示されている例示的な実施形態では、FET単位セル回路38〜42の各々のセルボディノード(「B」)は、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路46に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路46は、1つまたは複数のバイアス電圧のソースにも接続される。

[0039]FET単位セル回路38は、FET48とボディフィルタとを含む。ボディフィルタはボディフィルタキャパシタンス50を含む。ボディフィルタキャパシタンス50は、FET48のボディノードとゲートノードとの間に結合される。FET48のドレインノードは、FET単位セル回路38のセルドレインノード、すなわち、それがFET48のドレインノードであるかのように同じ様式でFET単位セル回路38の外部の回路に接続され得るノードを定義することに留意されたい。同様に、FET48のソースノードは、FET単位セル回路38のセルソースノード、すなわち、それがFET48のソースノードであるかのように同じ様式でFET単位セル回路38の外部の回路に接続され得るノードを定義する。同じく、FET48のゲートノードは、FET単位セル回路38のセルゲートノード、すなわち、それがFET48のゲートノードであるかのように同じ様式でFET単位セル回路38の外部の回路に接続され得るノードを定義する。また、FET48のボディノードは、FET単位セル回路38のセルボディノード、すなわち、それがFET48のボディノードであるかのように同じ様式でFET単位セル回路38の外部の回路に接続され得るノードを定義する。スイッチスタックデバイス36の線形性を促進する本明細書で説明するフィルタ処理効果を別にすれば、FET単位セル回路38〜42の各々は、従来のFETと同様の様式で挙動する。

[0040]FET単位セル回路38の上記で説明した構造は、以下の様式で線形動作を促進する。FET48のボディノードは、FET48のゲートノードと比較して極めて高いインピーダントであり、また、極めて非線形である。理想的な場合では、すなわち、最大線形性を促進するために、ボディノードとゲートノードの両方は、容量性電圧分割により、まったく同じRF電圧を有する。理想的な場合では、FET48のボディノードおよびゲートノードは同じRF電圧電位を有し、すなわち、それらはRF周波数において等電位ノードである。そのような等電位ノード間にボディフィルタキャパシタンス50を結合することは、この等電位関係の維持を促進する。ボディフィルタキャパシタンス50は、FET48のボディノードとソースノードとの間の内部または固有のキャパシタンスに関して、およびFET48のボディノードとドレインノードとの間の内部または固有のキャパシタンスに関して低インピーダントであるので、ボディフィルタキャパシタンス50は、ゲートノード電圧の使用によってボディノード電圧をフィルタ処理する。ボディバイアスネットワークフィルタ回路46を通るRF電流(コモンモードおよび差動モード)の主要部は、FETゲートノードが特徴的にFETボディノードよりもはるかに低インピーダントであるので、FET48のゲートノードから供給される。さらに、ゲートノード(および、したがって、ゲート接合)は、ボディ接合よりも線形であり、それにより、FET単位セル回路38の線形挙動を促進する。

[0041]残りのN−1個のFET単位セル回路40〜42の各々は、上記で説明したFET単位セル回路38のものと同等の構造を有するので、FET単位セル回路40〜42について同様に詳細には説明しない。FET単位セル回路40は、それぞれ、上記で説明したFET48およびボディフィルタキャパシタンス50と同等である、FET52およびボディフィルタキャパシタンス54を含むことに留意されたい。同様に、FET単位セル回路42は、それぞれ、上記で説明したFET48およびボディフィルタキャパシタンス50と同等である、FET56およびボディフィルタキャパシタンス58を含む。

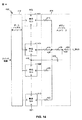

[0042]図4に示されているように、第2の例示的な実施形態では、スイッチスタックデバイス60は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路62、第2のFET単位セル回路64など〜第NのFET単位セル回路66を含む。明快のために図示されていない、第2のFET単位セル回路64と第NのFET単位セル回路66との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路62〜66の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス60は、SOI基板上か、または他の好適な様式で形成され得る。

[0043]図4に示されている例示的な実施形態では、FET単位セル回路62〜66の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路68に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路68はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス60を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路68は、1つまたは複数のバイアス電圧のソースにも接続される。

[0044]図4に示されている例示的な実施形態では、FET単位セル回路62〜66の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路70に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路70は、1つまたは複数のバイアス電圧のソースに接続される。

[0045]FET単位セル回路62は、FET72とボディフィルタとを含む。ボディフィルタは、ボディフィルタキャパシタンス74とボディフィルタ抵抗76とを含む。ボディフィルタキャパシタンス74およびボディフィルタ抵抗76は、互いに直列であり、FET72のボディノードとゲートノードとの間に結合される。FET72のドレインノードはFET単位セル回路62のセルドレインノードを定義し、FET72のソースノードはFET単位セル回路38のセルソースノードを定義し、FET72のゲートノードはFET単位セル回路62のセルゲートノードを定義することに留意されたい。しかしながら、FET単位セル回路62のセルボディノードは、FET72のボディノードによってではなく、ボディフィルタキャパシタンス74とボディフィルタ抵抗76との間の仮想ノード(B’)によって定義される。

[0046]FET単位セル回路38の上記で説明した構造は、図3に示されている実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。より詳細には、ボディフィルタキャパシタンス74とボディフィルタ抵抗76とを備えるRCベースボディフィルタは、図3に示されている実施形態におけるボディフィルタキャパシタンス50を備えるCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0047]残りのN−1個のFET単位セル回路64〜66の各々は、上記で説明したFET単位セル回路62のものと同等の構造を有するので、FET単位セル回路64〜66について同様に詳細には説明しない。FET単位セル回路64は、それぞれ、上記で説明したFET72、ボディフィルタキャパシタンス74、およびボディフィルタ抵抗76と同等である、FET78、ボディフィルタキャパシタンス80、およびボディフィルタ抵抗82を含むことに留意されたい。同様に、FET単位セル回路66は、それぞれ、上記で説明したFET72、ボディフィルタキャパシタンス74、およびボディフィルタ抵抗76と同等である、FET84、ボディフィルタキャパシタンス86、およびボディフィルタ抵抗88を含む。

[0048]図5に示されているように、第3の例示的な実施形態では、スイッチスタックデバイス90は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路92〜第NのFET単位セル回路94を含む。明快のために図示されていない、第1のFET単位セル回路92と第NのFET単位セル回路94との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路92〜94の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス90は、SOI基板上か、または他の好適な様式で形成され得る。

[0049]図5に示されている例示的な実施形態では、FET単位セル回路92〜94の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路96に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路96はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス90を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路96は、1つまたは複数のバイアス電圧のソースにも接続される。

[0050]図5に示されている例示的な実施形態では、FET単位セル回路92〜94の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路98に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路98は、1つまたは複数のバイアス電圧のソースに接続される。

[0051]FET単位セル回路92は、FET100とゲートフィルタとを含む。ゲートフィルタは、ゲートフィルタキャパシタンス102とドレインソース回路とを含む。ドレインソース回路は、FET100のドレインノードとソースノードとの間に接続され、第2の抵抗106と直列の第1の抵抗104を有する抵抗性分割器回路を備える。抵抗性分割器回路は、第1の抵抗104と第2の抵抗106との間の仮想ノード(「V」)を定義する。ゲートフィルタキャパシタンス102は、FET100のゲートノードとこの仮想ノードVとの間に結合される。

[0052]FET100のドレインノードはFET単位セル回路92のセルドレインノードを定義し、FET100のソースノードはFET単位セル回路92のセルソースノードを定義し、FET100のゲートノードはFET単位セル回路92のセルゲートノードを定義し、FET100のボディノードはFET単位セル回路92のセルボディノードを定義することに留意されたい。(FET100のボディノード、およびそれとFET単位セル回路92のセルボディノードとの間の接続は、明快のために図示されていない。)そのようなFETがボディノードを含まない実施形態(図示せず)では、ボディバイアスネットワークフィルタ回路98も他のボディバイアスネットワークも含まれる必要がないことに留意されたい。したがって、FET単位セル回路92〜94は、FET技術がボディノードを与えない実施形態にも好適である。

[0053]FET単位セル回路92の上記で説明した構造は、図5に示されている実施形態ではフィルタ処理がFETゲートノードに適用されるが、図3〜図4に示されている実施形態ではフィルタ処理がFETボディノードに適用されることを除いて、図3〜図4に示されている実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。ゲートフィルタキャパシタンス102を備えるCベースゲートフィルタは、それぞれ、図3および図4に示されている実施形態におけるCベースボディフィルタおよびRCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0054]残りのN−1個のFET単位セル回路94などの各々は、上記で説明したFET単位セル回路92のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路94は、それぞれ、上記で説明したFET100、ゲートフィルタキャパシタンス102、ならびに抵抗104および抵抗106と同等である、FET108、ゲートフィルタキャパシタンス110、および第1の抵抗112と第2の抵抗114とを備えるドレインソースバイアス回路を含むことに留意されたい。

[0055]図6に示されているように、第4の例示的な実施形態では、スイッチスタックデバイス116は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路118〜第NのFET単位セル回路120を含む。明快のために図示されていない、第1のFET単位セル回路118と第NのFET単位セル回路120との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路118〜120の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス116は、SOI基板上か、または他の好適な様式で形成され得る。

[0056]図6に示されている例示的な実施形態では、FET単位セル回路118〜120の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路122に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路122はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス116を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路122は、1つまたは複数のバイアス電圧のソースにも接続される。

[0057]図6に示されている例示的な実施形態では、FET単位セル回路118〜120の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路124に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路124は、1つまたは複数のバイアス電圧のソースに接続される。

[0058]FET単位セル回路118は、FET126とゲートフィルタとを含む。ゲートフィルタは、ゲートフィルタキャパシタンス128と、ゲートフィルタ抵抗130と、ドレインソース回路とを含む。ドレインソース回路は、FET126のドレインノードとソースノードとの間に接続され、第2の抵抗134と直列の第1の抵抗132を有する抵抗性分割器回路を備える。抵抗性分割器回路は、第1の抵抗132と第2の抵抗134との間の仮想ノードVを定義する。ゲートフィルタキャパシタンス128およびゲートフィルタ抵抗130は、互いに直列であり、FET126のゲートノードと、この仮想ノードVとの間に結合される。

[0059]FET126のドレインノードはFET単位セル回路118のセルドレインノードを定義し、FET126のソースノードはFET単位セル回路118のセルソースノードを定義し、FET126のボディノードはFET単位セル回路118のセルボディノードを定義することに留意されたい。(FET126のボディノード、およびそれとFET単位セル回路118のセルボディノードとの間の接続は、明快のために図示されていない。)しかしながら、FET単位セル回路118のセルゲートノード(G’)は、FET126のゲートノードによってではなく、ゲートフィルタキャパシタンス128とゲートフィルタ抵抗130との間の別の仮想(ゲート)ノードによって定義される。そのようなFETがボディノードを含まない実施形態(図示せず)では、ボディバイアスネットワークフィルタ回路124も他のボディバイアスネットワークも含まれる必要がないことに留意されたい。したがって、FET単位セル回路118〜120は、FET技術がボディノードを与えない実施形態にも好適である。

[0060]FET単位セル回路118の上記で説明した構造は、図5に示されている実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。ゲートフィルタキャパシタンス128とゲートフィルタ抵抗130とを備えるRCベースゲートフィルタは、図5に示されている実施形態におけるCベースゲートフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0061]残りのN−1個のFET単位セル回路120などの各々は、上記で説明したFET単位セル回路118のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路120は、それぞれ、上記で説明したFET126、ゲートフィルタキャパシタンス128、ゲートフィルタ抵抗130、ならびに抵抗132および抵抗134と同等である、FET136、ゲートフィルタキャパシタンス138、ゲートフィルタ抵抗140、および第1の抵抗142と第2の抵抗144とを備えるドレインソースバイアス回路を含むことに留意されたい。

[0062]図7に示されているように、第5の例示的な実施形態では、スイッチスタックデバイス146は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路148〜第NのFET単位セル回路150を含む。明快のために図示されていない、第1のFET単位セル回路148と第NのFET単位セル回路150との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路148〜150の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス146は、SOI基板上か、または他の好適な様式で形成され得る。

[0063]図7に示されている例示的な実施形態では、FET単位セル回路148〜150の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路152に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路152はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス146を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路152は、1つまたは複数のバイアス電圧のソースにも接続される。

[0064]FET単位セル回路148〜150の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路154に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路154は、1つまたは複数のバイアス電圧のソースに接続される。

[0065]FET単位セル回路148は、FET156とゲートフィルタとを含む。ゲートフィルタは、ゲートフィルタ抵抗158とドレインソース回路とを含む。ドレインソース回路は、FET156のドレインノードとソースノードとの間に接続され、第2のゲートフィルタキャパシタンス162と直列の第1のゲートフィルタキャパシタンス160を備える。このドレインソース回路は、第1のゲートフィルタキャパシタンス160と第2のゲートフィルタキャパシタンス162との間の仮想ノードVを定義する。ゲートフィルタ抵抗158は、FET156のゲートノードとこの仮想ノードVとの間に結合される。

[0066]FET156のドレインノードはFET単位セル回路148のセルドレインノードを定義し、FET156のソースノードはFET単位セル回路148のセルソースノードを定義し、FET156のボディノードはFET単位セル回路148のセルボディノードを定義することに留意されたい。(FET156のボディノード、およびそれとFET単位セル回路148のセルボディノードとの間の接続は、明快のために図示されていない。)しかしながら、FET単位セル回路148のセルゲートノード(G’)は、FET156のゲートノードによってではなく、ゲートフィルタ抵抗158と、ゲートフィルタキャパシタンス160および162を備えるドレインソース回路との間の別の仮想(ゲート)ノードによって定義される。そのようなFETがボディノードを含まない実施形態(図示せず)では、ボディバイアスネットワークフィルタ回路154も他のボディバイアスネットワークも含まれる必要がないことに留意されたい。したがって、FET単位セル回路148〜150は、FET技術がボディノードを与えない実施形態にも好適である。

[0067]FET単位セル回路148の上記で説明した構造は、図6に示されている実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。ゲートフィルタ抵抗158と、ゲートフィルタキャパシタンス160と、ゲートフィルタキャパシタンス162とを備えるRCベースゲートフィルタは、図6に示されている実施形態におけるRCベースゲートフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0068]残りのN−1個のFET単位セル回路150などの各々は、上記で説明したFET単位セル回路148のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路150は、それぞれ、上記で説明したFET156、ゲートフィルタ抵抗158、第1のゲートフィルタキャパシタンス160、および第2のゲートフィルタキャパシタンス162と同等である、FET164、ゲートフィルタ抵抗166、および第1のゲートフィルタキャパシタンス168と第2のゲートフィルタキャパシタンス170とを備えるドレインソースバイアス回路を含むことに留意されたい。

[0069]図8に示されているように、第6の例示的な実施形態では、スイッチスタックデバイス172は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路174〜第NのFET単位セル回路176を含む。明快のために図示されていない、第1のFET単位セル回路174と第NのFET単位セル回路176との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路174〜176の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス172は、SOI基板上か、または他の好適な様式で形成され得る。

[0070]図8に示されている例示的な実施形態では、FET単位セル回路174〜176の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路178に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路178はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス172を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路178は、1つまたは複数のバイアス電圧のソースにも接続される。

[0071]FET単位セル回路174〜176の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路180に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路180は、1つまたは複数のバイアス電圧のソースに接続される。

[0072]FET単位セル回路174は、FET182と、ゲートフィルタと、ボディフィルタとを含む。ゲートフィルタは、ゲートフィルタキャパシタンス184と、ゲートフィルタ抵抗186と、ドレインソース回路とを含む。ドレインソース回路は、FET182のドレインノードとソースノードとの間に接続され、第2の抵抗190と直列の第1の抵抗188を有する抵抗性分割器回路を備える。このドレインソース回路は、第1の抵抗188と第2の抵抗190との間の仮想ノードVを定義する。ゲートフィルタキャパシタンス184およびゲートフィルタ抵抗186は、互いに直列であり、FET182のゲートノードと、仮想ノードVとの間に結合される。ボディフィルタは、FET182のボディノードと、仮想ノードVとの間に結合された(および、したがって、FET182のボディノードと、FET182のゲートノードとの間にも結合された)ボディフィルタキャパシタンス192を含む。

[0073]FET182のドレインノードはFET単位セル回路174のセルドレインノードを定義し、FET182のソースノードはFET単位セル回路174のセルソースノードを定義し、FET182のボディノードはFET単位セル回路174のセルボディノードを定義することに留意されたい。(FET182のボディノードとFET単位セル回路174のセルボディノードとは同じノードBであるが、接続は、明快のために明示的に図示されていないことを理解されたい。)しかしながら、FET単位セル回路174のセルゲートノード(G’)は、FET182のゲートノードによってではなく、ゲートフィルタキャパシタンス184とゲートフィルタ抵抗186との間の別の仮想(ゲート)ノードによって定義される。

[0074]FET単位セル回路174の構造は、他の実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。RCベースゲートフィルタとRCベースボディフィルタとの組合せは、上記で説明した他の実施形態におけるRCベースゲートフィルタおよびRCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0075]残りのN−1個のFET単位セル回路176などの各々は、上記で説明したFET単位セル回路174のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路176は、それぞれ、上記で説明したFET182、ゲートフィルタキャパシタンス184、ゲートフィルタ抵抗186、第1の抵抗188および第2の抵抗190、ならびにボディフィルタキャパシタンス192と同等である、FET194、ゲートフィルタキャパシタンス196、ゲートフィルタ抵抗198、第1の抵抗200と第2の抵抗202とを備えるドレインソースバイアス回路、およびボディフィルタキャパシタンス204を含むことに留意されたい。

[0076]図9に示されているように、第7の例示的な実施形態では、スイッチスタックデバイス205は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路206〜第NのFET単位セル回路208を含む。明快のために図示されていない、第1のFET単位セル回路206と第NのFET単位セル回路208との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路206〜208の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス205は、SOI基板上か、または他の好適な様式で形成され得る。

[0077]図9に示されている例示的な実施形態では、FET単位セル回路206〜208の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路210に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路210はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス206を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路210は、1つまたは複数のバイアス電圧のソースに接続される。

[0078]FET単位セル回路206〜208の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路212に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路212は、1つまたは複数のバイアス電圧のソースに接続される。

[0079]FET単位セル回路206は、FET214と、ゲートフィルタと、ボディフィルタとを含む。ゲートフィルタは、ゲートフィルタキャパシタンス216と、ゲートフィルタ抵抗218と、ドレインソース回路とを含む。ドレインソース回路は、FET214のドレインノードとソースノードとの間に接続され、第2の抵抗222と直列の第1の抵抗220を有する抵抗性分割器回路を備える。このドレインソース回路は、第1の抵抗220と第2の抵抗222との間の仮想ノードVを定義する。ゲートフィルタキャパシタンス216およびゲートフィルタ抵抗218は、互いに直列であり、FET214のゲートノードと、仮想ノードVとの間に結合される。ボディフィルタは、FET214のボディノードと、仮想ノードVとの間に結合された(および、したがって、FET214のボディノードと、FET214のゲートノードとの間にも結合された)ボディフィルタキャパシタンス224とボディフィルタ抵抗226とを含む。

[0080]FET214のドレインノードはFET単位セル回路206のセルドレインノードを定義し、FET214のソースノードはFET単位セル回路206のセルソースノードを定義することに留意されたい。しかしながら、FET単位セル回路174のセルゲートノード(G’)は、FET214のゲートノードによってではなく、ゲートフィルタキャパシタンス216とゲートフィルタ抵抗218との間の別の仮想(ゲート)ノードによって定義される。また、FET単位セル回路206のセルボディノード(B’)は、FET214のボディノードによってではなく、ボディフィルタ抵抗226とボディフィルタキャパシタンス224との間の仮想(ボディ)ノードB’によって定義される。

[0081]FET単位セル回路206の構造は、他の実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。RCベースゲートフィルタとRCベースボディフィルタとの組合せは、上記で説明した他の実施形態におけるRCベースゲートフィルタおよびRCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0082]残りのN−1個のFET単位セル回路208などの各々は、上記で説明したFET単位セル回路206のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路208は、それぞれ、上記で説明したFET214、ゲートフィルタキャパシタンス216、ゲートフィルタ抵抗218、第1の抵抗220および第2の抵抗22、ボディフィルタキャパシタンス224、ならびにボディフィルタ抵抗226と同等である、FET228、ゲートフィルタキャパシタンス230、ゲートフィルタ抵抗232、第1の抵抗234と第2の抵抗236とを備えるドレインソースバイアス回路、ボディフィルタキャパシタンス238、およびボディフィルタ抵抗240を含むことに留意されたい。

[0083]図10に示されているように、第8の例示的な実施形態では、スイッチスタックデバイス242は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路244〜第NのFET単位セル回路246を含む。明快のために図示されていない、第1のFET単位セル回路244と第NのFET単位セル回路246との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路244〜246の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス242は、SOI基板上か、または他の好適な様式で形成され得る。

[0084]図10に示されている例示的な実施形態では、FET単位セル回路244〜246の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路248に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路248はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス248を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路248は、1つまたは複数のバイアス電圧のソースにも接続される。

[0085]FET単位セル回路244〜246の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路250に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路250は、1つまたは複数のバイアス電圧のソースに接続される。

[0086]FET単位セル回路244は、FET252と、ゲートフィルタと、ボディフィルタとを含む。ゲートフィルタは、ゲートフィルタ抵抗254とドレインソース回路とを含む。ドレインソース回路は、FET252のドレインノードとソースノードとの間に接続され、第2のキャパシタンス258と直列の第1のキャパシタンス256を有する容量性分割器回路を備える。このドレインソース回路は、第1のキャパシタンス256と第2のキャパシタンス258との間の仮想ノードVを定義する。ゲートフィルタ抵抗254は、FET252のゲートノードと、仮想ノードVとの間に結合される。ボディフィルタは、FET252のボディノードと、仮想ノードVとの間に結合された(および、したがって、FET252のボディノードと、FET252のゲートノードとの間にも結合された)ボディフィルタキャパシタンス260を含む。

[0087]FET252のドレインノードはFET単位セル回路244のセルドレインノードを定義し、FET252のソースノードはFET単位セル回路244のセルソースノードを定義し、FET252のボディノードはFET単位セル回路244のセルボディノードを定義することに留意されたい。(FET252のボディノードとFET単位セル回路244のセルボディノードとは同じノードBであるが、接続は、明快のために明示的に図示されていないことを理解されたい。)しかしながら、FET単位セル回路244のセルゲートノード(G’)は、FET252のゲートノードによってではなく、ゲートフィルタ抵抗254と仮想ノードVとの間の別の仮想(ゲート)ノードによって定義される。

[0088]FET単位セル回路244の構造は、他の実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。RCベースゲートフィルタとCベースボディフィルタとの組合せは、上記で説明した他の実施形態におけるRCベースゲートフィルタおよびCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0089]残りのN−1個のFET単位セル回路246などの各々は、上記で説明したFET単位セル回路244のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路246は、それぞれ、上記で説明したFET252、ゲートフィルタ抵抗254、第1のキャパシタンス256および第2のキャパシタンス258、ならびにボディフィルタキャパシタンス260と同等である、FET262、ゲートフィルタ抵抗264、第1のキャパシタンス266と第2のキャパシタンス268とを備えるドレインソース回路、およびボディフィルタキャパシタンス270を含むことに留意されたい。

[0090]図11に示されているように、第9の例示的な実施形態では、スイッチスタックデバイス272は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路274〜第NのFET単位セル回路276を含む。明快のために図示されていない、第1のFET単位セル回路274と第NのFET単位セル回路276との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路274〜276の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス272は、SOI基板上か、または他の好適な様式で形成され得る。

[0091]図11に示されている例示的な実施形態では、FET単位セル回路274〜276の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路278に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路278はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス272を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路278は、1つまたは複数のバイアス電圧のソースにも接続される。

[0092]FET単位セル回路274〜276の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路280に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路280は、1つまたは複数のバイアス電圧のソースに接続される。

[0093]FET単位セル回路274は、FET282と、ゲートフィルタと、ボディフィルタとを含む。ゲートフィルタは、ゲートフィルタ抵抗284とドレインソース回路とを含む。ドレインソース回路は、FET282のドレインノードとソースノードとの間に接続され、第2のキャパシタンス288と直列の第1のキャパシタンス286を有する容量性分割器回路を備える。このドレインソース回路は、第1のキャパシタンス286と第2のキャパシタンス288との間の仮想ノードVを定義する。ゲートフィルタ抵抗284は、FET282のゲートノードと、仮想ノードVとの間に結合される。ボディフィルタは、FET282のボディノードと、仮想ノードVとの間に結合された(および、したがって、FET282のボディノードと、FET282のゲートノードとの間にも結合された)ボディフィルタキャパシタンス290とボディフィルタ抵抗292とを含む。

[0094]FET282のドレインノードはFET単位セル回路274のセルドレインノードを定義し、FET282のソースノードはFET単位セル回路274のセルソースノードを定義することに留意されたい。しかしながら、FET単位セル回路274のセルゲートノード(G’)は、FET282のゲートノードによってではなく、ゲートフィルタ抵抗284と仮想ノードVとの間の別の仮想(ゲート)ノードによって定義される。また、FET単位セル回路274のセルボディノード(B’)は、FET282のボディノードによってではなく、ボディフィルタ抵抗292とボディフィルタキャパシタンス290との間の仮想(ボディ)ノードB’によって定義される。

[0095]FET単位セル回路274の構造は、他の実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。RCベースゲートフィルタとRCベースボディフィルタとの組合せは、上記で説明した他の実施形態におけるRCベースゲートフィルタおよびRCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[0096]残りのN−1個のFET単位セル回路276などの各々は、上記で説明したFET単位セル回路274のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路276は、それぞれ、上記で説明したFET282、ゲートフィルタ抵抗284、第1のキャパシタンス286および第2のキャパシタンス288、ボディフィルタキャパシタンス290、ならびにボディフィルタ抵抗292と同等である、FET294、ゲートフィルタ抵抗296、第1のキャパシタンス298と第2のキャパシタンス300とを備えるドレインソース回路、ボディフィルタキャパシタンス302、およびボディフィルタ抵抗304を含むことに留意されたい。

[0097]図12に示されているように、第10の例示的な実施形態では、スイッチスタックデバイス306は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路308〜第NのFET単位セル回路310を含む。明快のために図示されていない、第1のFET単位セル回路308と第NのFET単位セル回路310との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路308〜310の数Nは、1よりも大きい任意の数であり得る。スイッチスタックデバイス306は、SOI基板上か、または他の好適な様式で形成され得る。

[0098]図12に示されている例示的な実施形態では、FET単位セル回路308〜310の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路312に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路312はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス306を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路312は、1つまたは複数のバイアス電圧のソースにも接続される。

[0099]FET単位セル回路308〜310の各々のセルボディノードは、図13〜図17に関して以下で説明する様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路314に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。図示されていないが、ボディバイアスネットワークフィルタ回路314は、1つまたは複数のバイアス電圧のソースに接続される。

[00100]FET単位セル回路308は、2つのFET316および318を含む。さらに他の実施形態(図示せず)では、同様のFET単位セルは、3つ以上のFETを含むことができる。図12に示されているデュアルFET実施形態では、FET単位セル回路308はまた、FET316に関連付けられたゲートフィルタ、FET316に関連付けられたゲートボディフィルタ(gate-and-body filter)、およびFET316に関連付けられたボディフィルタ、ならびにFET318に関連付けられたゲートフィルタ、FET318に関連付けられたゲートボディフィルタ、およびFET318に関連付けられたボディフィルタを含む。

[00101]FET316に関連付けられたゲートフィルタは、共有ゲートフィルタキャパシタンス320とゲート抵抗322とを含む。ドレインソース回路は、FET316のドレインノードとソースノードとの間に接続された抵抗324を備える。FET316に関連付けられたゲートボディフィルタは、ゲートフィルタとボディフィルタの両方として働き、キャパシタンス326と、抵抗328と、抵抗330とを含む。FET316に関連付けられたボディフィルタは、共有キャパシタンス332と、抵抗328と、抵抗330とを含む。仮想ノードVは、キャパシタンス320とキャパシタンス332とFET316のソースノードとの間に定義される。

[00102]FET318に関連付けられたゲートフィルタは、共有ゲートフィルタキャパシタンス320とゲート抵抗334とを含む。ドレインソース回路は、FET318のドレインノードとソースノードとの間に接続された抵抗336を備える。仮想ノードVは、抵抗324と抵抗336との間にあることに留意されたい。FET318に関連付けられたゲートボディフィルタは、ゲートフィルタとボディフィルタの両方として働き、キャパシタンス338と、抵抗340と、抵抗342とを含む。FET318に関連付けられたボディフィルタは、共有キャパシタンス332と、抵抗340と、抵抗342とを含む。

[00103]FET316のドレインノードはFET単位セル回路308のセルドレインノードを定義し、FET318のソースノードはFET単位セル回路308のセルソースノードを定義することに留意されたい。FET単位セル回路308のセルゲートノード(G’)は、抵抗322と抵抗334との間の仮想(ゲート)ノードによって定義される。FET単位セル回路308のセルボディノード(B’)は、抵抗330と抵抗342との間の仮想(ボディ)ノードによって定義される。

[00104]FET単位セル回路308の構造は、他の実施形態に関して上記で説明したものと同様の様式で線形動作を促進する。2つのRCベースゲートフィルタ、および、事実上3つのRCベースボディフィルタの組合せは、上記で説明した他の実施形態におけるRCベースゲートフィルタおよびRCベースボディフィルタによって与えられる上記で説明した効果と同様である効果を与える。

[00105]残りのN−1個のFET単位セル回路310などの各々は、上記で説明したFET単位セル回路308のものと同等の構造を有するので、それらについて同様に詳細には説明しない。FET単位セル回路310は、それぞれ、上記で説明したFET316および318、ゲート抵抗322および334、ドレインソースバイアス抵抗324および336、ゲートボディフィルタキャパシタンス326および338、ならびにボディ抵抗328、330、340、および342と同等である、2つのFET344および346、ゲート抵抗350および362、ドレインソースバイアス抵抗352および364、ゲートボディフィルタキャパシタンス354および366、ならびにボディ抵抗356、358、368、および370を含むことに留意されたい。

[00106]図13に示されているように、第11の例示的な実施形態では、スイッチスタックデバイス372は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路374〜第NのFET単位セル回路380を含む。図13に示されている実施形態では、FET単位セル回路374〜380の総数Nは偶数である。したがって、FET単位セル回路374〜380の総数Nの半分(またはN/2)は、第1のFET単位セル回路374〜第(N/2)のFET単位セル回路376からなり、FET単位セル回路374〜380の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路378〜第NのFET単位セル回路380からなる。言い換えれば、第(N/2)のFET単位セル回路376および第(N/2)+1)のFET単位セル回路378は、チェーンの中央にある連続するFET単位セル回路のペアである。明快のために図示されていない、第1のFET単位セル回路374と第(N/2)のFET単位セル回路376との間の、および第((N/2)+1)のFET単位セル回路378と第NのFET単位セル回路380との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路374〜380の数Nは、1よりも大きい任意の偶数であり得る。スイッチスタックデバイス372は、SOI基板上か、または他の好適な様式で形成され得る。

[00107]FET単位セル回路374〜380は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路374〜380は従来のタイプのものであり得る。

[00108]FET単位セル回路374〜380の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路382に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路382はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス372を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路382は、1つまたは複数のバイアス電圧のソースにも接続される。

[00109]FET単位セル回路374〜380の各々のセルボディノードは、以下の様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路384に接続される。ボディバイアスネットワークフィルタ回路384は、共通ノード394に関して互いに並列のN個のボディバイアスネットワーク抵抗386〜392を含む。すなわち、ボディバイアスネットワーク抵抗386〜392の各々は、共通ノード394に接続される。ボディバイアスネットワーク抵抗386〜392の各々は、FET単位セル回路374〜380のうちの1つに対応し、FET単位セル回路374〜380のうちのその対応する1つのセルボディノードに接続される。したがって、ボディバイアスネットワーク抵抗386〜392の各々は、FET単位セル回路374〜380のうちのそれの対応する1つのセルボディノードと、共通ノード394との間に接続される。

[00110]ボディバイアスネットワークフィルタキャパシタンス396は、第(N/2)のFET単位セル回路376と第((N/2)+1)のFET単位セル回路378との間のドレインソース接続によって定義される中間ノード398に接続される。ボディバイアスネットワークフィルタキャパシタンス396は、中間ノード398と共通ノード394との間に接続される。したがって、ボディバイアスネットワークフィルタキャパシタンス396は、共通ノード394を介して、中間ノード398と、FET単位セル回路374〜380の各々のセルボディノードとの間に結合される。共通ノード394は、共通抵抗400を介して、ボディバイアス電圧(「V_BIAS」)ノードに結合される。

[00111]ボディバイアスネットワークフィルタキャパシタンス396は、FET単位セル回路374〜380の各々のセルボディノード電圧をフィルタ処理するCベースフィルタを定義する。したがって、このCベースボディバイアスネットワークフィルタ回路384は、スイッチスタックデバイス372の線形動作を促進する。

[00112]図14に示されているように、第12の例示的な実施形態では、スイッチスタックデバイス402は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路404〜第NのFET単位セル回路410を含む。図14に示されている実施形態では、FET単位セル回路404〜410の総数Nは偶数である。したがって、FET単位セル回路404〜410の総数Nの半分(またはN/2)は、第1のFET単位セル回路404〜第(N/2)のFET単位セル回路406からなり、FET単位セル回路404〜410の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路408〜第NのFET単位セル回路410からなる。言い換えれば、第(N/2)のFET単位セル回路406および第((N/2)+1)のFET単位セル回路408は、チェーンの中央にある連続するFET単位セル回路のペアである。明快のために図示されていない、第1のFET単位セル回路404と第(N/2)のFET単位セル回路406との間の、および第((N/2)+1)のFET単位セル回路408と第NのFET単位セル回路410との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路404〜410の数Nは、1よりも大きい任意の偶数であり得る。

[00113]FET単位セル回路404〜410は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路404〜410は従来のタイプのものであり得る。スイッチスタックデバイス402は、SOI基板上か、または他の好適な様式で形成され得る。

[00114]FET単位セル回路404〜410の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路412に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路412はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス402を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路412は、1つまたは複数のバイアス電圧のソースにも接続される。

[00115]FET単位セル回路404〜410の各々のセルボディノードは、以下の様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路414に接続される。ボディバイアスネットワークフィルタ回路414は、共通ノード424に関して互いに並列のN個のボディバイアスネットワーク抵抗416〜422を含む。すなわち、ボディバイアスネットワーク抵抗416〜422の各々は、共通ノード424に接続される。ボディバイアスネットワークフィルタ抵抗416〜422の各々は、FET単位セル回路404〜410のうちの1つに対応し、FET単位セル回路404〜410のうちのその対応する1つのセルボディノードに接続される。したがって、ボディバイアスネットワーク抵抗416〜422の各々は、FET単位セル回路404〜410のうちのそれの対応する1つのセルボディノードと、共通ノード424との間に接続される。

[00116]ボディバイアスネットワークフィルタ回路414はまた、ボディバイアスネットワークフィルタキャパシタンス426とボディバイアスネットワークフィルタ共通抵抗430とを含む。ボディバイアスネットワークフィルタキャパシタンス426は、第(N/2)のFET単位セル回路406と第((N/2)+1)のFET単位セル回路408との間のドレインソース接続によって定義される中間ノード428に接続される。ボディバイアスネットワークフィルタキャパシタンス426は、ボディバイアスネットワークフィルタ共通抵抗430を介して、共通ノード424に結合される。したがって、ボディバイアスネットワークフィルタキャパシタンス426およびボディバイアスネットワークフィルタ共通抵抗430は、互いに直列であり、共通ノード424を介して、中間ノード428と、FET単位セル回路404〜410の各々のセルボディノードとの間に結合される。共通抵抗432は、ボディバイアスネットワークフィルタキャパシタンス426とボディバイアスネットワークフィルタ共通抵抗430との間のノード434にボディバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード424は、抵抗430および抵抗432を介して、V_BIASノードに結合される。

[00117]ボディバイアスネットワークフィルタキャパシタンス426およびボディバイアスネットワークフィルタ共通抵抗430は、一緒に、FET単位セル回路404〜410の各々のセルボディノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースボディバイアスネットワークフィルタ回路414は、したがって、スイッチスタックデバイス402の線形動作を促進する。

[00118]図15に示されているように、第13の例示的な実施形態では、スイッチスタックデバイス436は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路438〜第NのFET単位セル回路446を含む。したがって、チェーンは、第2のFET単位セル回路440のセルドレインノードに接続された第1のFET単位セル回路438のセルソースノードから始まり、第NのFET単位セル回路446のセルドレインノードに接続された第(N−1)のFET単位セル回路444のセルソースノードまで続く。図15に示されている実施形態では、FET単位セル回路438〜446の総数Nは奇数である。したがって、第((N+1)/2)のFET単位セル回路442は、チェーンの中央にある。明快のために図示されていない、第2のFET単位セル回路440と第((N+1)/2)のFET単位セル回路442との間の、および第((N+1)/2)のFET単位セル回路442と第(N−1)のFET単位セル回路444との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路438〜446の数Nは、1よりも大きい任意の奇数であり得る。スイッチスタックデバイス436は、SOI基板上か、または他の好適な様式で形成され得る。

[00119]FET単位セル回路438〜446は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路438〜446は従来のタイプのものであり得る。

[00120]FET単位セル回路438〜446の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路448に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路448はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス436を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路448は、1つまたは複数のバイアス電圧のソースにも接続される。

[00121]FET単位セル回路438〜446の各々のセルボディノードは、以下の様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路450に接続される。ボディバイアスネットワークフィルタ回路450は、共通ノード462に関して互いに並列のN個のボディバイアスネットワーク抵抗452〜460を含む。すなわち、ボディバイアスネットワーク抵抗452〜460の各々は、共通ノード462に接続される。ボディバイアスネットワーク抵抗452〜460の各々は、FET単位セル回路438〜446のうちの1つに対応し、FET単位セル回路438〜446のうちのその対応する1つのセルボディノードに接続される。したがって、第1のボディバイアスネットワーク抵抗452は、第1のFET単位セル回路438のセルボディノードに接続され、第2のボディバイアスネットワーク抵抗454は、第2のFET単位セル回路440のセルボディノードに接続され、以下、第((N+1)/2)のFET単位セル回路442のセルボディノードに接続された第((N+1)/2)のボディバイアスネットワーク抵抗456まで同様であり、以下、FET単位セル回路444のセルボディノードに接続された第(N−1)のボディバイアス抵抗458まで同様であり、最後に、第NのFET単位セル回路446のセルボディノードに接続された第Nのボディバイアスネットワーク抵抗460である。ボディバイアスネットワーク抵抗452〜460の各々は、FET単位セル回路438〜446のうちのそれの対応する1つのセルボディノードと、共通ノード462との間に接続される。

[00122]ボディバイアスネットワークフィルタ回路450はまた、互いに直列に接続されたN+1個のドレインソース抵抗464〜474を含む。ドレインソース抵抗464〜474の各々は、FET単位セル回路438〜446のうちの1つに対応し、FET単位セル回路438〜446のうちのそれの対応する1つのセルドレインノードとセルソースノードとの間に接続される。したがって、第1のドレインソース抵抗464は、FET単位セル回路438のセルドレインノードとセルソースノードとの間に接続され、第2のドレインソース抵抗466は、第2のFET単位セル回路440のセルドレインノードとセルソースノードとの間に接続され、以下、第(N−1)のFET単位セル回路444のセルドレインノードとセルソースノードとの間に接続された第Nのドレインソース抵抗472まで同様であり、最後に、第NのFET単位セル回路446のセルドレインノードとセルソースノードとの間に接続された第(N+1)のドレインソース抵抗474である。この実施形態では、中間ノード476(すなわち、仮想ノードV)は、第((N+1)/2)のドレインソース抵抗468と第((N+1)/2+1)のドレインソース抵抗470との間に定義される。第((N+1)/2)のドレインソース抵抗468および第((N+1)/2+1)のドレインソース抵抗470は、互いに直列であり、チェーンの中央の第((N+1)/2)のFET単位セル回路442のセルドレインノードとセルソースノードとの間に接続される。第((N+1)/2)のドレインソース抵抗468および第((N+1)/2+1)のドレインソース抵抗470は、両方とも、第((N+1)/2)のFET単位セル回路442に対応する。言い換えれば、直列のドレインソース抵抗468およびドレインソース抵抗470によって接続された第((N+1)/2)のFET単位セル回路442のセルドレインノードおよびセルソースノードを除いて、各対応するFET単位セル回路のセルドレインノードとセルソースノードとの間に、単一のドレインソース抵抗のみが接続される。中間ノード476も、第((N+1)/2)のFET単位セル回路442のセルドレインノードとセルソースノードとの間にあることに留意されたい。また、中間ノード476は、ドレインソース抵抗のうちの(N+1)/2個の第1の直列接続グループ464〜468と、ドレインソース抵抗のうちの(N+1)/2個の第2の直列接続グループ470〜474との間にあることに留意されたい。

[00123]ボディバイアスネットワークフィルタ回路450はまた、ボディバイアスネットワークフィルタキャパシタンス478とボディバイアスネットワークフィルタ共通抵抗480とを含む。ボディバイアスネットワークフィルタキャパシタンス478は、中間ノード476に接続され、ボディバイアスネットワークフィルタ共通抵抗480を介して、共通ノード462に結合される。したがって、ボディバイアスネットワークフィルタキャパシタンス478およびボディバイアスネットワークフィルタ共通抵抗480は、互いに直列であり、共通ノード476を介して、中間ノード476と、FET単位セル回路438〜446の各々のセルボディノードとの間に結合される。共通抵抗482は、ボディバイアスネットワークフィルタキャパシタンス478とボディバイアスネットワークフィルタ共通抵抗480との間のノード484にボディバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード462は、抵抗480および抵抗482を介して、V_BIASノードに結合される。

[00124]ボディバイアスネットワークフィルタキャパシタンス478およびボディバイアスネットワークフィルタ共通抵抗480は、一緒に、FET単位セル回路438〜446の各々のセルボディノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースボディバイアスネットワークフィルタ回路450は、したがって、スイッチスタックデバイス436の線形動作を促進する。

[00125]図16に示されているように、第14の例示的な実施形態では、スイッチスタックデバイス486は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路488〜第NのFET単位セル回路496を含む。図16に示されている実施形態では、FET単位セル回路488〜496の総数Nは偶数である。したがって、FET単位セル回路488〜496の総数Nの半分(またはN/2)は、第1のFET単位セル回路488、第2のFET単位セル回路490など〜第(N/2)のFET単位セル回路492からなり、FET単位セル回路488〜496の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路494〜第NのFET単位セル回路496からなる。言い換えれば、第(N/2)のFET単位セル回路492および第((N/2)+1)のFET単位セル回路494は、チェーンの中央にある連続するFET単位セル回路のペアである。中間ノード498は、第(N/2)のFET単位セル回路492のセルソースノードと、第((N/2)+1)のFET単位セル回路494のセルドレインノードとの間のドレインソース接続によって定義される。明快のために図示されていない、第2のFET単位セル回路490と第(N/2)のFET単位セル回路492との間の、および第((N/2)+1)のFET単位セル回路494と第NのFET単位セル回路496との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路488〜496の数Nは、1よりも大きい任意の偶数であり得る。スイッチスタックデバイス486は、SOI基板上か、または他の好適な様式で形成され得る。

[00126]FET単位セル回路488〜496は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路488〜496は従来のタイプのものであり得る。

[00127]FET単位セル回路488〜496の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路500に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路500はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス486を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路486は、1つまたは複数のバイアス電圧のソースにも接続される。

[00128]FET単位セル回路488〜496の各々のセルボディノードは、以下の様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路502に接続される。ボディバイアスネットワークフィルタ回路502は、互いに直列のN個のボディバイアスネットワーク抵抗504〜510を含む。ボディバイアスネットワーク抵抗504〜510の各々は、チェーン中の連続するFET単位セル回路のペアのボディノード間に結合される。たとえば、第1のボディバイアスネットワーク抵抗504は、第1のFET単位セル回路488のセルボディノードと第2のFET単位セル回路490のセルボディノードとの間に接続される。この実施形態では、共通ノード512(すなわち、仮想ノードV)は、第(N/2)のボディバイアスネットワーク抵抗506と第((N/2)+1)のボディバイアスネットワーク抵抗508との間に定義される。第(N/2)のボディバイアスネットワーク抵抗506および第((N/2)+1)のボディバイアスネットワーク抵抗508は、互いに直列であり、第(N/2)のFET単位セル回路492のセルボディノードと、第((N/2)+1)のFET単位セル回路494のセルボディノードとの間に接続される。直列のボディバイアスネットワーク抵抗506およびボディバイアスネットワーク抵抗508によって接続された、第(N/2)のFET単位セル回路492および第((N/2)+1)のFET単位セル回路494からなる連続するFET単位回路セルペアを除いて、各連続するFET単位セル回路ペア間に、単一のボディバイアスネットワーク抵抗のみが接続される。共通ノード512は、ボディバイアスネットワーク抵抗のうちのN/2個の第1の直列接続グループ504〜506と、ボディバイアスネットワーク抵抗のうちのN/2個の第2の直列接続グループ508〜510との間にあることに留意されたい。

[00129]ボディバイアスネットワークフィルタ回路502はまた、ボディバイアスネットワークフィルタキャパシタンス514とボディバイアスネットワーク共通抵抗516とを含む。ボディバイアスネットワークフィルタキャパシタンス514は、ボディバイアスネットワークフィルタ共通抵抗516を介して、中間ノード498と共通ノード512との間に結合される。したがって、ボディバイアスネットワークフィルタキャパシタンス514およびボディバイアスネットワーク共通抵抗516は、互いに直列であり、共通ノード512を介して、中間ノード498と、FET単位セル回路488〜496の各々のセルボディノードとの間に結合される。共通抵抗518は、ボディバイアスネットワークフィルタキャパシタンス514とボディバイアスネットワーク共通抵抗516との間のノード520にボディバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード512は、抵抗516および抵抗518を介して、V_BIASノードに結合される。

[00130]ボディバイアスネットワークフィルタキャパシタンス514およびボディバイアスネットワーク共通抵抗516は、一緒に、FET単位セル回路488〜496の各々のセルボディノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースボディバイアスネットワークフィルタ回路502は、したがって、スイッチスタックデバイス486の線形動作を促進する。

[00131]図17に示されているように、第15の例示的な実施形態では、スイッチスタックデバイス522は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路524〜第NのFET単位セル回路532を含む。したがって、チェーンは、第2のFET単位セル回路526のセルドレインノードに接続された第1のFET単位セル回路524のセルソースノードから始まり、第NのFET単位セル回路532のセルドレインノードに接続された第(N−1)のFET単位セル回路530のセルソースノードまで続く。図17に示されている実施形態では、FET単位セル回路524〜532の総数Nは奇数である。したがって、第((N+1)/2)のFET単位セル回路528は、チェーンの中央にある。明快のために図示されていない、第2のFET単位セル回路526と第((N+1)/2)のFET単位セル回路528との間の、および第((N+1)/2)のFET単位セル回路528と第(N−1)のFET単位セル回路530との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路524〜532の数Nは、1よりも大きい任意の奇数であり得る。スイッチスタックデバイス522は、SOI基板上か、または他の好適な様式で形成され得る。

[00132]FET単位セル回路524〜532は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路524〜532は従来のタイプのものであり得る。

[00133]FET単位セル回路524〜532の各々のセルゲートノードは、図18〜図22に関して以下で説明する様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路534に接続される。しかしながら、他の実施形態(図示せず)では、そのようなFET単位セル回路のセルゲートノードは、フィルタ処理を行わないものなど、他のタイプのゲートバイアスネットワークに接続され得る。ゲートバイアスネットワークフィルタ回路534はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス522を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。図示されていないが、ゲートバイアスネットワークフィルタ回路534は、1つまたは複数のバイアス電圧のソースにも接続される。

[00134]FET単位セル回路524〜532の各々のセルボディノードは、以下の様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路536に接続される。ボディバイアスネットワークフィルタ回路536は、互いに直列のN個のボディバイアスネットワーク抵抗538〜540を含む。ボディバイアスネットワーク抵抗538〜540の各々は、チェーン中の連続するFET単位セル回路のペアのボディノード間に結合される。たとえば、第1のボディバイアスネットワーク抵抗538は、第1のFET単位セル回路524のセルボディノードと、第2のFET単位セル回路526のセルボディノードとの間に接続され、第Nのボディバイアスネットワーク抵抗540は、第(N−1)のFET単位セル回路530のセルボディノードと、第NのFET単位セル回路532のセルボディノードとの間に接続される。この実施形態では、共通ノード542は、チェーンの中央の第((N+1)/2)のFET単位セル回路528のセルボディノードによって定義される。共通ノード542は、したがって、ボディバイアスネットワーク抵抗のうちの(N−1)/2個の第1の直列接続グループと、ボディバイアスネットワーク抵抗のうちの(N−1)/2個の第2の直列接続グループとの間にある。

[00135]ボディバイアスネットワークフィルタ回路536はまた、互いに直列に接続されたN+1個のドレインソース抵抗544〜554を含む。ドレインソース抵抗544〜554の各々は、FET単位セル回路524〜532のうちの1つに対応し、FET単位セル回路524〜532のうちのそれの対応する1つのセルドレインノードとセルソースノードとの間に接続される。したがって、たとえば、第1のドレインソース抵抗544は、FET単位セル回路524のセルドレインノードとセルソースノードとの間に接続され、第2のドレインソース抵抗546は、第2のFET単位セル回路526のセルドレインノードとセルソースノードとの間に接続され、以下、第(N−1)のFET単位セル回路530のセルドレインノードとセルソースノードとの間に接続された第Nのドレインソース抵抗552まで同様であり、最後に、第NのFET単位セル回路532のセルドレインノードとセルソースノードとの間に接続された第(N+1)のドレインソース抵抗554である。この実施形態では、中間ノード556(すなわち、仮想ノードV)は、第((N+1)/2)のドレインソース抵抗548と第((N+1)/2)+1)のドレインソース抵抗550との間に定義される。第((N+1)/2)のドレインソース抵抗548および第((N+1)/2)+1)のドレインソース抵抗550は、互いに直列であり、チェーンの中央の第((N+1)/2)のFET単位セル回路528のセルドレインノードとセルソースノードとの間に接続される。第(N/2)のドレインソース抵抗548および第((N+1)/2)+1)のドレインソース抵抗550は、両方とも、第((N+1)/2)のFET単位セル回路528に対応する。言い換えれば、直列のドレインソース抵抗548およびドレインソース抵抗550によって接続されたFET単位セル回路528のセルドレインノードおよびセルソースノードを除いて、各対応するFET単位セル回路のセルドレインノードとセルソースノードとの間に、単一のドレインソース抵抗のみが接続される。中間ノード556も、第((N+1)/2)のFET単位セル回路528のセルドレインノードとセルソースノードとの間にあることに留意されたい。また、中間ノード556は、ドレインソース抵抗のうちの(N+1)/2個の第1の直列接続グループ544〜548と、ドレインソース抵抗のうちの(N+1)/2個の第2の直列接続グループ550〜554との間にあることに留意されたい。

[00136]ボディバイアスネットワークフィルタ回路536はまた、ボディバイアスネットワークフィルタキャパシタンス558とボディバイアスネットワーク共通抵抗560とを含む。ボディバイアスネットワークフィルタキャパシタンス558は、中間ノード556に接続され、ボディバイアスネットワーク共通抵抗560を介して、共通ノード542に結合される。したがって、ボディバイアスネットワークフィルタキャパシタンス558およびボディバイアスネットワークフィルタ共通抵抗560は、互いに直列であり、共通ノード542を介して、中間ノード556と、FET単位セル回路524〜532の各々のセルボディノードとの間に結合される。共通抵抗562は、ボディバイアスネットワークフィルタキャパシタンス558とボディバイアスネットワーク共通抵抗560との間のノード564にボディバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード542は、抵抗560および抵抗562を介して、V_BIASノードに結合される。

[00137]ボディバイアスネットワークフィルタキャパシタンス558およびボディバイアスネットワークフィルタ共通抵抗560は、一緒に、FET単位セル回路524〜532の各々のセルボディノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースボディバイアスネットワークフィルタ回路536は、したがって、スイッチスタックデバイス522の線形動作を促進する。

[00138]図18に示されているように、第16の例示的な実施形態では、スイッチスタックデバイス566は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路568〜第NのFET単位セル回路574を含む。図18に示されている実施形態では、FET単位セル回路568〜574の総数Nは偶数である。したがって、FET単位セル回路568〜574の総数Nの半分(またはN/2)は、第1のFET単位セル回路568〜第(N/2)のFET単位セル回路570からなり、FET単位セル回路568〜574の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路572〜第NのFET単位セル回路574からなる。言い換えれば、第(N/2)のFET単位セル回路570および第(N/2)+1)のFET単位セル回路572は、チェーンの中央にある連続するFET単位セル回路のペアである。明快のために図示されていない、第1のFET単位セル回路568と第(N/2)のFET単位セル回路570との間の、および第((N/2)+1)のFET単位セル回路572と第NのFET単位セル回路574との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路568〜574の数Nは、1よりも大きい任意の偶数であり得る。

[00139]FET単位セル回路568〜574は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路568〜574は従来のタイプのものであり得る。スイッチスタックデバイス566は、SOI基板上か、または他の好適な様式で形成され得る。

[00140]FET単位セル回路568〜574の各々のセルボディノードは、図13〜図17に関して上記で説明した様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路576に接続される。すなわち、ボディバイアスネットワークフィルタ回路576は、上記で説明したボディバイアスネットワークフィルタ回路384、414、450、502および536のいずれかを備えることができる。さらに他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。

[00141]FET単位セル回路568〜574の各々のセルゲートノードは、以下の様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路578に接続される。ゲートバイアスネットワークフィルタ回路578は、共通ノード588に関して互いに並列のN個のゲートバイアスネットワーク抵抗580〜586を含む。すなわち、ゲートバイアスネットワーク抵抗580〜586の各々は、共通ノード588に接続される。ゲートバイアスネットワーク抵抗580〜586の各々は、FET単位セル回路568〜574のうちの1つに対応し、FET単位セル回路568〜574のうちのその対応する1つのセルゲートノードに接続される。したがって、ゲートバイアスネットワーク抵抗580〜586の各々は、FET単位セル回路568〜574のうちのそれの対応する1つのセルゲートノードと、共通ノード588との間に接続される。

[00142]ゲートバイアスネットワークフィルタキャパシタンス590は、第(N/2)のFET単位セル回路570と第((N/2)+1)のFET単位セル回路572との間のドレインソース接続によって定義される中間ノード592に接続される。ゲートバイアスネットワークフィルタキャパシタンス590は、中間ノード592と共通ノード588との間に接続される。したがって、ゲートバイアスネットワークフィルタキャパシタンス590は、共通ノード588を介して、中間ノード592と、FET単位セル回路568〜574の各々のセルゲートノードとの間に結合される。共通ノード588は、共通抵抗594を介して、ゲートバイアス電圧(「V_BIAS」)ノードに結合される。

[00143]ゲートバイアスネットワークフィルタ回路578はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス566を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。

[00144]ゲートバイアスネットワークフィルタキャパシタンス590は、FET単位セル回路568〜574の各々のセルゲートノード電圧をフィルタ処理するキャパシタンスベースまたはCベースフィルタを定義する。したがって、このCベースゲートバイアスネットワークフィルタ回路578は、スイッチスタックデバイス566の線形動作を促進する。

[00145]図19に示されているように、第17の例示的な実施形態では、スイッチスタックデバイス596は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路598〜第NのFET単位セル回路604を含む。図19に示されている実施形態では、FET単位セル回路598〜604の総数Nは偶数である。したがって、FET単位セル回路598〜604の総数Nの半分(またはN/2)は、第1のFET単位セル回路598〜第(N/2)のFET単位セル回路600からなり、FET単位セル回路598〜604の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路602〜第NのFET単位セル回路604からなる。言い換えれば、第(N/2)のFET単位セル回路600および第((N/2)+1)のFET単位セル回路602は、チェーンの中央にある連続するFET単位セル回路のペアである。明快のために図示されていない、第1のFET単位セル回路598と第(N/2)のFET単位セル回路600との間の、および第((N/2)+1)のFET単位セル回路602と第NのFET単位セル回路604との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路598〜604の数Nは、1よりも大きい任意の偶数であり得る。スイッチスタックデバイス596は、SOI基板上か、または他の好適な様式で形成され得る。

[00146]FET単位セル回路598〜604は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路598〜604は従来のタイプのものであり得る。

[00147]FET単位セル回路598〜604の各々のセルボディノードは、図13〜図17に関して上記で説明した様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路606に接続される。すなわち、ボディバイアスネットワークフィルタ回路608は、上記で説明したボディバイアスネットワークフィルタ回路384、414、450、502および536のいずれかを備えることができる。さらに他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。

[00148]FET単位セル回路598〜604の各々のセルゲートノードは、以下の様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路608に接続される。ゲートバイアスネットワークフィルタ回路608は、共通ノード618に関して互いに並列のN個のゲートバイアスネットワーク抵抗610〜616を含む。すなわち、ゲートバイアスネットワーク抵抗610〜616の各々は、共通ノード618に接続される。ゲートバイアスネットワーク抵抗610〜616の各々は、FET単位セル回路598〜604のうちの1つに対応し、FET単位セル回路598〜604のうちのその対応する1つのセルゲートノードに接続される。したがって、ゲートバイアスネットワーク抵抗610〜616の各々は、FET単位セル回路598〜604のうちのそれの対応する1つのセルゲートノードと、共通ノード618との間に接続される。

[00149]ゲートバイアスネットワークフィルタ回路608はまた、ゲートバイアスネットワークフィルタキャパシタンス620とゲートバイアスネットワーク共通抵抗622とを含む。ゲートバイアスネットワークフィルタキャパシタンス620は、第(N/2)のFET単位セル回路600と第((N/2)+1)のFET単位セル回路602との間のドレインソース接続によって定義される中間ノード624に接続される。ゲートバイアスネットワークフィルタキャパシタンス620は、ゲートバイアスネットワークフィルタ共通抵抗622を介して、共通ノード618に結合される。したがって、ゲートバイアスネットワークフィルタキャパシタンス620およびゲートバイアスネットワーク共通抵抗622は、互いに直列であり、共通ノード618を介して、中間ノード624と、FET単位セル回路598〜604の各々のセルゲートノードとの間に結合される。共通抵抗626は、ゲートバイアスネットワークフィルタキャパシタンス620とゲートバイアスネットワーク共通抵抗622との間のノード628にゲートバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード618は、抵抗622および抵抗626を介して、V_BIASノードに結合される。

[00150]ゲートバイアスネットワークフィルタ回路608はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス596を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。

[00151]ゲートバイアスネットワークフィルタキャパシタンス620およびゲートバイアスネットワークフィルタ共通抵抗622は、一緒に、FET単位セル回路598〜604の各々のセルボディノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースゲートバイアスネットワークフィルタ回路608は、したがって、スイッチスタックデバイス596の線形動作を促進する。

[00152]図20に示されているように、第18の例示的な実施形態では、スイッチスタックデバイス630は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路632〜第NのFET単位セル回路640を含む。したがって、チェーンは、第2のFET単位セル回路634のセルドレインノードに接続された第1のFET単位セル回路632のセルソースノードから始まり、第NのFET単位セル回路640のセルドレインノードに接続された第(N−1)のFET単位セル回路638のセルソースノードまで続く。図20に示されている実施形態では、FET単位セル回路632〜640の総数Nは奇数である。したがって、第((N+1)/2)のFET単位セル回路636は、チェーンの中央にある。明快のために図示されていない、第2のFET単位セル回路634と第((N+1)/2)のFET単位セル回路636との間の、および第((N+1)/2)のFET単位セル回路636と第(N−1)のFET単位セル回路638との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路632〜640の数Nは、1よりも大きい任意の奇数であり得る。スイッチスタックデバイス630は、SOI基板上か、または他の好適な様式で形成され得る。

[00153]FET単位セル回路632〜640は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路632〜640は従来のタイプのものであり得る。

[00154]FET単位セル回路438〜446の各々のセルボディは、図13〜図17に関して上記で説明した様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路642に接続される。すなわち、ボディバイアスネットワークフィルタ回路642は、上記で説明したボディバイアスネットワークフィルタ回路384、414、450、502および536のいずれかを備えることができる。さらに他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。

[00155]FET単位セル回路632〜640の各々のセルゲートノードは、以下の様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路644に接続される。ゲートバイアスネットワークフィルタ回路644は、共通ノード676に関して互いに並列のN個のゲートバイアスネットワーク抵抗646〜654を含む。すなわち、ゲートバイアスネットワーク抵抗646〜654の各々は、共通ノード676に接続される。ゲートバイアスネットワーク抵抗646〜654の各々は、FET単位セル回路632〜640のうちの1つに対応し、FET単位セル回路632〜640のうちのその対応する1つのセルゲートノードに接続される。したがって、第1のゲートバイアスネットワーク抵抗646は、第1のFET単位セル回路632のセルゲートノードに接続され、第2のゲートバイアスネットワーク抵抗648は、第2のFET単位セル回路634のセルゲートノードに接続され、以下、第((N+1)/2)のFET単位セル回路636のセルゲートノードに接続された第((N+1)/2)のゲートバイアスネットワーク抵抗650まで同様であり、以下、第(N−1)のFET単位セル回路638のセルゲートノードに接続された第(N−1)のゲートバイアスネットワーク抵抗652まで同様であり、最後に、第NのFET単位セル回路640のセルゲートノードに接続された第Nのゲートバイアスネットワーク抵抗654である。ゲートバイアスネットワーク抵抗646〜654の各々は、FET単位セル回路632〜640のうちのそれの対応する1つのセルゲートノードと、共通ノード676との間に接続される。

[00156]ゲートバイアスネットワークフィルタ回路644はまた、互いに直列に接続されたN+1個のドレインソース抵抗656〜666を含む。ドレインソース抵抗656〜666の各々は、FET単位セル回路632〜640のうちの1つに対応し、FET単位セル回路632〜640のうちのそれの対応する1つのセルドレインノードとセルソースノードとの間に接続される。したがって、第1のドレインソース抵抗656は、FET単位セル回路632のセルドレインノードとセルソースノードとの間に接続され、第2のドレインソース抵抗658は、第2のFET単位セル回路634のセルドレインノードとセルソースノードとの間に接続され、以下、第(N−1)のFET単位セル回路638のセルドレインノードとセルソースノードとの間に接続された第Nのドレインソース抵抗664まで同様であり、最後に、第NのFET単位セル回路640のセルドレインノードとセルソースノードとの間に接続された第(N+1)のドレインソース抵抗666である。この実施形態では、中間ノード668(すなわち、仮想ノードV)は、第(N/2)のドレインソース抵抗660と第((N/2)+1)のドレインソース抵抗662との間に定義される。第(N/2)のドレインソース抵抗660および第((N/2)+1)のドレインソース抵抗662は、互いに直列であり、チェーンの中央の第((N+1)/2)のFET単位セル回路636のセルドレインノードとセルソースノードとの間に接続される。第(N/2)のドレインソース抵抗660および第((N+1)/2+1)のドレインソース抵抗662は、両方とも、第((N+1)/2)のFET単位セル回路636に対応する。言い換えれば、直列のドレインソース抵抗660およびドレインソース抵抗662によって接続された第((N+1)/2)のFET単位セル回路636のセルドレインノードおよびセルソースノードを除いて、各対応するFET単位セル回路のセルドレインノードとセルソースノードとの間に、単一のドレインソース抵抗のみが接続される。中間ノード668も、第((N+1)/2)のFET単位セル回路636のセルドレインノードとセルソースノードとの間にあることに留意されたい。また、中間ノード668は、ドレインソース抵抗のうちの(N+1)/2個の第1の直列接続グループ656〜660と、ドレインソース抵抗のうちの(N+1)/2個の第2の直列接続グループ662〜666との間にあることに留意されたい。

[00157]ゲートバイアスネットワークフィルタ回路644はまた、ゲートバイアスネットワークフィルタキャパシタンス670とゲートバイアスネットワーク共通抵抗672とを含む。ゲートバイアスネットワークフィルタキャパシタンス670は、中間ノード668に接続され、ゲートバイアスネットワーク共通抵抗672を介して、共通ノード656に結合される。したがって、ゲートバイアスネットワークフィルタキャパシタンス670およびゲートバイアスネットワーク共通抵抗672は、互いに直列であり、共通ノード656を介して、中間ノード668と、FET単位セル回路632〜640の各々のセルゲートノードとの間に結合される。共通抵抗674は、ゲートバイアスネットワークフィルタキャパシタンス670とゲートバイアスネットワーク共通抵抗672との間のノード676にゲートバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード656は、抵抗672および抵抗674を介して、V_BIASノードに結合される。

[00158]ゲートバイアスネットワークフィルタ回路644はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス630を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。

[00159]ゲートバイアスネットワークフィルタキャパシタンス670およびゲートバイアスネットワークフィルタ共通抵抗672は、一緒に、FET単位セル回路632〜640の各々のセルゲートノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースゲートバイアスネットワークフィルタ回路644は、したがって、スイッチスタックデバイス630の線形動作を促進する。

[00160]図21に示されているように、第19の例示的な実施形態では、スイッチスタックデバイス678は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路680〜第NのFET単位セル回路688を含む。図21に示されている実施形態では、FET単位セル回路680〜688の総数Nは偶数である。したがって、FET単位セル回路680〜688の総数Nの半分(またはN/2)は、第1のFET単位セル回路680、第2のFET単位セル回路682など〜第(N/2)のFET単位セル回路684からなり、FET単位セル回路680〜688の総数Nの他方の半分(またはN/2)は、第((N/2)+1)のFET単位セル回路686〜第NのFET単位セル回路688からなる。言い換えれば、第(N/2)のFET単位セル回路684および第((N/2)+1)のFET単位セル回路686は、チェーンの中央にある連続するFET単位セル回路のペアである。中間ノード690は、第(N/2)のFET単位セル回路684のセルソースノードと、第((N/2)+1)のFET単位セル回路686のセルドレインノードとの間のドレインソース接続によって定義される。明快のために図示されていない、第2のFET単位セル回路682と第(N/2)のFET単位セル回路684との間の、および第((N/2)+1)のFET単位セル回路686と第NのFET単位セル回路688との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路680〜688の数Nは、1よりも大きい任意の偶数であり得る。スイッチスタックデバイス678は、SOI基板上か、または他の好適な様式で形成され得る。

[00161]FET単位セル回路680〜688は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路680〜688は従来のタイプのものであり得る。

[00162]FET単位セル回路680〜688の各々のセルボディノードは、図13〜図17に関して上記で説明した様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路692に接続される。すなわち、ボディバイアスネットワークフィルタ回路692は、上記で説明したボディバイアスネットワークフィルタ回路384、414、450、502および536のいずれかを備えることができる。さらに他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。

[00163]FET単位セル回路680〜688の各々のセルゲートノードは、以下の様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路694に接続される。ゲートバイアスネットワークフィルタ回路694は、互いに直列のN個のゲートバイアスネットワーク抵抗696〜702を含む。ゲートバイアスネットワーク抵抗696〜702の各々は、チェーン中の連続するFET単位セル回路のペアのセルゲートノード間に結合される。たとえば、第1のゲートバイアスネットワーク抵抗696は、第1のFET単位セル回路680のセルゲートノードと第2のFET単位セル回路682のセルゲートノードとの間に接続される。この実施形態では、共通ノード704(すなわち、仮想ノードV)は、第(N/2)のゲートバイアスネットワーク抵抗698と第((N/2)+1)のゲートバイアスネットワーク抵抗700との間に定義される。第(N/2)のゲートバイアスネットワーク抵抗698および第((N/2)+1)のゲートバイアスネットワーク抵抗700は、互いに直列であり、第(N/2)のFET単位セル回路684のセルゲートノードと、第((N/2)+1)のFET単位セル回路686との間に接続される。直列のゲートバイアスネットワーク抵抗698およびゲートバイアスネットワーク抵抗700によって接続された、第(N/2)のFET単位セル回路684および第((N/2)+1)のFET単位セル回路686からなる連続するFET単位セル回路ペアを除いて、各連続するFET単位セル回路ペア間に、単一のゲートバイアスネットワーク抵抗のみが接続される。共通ノード704は、ゲートバイアスネットワーク抵抗のうちのN/2個の第1の直列接続グループ696〜698と、ゲートバイアスネットワーク抵抗のうちのN/2個の第2の直列接続グループ700〜702との間にあることに留意されたい。

[00164]ゲートバイアスネットワークフィルタ回路694はまた、ゲートバイアスネットワークフィルタキャパシタンス706を含む。ゲートバイアスネットワークフィルタキャパシタンス706は、中間ノード690と共通ノード704との間に結合される。共通抵抗708は、抵抗698と抵抗700との間の共通ノード704と、ゲートバイアスネットワークフィルタキャパシタンス706とにゲートバイアス電圧(「V_BIAS」)ノードを結合する。

[00165]ゲートバイアスネットワークフィルタ回路694はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス678を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。

[00166]ゲートバイアスネットワークフィルタキャパシタンス706および抵抗698および抵抗700は、一緒に、FET単位セル回路680〜688の各々のセルゲートノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースゲートバイアスネットワークフィルタ回路694は、したがって、スイッチスタックデバイス678の線形動作を促進する。

[00167]図22に示されているように、第20の例示的な実施形態では、スイッチスタックデバイス710は、他の実施形態に関して上記で説明したのと同じ様式でスタックまたはチェーントポロジーで接続された、第1のFET単位セル回路712〜第NのFET単位セル回路720を含む。したがって、チェーンは、第2のFET単位セル回路714のセルドレインノードに接続された第1のFET単位セル回路712のセルソースノードから始まり、第NのFET単位セル回路720のセルドレインノードに接続された第(N−1)のFET単位セル回路718のセルソースノードまで続く。図22に示されている実施形態では、FET単位セル回路712〜720の総数Nは奇数である。したがって、第((N+1)/2)のFET単位セル回路716は、チェーンの中央にある。明快のために図示されていない、第2のFET単位セル回路714と第((N+1)/2)のFET単位セル回路716との間の、および第((N+1)/2)のFET単位セル回路716と第(N−1)のFET単位セル回路718との間のチェーン中のさらなるFET単位セル回路が、省略記号(「...」)によって示されている。FET単位セル回路712〜720の数Nは、1よりも大きい任意の奇数であり得る。スイッチスタックデバイス710は、SOI基板上か、または他の好適な様式で形成され得る。

[00168]FET単位セル回路712〜720は、図3〜図12に示されている実施形態に関して上記で説明した様々なタイプのいずれかのものであり得る。代替的に、FET単位セル回路712〜720は従来のタイプのものであり得る。

[00169]FET単位セル回路712〜720の各々のセルボディノードは、図13〜図17に関して上記で説明した様式で、セルボディノードをバイアスし、ならびにフィルタ処理を行うボディバイアスネットワークフィルタ回路722に接続される。すなわち、ボディバイアスネットワークフィルタ回路722は、上記で説明したボディバイアスネットワークフィルタ回路384、414、450、502および536のいずれかを備えることができる。さらに他の実施形態(図示せず)では、そのようなFET単位セル回路のセルボディノードは、フィルタ処理を行わないものなど、他のタイプのボディバイアスネットワークに接続され得る。

[00170]FET単位セル回路712〜720の各々のセルゲートノードは、以下の様式で、セルゲートノードをバイアスし、ならびにフィルタ処理を行うゲートバイアスネットワークフィルタ回路724に接続される。ゲートバイアスネットワークフィルタ回路724は、互いに直列のN個のゲートバイアスネットワークフィルタ抵抗726〜728を含む。ゲートバイアスネットワーク抵抗726〜728の各々は、チェーン中の連続するFET単位セル回路のペアのセルゲートノード間に結合される。たとえば、第1のゲートバイアスネットワーク抵抗726は、第1のFET単位セル回路712のセルゲートノードと、第2のFET単位セル回路714のセルゲートノードとの間に接続され、第Nのゲートバイアスネットワーク抵抗728は、第(N−1)のFET単位セル回路718のセルゲートノードと、第NのFET単位セル回路720のセルゲートノードとの間に接続される。この実施形態では、共通ノード730は、チェーンの中央の第((N+1)/2)のFET単位セル回路716のセルゲートノードによって定義される。共通ノード730は、したがって、ゲートバイアスネットワーク抵抗のうちの(N−1)/2個の第1の直列接続グループと、ゲートバイアスネットワーク抵抗のうちの(N−1)/2個の第2の直列接続グループとの間にある。

[00171]ゲートバイアスネットワークフィルタ回路724はまた、互いに直列に接続されたN+1個のドレインソース抵抗732〜742を含む。ドレインソース抵抗732〜742の各々は、FET単位セル回路712〜720のうちの1つに対応し、FET単位セル回路712〜720のうちのそれの対応する1つのセルドレインノードとセルソースノードとの間に接続される。したがって、第1のドレインソース抵抗732は、第1のFET単位セル回路712のセルドレインノードとセルソースノードとの間に接続され、第2のドレインソース抵抗734は、第2のFET単位セル回路714のセルドレインノードとセルソースノードとの間に接続され、以下、第(N−1)のFET単位セル回路718のセルドレインノードとセルソースノードとの間に接続された第Nのドレインソース抵抗740まで同様であり、最後に、第NのFET単位セル回路720のセルドレインノードとセルソースノードとの間に接続された第(N+1)のドレインソース抵抗742である。この実施形態では、中間ノード744(すなわち、仮想ノードV)は、第(N/2)のドレインソース抵抗736と第((N/2)+1)のドレインソース抵抗738との間に定義される。第(N/2)のドレインソース抵抗736および第((N/2)+1)のドレインソース抵抗738は、互いに直列であり、チェーンの中央の第((N+1)/2)のFET単位セル回路528のセルドレインノードとセルソースノードとの間に接続される。第(N/2)のドレインソース抵抗736および第((N/2)+1)のドレインソース抵抗738は、両方とも、第((N+1)/2)のFET単位セル回路716に対応する。言い換えれば、直列のドレインソース抵抗736およびドレインソース抵抗738によって接続されたFET単位セル回路716のセルドレインノードおよびセルソースノードを除いて、各対応するFET単位セル回路のセルドレインノードとセルソースノードとの間に、単一のドレインソース抵抗のみが接続される。中間ノード744も、第((N+1)/2)のFET単位セル回路716のセルドレインノードとセルソースノードとの間にあることに留意されたい。また、中間ノード744は、ドレインソース抵抗のうちの(N+1)/2個の第1の直列接続グループ732〜736と、ドレインソース抵抗のうちの(N+1)/2個の第2の直列接続グループ738〜742との間にあることに留意されたい。

[00172]ゲートバイアスネットワークフィルタ回路724はまた、ゲートバイアスネットワークフィルタキャパシタンス746とゲートバイアスネットワークフィルタ共通抵抗748とを含む。ゲートバイアスネットワークフィルタキャパシタンス746は、中間ノード744に接続され、ゲートバイアスネットワークフィルタ共通抵抗748を介して、共通ノード730に結合される。したがって、ゲートバイアスネットワークフィルタキャパシタンス746およびゲートバイアスネットワークフィルタ共通抵抗748は、互いに直列であり、共通ノード730を介して、中間ノード744と、FET単位セル回路712〜720の各々のセルゲートノードとの間に結合される。共通抵抗750は、ゲートバイアスネットワークフィルタキャパシタンス746とゲートバイアスネットワークフィルタ共通抵抗748との間のノード752にゲートバイアス電圧(「V_BIAS」)ノードを結合する。したがって、共通ノード730は、抵抗748および抵抗750を介して、V_BIASノードに結合される。

[00173]ゲートバイアスネットワークフィルタ回路724はまた、他の実施形態に関して上記で説明した様式でスイッチスタックデバイス710を動作させるために使用され得る入力として、従来のスイッチ制御信号を受信する。

[00174]ゲートバイアスネットワークフィルタキャパシタンス746およびゲートバイアスネットワークフィルタ共通抵抗748は、一緒に、FET単位セル回路712〜720の各々のセルゲートノード電圧をフィルタ処理するRCベースフィルタを定義する。このRCベースゲートバイアスネットワークフィルタ回路724は、したがって、スイッチスタックデバイス710の線形動作を促進する。

[00175]上記の実施形態は、様々な方法で組み合わせられ得る。図23に示されているように、スイッチスタックデバイス754は、従来のタイプのFET単位セル回路が、図19に関して上記で説明した並列抵抗タイプのゲートバイアスネットワークフィルタ回路756、および図14に関して上記で説明した並列抵抗タイプのボディバイアスネットワークフィルタ回路758と組み合わせられた例を表す。スイッチスタックデバイス754は、図13、図14、図16、図18、図19および図21に関して上記で説明したのと同じ様式で接続された偶数個のFET単位セル回路760〜762および764〜766を含む。FET単位セル回路760〜766の各々は、従来の構造のものであり、それぞれ、FET768〜770および772〜774と、それぞれ、ドレインソースバイアス抵抗776〜778および780〜782とを備える。FET単位セル回路760〜766の各々は、他の実施形態に関して上記で説明した様式で、ゲートバイアスネットワークフィルタ回路756およびボディバイアスネットワークフィルタ回路758に接続される。ゲートバイアスネットワークフィルタ回路756は、図19に関して上記で説明したゲートバイアスネットワークフィルタ回路608と同等であるので、ゲートバイアスネットワークフィルタ回路756は、互いに並列のN個のゲートバイアスネットワーク抵抗784〜786および788〜790と、ゲートバイアスネットワークフィルタキャパシタンス792と、ゲートバイアスネットワークフィルタ共通抵抗794と、共通抵抗796とを含むことに留意されたい。ボディバイアスネットワークフィルタ回路758は、図14に関して上記で説明したボディバイアスネットワークフィルタ回路414と同等であるので、ボディバイアスネットワークフィルタ回路758は、互いに並列のN個のボディバイアスネットワークフィルタ抵抗798〜800および802〜804と、ボディバイアスネットワークフィルタキャパシタンス806と、ボディバイアスネットワークフィルタ共通抵抗808と、共通抵抗810とを含むことに留意されたい。

[00176]図24に示されているように、スイッチスタックデバイス812は、図4に関して上記で説明したタイプのFET単位セル回路が、図19に関して上記で説明した並列抵抗タイプのゲートバイアスネットワークフィルタ回路814、および図16に関して上記で説明した直列抵抗タイプのボディバイアスネットワークフィルタ回路816と組み合わせられた例を表す。スイッチスタックデバイス812は、図13、図14、図16、図18、図19および図21に関して上記で説明したのと同じ様式で接続された偶数個のFET単位セル回路818〜820および822〜824を含む。FET単位セル回路818〜824の各々は、図4に関して上記で説明したFET単位セル回路62〜66と同等である。FET単位セル回路818〜824の各々は、他の実施形態に関して上記で説明した様式で、ゲートバイアスネットワークフィルタ回路814およびボディバイアスネットワークフィルタ回路816に接続される。ゲートバイアスネットワークフィルタ回路814は、図19に関して上記で説明したゲートバイアスネットワークフィルタ回路608と同等であるので、ゲートバイアスネットワークフィルタ回路814は、互いに並列のN個のゲートバイアスネットワーク抵抗826〜828および830〜832と、ゲートバイアスネットワークフィルタキャパシタンス834と、ゲートバイアスネットワークフィルタ共通抵抗836と、共通抵抗838とを含むことに留意されたい。ボディバイアスネットワークフィルタ回路816は、図16に関して上記で説明したボディバイアスネットワークフィルタ回路502と同等であるので、ボディバイアスネットワークフィルタ回路816は、互いに直列のN個のボディバイアスネットワーク抵抗840〜842および844〜846と、ボディバイアスネットワークフィルタキャパシタンス848と、ボディバイアスネットワークフィルタ共通抵抗850と、共通抵抗852とを含むことに留意されたい。

[00177]図25に示されているように、スイッチスタックデバイス854は、図8に関して上記で説明したタイプのFET単位セル回路が、図22に関して上記で説明した直列抵抗タイプのゲートバイアスネットワークフィルタ回路856、および図14に関して上記で説明した並列抵抗タイプのボディバイアスネットワークフィルタ回路858と組み合わせられた例を表す。スイッチスタックデバイス854は、図13、図14、図16、図18、図19および図21に関して上記で説明したのと同じ様式で接続された偶数個のFET単位セル回路860〜862および864〜866を含む。FET単位セル回路860〜866の各々は、図8に関して上記で説明したFET単位セル回路174〜176と同等である。FET単位セル回路860〜866の各々は、他の実施形態に関して上記で説明した様式で、ゲートバイアスネットワークフィルタ回路856およびボディバイアスネットワークフィルタ回路858に接続される。ゲートバイアスネットワークフィルタ回路856は、図22に関して上記で説明したゲートバイアスネットワークフィルタ回路724と同様であるので、ゲートバイアスネットワークフィルタ回路856は、互いに直列のN個のゲートバイアスネットワーク抵抗868〜870および872〜874と、ゲートバイアスネットワークフィルタキャパシタンス876と、ゲートバイアスネットワークフィルタ共通抵抗878と、共通抵抗880とを含むことに留意されたい。ボディバイアスネットワークフィルタ回路858は、図14に関して上記で説明したボディバイアスネットワークフィルタ回路414と同等であるので、ボディバイアスネットワークフィルタ回路858は、互いに直列のN個のボディバイアスネットワーク抵抗882〜884および886〜888と、ボディバイアスネットワークフィルタキャパシタンス890と、ボディバイアスネットワークフィルタ共通抵抗892と、共通抵抗894とを含むことに留意されたい。

[00178]図26に示されているように、スイッチスタックデバイス896は、図12に関して上記で説明したタイプのFET単位セル回路が、図22に関して上記で説明した直列抵抗タイプのゲートバイアスネットワークフィルタ回路898、および図16に関して上記で説明した直列抵抗タイプのボディバイアスネットワークフィルタ回路900と組み合わせられた例を表す。スイッチスタックデバイス896は、図13、図14、図16、図18、図19および図21に関して上記で説明したのと同じ様式で接続された偶数個のFET単位セル回路902〜904および906〜908を含む。FET単位セル回路902〜908の各々は、図12に関して上記で説明したFET単位セル回路308〜310と同等である。FET単位セル回路902〜908の各々は、他の実施形態に関して上記で説明した様式で、ゲートバイアスネットワークフィルタ回路898およびボディバイアスネットワークフィルタ回路900に接続される。ゲートバイアスネットワークフィルタ回路898は、図22に関して上記で説明したゲートバイアスネットワークフィルタ回路724と同様であるので、ゲートバイアスネットワークフィルタ回路898は、互いに直列のN個のゲートバイアスネットワーク抵抗910〜912および914〜916と、ゲートバイアスネットワークフィルタキャパシタンス918と、ゲートバイアスネットワークフィルタ共通抵抗920と、抵抗922とを含むことに留意されたい。ボディバイアスネットワークフィルタ回路900は、図16に関して上記で説明したボディバイアスネットワークフィルタ回路502と同等であるので、ボディバイアスネットワークフィルタ回路900は、互いに直列のN個のボディバイアスネットワーク抵抗924〜926および928〜930と、ボディバイアスネットワークフィルタキャパシタンス932と、ボディバイアスネットワークフィルタ共通抵抗934と、抵抗936とを含むことに留意されたい。

[00179]図23〜図26に示されている例は、当業者が可能であると認識するであろう、上記で説明したタイプのFET単位セル回路と、ゲートバイアスネットワークフィルタ回路と、ボディバイアスネットワークフィルタ回路との様々な組合せの一部分のみを表す。本明細書での説明に鑑みて、他のそのような組合せは、当業者にとって容易に思い付くものであろう。

[00180]選択された態様について詳細に図示および説明したが、以下の特許請求の範囲によって定義されるように、本発明の趣旨および範囲から逸脱することなく、様々な置換および改変を本明細書で行い得ることを理解されよう。

[00180]選択された態様について詳細に図示および説明したが、以下の特許請求の範囲によって定義されるように、本発明の趣旨および範囲から逸脱することなく、様々な置換および改変を本明細書で行い得ることを理解されよう。

以下に、出願当初の特許請求の範囲に記載された発明を付記する。

[C1]

電界効果トランジスタ(FET)スタックとして構成された複数のFET単位セル回路と、各FET単位セル回路がFETを備え、

前記FETスタックに結合されたバイアスネットワーク回路と、

前記バイアスネットワーク回路または前記複数のFET単位セル回路中に含まれるフィルタ処理回路と、前記フィルタ処理回路がキャパシタンスを含み、を備える、無線周波数(RF)信号を切り替えるためのデバイス。

[C2]

各FET単位セル回路が、少なくとも、ボディフィルタまたはゲートフィルタを含み、前記ボディフィルタが、前記FETのボディノードに結合されたボディフィルタキャパシタンスを含み、前記ゲートフィルタが、前記FETの前記ゲートノードに結合されたゲートフィルタキャパシタンスを含む、C1に記載のデバイス。

[C3]

前記ゲートフィルタがドレインソース回路を含み、前記ドレインソース回路が、第2の抵抗と直列の第1の抵抗を有する分割器回路を備え、前記分割器回路が、前記第1の抵抗と前記第2の抵抗との間の仮想ノードを定義し、前記ゲートフィルタキャパシタンスが、前記仮想ノードに結合された、C2に記載のデバイス。

[C4]

前記FETの前記ボディノードと、前記仮想ノードとの間のボディフィルタキャパシタンスをさらに備える、C3に記載のデバイス。

[C5]

前記ゲートフィルタがドレインソース回路を含み、前記ドレインソース回路が、第2のキャパシタンスと直列の第1のキャパシタンスを有する分割器回路を備え、前記分割器回路が、前記第1のキャパシタンスと前記第2のキャパシタンスとの間の仮想ノードを定義し、前記ゲートフィルタが、前記仮想ノードと、前記FETの前記ゲートノードとの間に結合されたゲートフィルタ抵抗を備える、C2に記載のデバイス。

[C6]

前記FETの前記ボディノードと、前記仮想ノードとの間のボディフィルタキャパシタンスをさらに備える、C5に記載のデバイス。

[C7]

前記複数のFET単位セル回路の各FET単位セル回路が、第1のFETと第2のFETとを備え、前記デバイスが、

前記第1のFETのボディノードと、前記第1のFETのゲートノードとの間に結合された第1のボディフィルタキャパシタンスを有する第1のボディフィルタと、

前記第2のFETのボディノードと、前記第2のFETのゲートノードとの間に結合された第2のボディフィルタキャパシタンスを有する第2のボディフィルタとをさらに備える、C2に記載のデバイス。

[C8]

前記第1のFETのソースノードと、前記第1のFETの前記ボディノードとの間に結合され、前記第2のFETのドレインノードと、前記第2のFETの前記ボディノードとの間に結合された共有ボディフィルタキャパシタンスをさらに備える、C7に記載のデバイス。

[C9]

前記複数のFET単位セル回路が、シリコンオンインシュレータ(SOI)基板上に形成された、C1に記載のデバイス。

[C10]

前記バイアスネットワーク回路が、少なくとも、ゲートバイアスネットワークフィルタ回路またはボディバイアスネットワークフィルタ回路を備え、前記ゲートバイアスネットワークフィルタ回路が、各FET単位セル回路の前記ゲートノードに結合され、前記ボディバイアスネットワークフィルタ回路が、各FET単位セル回路の前記ボディノードに結合され、前記ボディバイアスネットワークフィルタ回路が、連続するFET単位セル回路のペア間の少なくとも1つのドレインソースノードに結合された中間ノードを有し、前記ボディバイアスネットワークフィルタ回路が、前記中間ノードと、各FET単位セル回路の前記ボディノードとの間に結合されたボディバイアスネットワークフィルタキャパシタンスを有し、前記ゲートバイアスネットワークフィルタ回路が、前記中間ノードと、各FET単位セル回路の前記ゲートノードとの間に結合されたゲートバイアスネットワークフィルタキャパシタンスを有する、C1に記載のデバイス。

[C11]

前記ボディバイアスネットワークフィルタ回路が、共通ノードに関して互いに並列の複数のボディバイアスネットワーク抵抗を備え、各ボディバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ボディバイアスネットワーク抵抗が、前記共通ノードと、対応するFET単位セル回路の前記ボディノードとの間に接続された、C10に記載のデバイス。

[C12]

前記ボディバイアスネットワークフィルタ回路が、互いに直列の複数のボディバイアスネットワーク抵抗を備え、各ボディバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ボディノード間に結合された、C10に記載のデバイス。

[C13]

前記ゲートバイアスネットワークフィルタ回路が、共通ノードに関して互いに並列の複数のゲートバイアスネットワーク抵抗を備え、各ゲートバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ゲートバイアスネットワーク抵抗が、前記共通ノードと、対応するFET単位セル回路の前記ゲートノードとの間に接続された、C10に記載のデバイス。

[C14]

前記ゲートバイアスネットワークフィルタ回路が、互いに直列の複数のゲートバイアスネットワーク抵抗を備え、各ゲートバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ゲートノード間に結合された、C10に記載のデバイス。

[C15]

前記ボディバイアスネットワークフィルタ回路が、ボディバイアスネットワークキャパシタと、前記ボディバイアスネットワークフィルタ回路の共通ノードに関して互いに並列の複数のボディバイアスネットワークフィルタ抵抗とを備え、各ボディバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ボディバイアスネットワーク抵抗が、前記ボディバイアスネットワークフィルタ回路の前記共通ノードと、対応するFET単位セル回路の前記ボディノードとの間に接続され、前記ボディバイアスネットワークキャパシタが、前記中間ノードと、前記ボディバイアスネットワークフィルタ回路の前記共通ノードとの間に結合された、

前記ゲートバイアスネットワークフィルタ回路が、ゲートバイアスネットワークキャパシタと、前記ゲートバイアスネットワークフィルタ回路の共通ノードに関して互いに並列の複数のゲートバイアスネットワーク抵抗とを備え、各ゲートバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ゲートバイアスネットワーク抵抗が、前記ゲートバイアスネットワークフィルタ回路の前記共通ノードと、対応するFET単位セル回路の前記ゲートノードとの間に接続され、前記ゲートバイアスネットワークキャパシタが、前記中間ノードと、前記ゲートバイアスネットワークフィルタ回路の前記共通ノードとの間に結合された、C10に記載のデバイス。

[C16]

前記ボディバイアスネットワークフィルタ回路が、ボディバイアスネットワークキャパシタと、前記ボディバイアスネットワークフィルタ回路の共通ノードに関して互いに並列の複数のボディバイアスネットワーク抵抗とを備え、各ボディバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ボディバイアスネットワーク抵抗が、前記ボディバイアスネットワークフィルタ回路の前記共通ノードと、対応するFET単位セル回路の前記ボディノードとの間に接続され、前記ボディバイアスネットワークキャパシタが、前記中間ノードと、前記ボディバイアスネットワークフィルタ回路の前記共通ノードとの間に結合された、

前記ゲートバイアスネットワークフィルタ回路が、ゲートバイアスネットワークキャパシタと、互いに直列の複数のゲートバイアスネットワーク抵抗とを備え、各ゲートバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ゲートノード間に結合され、前記ゲートバイアスネットワークキャパシタが、前記中間ノードと、前記ゲートバイアスネットワークフィルタ回路の共通ノードとの間に結合された、C10に記載のデバイス。

[C17]

前記ボディバイアスネットワークフィルタ回路が、ボディバイアスネットワークキャパシタと、互いに直列の複数のボディバイアスネットワーク抵抗とを備え、各ボディバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ボディノード間に結合され、前記ボディバイアスネットワークキャパシタが、前記中間ノードと、前記ゲートバイアスネットワークフィルタ回路の共通ノードとの間に結合された、

前記ゲートバイアスネットワークフィルタ回路が、ゲートバイアスネットワークキャパシタと、前記ゲートバイアスネットワークフィルタ回路の共通ノードに関して互いに並列の複数のゲートバイアスネットワーク抵抗とを備え、各ゲートバイアスネットワーク抵抗が、前記複数のFET単位セル回路のうちの1つに対応し、各ゲートバイアスネットワーク抵抗が、前記共通ノードと、対応するFET単位セル回路の前記ゲートノードとの間に接続され、前記ゲートバイアスネットワークキャパシタが、前記中間ノードと、前記ゲートバイアスネットワークフィルタ回路の前記共通ノードとの間に結合された、C10に記載のデバイス。

[C18]

前記ボディバイアスネットワークフィルタ回路が、ボディバイアスネットワークキャパシタと、互いに直列の複数のボディバイアスネットワーク抵抗とを備え、各ボディバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ボディノード間に結合され、前記ボディバイアスネットワークキャパシタが、前記中間ノードと、前記ボディバイアスネットワークフィルタ回路の共通ノードとの間に結合された、

前記ゲートバイアスネットワークフィルタ回路が、ゲートバイアスネットワークキャパシタと、互いに直列の複数のゲートバイアスネットワーク抵抗とを備え、各ゲートバイアスネットワーク抵抗が、連続するFET単位セル回路のペアの前記ゲートノード間に結合され、前記ゲートバイアスネットワークキャパシタが、前記中間ノードと、前記ゲートバイアスネットワークフィルタ回路の共通ノードとの間に結合された、C10に記載のデバイス。

[C19]

無線周波数信号を切り替えるための手段と、

切り替えるための前記手段をバイアスするための手段と、

切り替えるための前記手段またはバイアスするための前記手段中に含まれるフィルタ処理するための手段と、フィルタ処理するための前記手段がキャパシタンスを含む、を備える、デバイス。

[C20]

フィルタ処理するための前記手段が、FETゲートノード信号をフィルタ処理するための手段、またはFETボディノード信号をフィルタ処理するための手段を備える、C19に記載のデバイス。