JP2016164780A - メモリシステム、および情報処理システム - Google Patents

メモリシステム、および情報処理システム Download PDFInfo

- Publication number

- JP2016164780A JP2016164780A JP2016035144A JP2016035144A JP2016164780A JP 2016164780 A JP2016164780 A JP 2016164780A JP 2016035144 A JP2016035144 A JP 2016035144A JP 2016035144 A JP2016035144 A JP 2016035144A JP 2016164780 A JP2016164780 A JP 2016164780A

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- memory

- metal oxide

- layer

- oxide layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 230000010365 information processing Effects 0.000 title claims description 18

- 239000004065 semiconductor Substances 0.000 claims description 156

- 230000006870 function Effects 0.000 claims description 43

- 238000012937 correction Methods 0.000 claims description 27

- 238000001514 detection method Methods 0.000 claims description 21

- 230000015572 biosynthetic process Effects 0.000 claims description 18

- 238000007599 discharging Methods 0.000 claims description 3

- 239000010410 layer Substances 0.000 description 365

- 229910044991 metal oxide Inorganic materials 0.000 description 178

- 150000004706 metal oxides Chemical class 0.000 description 178

- 210000004027 cell Anatomy 0.000 description 90

- 239000000758 substrate Substances 0.000 description 76

- 239000004020 conductor Substances 0.000 description 44

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 43

- 239000001301 oxygen Substances 0.000 description 43

- 229910052760 oxygen Inorganic materials 0.000 description 43

- 125000004429 atom Chemical group 0.000 description 42

- 239000013078 crystal Substances 0.000 description 42

- 238000000034 method Methods 0.000 description 34

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 24

- 238000010586 diagram Methods 0.000 description 24

- 239000012535 impurity Substances 0.000 description 22

- 239000008188 pellet Substances 0.000 description 21

- 238000003860 storage Methods 0.000 description 19

- 239000011701 zinc Substances 0.000 description 18

- 229910052739 hydrogen Inorganic materials 0.000 description 17

- 239000001257 hydrogen Substances 0.000 description 17

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 16

- 229910052710 silicon Inorganic materials 0.000 description 16

- 239000010703 silicon Substances 0.000 description 16

- 239000012212 insulator Substances 0.000 description 15

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 13

- 229910052738 indium Inorganic materials 0.000 description 13

- 239000003990 capacitor Substances 0.000 description 12

- 239000000203 mixture Substances 0.000 description 12

- 229910052757 nitrogen Inorganic materials 0.000 description 12

- 239000000523 sample Substances 0.000 description 12

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 11

- 229910052751 metal Inorganic materials 0.000 description 11

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 10

- 239000002184 metal Substances 0.000 description 10

- 238000002173 high-resolution transmission electron microscopy Methods 0.000 description 9

- 230000005684 electric field Effects 0.000 description 8

- 238000004544 sputter deposition Methods 0.000 description 8

- 239000011135 tin Substances 0.000 description 8

- 229910052782 aluminium Inorganic materials 0.000 description 7

- 239000010949 copper Substances 0.000 description 7

- 230000007547 defect Effects 0.000 description 7

- 230000014759 maintenance of location Effects 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 238000012545 processing Methods 0.000 description 7

- 239000010936 titanium Substances 0.000 description 7

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 6

- 238000004458 analytical method Methods 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 6

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 6

- 238000002003 electron diffraction Methods 0.000 description 6

- 229910052733 gallium Inorganic materials 0.000 description 6

- 229910001195 gallium oxide Inorganic materials 0.000 description 6

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 6

- 239000002159 nanocrystal Substances 0.000 description 6

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 5

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 5

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 5

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 5

- 229910045601 alloy Inorganic materials 0.000 description 5

- 239000000956 alloy Substances 0.000 description 5

- 150000001875 compounds Chemical class 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000004519 manufacturing process Methods 0.000 description 5

- 230000008569 process Effects 0.000 description 5

- 239000011347 resin Substances 0.000 description 5

- 229920005989 resin Polymers 0.000 description 5

- 238000012916 structural analysis Methods 0.000 description 5

- 229910052718 tin Inorganic materials 0.000 description 5

- 229910052719 titanium Inorganic materials 0.000 description 5

- 239000011800 void material Substances 0.000 description 5

- 229910052727 yttrium Inorganic materials 0.000 description 5

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 4

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 4

- 229910052581 Si3N4 Inorganic materials 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 238000000231 atomic layer deposition Methods 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 238000010894 electron beam technology Methods 0.000 description 4

- 229910000449 hafnium oxide Inorganic materials 0.000 description 4

- 238000010438 heat treatment Methods 0.000 description 4

- 150000002431 hydrogen Chemical class 0.000 description 4

- AMWRITDGCCNYAT-UHFFFAOYSA-L hydroxy(oxo)manganese;manganese Chemical compound [Mn].O[Mn]=O.O[Mn]=O AMWRITDGCCNYAT-UHFFFAOYSA-L 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 239000011733 molybdenum Substances 0.000 description 4

- 229910052759 nickel Inorganic materials 0.000 description 4

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 4

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 4

- 239000002356 single layer Substances 0.000 description 4

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- 239000010937 tungsten Substances 0.000 description 4

- VWQVUPCCIRVNHF-UHFFFAOYSA-N yttrium atom Chemical compound [Y] VWQVUPCCIRVNHF-UHFFFAOYSA-N 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 239000011651 chromium Substances 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 230000002950 deficient Effects 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 230000012447 hatching Effects 0.000 description 3

- 238000003384 imaging method Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- 238000005477 sputtering target Methods 0.000 description 3

- 229910052715 tantalum Inorganic materials 0.000 description 3

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 3

- 229910052725 zinc Inorganic materials 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 2

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- KJTLSVCANCCWHF-UHFFFAOYSA-N Ruthenium Chemical compound [Ru] KJTLSVCANCCWHF-UHFFFAOYSA-N 0.000 description 2

- 238000002441 X-ray diffraction Methods 0.000 description 2

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 2

- 239000004760 aramid Substances 0.000 description 2

- 229920003235 aromatic polyamide Polymers 0.000 description 2

- 238000005452 bending Methods 0.000 description 2

- 229910052796 boron Inorganic materials 0.000 description 2

- 229910052799 carbon Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000003795 desorption Methods 0.000 description 2

- 230000006866 deterioration Effects 0.000 description 2

- 239000000835 fiber Substances 0.000 description 2

- 229910052732 germanium Inorganic materials 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910052735 hafnium Inorganic materials 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 description 2

- 239000004973 liquid crystal related substance Substances 0.000 description 2

- 239000011572 manganese Substances 0.000 description 2

- WPBNNNQJVZRUHP-UHFFFAOYSA-L manganese(2+);methyl n-[[2-(methoxycarbonylcarbamothioylamino)phenyl]carbamothioyl]carbamate;n-[2-(sulfidocarbothioylamino)ethyl]carbamodithioate Chemical compound [Mn+2].[S-]C(=S)NCCNC([S-])=S.COC(=O)NC(=S)NC1=CC=CC=C1NC(=S)NC(=O)OC WPBNNNQJVZRUHP-UHFFFAOYSA-L 0.000 description 2

- 238000012544 monitoring process Methods 0.000 description 2

- PLDDOISOJJCEMH-UHFFFAOYSA-N neodymium(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Nd+3].[Nd+3] PLDDOISOJJCEMH-UHFFFAOYSA-N 0.000 description 2

- 150000004767 nitrides Chemical class 0.000 description 2

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 229920001343 polytetrafluoroethylene Polymers 0.000 description 2

- 239000004810 polytetrafluoroethylene Substances 0.000 description 2

- 238000004549 pulsed laser deposition Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- 229910001936 tantalum oxide Inorganic materials 0.000 description 2

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 2

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 2

- 238000004402 ultra-violet photoelectron spectroscopy Methods 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- 229910001868 water Inorganic materials 0.000 description 2

- 210000002925 A-like Anatomy 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- 229910052684 Cerium Inorganic materials 0.000 description 1

- 229910017566 Cu-Mn Inorganic materials 0.000 description 1

- 229910017871 Cu—Mn Inorganic materials 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- PWHULOQIROXLJO-UHFFFAOYSA-N Manganese Chemical compound [Mn] PWHULOQIROXLJO-UHFFFAOYSA-N 0.000 description 1

- 229910052779 Neodymium Inorganic materials 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 238000003917 TEM image Methods 0.000 description 1

- QCWXUUIWCKQGHC-UHFFFAOYSA-N Zirconium Chemical compound [Zr] QCWXUUIWCKQGHC-UHFFFAOYSA-N 0.000 description 1

- YKTSYUJCYHOUJP-UHFFFAOYSA-N [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] Chemical compound [O--].[Al+3].[Al+3].[O-][Si]([O-])([O-])[O-] YKTSYUJCYHOUJP-UHFFFAOYSA-N 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 1

- 230000032683 aging Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 229910052786 argon Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- GWXLDORMOJMVQZ-UHFFFAOYSA-N cerium Chemical compound [Ce] GWXLDORMOJMVQZ-UHFFFAOYSA-N 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 230000003750 conditioning effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000002524 electron diffraction data Methods 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- YZZNJYQZJKSEER-UHFFFAOYSA-N gallium tin Chemical compound [Ga].[Sn] YZZNJYQZJKSEER-UHFFFAOYSA-N 0.000 description 1

- 239000007789 gas Substances 0.000 description 1

- YBMRDBCBODYGJE-UHFFFAOYSA-N germanium oxide Inorganic materials O=[Ge]=O YBMRDBCBODYGJE-UHFFFAOYSA-N 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 229910002804 graphite Inorganic materials 0.000 description 1

- 239000010439 graphite Substances 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 229910001385 heavy metal Inorganic materials 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- 230000001788 irregular Effects 0.000 description 1

- 229910052746 lanthanum Inorganic materials 0.000 description 1

- FZLIPJUXYLNCLC-UHFFFAOYSA-N lanthanum atom Chemical compound [La] FZLIPJUXYLNCLC-UHFFFAOYSA-N 0.000 description 1

- 239000007788 liquid Substances 0.000 description 1

- CPLXHLVBOLITMK-UHFFFAOYSA-N magnesium oxide Inorganic materials [Mg]=O CPLXHLVBOLITMK-UHFFFAOYSA-N 0.000 description 1

- 239000000395 magnesium oxide Substances 0.000 description 1

- AXZKOIWUVFPNLO-UHFFFAOYSA-N magnesium;oxygen(2-) Chemical compound [O-2].[Mg+2] AXZKOIWUVFPNLO-UHFFFAOYSA-N 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 238000002844 melting Methods 0.000 description 1

- 230000008018 melting Effects 0.000 description 1

- 238000001451 molecular beam epitaxy Methods 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- SIWVEOZUMHYXCS-UHFFFAOYSA-N oxo(oxoyttriooxy)yttrium Chemical compound O=[Y]O[Y]=O SIWVEOZUMHYXCS-UHFFFAOYSA-N 0.000 description 1

- PVADDRMAFCOOPC-UHFFFAOYSA-N oxogermanium Chemical compound [Ge]=O PVADDRMAFCOOPC-UHFFFAOYSA-N 0.000 description 1

- KYKLWYKWCAYAJY-UHFFFAOYSA-N oxotin;zinc Chemical compound [Zn].[Sn]=O KYKLWYKWCAYAJY-UHFFFAOYSA-N 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 230000035699 permeability Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229920000515 polycarbonate Polymers 0.000 description 1

- 239000004417 polycarbonate Substances 0.000 description 1

- 229920000728 polyester Polymers 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 229920000098 polyolefin Polymers 0.000 description 1

- -1 polytetrafluoroethylene Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- VSZWPYCFIRKVQL-UHFFFAOYSA-N selanylidenegallium;selenium Chemical compound [Se].[Se]=[Ga].[Se]=[Ga] VSZWPYCFIRKVQL-UHFFFAOYSA-N 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000004332 silver Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 229910002076 stabilized zirconia Inorganic materials 0.000 description 1

- 230000035882 stress Effects 0.000 description 1

- 229910052712 strontium Inorganic materials 0.000 description 1

- CIOAGBVUUVVLOB-UHFFFAOYSA-N strontium atom Chemical compound [Sr] CIOAGBVUUVVLOB-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

- 229910001887 tin oxide Inorganic materials 0.000 description 1

- 229910052723 transition metal Inorganic materials 0.000 description 1

- 229910001233 yttria-stabilized zirconia Inorganic materials 0.000 description 1

- 239000011787 zinc oxide Substances 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

- 229910001928 zirconium oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1068—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in sector programmable memories, e.g. flash disk

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/52—Protection of memory contents; Detection of errors in memory contents

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1048—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices using arrangements adapted for a specific error detection or correction feature

- G06F11/106—Correcting systematically all correctable errors, i.e. scrubbing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/7869—Thin film transistors, i.e. transistors with a channel being at least partly a thin film having a semiconductor body comprising an oxide semiconductor material, e.g. zinc oxide, copper aluminium oxide, cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/70—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates the floating gate being an electrode shared by two or more components

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- General Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

- Dram (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

- Debugging And Monitoring (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

Abstract

【解決手段】メモリシステムは、メモリ、ECC回路、およびプロセッサを有する。プロセッサは、メモリシステム全体の動作を制御する。メモリは、ユーザデータ領域および管理領域を有する。管理領域には、管理テーブルとして、ユーザデータ領域のブロック別にアクセス情報が格納されている。アクセス情報の値は、アクセス回数が0であることを表す第1の値か、アクセス回数が1以上であることを表す第2の値かのいずれかである。ブロックのアクセス情報が第1の値である場合、該当するブロックに対してエラー訂正が行われ、第2の値である場合、該当するブロックのエラー検出および訂正が行われない。

【選択図】図1

Description

本実施の形態では、OSトランジスタが適用されたメモリシステム、およびその動作方法等について説明する。

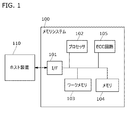

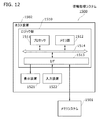

図1は、メモリシステムの構成例を示すブロック図である。メモリシステム100は、ホスト装置110のアクセス要求に応じて、データの書き込み、データの読み出しを行う機能を有する。メモリシステム100は、インターフェース(I/F)101、プロセッサ102、ワークメモリ103、メモリ104、およびECC回路105を有する。

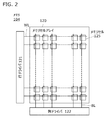

図2はメモリ104の構成例を示すブロック図である。メモリ104は、メモリセルアレイ120、行ドライバ121、および列ドライバ122を有する。メモリセルアレイ120は、メモリセル125、配線WL、および配線BLを有する。複数のメモリセル125は、行列状に配置されている。同じ行のメモリセル125は、当該行の配線WLと電気的に接続され、同じ列のメモリセル125は、当該列の配線BLと電気的に接続されている。

図3に、メモリセルの回路構成例を示す。図3に示すメモリセル151−155は、メモリセル125に適用することができ、書き込みトランジスタがOSトランジスタである。OSトランジスタはオフ電流が極めて小さいため、図3に示すメモリセルは、不揮発性のメモリデバイスとして機能する。

図3Aのメモリセル151は1T1C型のメモリセルであり、ノードSN1、トランジスタTW1、容量素子CS1を有する。ノードSN1は保持ノードである。容量素子CS1は、ノードSN1の電荷を保持するための保持容量である。トランジスタTW1は書き込みトランジスタであり、OSトランジスタである。トランジスタTW1は配線BLとノードSN1との間の導通状態を制御する機能を有する。トランジスタTW1のゲートは配線WLと電気的に接続されている。

図3Dのメモリセル154は2T型のメモリセルであり、配線WWL、RWL、BL、SLと電気的に接続されている。配線WWLは書き込みワード線であり、配線RWLは読み出しワード線であり、それぞれ行ドライバ121から信号が入力される。配線SLには、列ドライバ122から信号が入力される。

図3Fのメモリセル155は3T型のメモリセルであり、配線WWL、RWL、BL、SL、CNLと電気的に接続されている。メモリセル155は、ノードSN1、容量素子CS1、トランジスタTW1、TR2、TR3を有する。容量素子CS1は、ノードSN1と配線CNLとの間を容量結合している。配線CNLには固定電位を入力してもよいし、メモリセル155の選択状態、および非選択状態に合わせて、配線CNLの電位を制御してもよい。配線BLと配線SLとの間に、トランジスタTR2とトランジスタTR3は直列に電気的に接続されている。トランジスタTR2のゲートはノードSN1と電気的に接続され、トランジスタTR3のゲートは配線RWLと電気的に接続されている。

ここでは、代表的に、メモリセル155の駆動方法の一例を説明する。図4はメモリセル155の動作例を示すタイミングチャートである。図4において、配線WWL、RWL、WBL、RBL、SL、CNLの低(L)レベルの電位は、VSSMとしている。VSSMは接地電位(GND)や、0Vとすればよい。配線WWLの高(H)レベルの電位はVDDHであり、配線RWL、WBL、RBL、SL、CNLの高(H)レベルの電位はVDDMである。ここでは、トランジスタTW1のしきい値電圧がトランジスタTR2、TR3よりも高いこととし、そのため、VDDHはVDDMよりも高い。

期間P2は書き込み期間である。選択行の配線WWLをHレベルにして、トランジスタTW1をオンにする。メモリセル155に“1”を書き込む場合は、配線WBLをHレベルにし、“0”を書き込む場合は、配線WBLをLレベルにする。選択されたメモリセル155において、ノードSN1の電位は、配線WBLの電位に応じて、VDDMまたはVSSMとなる。

期間P4は読み出し期間である。まず、配線RBLをプリチャージして、Hレベルにする。次に、非選択行の配線RWLはLレベルのままとし、選択行の配線RWLをHレベルにする。選択されたメモリセル155のトランジスタTR3はオンとなる。ノードSN1が“0”を保持している場合は、トランジスタTR2がオフであるので、配線RBLはHレベルのままである。ノードSN1が“1”を保持している場合は、トランジスタTR2がオンとなるので、配線RBLの電位は低下する。配線RWLをLレベルにして、トランジスタTR3をオフにすることで、読み出し動作が終了する。列ドライバ122は、期間P4の配線RBLの電位に基づいて、メモリセル155から読み出したデータが“0”か“1”を決定する。

図5を参照して、メモリ104の記憶領域の構成を説明する。図5Aに、メモリ104の記憶領域の構成例を示す。メモリ104は、ユーザデータ領域130、ファームウエア領域131、ECC管理領域132を有する。

図6−図10Bを参照して、メモリシステム100の動作例について説明する。各フローチャートに示される動作は、ファームウエア領域131に記憶されているファームウエアによって定義されている。プロセッサ102がファームウエアを実行することで、定義されている処理が実行されるように、メモリシステム100の各回路が動作する。

図6は、電源をオンにした際のメモリシステム100の動作例を示すフローチャートである。電源がオンになると、プロセッサ102は、メモリ104にアクセスして、ECC管理テーブル135の全てのビットを“0”に初期化する(ステップS11)。

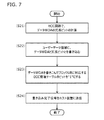

図7は、ホスト装置110の書き込みアクセスに対するメモリシステム100の動作例を示すフローチャートである。ここでは、ホスト装置110から送信された書き込みデータをデータWDAと呼ぶことする。書き込み要求があると、プロセッサ102は、ECC回路105において、データWDAの冗長ビットを計算させる(ステップS21)。次に、プロセッサ102は、メモリ104を制御して、ユーザデータ領域130およびECC管理テーブル135を更新する。ユーザデータ領域130に、データWDAおよびステップS21で得られた冗長ビットを書き込む(ステップS22)。ステップS22でデータを書きこんだブロックUBに対応するECC管理テーブル135のビットを“1”にする(ステップS23)。最後に、プロセッサ102は、I/F101を介して書き込み完了信号をホスト装置110に送信する(ステップS24)。

図8は、ホスト装置110の読み出しアクセスに対するメモリシステム100の動作例を示すフローチャートである。ホスト装置110は、読み出し要求信号、アドレスをI/F101に送信する。読み出し要求信号を受信すると、プロセッサ102は、メモリ104を制御し、ホスト装置110から送信されたアドレスが指定するブロックUB[r]からデータを読み出し(ステップS31)、ECC管理テーブル135から、ブロックUB[r]に対応するビットを読み出す(ステップS32)。なお、rは1以上K以下の整数である。

図9は、メモリシステム100の電源をオフにする際のプロセッサ102の動作例を示すフローチャートである。メモリシステム100では、電源をオフする前に、ECC管理テーブル135を利用して、1回もアクセスされなかったユーザデータ領域130のブロックUBを見つけ、見つけたブロックUBに対して、ECC回路105でエラー検出訂正が行われる。これにより、メモリシステム100のデータ保持の信頼性が強化される。

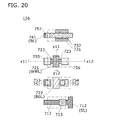

本実施の形態では、メモリシステム100の応用例について説明する。メモリシステム100は、例えば、各種電子機器(例えば、情報端末、スマートフォン、電子書籍端末、デジタルカメラ(ビデオカメラも含む)、録画再生装置、ナビゲーションシステムなど)のストレージ装置に適用できる。または、メモリシステム100は、メモリカード(例えば、SDカード)、USBメモリ、SSD(ソリッド・ステート・ドライブ)等の各種のリムーバブル記憶装置に適用される。図11に、リムーバブル記憶装置の幾つかの構成例を模式的に示す。

本実施の形態では、ホスト装置110とメモリシステム100とを組み合わせた情報処理システムについて説明する。

本実施の形態では、OSトランジスタ、およびOSトランジスタを有する半導体装置について説明する。

図15にOSトランジスタの構成の一例を示す。図15AはOSトランジスタの構成の一例を示す上面図である。図15Bは、y1−y2線断面図であり、図15Cはx1−x2線断面図であり、図15Dはx3−x4線断面図である。ここでは、y1−y2線の方向をチャネル長方向と呼び、x1−x2線方向をチャネル幅方向と呼ぶ場合がある。なお、デバイス構造を明確にするため、図15Aでは、一部の構成要素が省略されている。

導電層850−853は、銅(Cu)、タングステン(W)、モリブデン(Mo)、金(Au)、アルミニウム(Al)、マンガン(Mn)、チタン(Ti)、タンタル(Ta)、ニッケル(Ni)、クロム(Cr)、鉛(Pb)、錫(Sn)、鉄(Fe)、コバルト(Co)、ルテニウム(Ru)、白金(Pt)、イリジウム(Ir)、ストロンチウム(Sr)の低抵抗材料からなる単体、もしくは合金、またはこれらを主成分とする化合物を含む導電膜の単層または積層とすることが好ましい。特に、耐熱性と導電性を両立するタングステンやモリブデンなどの高融点材料を用いることが好ましい。また、アルミニウムや銅などの低抵抗導電性材料で形成することが好ましい。さらに、Cu−Mn合金を用いると、酸素を含む絶縁体との界面に酸化マンガンを形成し、酸化マンガンがCuの拡散を抑制する機能を持つので好ましい。

金属酸化物層842は、例えば、インジウム(In)を含む酸化物半導体である。金属酸化物層842は、例えば、インジウムを含むと、キャリア移動度(電子移動度)が高くなる。また、金属酸化物層842は、元素Mを含むと好ましい。元素Mは、好ましくは、アルミニウム(Al)、ガリウム(Ga)、イットリウム(Y)またはスズ(Sn)などとする。その他の元素Mに適用可能な元素としては、ホウ素B、シリコン(Si)、チタン(Ti)、鉄(Fe)、ニッケル(Ni)、ゲルマニウム(Ge)、ジルコニウム(Zr)、モリブデン(Mo)、ランタン(La)、セリウム(Ce)、ネオジム(Nd)、ハフニウム(Hf)、タンタル(Ta)、タングステン(W)などがある。ただし、元素Mとして、前述の元素を複数組み合わせても構わない場合がある。元素Mは、例えば、酸素との結合エネルギーが高い元素である。例えば、酸素との結合エネルギーがインジウムよりも高い元素である。または、元素Mは、例えば、酸化物半導体のエネルギーギャップを大きくする機能を有する元素である。また、金属酸化物層842は、亜鉛(Zn)を含むと好ましい。酸化物半導体は、亜鉛を含むと結晶化しやすくなる場合がある。

図16を参照して、金属酸化物層841、金属酸化物層842、および金属酸化物層843の積層により構成される半導体領域840の機能およびその効果について、説明する。図16Aは、図15Bの部分拡大図であり、OSトランジスタ800の活性層(チャネル部分)を拡大した図である。図16BはOSトランジスタ800のチャネル形成領域のエネルギーバンド構造であり、図16Aの点線z1−z2で示す部位のエネルギーバンド構造を示している。

絶縁層821−825は、単層構造または積層構造の絶縁膜で形成される。絶縁膜を構成する材料には、例えば、酸化アルミニウム、酸化マグネシウム、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化ガリウム、酸化ゲルマニウム、酸化イットリウム、酸化ジルコニウム、酸化ランタン、酸化ネオジム、酸化ハフニウム、酸化タンタルなどがある。

Siトランジスタでは、チャネルドーピングによってしきい値電圧を容易に制御することができる。これに対して、OSトランジスタは、チャネルドーピングでは、しきい値電圧を効果的に変化させることが困難である。OSトランジスタでは、電荷捕獲層に電子を注入することで、しきい値電圧を変動させることが可能である。例えば、電荷捕獲層への電子の注入はトンネル効果を利用すればよい。導電層853に正の電圧を印加することによって、トンネル電子を電荷捕獲層に注入する。

基板820としては、例えば、絶縁体基板、半導体基板または導電体基板を用いればよい。絶縁体基板は、例えば、ガラス基板、石英基板、サファイア基板、安定化ジルコニア基板(イットリア安定化ジルコニア基板など)、樹脂基板などである。また、半導体基板は、例えば、シリコン、ゲルマニウムなどの単体半導体基板、または炭化シリコン、シリコンゲルマニウム、ヒ化ガリウム、リン化インジウム、酸化亜鉛、酸化ガリウムからなる化合物半導体基板などである。半導体基板は、バルク型でよいし、半導体基板に絶縁領域を介して半導体層が設けられているSOI(Silicon On Insulator)型でもよい。導電体基板は、黒鉛基板、金属基板、合金基板、導電性樹脂基板などである。または、金属の窒化物を有する基板、金属の酸化物を有する基板などがある。さらには、絶縁体基板に導電体または半導体が設けられた基板、半導体基板に導電体または絶縁体が設けられた基板、導電体基板に半導体または絶縁体が設けられた基板などである。または、上掲された基板に素子が設けられたものを用いてもよい。基板に設けられる素子は、容量素子、抵抗素子、スイッチ素子、発光素子、記憶素子などである。

導電層850をマスクにして、金属酸化物層843及び絶縁層824をエッチングしてもよい。そのような工程を経たOSトランジスタの構成例を図17Aに示す。図17AのOSトランジスタ801では、金属酸化物層843および絶縁層824の端部は導電層850の端部とほぼ一致することになる。導電層850の下部のみに金属酸化物層843および絶縁層824が存在する。

図17Bに示すOSトランジスタ802は、OSトランジスタ801に導電層855、導電層856を追加したデバイス構造を有する。ソース電極およびドレイン電極として機能する一対の電極は、導電層855と導電層851との積層、および導電層856と導電層852との積層で構成される。

図15に示すOSトランジスタ800は、導電層851及び導電層852が、金属酸化物層841、842の側面と接していてもよい。そのような構成例を図17Cに示す。図17Cに示すOSトランジスタ803は、導電層851及び導電層852が金属酸化物層841の側面及び金属酸化物層842の側面と接している。

図18に、OSトランジスタの構成例を示す。図18Aは、OSトランジスタ804の上面図であり、図18Bはy5−y6線断面図であり、図18Cはx5−x6線断面図である。なお、図18Aでは、図の明瞭化のために一部の要素が省略されている。

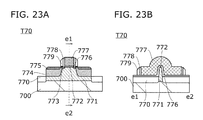

OSトランジスタは、Siトランジスタ等が作製された素子層に積層することが可能である。実施の形態1のメモリ104を、SiトランジスタとOSトランジスタとが積層されたデバイス構造とすることができる。ここでは、図19−図22を用いて、OSトランジスタを用いたメモリのデバイス構造を説明する。

本実施の形態では、酸化物半導体について説明する。ここで説明される酸化物半導体は金属酸化物であり、実施の形態4のOSトランジスタの金属酸化物層841−843適用することが可能である。

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体とに分けられる。非単結晶酸化物半導体としては、CAAC−OS(C Axis Aligned Crystalline Oxide Semiconductor)、多結晶酸化物半導体、nc−OS(nanocrystalline Oxide Semiconductor)、擬似非晶質酸化物半導体(a−like OS:amorphous like Oxide Semiconductor)、非晶質酸化物半導体などがある。

CAAC−OSは、c軸配向した複数の結晶部(ペレットともいう。)を有する酸化物半導体の一つである。

nc−OSは、高分解能TEM像において、結晶部を確認することのできる領域と、明確な結晶部を確認することのできない領域と、を有する。nc−OSに含まれる結晶部は、1nm以上10nm以下、または1nm以上3nm以下の大きさであることが多い。なお、結晶部の大きさが10nmより大きく100nm以下である酸化物半導体を微結晶酸化物半導体と呼ぶことがある。nc−OSは、例えば、高分解能TEM像では、結晶粒界を明確に確認できない場合がある。なお、ナノ結晶は、CAAC−OSにおけるペレットと起源を同じくする可能性がある。そのため、以下ではnc−OSの結晶部をペレットと呼ぶ場合がある。

a−like OSは、nc−OSと非晶質酸化物半導体との間の構造を有する酸化物半導体である。a−like OSは、高分解能TEM像において鬆が観察される場合がある。また、高分解能TEM像において、明確に結晶部を確認することのできる領域と、結晶部を確認することのできない領域と、を有する。鬆を有するため、a−like OSは、不安定な構造である。a−like OSは、電子照射によって結晶部の成長が見られる場合がある。一方、nc−OSおよびCAAC−OSは、電子照射による結晶部の成長がほとんど見られないことがわかる。即ち、a−like OSは、nc−OSおよびCAAC−OSと比べて、不安定な構造であることがわかる。

101 I/F

102 プロセッサ

103 メモリシステム

103 ワークメモリ

104 メモリ

105 ECC回路

110 ホスト装置

120 メモリセルアレイ

121 行ドライバ

122 列ドライバ

125 メモリセル

130 ユーザデータ領域

131 ファームウエア領域

132 ECC管理領域

135 ECC管理テーブル

151 メモリセル

152 メモリセル

153 メモリセル

154 メモリセル

155 メモリセル

156 メモリセル

157 メモリセル

700 単結晶シリコンウエハ

701 素子層

702 素子層

703 素子層

710 p型ウエル

711 p型不純物領域

712 p型不純物領域

713 導電体

721 導電体

722 導電体

723 導電体

731 導電体

732 導電体

741 導電体

751 導電体

752 導電体

753 導電体

754 導電体

755 導電体

756 導電体

757 導電体

770 素子分離層

771 ウエル

772 活性層

773 低濃度不純物領域

774 高濃度不純物領域

775 導電性領域

776 ゲート絶縁層

777 ゲート電極

778 側壁絶縁層

779 側壁絶縁層

800 OSトランジスタ

801 OSトランジスタ

802 OSトランジスタ

803 OSトランジスタ

804 OSトランジスタ

820 基板

821 絶縁層

822 絶縁層

823 絶縁層

824 絶縁層

825 絶縁層

840 半導体領域

841 金属酸化物層

842 金属酸化物層

843 金属酸化物層

850 導電層

851 導電層

852 導電層

853 導電層

855 導電層

856 導電層

1100 USBメモリ

1101 筐体

1102 キャップ

1103 USBコネクタ

1104 基板

1105 メモリチップ

1106 コントローラチップ

1110 SDカード

1111 筐体

1112 コネクタ

1113 基板

1114 メモリチップ

1115 コントローラチップ

1150 SSD

1151 筐体

1152 コネクタ

1153 基板

1154 メモリチップ

1155 メモリチップ

1156 コントローラチップ

1500 情報処理システム

1501 メモリシステム

1502 ホスト装置

1510 ロジック部

1511 プロセッサ

1512 メモリ部

1513 I/F

1514 バス

1521 表示装置

1522 入力装置

1700 携帯型ゲーム機

1701 筐体

1702 筐体

1703 表示部

1704 表示部

1705 マイクロフォン

1706 スピーカ

1710 ビデオカメラ

1711 筐体

1712 筐体

1713 表示部

1714 操作ボタン

1715 レンズ

1716 接続部

1720 タブレット型情報端末

1721 筐体

1722 表示部

1723 操作ボタン

1724 スピーカ

1730 情報端末

1731 筐体

1732 筐体

1733 表示部

1734 表示部

1735 接続部

1736 操作ボタン

1740 スマートフォン

1741 筐体

1742 操作ボタン

1743 マイクロフォン

1744 表示部

1745 スピーカ

1746 カメラ用レンズ

1750 ノート型PC

1751 筐体

1752 表示部

1753 キーボード

1754 ポインティングデバイス

1800 情報端末

1801 表示部

1802 筐体

1810 情報端末

1811 表示部

1812 表示部

1813 筐体

1820 情報端末

1821 表示部

1822 筐体

1823 筐体

CS1 容量素子

SN1 ノード

T70 トランジスタ

TR1 トランジスタ

TR2 トランジスタ

TR3 トランジスタ

TW1 トランジスタ

TW2 トランジスタ

TW3 トランジスタ

Claims (7)

- メモリ、回路、およびプロセッサを有するメモリシステムであって、

前記メモリは、ユーザデータ領域と、管理領域とを有し、

前記ユーザデータ領域は、複数のブロックに分割され、

前記回路は、前記複数のブロックの内のブロックから読み出されたデータのエラー検出および訂正をする機能を有し、

前記管理領域には、管理テーブルとして、前記複数のブロック別にアクセス情報が格納され、

前記アクセス情報の値は、アクセス回数が0であることを表す第1の値か、前記アクセス回数が1以上であることを表す第2の値かのいずれかをとり、

前記プロセッサは、

前記アクセス情報の値を決定する機能と、

前記管理領域に対する書き込み、および読み出しを制御する機能と、

前記ユーザデータ領域に対する書き込み、および読み出しを制御する機能と、

前記回路を制御する機能と、

を有し、

前記プロセッサは、前記ブロックの前記アクセス情報が前記第2の値である場合、前記ブロックから読み出したデータのエラー検出および訂正を前記回路に実行させない制御をするメモリシステム。 - 請求項1において、

前記プロセッサは、前記回路でエラー検出および訂正が実行されると、該当するブロックの前記アクセス情報を前記第2の値にするための制御をするメモリシステム。 - 請求項1又は2において、

前記プロセッサは、前記ユーザデータ領域に書き込みアクセスがあると、該当するブロックの前記アクセス情報を前記第2の値にするための制御をするメモリシステム。 - 請求項1乃至3の何れか一項において、

電源がオンになると、前記プロセッサは、前記管理テーブルを前記第1の値で初期化するための制御をするメモリシステム。 - 請求項1乃至4の何れか一項において、

電源をオフにするときに、前記アクセス情報が前記第1の値である前記ブロックがある場合、前記プロセッサは、前記回路において当該ブロックのデータのエラー検出および訂正がされるための制御をするメモリシステム。 - 請求項1乃至5の何れか一項において、

前記メモリは、複数のメモリセルを有し、

前記複数のメモリセルのそれぞれは、保持ノードと、前記保持ノードの充放電を制御できるトランジスタとを有し、

前記トランジスタのチャネル形成領域は酸化物半導体を有するメモリシステム。 - 請求項1乃至6の何れか一項に記載のメモリシステムと、

ホスト装置と、

を有し、

前記ホスト装置が前記ユーザデータ領域にアクセス可能なように、前記ホスト装置と前記メモリシステムとが接続されている情報処理システム。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015036768 | 2015-02-26 | ||

| JP2015036768 | 2015-02-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016164780A true JP2016164780A (ja) | 2016-09-08 |

| JP2016164780A5 JP2016164780A5 (ja) | 2019-03-28 |

Family

ID=56787957

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016035144A Withdrawn JP2016164780A (ja) | 2015-02-26 | 2016-02-26 | メモリシステム、および情報処理システム |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US9852023B2 (ja) |

| JP (1) | JP2016164780A (ja) |

| KR (2) | KR20170122771A (ja) |

| DE (1) | DE112016000926T5 (ja) |

| TW (1) | TWI696071B (ja) |

| WO (1) | WO2016135591A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020170069A1 (ja) * | 2019-02-22 | 2020-08-27 | 株式会社半導体エネルギー研究所 | エラー検出機能を有する記憶装置、半導体装置、および、電子機器 |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6901831B2 (ja) | 2015-05-26 | 2021-07-14 | 株式会社半導体エネルギー研究所 | メモリシステム、及び情報処理システム |

| SG10201701689UA (en) * | 2016-03-18 | 2017-10-30 | Semiconductor Energy Lab | Semiconductor device, semiconductor wafer, and electronic device |

| US10223194B2 (en) | 2016-11-04 | 2019-03-05 | Semiconductor Energy Laboratory Co., Ltd. | Storage device, semiconductor device, electronic device, and server system |

| JPWO2021024083A1 (ja) | 2019-08-08 | 2021-02-11 | ||

| KR20210022260A (ko) | 2019-08-20 | 2021-03-03 | 삼성전자주식회사 | 메모리 컨트롤러의 구동방법, 메모리 컨트롤러 및 스토리지 장치 |

| WO2021053453A1 (ja) * | 2019-09-20 | 2021-03-25 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP2021051399A (ja) * | 2019-09-20 | 2021-04-01 | キオクシア株式会社 | 記憶システムおよび保護方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070091678A1 (en) * | 2005-10-20 | 2007-04-26 | Fujitsu Limited | Memory system and operating method of same |

| JP2011187950A (ja) * | 2010-02-12 | 2011-09-22 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体装置の駆動方法 |

| JP2015036905A (ja) * | 2013-08-14 | 2015-02-23 | ソニー株式会社 | 記憶制御装置、ホストコンピュータ、情報処理システムおよび記憶制御装置の制御方法 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4073799B2 (ja) * | 2003-02-07 | 2008-04-09 | 株式会社ルネサステクノロジ | メモリシステム |

| JP2005078378A (ja) * | 2003-08-29 | 2005-03-24 | Sony Corp | データ記憶装置及び不揮発性メモリに対するデータ書き込み方法 |

| JP2008287404A (ja) | 2007-05-16 | 2008-11-27 | Hitachi Ltd | 読み出しによる非アクセスメモリセルのデータ破壊を検出及び回復する装置、及びその方法 |

| JP2009087509A (ja) * | 2007-10-03 | 2009-04-23 | Toshiba Corp | 半導体記憶装置 |

| JPWO2011013351A1 (ja) | 2009-07-30 | 2013-01-07 | パナソニック株式会社 | アクセス装置およびメモリコントローラ |

| JP5612514B2 (ja) | 2010-03-24 | 2014-10-22 | パナソニック株式会社 | 不揮発性メモリコントローラ及び不揮発性記憶装置 |

| US20130254463A1 (en) | 2012-03-23 | 2013-09-26 | Kabushiki Kaisha Toshiba | Memory system |

-

2016

- 2016-02-18 KR KR1020177026159A patent/KR20170122771A/ko not_active Application Discontinuation

- 2016-02-18 WO PCT/IB2016/050865 patent/WO2016135591A1/en active Application Filing

- 2016-02-18 DE DE112016000926.7T patent/DE112016000926T5/de active Pending

- 2016-02-18 KR KR1020227043138A patent/KR20230003301A/ko not_active Application Discontinuation

- 2016-02-19 US US15/047,729 patent/US9852023B2/en not_active Expired - Fee Related

- 2016-02-22 TW TW105105184A patent/TWI696071B/zh not_active IP Right Cessation

- 2016-02-26 JP JP2016035144A patent/JP2016164780A/ja not_active Withdrawn

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070091678A1 (en) * | 2005-10-20 | 2007-04-26 | Fujitsu Limited | Memory system and operating method of same |

| JP2007115013A (ja) * | 2005-10-20 | 2007-05-10 | Fujitsu Ltd | メモリシステムおよびメモリシステムの動作方法 |

| JP2011187950A (ja) * | 2010-02-12 | 2011-09-22 | Semiconductor Energy Lab Co Ltd | 半導体装置および半導体装置の駆動方法 |

| JP2015036905A (ja) * | 2013-08-14 | 2015-02-23 | ソニー株式会社 | 記憶制御装置、ホストコンピュータ、情報処理システムおよび記憶制御装置の制御方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020170069A1 (ja) * | 2019-02-22 | 2020-08-27 | 株式会社半導体エネルギー研究所 | エラー検出機能を有する記憶装置、半導体装置、および、電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI696071B (zh) | 2020-06-11 |

| KR20230003301A (ko) | 2023-01-05 |

| KR20170122771A (ko) | 2017-11-06 |

| WO2016135591A1 (en) | 2016-09-01 |

| DE112016000926T5 (de) | 2017-11-09 |

| US9852023B2 (en) | 2017-12-26 |

| US20160253236A1 (en) | 2016-09-01 |

| TW201643723A (zh) | 2016-12-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11985828B2 (en) | Semiconductor device, semiconductor wafer, memory device, and electronic device | |

| JP2016164780A (ja) | メモリシステム、および情報処理システム | |

| JP6549422B2 (ja) | 半導体装置 | |

| JP6717604B2 (ja) | 半導体装置、中央処理装置及び電子機器 | |

| US10205452B2 (en) | Logic circuit, semiconductor device, electronic component, and electronic device | |

| US9721953B2 (en) | Semiconductor device | |

| US9424890B2 (en) | Semiconductor device and driving method thereof | |

| JP6683491B2 (ja) | 半導体装置 | |

| JP2020145473A (ja) | 半導体装置 | |

| US10936410B2 (en) | Memory system and information processing system | |

| JP2016105474A (ja) | 半導体装置及び記憶装置 | |

| JP2016225617A (ja) | 記憶装置、又は該記憶装置を有する電子機器 | |

| JP2016194966A (ja) | 記憶装置、半導体装置、および電子機器 | |

| JP2016115388A (ja) | 記憶装置、およびそれを有する半導体装置 | |

| JP2017107194A (ja) | 表示装置、入出力装置、情報処理装置、情報処理装置の駆動方法 | |

| JP2016105590A (ja) | 論理回路、および論理回路を有する半導体装置 | |

| US20170270977A1 (en) | Semiconductor device, driver ic, computer and electronic device | |

| JP2016146475A (ja) | 半導体装置およびその作製方法 | |

| JP2016110679A (ja) | 記憶装置、およびそれを有する半導体装置 | |

| JP2016092084A (ja) | 半導体装置、半導体装置の作製方法、モジュールおよび電子機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190213 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190924 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200407 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20201013 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20201202 |