JP2012522369A - ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造 - Google Patents

ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造 Download PDFInfo

- Publication number

- JP2012522369A JP2012522369A JP2012502017A JP2012502017A JP2012522369A JP 2012522369 A JP2012522369 A JP 2012522369A JP 2012502017 A JP2012502017 A JP 2012502017A JP 2012502017 A JP2012502017 A JP 2012502017A JP 2012522369 A JP2012522369 A JP 2012522369A

- Authority

- JP

- Japan

- Prior art keywords

- zone

- fet

- extension

- dopant

- type

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 122

- 230000005669 field effect Effects 0.000 title claims abstract description 7

- 125000001475 halogen functional group Chemical group 0.000 title abstract description 13

- 239000004065 semiconductor Substances 0.000 claims abstract description 743

- 239000002019 doping agent Substances 0.000 claims description 2346

- 239000000463 material Substances 0.000 claims description 686

- 238000000034 method Methods 0.000 claims description 70

- 239000002131 composite material Substances 0.000 claims description 9

- 238000010276 construction Methods 0.000 claims description 3

- 125000005843 halogen group Chemical group 0.000 description 742

- 239000002243 precursor Substances 0.000 description 492

- 108091006146 Channels Proteins 0.000 description 414

- 239000010410 layer Substances 0.000 description 411

- 238000009826 distribution Methods 0.000 description 284

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 244

- 239000007943 implant Substances 0.000 description 186

- 238000002513 implantation Methods 0.000 description 170

- 229920002120 photoresistant polymer Polymers 0.000 description 162

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 152

- 150000002500 ions Chemical class 0.000 description 135

- 229910052757 nitrogen Inorganic materials 0.000 description 124

- 238000005468 ion implantation Methods 0.000 description 123

- 125000004429 atom Chemical group 0.000 description 110

- 230000000875 corresponding effect Effects 0.000 description 90

- 239000000758 substrate Substances 0.000 description 88

- 230000006870 function Effects 0.000 description 82

- 230000002829 reductive effect Effects 0.000 description 78

- 230000007423 decrease Effects 0.000 description 70

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 67

- 229910052796 boron Inorganic materials 0.000 description 66

- 238000002347 injection Methods 0.000 description 55

- 239000007924 injection Substances 0.000 description 55

- 239000002245 particle Substances 0.000 description 54

- 230000000295 complement effect Effects 0.000 description 49

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 45

- 230000005684 electric field Effects 0.000 description 45

- 229910052785 arsenic Inorganic materials 0.000 description 44

- 230000015556 catabolic process Effects 0.000 description 44

- 125000006850 spacer group Chemical group 0.000 description 41

- 238000009792 diffusion process Methods 0.000 description 40

- 230000008569 process Effects 0.000 description 40

- 229910052751 metal Inorganic materials 0.000 description 37

- 239000002184 metal Substances 0.000 description 37

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 34

- 229920005591 polysilicon Polymers 0.000 description 33

- 229910021332 silicide Inorganic materials 0.000 description 33

- 239000002800 charge carrier Substances 0.000 description 32

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 32

- 230000008859 change Effects 0.000 description 30

- 229910052698 phosphorus Inorganic materials 0.000 description 30

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 29

- 239000011574 phosphorus Substances 0.000 description 29

- 239000012212 insulator Substances 0.000 description 28

- 238000002955 isolation Methods 0.000 description 27

- 230000015572 biosynthetic process Effects 0.000 description 25

- 239000008186 active pharmaceutical agent Substances 0.000 description 17

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 17

- 230000003071 parasitic effect Effects 0.000 description 17

- 230000000694 effects Effects 0.000 description 16

- 238000000926 separation method Methods 0.000 description 16

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 14

- 229910052814 silicon oxide Inorganic materials 0.000 description 14

- 229910052710 silicon Inorganic materials 0.000 description 13

- 239000010703 silicon Substances 0.000 description 13

- 230000009467 reduction Effects 0.000 description 12

- 230000008901 benefit Effects 0.000 description 10

- 230000003247 decreasing effect Effects 0.000 description 9

- 239000003989 dielectric material Substances 0.000 description 9

- 150000004767 nitrides Chemical group 0.000 description 9

- 238000012545 processing Methods 0.000 description 9

- 230000008439 repair process Effects 0.000 description 9

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 8

- 239000003795 chemical substances by application Substances 0.000 description 8

- 238000013461 design Methods 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 8

- 229910052760 oxygen Inorganic materials 0.000 description 8

- 239000001301 oxygen Substances 0.000 description 8

- 230000036961 partial effect Effects 0.000 description 8

- 239000013078 crystal Substances 0.000 description 7

- 230000004048 modification Effects 0.000 description 7

- 238000012986 modification Methods 0.000 description 7

- 238000000137 annealing Methods 0.000 description 6

- 230000000873 masking effect Effects 0.000 description 6

- 238000005121 nitriding Methods 0.000 description 6

- 229910052787 antimony Inorganic materials 0.000 description 5

- WATWJIUSRGPENY-UHFFFAOYSA-N antimony atom Chemical compound [Sb] WATWJIUSRGPENY-UHFFFAOYSA-N 0.000 description 5

- 230000000903 blocking effect Effects 0.000 description 5

- 238000009279 wet oxidation reaction Methods 0.000 description 5

- 210000000746 body region Anatomy 0.000 description 4

- 150000001875 compounds Chemical class 0.000 description 4

- 238000005094 computer simulation Methods 0.000 description 4

- 238000011049 filling Methods 0.000 description 4

- 238000012546 transfer Methods 0.000 description 4

- 230000007704 transition Effects 0.000 description 4

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 3

- 101100189356 Mus musculus Papolb gene Proteins 0.000 description 3

- 238000013459 approach Methods 0.000 description 3

- -1 boron ions Chemical class 0.000 description 3

- 239000000969 carrier Substances 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 238000000151 deposition Methods 0.000 description 3

- 229910052733 gallium Inorganic materials 0.000 description 3

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000010931 gold Substances 0.000 description 3

- 238000010348 incorporation Methods 0.000 description 3

- 229910052738 indium Inorganic materials 0.000 description 3

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 3

- 230000035515 penetration Effects 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- 238000007789 sealing Methods 0.000 description 3

- 229910052717 sulfur Inorganic materials 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 239000003990 capacitor Substances 0.000 description 2

- 230000005465 channeling Effects 0.000 description 2

- 229910017052 cobalt Inorganic materials 0.000 description 2

- 239000010941 cobalt Substances 0.000 description 2

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 2

- 230000008878 coupling Effects 0.000 description 2

- 238000010168 coupling process Methods 0.000 description 2

- 238000005859 coupling reaction Methods 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000007872 degassing Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 239000007789 gas Substances 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000001307 helium Substances 0.000 description 2

- 229910052734 helium Inorganic materials 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 229910052739 hydrogen Inorganic materials 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 238000005457 optimization Methods 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 238000005036 potential barrier Methods 0.000 description 2

- 238000004080 punching Methods 0.000 description 2

- 238000009877 rendering Methods 0.000 description 2

- 229920006395 saturated elastomer Polymers 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 238000004088 simulation Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- ZXEYZECDXFPJRJ-UHFFFAOYSA-N $l^{3}-silane;platinum Chemical compound [SiH3].[Pt] ZXEYZECDXFPJRJ-UHFFFAOYSA-N 0.000 description 1

- 108010075750 P-Type Calcium Channels Proteins 0.000 description 1

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- 230000000996 additive effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 238000004458 analytical method Methods 0.000 description 1

- 230000009286 beneficial effect Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000004581 coalescence Methods 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 239000012777 electrically insulating material Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- BHEPBYXIRTUNPN-UHFFFAOYSA-N hydridophosphorus(.) (triplet) Chemical compound [PH] BHEPBYXIRTUNPN-UHFFFAOYSA-N 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000005527 interface trap Effects 0.000 description 1

- 230000005596 ionic collisions Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910021334 nickel silicide Inorganic materials 0.000 description 1

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 1

- 125000004433 nitrogen atom Chemical group N* 0.000 description 1

- 238000010606 normalization Methods 0.000 description 1

- 238000012856 packing Methods 0.000 description 1

- 229910021339 platinum silicide Inorganic materials 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 230000011218 segmentation Effects 0.000 description 1

- SBEQWOXEGHQIMW-UHFFFAOYSA-N silicon Chemical compound [Si].[Si] SBEQWOXEGHQIMW-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 230000007480 spreading Effects 0.000 description 1

- 238000003892 spreading Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 229910052714 tellurium Inorganic materials 0.000 description 1

- 238000003949 trap density measurement Methods 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 238000007704 wet chemistry method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

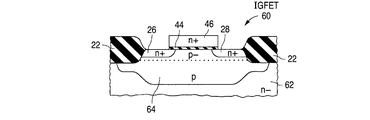

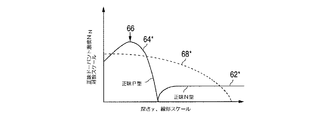

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/013—Manufacturing their source or drain regions, e.g. silicided source or drain regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

- H01L21/2652—Through-implantation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0221—Manufacture or treatment of FETs having insulated gates [IGFET] having asymmetry in the channel direction, e.g. lateral high-voltage MISFETs having drain offset region or extended-drain MOSFETs [EDMOS]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

- H10D30/603—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs having asymmetry in the channel direction, e.g. lateral high-voltage MISFETs having drain offset region or extended drain IGFETs [EDMOS]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

- H10D62/116—Dielectric isolations, e.g. air gaps adjoining the input or output regions of field-effect devices, e.g. adjoining source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/149—Source or drain regions of field-effect devices

- H10D62/151—Source or drain regions of field-effect devices of IGFETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/213—Channel regions of field-effect devices

- H10D62/221—Channel regions of field-effect devices of FETs

- H10D62/235—Channel regions of field-effect devices of FETs of IGFETs

- H10D62/299—Channel regions of field-effect devices of FETs of IGFETs having lateral doping variations

- H10D62/307—Channel regions of field-effect devices of FETs of IGFETs having lateral doping variations the doping variations being parallel to the channel lengths

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/351—Substrate regions of field-effect devices

- H10D62/357—Substrate regions of field-effect devices of FETs

- H10D62/364—Substrate regions of field-effect devices of FETs of IGFETs

- H10D62/371—Inactive supplementary semiconductor regions, e.g. for preventing punch-through, improving capacity effect or leakage current

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0128—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0167—Manufacturing their channels

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/017—Manufacturing their source or drain regions, e.g. silicided source or drain regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/02—Manufacture or treatment characterised by using material-based technologies

- H10D84/03—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology

- H10D84/038—Manufacture or treatment characterised by using material-based technologies using Group IV technology, e.g. silicon technology or silicon-carbide [SiC] technology using silicon technology, e.g. SiGe

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/2658—Bombardment with radiation with high-energy radiation producing ion implantation of a molecular ion, e.g. decaborane

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/213—Channel regions of field-effect devices

- H10D62/221—Channel regions of field-effect devices of FETs

- H10D62/235—Channel regions of field-effect devices of FETs of IGFETs

- H10D62/314—Channel regions of field-effect devices of FETs of IGFETs having vertical doping variations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/60—Electrodes characterised by their materials

- H10D64/66—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes

- H10D64/68—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator

- H10D64/693—Electrodes having a conductor capacitively coupled to a semiconductor by an insulator, e.g. MIS electrodes characterised by the insulator, e.g. by the gate insulator the insulator comprising nitrogen, e.g. nitrides, oxynitrides or nitrogen-doped materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

- H10D84/0123—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs

- H10D84/0126—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs

- H10D84/0165—Integrating together multiple components covered by H10D12/00 or H10D30/00, e.g. integrating multiple IGBTs the components including insulated gates, e.g. IGFETs the components including complementary IGFETs, e.g. CMOS devices

- H10D84/0191—Manufacturing their doped wells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/82—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components

- H10D84/83—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs of only field-effect components of only insulated-gate FETs [IGFET]

- H10D84/85—Complementary IGFETs, e.g. CMOS

- H10D84/856—Complementary IGFETs, e.g. CMOS the complementary IGFETs having different architectures than each other, e.g. high-voltage and low-voltage CMOS

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- High Energy & Nuclear Physics (AREA)

- General Physics & Mathematics (AREA)

- Toxicology (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Health & Medical Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/382,971 US8084827B2 (en) | 2009-03-27 | 2009-03-27 | Structure and fabrication of like-polarity field-effect transistors having different configurations of source/drain extensions, halo pockets, and gate dielectric thicknesses |

| US12/382,971 | 2009-03-27 | ||

| PCT/US2010/000898 WO2010110902A1 (en) | 2009-03-27 | 2010-03-25 | Structure and fabrication of like-polarity field-effect transistors having different configurations of source/drain extensions, halo pockets, and gate dielectric thicknesses |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012522369A true JP2012522369A (ja) | 2012-09-20 |

| JP2012522369A5 JP2012522369A5 (enExample) | 2013-05-09 |

Family

ID=42781346

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012502017A Pending JP2012522369A (ja) | 2009-03-27 | 2010-03-25 | ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US8084827B2 (enExample) |

| EP (1) | EP2412016A4 (enExample) |

| JP (1) | JP2012522369A (enExample) |

| KR (1) | KR20110133622A (enExample) |

| CN (1) | CN102365730A (enExample) |

| TW (1) | TW201101463A (enExample) |

| WO (1) | WO2010110902A1 (enExample) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8482076B2 (en) * | 2009-09-16 | 2013-07-09 | International Business Machines Corporation | Method and structure for differential silicide and recessed or raised source/drain to improve field effect transistor |

| US20110291193A1 (en) * | 2010-05-27 | 2011-12-01 | International Business Machines Corporation | High density butted junction cmos inverter, and making and layout of same |

| JP6043193B2 (ja) * | 2013-01-28 | 2016-12-14 | 株式会社東芝 | トンネルトランジスタ |

| KR102180554B1 (ko) | 2013-12-04 | 2020-11-19 | 삼성디스플레이 주식회사 | 박막 트랜지스터 및 이의 제조 방법 |

| US9324783B2 (en) * | 2014-09-30 | 2016-04-26 | Infineon Technologies Ag | Soft switching semiconductor device and method for producing thereof |

| CN109980009B (zh) * | 2017-12-28 | 2020-11-03 | 无锡华润上华科技有限公司 | 一种半导体器件的制造方法和集成半导体器件 |

| CN109980010B (zh) * | 2017-12-28 | 2020-10-13 | 无锡华润上华科技有限公司 | 一种半导体器件的制造方法和集成半导体器件 |

| FR3099638A1 (fr) * | 2019-07-31 | 2021-02-05 | Stmicroelectronics (Rousset) Sas | Procédé de fabrication comprenant une définition d’une longueur effective de canal de transistors MOSFET |

| US11455452B2 (en) * | 2019-09-23 | 2022-09-27 | Texas Instruments Incorporated | Variable implant and wafer-level feed-forward for dopant dose optimization |

| CN111785777B (zh) * | 2020-06-28 | 2023-10-20 | 上海华虹宏力半导体制造有限公司 | 高压cmos器件及其制造方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0888362A (ja) * | 1994-09-19 | 1996-04-02 | Sony Corp | 半導体装置とその製造方法 |

| JP2001168210A (ja) * | 1999-10-27 | 2001-06-22 | Texas Instr Inc <Ti> | 集積回路用ドレイン拡張型トランジスタ |

| JP2004221223A (ja) * | 2003-01-14 | 2004-08-05 | Matsushita Electric Ind Co Ltd | Mis型半導体装置及びその製造方法 |

| JP2006019576A (ja) * | 2004-07-02 | 2006-01-19 | Asahi Kasei Microsystems Kk | 半導体装置及びその製造方法 |

| JP2007158090A (ja) * | 2005-12-06 | 2007-06-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2008147693A (ja) * | 2008-01-28 | 2008-06-26 | Fujitsu Ltd | 半導体装置の製造方法 |

| US20080311717A1 (en) * | 2005-08-29 | 2008-12-18 | Constantin Bulucea | Fabrication of semiconductor architecture having field-effect transistors especially suitable for analog applications |

| JP2011519469A (ja) * | 2007-10-31 | 2011-07-07 | ナショナル セミコンダクタ コーポレイション | 特にアナログ適用例に適した電界効果トランジスタを具備する半導体アーキテクチャの構成及び製造 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0083447B1 (en) | 1981-12-30 | 1989-04-26 | Thomson Components-Mostek Corporation | Triple diffused short channel device structure |

| EP0360036B1 (de) | 1988-09-20 | 1994-06-01 | Siemens Aktiengesellschaft | Planarer pn-Übergang hoher Spannungsfestigkeit |

| USH986H (en) * | 1989-06-09 | 1991-11-05 | International Business Machines Corporation | Field effect-transistor with asymmetrical structure |

| US6081010A (en) * | 1992-10-13 | 2000-06-27 | Intel Corporation | MOS semiconductor device with self-aligned punchthrough stops and method of fabrication |

| US5482878A (en) * | 1994-04-04 | 1996-01-09 | Motorola, Inc. | Method for fabricating insulated gate field effect transistor having subthreshold swing |

| US5650340A (en) * | 1994-08-18 | 1997-07-22 | Sun Microsystems, Inc. | Method of making asymmetric low power MOS devices |

| US5622880A (en) * | 1994-08-18 | 1997-04-22 | Sun Microsystems, Inc. | Method of making a low power, high performance junction transistor |

| US5744372A (en) * | 1995-04-12 | 1998-04-28 | National Semiconductor Corporation | Fabrication of complementary field-effect transistors each having multi-part channel |

| JP3714995B2 (ja) * | 1995-07-05 | 2005-11-09 | シャープ株式会社 | 半導体装置 |

| US6127700A (en) * | 1995-09-12 | 2000-10-03 | National Semiconductor Corporation | Field-effect transistor having local threshold-adjust doping |

| US5793090A (en) | 1997-01-10 | 1998-08-11 | Advanced Micro Devices, Inc. | Integrated circuit having multiple LDD and/or source/drain implant steps to enhance circuit performance |

| JPH1167786A (ja) | 1997-08-25 | 1999-03-09 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| US5952693A (en) * | 1997-09-05 | 1999-09-14 | Advanced Micro Devices, Inc. | CMOS semiconductor device comprising graded junctions with reduced junction capacitance |

| US6548842B1 (en) * | 2000-03-31 | 2003-04-15 | National Semiconductor Corporation | Field-effect transistor for alleviating short-channel effects |

| US6566204B1 (en) * | 2000-03-31 | 2003-05-20 | National Semiconductor Corporation | Use of mask shadowing and angled implantation in fabricating asymmetrical field-effect transistors |

| US7145191B1 (en) | 2000-03-31 | 2006-12-05 | National Semiconductor Corporation | P-channel field-effect transistor with reduced junction capacitance |

| US20020052083A1 (en) * | 2000-10-26 | 2002-05-02 | Xin Zhang | Cost effective split-gate process that can independently optimize the low voltage(LV) and high voltage (HV) transistors to minimize reverse short channel effects |

| US6855985B2 (en) * | 2002-09-29 | 2005-02-15 | Advanced Analogic Technologies, Inc. | Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology |

| US7176530B1 (en) * | 2004-03-17 | 2007-02-13 | National Semiconductor Corporation | Configuration and fabrication of semiconductor structure having n-channel channel-junction field-effect transistor |

| JP2006210653A (ja) * | 2005-01-28 | 2006-08-10 | Fujitsu Ltd | 半導体装置、半導体集積回路装置および半導体装置の製造方法 |

| US7397084B2 (en) * | 2005-04-01 | 2008-07-08 | Semiconductor Components Industries, L.L.C. | Semiconductor device having enhanced performance and method |

| US7642574B2 (en) * | 2005-08-29 | 2010-01-05 | National Semiconductor Corporation | Semiconductor architecture having field-effect transistors especially suitable for analog applications |

| US7419863B1 (en) * | 2005-08-29 | 2008-09-02 | National Semiconductor Corporation | Fabrication of semiconductor structure in which complementary field-effect transistors each have hypoabrupt body dopant distribution below at least one source/drain zone |

| US7468305B2 (en) * | 2006-05-01 | 2008-12-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Forming pocket and LDD regions using separate masks |

| JP2009004444A (ja) * | 2007-06-19 | 2009-01-08 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP4970185B2 (ja) * | 2007-07-30 | 2012-07-04 | 株式会社東芝 | 半導体装置及びその製造方法 |

-

2009

- 2009-03-27 US US12/382,971 patent/US8084827B2/en active Active

-

2010

- 2010-03-24 TW TW099108624A patent/TW201101463A/zh unknown

- 2010-03-25 CN CN2010800138539A patent/CN102365730A/zh active Pending

- 2010-03-25 EP EP10756493.2A patent/EP2412016A4/en not_active Withdrawn

- 2010-03-25 JP JP2012502017A patent/JP2012522369A/ja active Pending

- 2010-03-25 KR KR1020117025429A patent/KR20110133622A/ko not_active Withdrawn

- 2010-03-25 WO PCT/US2010/000898 patent/WO2010110902A1/en not_active Ceased

-

2011

- 2011-11-09 US US13/293,096 patent/US8377768B2/en active Active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0888362A (ja) * | 1994-09-19 | 1996-04-02 | Sony Corp | 半導体装置とその製造方法 |

| JP2001168210A (ja) * | 1999-10-27 | 2001-06-22 | Texas Instr Inc <Ti> | 集積回路用ドレイン拡張型トランジスタ |

| JP2004221223A (ja) * | 2003-01-14 | 2004-08-05 | Matsushita Electric Ind Co Ltd | Mis型半導体装置及びその製造方法 |

| JP2006019576A (ja) * | 2004-07-02 | 2006-01-19 | Asahi Kasei Microsystems Kk | 半導体装置及びその製造方法 |

| US20080311717A1 (en) * | 2005-08-29 | 2008-12-18 | Constantin Bulucea | Fabrication of semiconductor architecture having field-effect transistors especially suitable for analog applications |

| JP2007158090A (ja) * | 2005-12-06 | 2007-06-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2011519469A (ja) * | 2007-10-31 | 2011-07-07 | ナショナル セミコンダクタ コーポレイション | 特にアナログ適用例に適した電界効果トランジスタを具備する半導体アーキテクチャの構成及び製造 |

| JP2008147693A (ja) * | 2008-01-28 | 2008-06-26 | Fujitsu Ltd | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100244149A1 (en) | 2010-09-30 |

| US8084827B2 (en) | 2011-12-27 |

| EP2412016A4 (en) | 2014-03-19 |

| CN102365730A (zh) | 2012-02-29 |

| WO2010110902A1 (en) | 2010-09-30 |

| TW201101463A (en) | 2011-01-01 |

| US8377768B2 (en) | 2013-02-19 |

| US20120264263A1 (en) | 2012-10-18 |

| KR20110133622A (ko) | 2011-12-13 |

| EP2412016A1 (en) | 2012-02-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2012522361A (ja) | ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造 | |

| JP2012522364A (ja) | 空のウエル及び充填したウエルを使用した半導体構成体の構成及び製造 | |

| JP2012522363A (ja) | 延長型ドレイン電界効果トランジスタを有する半導体構成体の構成及び製造 | |

| JP2012522366A (ja) | 電界効果トランジスタのソース延長部及びドレイン延長部が異なるドーパントで画定される半導体構成体の構成及び製造 | |

| JP2012522371A (ja) | ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造 | |

| JP2012522369A (ja) | ソース/ドレイン延長部、ハローポケット及びゲート誘電体厚さの異なる構成を有する同極性の電界効果トランジスタの構成及び製造 | |

| JP2012522368A (ja) | L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体 | |

| JP2012522365A (ja) | 非対称的チャンネルゾーン及び異なる構成としたソース/ドレイン延長部を有する非対称的電界効果トランジスタの構成及び製造 | |

| JP2012522370A (ja) | 調整した垂直窒素濃度分布を具備する窒化ゲート誘電体層を有する電界効果トランジスタの構成及び製造 | |

| JP2012522367A (ja) | 複数の局所的濃度最大によって画定されたソース/ドレイン延長部を有する電界効果トランジスタの構成及び製造 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130321 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20130321 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20140313 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140416 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140430 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20141014 |