JP2012198822A - 情報処理装置、制御装置および異常ユニット判定方法 - Google Patents

情報処理装置、制御装置および異常ユニット判定方法 Download PDFInfo

- Publication number

- JP2012198822A JP2012198822A JP2011063404A JP2011063404A JP2012198822A JP 2012198822 A JP2012198822 A JP 2012198822A JP 2011063404 A JP2011063404 A JP 2011063404A JP 2011063404 A JP2011063404 A JP 2011063404A JP 2012198822 A JP2012198822 A JP 2012198822A

- Authority

- JP

- Japan

- Prior art keywords

- unit

- abnormal

- abnormality

- access

- svc

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/2002—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant

- G06F11/2005—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant using redundant communication controllers

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/16—Error detection or correction of the data by redundancy in hardware

- G06F11/20—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements

- G06F11/2002—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant

- G06F11/2007—Error detection or correction of the data by redundancy in hardware using active fault-masking, e.g. by switching out faulty elements or by switching in spare elements where interconnections or communication control functionality are redundant using redundant communication media

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/42—Bus transfer protocol, e.g. handshake; Synchronisation

- G06F13/4282—Bus transfer protocol, e.g. handshake; Synchronisation on a serial bus, e.g. I2C bus, SPI bus

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/0016—Inter-integrated circuit (I2C)

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Quality & Reliability (AREA)

- Hardware Redundancy (AREA)

- Debugging And Monitoring (AREA)

Abstract

【解決手段】I2Cバス装置9は、I2Cバスで接続する複数のI2Cスレーブユニット3を制御するI2Cマスタユニット1Aと、複数のI2Cスレーブユニット3を制御し、I2Cマスタユニット1Aと二重化されたI2Cマスタユニット2とを有し、I2Cマスタユニット1Aは、自ユニットと接続されたI2Cスレーブユニット3へのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、I2Cマスタユニット1Bと接続されたI2Cスレーブユニット3へのI2Cマスタユニット1Bからのアクセス結果とを用いて、異常となるユニットを判定する制御部30を有する。

【選択図】図1

Description

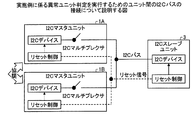

次に、図1は、本実施例に係るI2Cバス装置の構成を示す機能ブロック図である。図1に示すように、I2Cバス装置9は、I2Cマスタユニット1Aと、I2Cマスタユニット1Bと、I2Cスレーブユニット3とを備える。I2Cバス装置9は、例えば、複数のハードディスクを有するストレージデバイス格納筐体(DE)およびハードディスク以外のユニットが搭載された筐体(CE)を備えるストレージ装置である。I2Cマスタユニット1Aは、サービスコントローラ(SVC:Service Controller)といい、I2Cバスで接続する複数のI2Cスレーブユニット3を制御したり、監視したりする。I2Cマスタユニット1Aは、I2Cマスタユニット1Bと冗長構成であり、運用系となったり、待機系となったりする。以降の説明では、I2Cマスタユニット1Aが、運用系であるものとして説明する。そして、I2Cマスタユニット1Bは、I2Cマスタユニット1Aと同様の構成であるので、その説明を省略する。

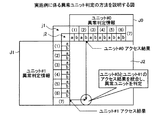

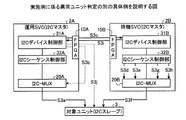

ここで、異常判定部31aによる異常箇所判定について、図3を参照しながら説明する。図3は、実施例に係る異常箇所判定を説明する図である。なお、図3では、運用SVC2Aが運用系のI2Cマスタユニットに相当し、待機SVC2Bが待機系のI2Cマスタユニットに相当するものとする。図3に示すように、運用SVC2Aは、待機SVC2Bと二重化され、自己に搭載されたI2C−MUX20Aを介して、対象ユニット3とI2Cバスで接続する。なお、説明内の「 」内の符号は、各異常種別を表すものとする。

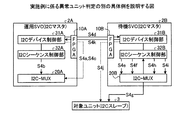

次に、異常ユニット判定マトリクス41の一例について、図4を参照しながら説明する。図4は、異常ユニット判定マトリクス41の一例を示す図である。図4に示すように、異常ユニット判定マトリクス41は、横軸に運用SVCの異常判定情報41A、縦軸に待機SVCの異常判定情報41Bを記憶する。運用SVCの異常判定情報41Aには、異常となる可能性のある箇所と異常内容とからなる異常種別(正常を含む)を複数記憶する。待機SVCの異常判定情報41Bには、運用SVCの異常判定情報41Aと同様に異常種別を複数記憶する。

次に、運用SVC2Aから対象ユニット3へのアクセスで異常となる異常箇所があった場合に、異常箇所に基づいて異常ユニットを判定する具体例を、図5〜図8を参照しながら説明する。

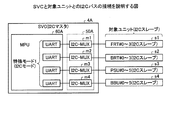

次に、実施例に係る異常ユニット判定を実行するためのI2Cバス装置について、図9を参照しながら説明する。図9は、実施例に係る異常ユニット判定を実行するためのI2Cバス装置の一例を説明する図である。図9に示すように、I2Cバス装置9Aは、ハードディスクが搭載される筐体(DE:Device Enclosure)とハードディスク以外のユニットが搭載される筐体(CE:Controller Enclosure)を有する。DEには、複数のハードディスク(Hard Disk)が搭載されている。また、CEには、ユニットの動作を管理するユニット(CM:Control Module)、CM間の通信手段を提供するユニット(FRT:Frontend Router)、CMにハードディスクへのアクセス手段を提供するユニット(BRT:Backend Router)が搭載されている。また、CEには、CEに搭載される全ユニットに電力を供給するユニット(PSU:Power Supply Unit)、停電発生時に特定のユニットに電力を供給するユニット(BBU:Battery Backup Unit)が搭載されている。さらに、CEには、ユーザの操作により自装置に電源を投入したり切断したりするユニット(Panel)および自装置を制御したり監視したりするユニット(SVC:Service Controller)が搭載されている。なお、SVC4Aが図1のI2Cマスタユニット1Aに相当し、SVC4Bが図1のI2Cマスタユニット1Bに相当する。また、符号5で表したFRT、BRT、PSUおよびBBUが図1のI2Cスレーブユニット3(対象ユニット)に相当する。

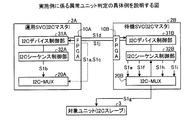

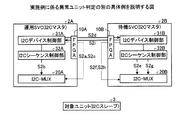

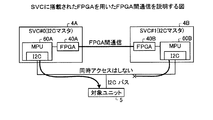

次に、実施例に係る異常ユニット判定を実行するためのハードウェアの全体構成について、図10を参照しながら説明する。図10は、実施例に係る異常ユニット判定を実行するためのハードウェアの全体構成の一例を説明する図である。図10に示すように、SVC4Aは、FPGA40A、I2C−MUX50AおよびMPU60Aを有する。SVC4Aは、SVC4Bと冗長構成となっている。また、SVC4Aは、SVC4Bと、それぞれに搭載されたFPGA40A、40Bを介して接続する。また、SVC4Aは、I2C−MUX50Aを介して、対象ユニット5とI2Cバスで接続する。

次に、実施例に係る異常ユニット判定処理の手順を、図15A〜図20を参照して説明する。図15A〜図17では、運用SVCの異常ユニット判定処理の手順を示し、図18〜図20では、待機SVCの異常ユニット判定処理の手順を示す。

続いて、異常箇所判定部31aは、運用SVC上のI2C−MUXのリセット回数を0にクリアする(ステップS13)。そして、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、I2C−MUX20の接続状態(ステータス)を読み取る(ステップS14)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS15)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS15;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS16)。ここでは、異常の発生箇所をI2C−MUX20のステータスを確認する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e1」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS71からの「待機SVCへのアクセス依頼」に移行する。

次に、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、運用SVC上のI2C−MUX20を対象ユニット3と接続する(ステップS31)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS32)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS32;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS33)。ここでは、異常の発生箇所をI2C−MUX20を対象ユニット3と接続する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e3」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS71からの「待機SVCへのアクセス依頼」に移行する。

次に、異常箇所判定部31aは、対象ユニット3のI2Cデバイスへの操作内容が書き込みのみか否かを判定する(ステップS41)。対象ユニット3のI2Cデバイスへの操作内容が書き込みのみであると判定した場合(ステップS41;Yes)、異常箇所判定部31aは、ステップS51からの「対象ユニットへの書込異常判定」に移行する。

次に、異常箇所判定部31aは、運用SVC側から接続した対象ユニット3のI2Cデバイスのレジスタへデータを書き込む(ステップS51)。そして、異常箇所判定部31aは、I2Cデバイスへのアクセスで異常があるか否かを判定する(ステップS52)。I2Cデバイスへのアクセスで異常があると判定した場合(ステップS52;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS53)。ここでは、異常の発生箇所を対象ユニットとアクセスする箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e6」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS71からの「待機SVCへのアクセス依頼」に移行する。

次に、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、運用SVC上のI2C−MUX20を対象ユニット3から切断する(ステップS61)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS62)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS62;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS63)。ここでは、異常の発生箇所をI2C−MUX20を対象ユニット3から切断したことを確認する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e8」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS71からの「待機SVCへのアクセス依頼」に移行する。

図16は、待機SVCへのアクセス依頼の手順を示すフローチャートである。

図17は、異常ユニット判定の手順を示すフローチャートである。

図18は、待機SVCのアクセス依頼待ちの手順を示すフローチャートである。

対象ユニット3へのアクセス依頼を受け取った異常箇所判定部31aは、待機SVC上のI2C−MUXのリセット回数を0にクリアする(ステップS111)。そして、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、I2C−MUX20の接続状態(ステータス)を読み取る(ステップS112)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS113)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS113;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS114)。ここでは、異常の発生箇所をI2C−MUX20のステータスを確認する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e1」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS161からの「運用SVCへのアクセス結果通知」に移行する。

次に、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、待機SVC上のI2C−MUX20を対象ユニット3と接続する(ステップS121)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS122)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS122;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS123)。ここでは、異常の発生箇所をI2C−MUX20を対象ユニット3と接続する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e3」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS161からの「運用SVCへのアクセス結果通知」に移行する。

次に、異常箇所判定部31aは、対象ユニット3のI2Cデバイスへの操作内容が書き込みのみか否かを判定する(ステップS131)。対象ユニット3のI2Cデバイスへの操作内容が書き込みのみであると判定した場合(ステップS131;Yes)、異常箇所判定部31aは、ステップS141からの「対象ユニットへの書込異常判定」に移行する。

次に、異常箇所判定部31aは、待機SVC側から接続した対象ユニット3のI2Cデバイスのレジスタへデータを書き込む(ステップS141)。そして、異常箇所判定部31aは、I2Cデバイスへのアクセスで異常があるか否かを判定する(ステップS142)。I2Cデバイスへのアクセスで異常があると判定した場合(ステップS142;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS143)。ここでは、異常の発生箇所を対象ユニットとアクセスする箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e6」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS161からの「運用SVCへのアクセス結果通知」に移行する。

次に、異常箇所判定部31aは、I2Cシーケンス制御部32を介して、待機SVC上のI2C−MUX20を対象ユニット3から切断する(ステップS151)。そして、異常箇所判定部31aは、I2C−MUX20へのアクセスで異常があるか否かを判定する(ステップS152)。I2C−MUX20へのアクセスで異常があると判定した場合(ステップS152;Yes)、異常箇所判定部31aは、異常の発生箇所と異常内容を含む異常種別をアクセス結果として記憶部40に保持する(ステップS153)。ここでは、異常の発生箇所をI2C−MUX20を対象ユニット3から切断したことを確認する箇所とし、異常内容をI2Cシーケンス異常とする異常種別「e8」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS161からの「運用SVCへのアクセス結果通知」に移行する。

40に保持する(ステップS158)。ここでは、異常の発生箇所をI2C−MUX20を対象ユニット3から切断したことを確認する箇所とし、異常内容をI2Cデバイス異常とする異常種別「e10」を記憶部40に保持する。その後、異常箇所判定部31aは、ステップS161からの「運用SVCへのアクセス結果通知」に移行する。

図20は、運用SVCへのアクセス結果通知の手順を示すフローチャートである。

上記実施例によれば、I2Cバス装置9は、I2Cマスタユニット1Aと、I2Cマスタユニット1Aと二重化されたI2Cマスタユニット1Bとを有する。そして、I2Cマスタユニット1AおよびI2Cマスタユニット1Bは、I2Cバスで接続する複数のI2Cスレーブユニット3を制御する。さらに、I2Cマスタユニット1Aは、I2Cスレーブユニット3へのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、I2Cマスタユニット1Bからのアクセス結果との組み合わせを用いて、異常であるユニットを判定する。かかる構成によれば、I2Cバス装置9は、異常を検出されたI2Cスレーブユニット3に対する2個のアクセス結果の組み合わせを用いて、異常であるユニットを判定するので、どのユニットに異常があるのかを判定できる。例えば、I2Cバス装置9は、2個のアクセス結果が同じ箇所の異常である場合には、I2Cマスタユニット1A、1Bに異常はなく、I2Cスレーブユニット3に異常があることを判定できる。また、I2Cバス装置9は、I2Cマスタユニット1Aに異常があってもI2Cマスタユニット1Bに異常がない場合は、I2Cマスタユニット1Aに異常があることを判定できる。

なお、本実施例では、I2Cバス装置1が運用中に、運用SVCであるI2Cマスタユニット1Aが対象ユニット3へのアクセスで異常があった場合に、異常ユニットを判定するものとして説明した。しかしながら、これに限定されるものではなく、I2Cバス装置1が運用中でない場合であっても、異常ユニット判定処理を行っても良い。例えば、I2Cバス装置1が事前にI2Cバス間のユニットの故障診断を行う場合であっても良い。

前記複数のスレーブユニットを制御し、前記第1のマスタユニットと二重化された第2のマスタユニットとを有し、

前記第1のマスタユニットは、

自ユニットと接続された前記スレーブユニットへのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、前記第2のマスタユニットと接続された前記スレーブユニットへの前記第2のマスタユニットからのアクセス結果とを用いて、異常であるユニットを判定する制御部

を有することを特徴とする情報処理装置。

自ユニットと接続された前記スレーブユニットへのアクセスで異常箇所があるか否かを判定する異常箇所判定部と、

前記異常箇所判定部によって前記スレーブユニットへのアクセスで異常箇所があると判定された場合に、前記スレーブユニットと同一のスレーブユニットへのアクセスを、前記第2のマスタユニットに依頼するアクセス依頼部と、

前記異常箇所判定部によって異常箇所があると判定された異常箇所に関するアクセス結果と前記アクセス依頼部による依頼の結果を示すアクセス結果との組み合わせを用いて、異常であるユニットを判定する異常ユニット判定部と

を有することを特徴とする付記1に記載の情報処理装置。

前記スレーブユニットへのアクセスでマスタユニット中の異常となる可能性のある箇所に関するアクセス情報について、二重化されたマスタユニットの一方の前記アクセス情報と他方の前記アクセス情報との組み合わせにより異常と判定されるユニットの候補を記憶する記憶部を有し、

前記異常ユニット判定部は、

さらに、前記記憶部に記憶された、二重化されたマスタユニットのそれぞれの前記アクセス情報の組み合わせを用いて、前記スレーブユニットへのアクセスで異常の原因となったユニットを判定する

ことを特徴とする付記1または付記2に記載の情報処理装置。

を有することを特徴とする制御装置。

シリアルバスで接続する複数のスレーブユニットを制御する第1のマスタユニットが前記スレーブユニットへのアクセスで異常箇所があるか否かを判定し、

前記判定する処理によって前記スレーブユニットへのアクセスで異常箇所があると判定された場合に、前記スレーブユニットと同一のスレーブユニットへのアクセスを、前記第1のマスタユニットと二重化された第2のマスタユニットに依頼し、

前記判定する処理によって異常箇所があると判定された異常箇所に関するアクセス結果と前記依頼する処理によって依頼した結果を示すアクセス結果とを用いて、異常であるユニットを判定する

処理を含むことを特徴とする異常ユニット判定方法。

3 I2Cスレーブユニット

10 FPGA

20 I2C−MUX

30 制御部

31 I2Cデバイス制御部

31a 異常箇所判定部

31b アクセス依頼部

31c 異常ユニット判定部

32 I2Cシーケンス制御部

40 記憶部

41 異常ユニット判定マトリクス

Claims (5)

- シリアルバスで接続する複数のスレーブユニットを制御する第1のマスタユニットと、

前記複数のスレーブユニットを制御し、前記第1のマスタユニットと二重化された第2のマスタユニットとを有し、

前記第1のマスタユニットは、

自ユニットと接続された前記スレーブユニットへのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、前記第2のマスタユニットと接続された前記スレーブユニットへの前記第2のマスタユニットからのアクセス結果とを用いて、異常であるユニットを判定する制御部

を有することを特徴とする情報処理装置。 - 前記制御部は、

自ユニットと接続された前記スレーブユニットへのアクセスで異常箇所があるか否かを判定する異常箇所判定部と、

前記異常箇所判定部によって前記スレーブユニットへのアクセスで異常箇所があると判定された場合に、前記スレーブユニットと同一のスレーブユニットへのアクセスを、前記第2のマスタユニットに依頼するアクセス依頼部と、

前記異常箇所判定部によって異常箇所があると判定された異常箇所に関するアクセス結果と前記アクセス依頼部による依頼の結果を示すアクセス結果との組み合わせを用いて、異常であるユニットを判定する異常ユニット判定部と

を有することを特徴とする請求項1に記載の情報処理装置。 - 前記第1のマスタユニットは、

前記スレーブユニットへのアクセスでマスタユニット中の異常となる可能性のある箇所に関するアクセス情報について、二重化されたマスタユニットの一方の前記アクセス情報と他方の前記アクセス情報との組み合わせにより異常と判定されるユニットの候補を記憶する記憶部を有し、

前記異常ユニット判定部は、

さらに、前記記憶部に記憶された、二重化されたマスタユニットのそれぞれの前記アクセス情報の組み合わせを用いて、前記スレーブユニットへのアクセスで異常の原因となったユニットを判定する

ことを特徴とする請求項1または請求項2に記載の情報処理装置。 - 自ユニットとシリアルバスで接続されたスレーブユニットへのアクセスで異常を検出したとき、異常を検出した箇所に関するアクセス結果と、自ユニットと二重化された他のマスタユニットとシリアルバスで接続された前記スレーブユニットへの他のマスタユニットからのアクセス結果とを用いて、異常であるユニットを判定する制御部

を有することを特徴とする制御装置。 - 情報処理装置によって実行される異常ユニット判定方法であって、

シリアルバスで接続する複数のスレーブユニットを制御する第1のマスタユニットが前記スレーブユニットへのアクセスで異常箇所があるか否かを判定し、

前記判定する処理によって前記スレーブユニットへのアクセスで異常箇所があると判定された場合に、前記スレーブユニットと同一のスレーブユニットへのアクセスを、前記第1のマスタユニットと二重化された第2のマスタユニットに依頼し、

前記判定する処理によって異常箇所があると判定された異常箇所に関するアクセス結果と前記依頼する処理によって依頼した結果を示すアクセス結果とを用いて、異常であるユニットを判定する

処理を含むことを特徴とする異常ユニット判定方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011063404A JP5682392B2 (ja) | 2011-03-22 | 2011-03-22 | 情報処理装置、制御装置および異常ユニット判定方法 |

| US13/346,820 US8799708B2 (en) | 2011-03-22 | 2012-01-10 | Information processing apparatus, control device, and abnormal unit determination method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2011063404A JP5682392B2 (ja) | 2011-03-22 | 2011-03-22 | 情報処理装置、制御装置および異常ユニット判定方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012198822A true JP2012198822A (ja) | 2012-10-18 |

| JP5682392B2 JP5682392B2 (ja) | 2015-03-11 |

Family

ID=46878356

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011063404A Active JP5682392B2 (ja) | 2011-03-22 | 2011-03-22 | 情報処理装置、制御装置および異常ユニット判定方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8799708B2 (ja) |

| JP (1) | JP5682392B2 (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015018315A (ja) * | 2013-07-09 | 2015-01-29 | 富士通株式会社 | ストレージ制御装置、制御装置および制御プログラム |

| JP2015099487A (ja) * | 2013-11-19 | 2015-05-28 | 富士通株式会社 | 情報処理装置,制御装置及び制御プログラム |

| KR101674529B1 (ko) * | 2015-09-09 | 2016-11-09 | 한국원자력의학원 | 다엽 콜리메이터 제어 장치 및 방법 |

| CN109189619A (zh) * | 2018-08-13 | 2019-01-11 | 光梓信息科技(上海)有限公司 | I2c总线兼容性测试方法、系统、存储介质及设备 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2013046734A1 (ja) * | 2011-09-27 | 2013-04-04 | 三菱電機株式会社 | スレーブ装置、マスター装置及び通信方法 |

| US8891405B2 (en) | 2012-07-18 | 2014-11-18 | International Business Machines Corporation | Integrated device management over Ethernet network |

| WO2015045062A1 (ja) | 2013-09-26 | 2015-04-02 | 三菱電機株式会社 | 通信システム、待機装置、通信方法及び待機プログラム |

| JP6340962B2 (ja) * | 2014-07-07 | 2018-06-13 | 富士通株式会社 | バス制御装置、データ転送システム、及びバス制御方法 |

| US9665528B2 (en) * | 2014-11-20 | 2017-05-30 | International Business Machines Corporation | Bus serialization for devices without multi-device support |

| CN105446837B (zh) * | 2015-04-02 | 2019-05-07 | 北京眼神智能科技有限公司 | 检测iic接口器件是否连接的方法、装置以及系统 |

| KR101999148B1 (ko) * | 2017-07-28 | 2019-07-11 | (주)씨드젠 | 로그 ap 탐지 시스템 및 방법과, 이를 위한 사용자 단말 및 컴퓨터 프로그램 |

| JP6886934B2 (ja) * | 2018-03-09 | 2021-06-16 | 株式会社東芝 | I/o拡張装置及び制御システム |

| JP6939665B2 (ja) * | 2018-03-15 | 2021-09-22 | オムロン株式会社 | ネットワークシステム |

| CN115658409B (zh) * | 2022-11-11 | 2023-03-14 | 苏州浪潮智能科技有限公司 | 一种异常检测方法、装置、主机设备、系统及存储介质 |

Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06214895A (ja) * | 1993-01-14 | 1994-08-05 | Mitsubishi Electric Corp | バス監視方法 |

| JPH0934809A (ja) * | 1995-07-18 | 1997-02-07 | Hitachi Ltd | 高信頼化コンピュータシステム |

| JPH10320307A (ja) * | 1997-05-19 | 1998-12-04 | Omron Corp | リモートi/oシステム |

| JP2000181501A (ja) * | 1998-12-14 | 2000-06-30 | Hitachi Ltd | 二重化制御装置 |

| JP2002132535A (ja) * | 2000-10-25 | 2002-05-10 | Chubu Electric Power Co Inc | 分散型計算機システムにおける計算機診断方式 |

| JP2005004745A (ja) * | 2003-06-12 | 2005-01-06 | Hewlett-Packard Development Co Lp | 集積回路間バスルータ |

| JP2009003613A (ja) * | 2007-06-20 | 2009-01-08 | Fujitsu Ltd | バス障害検出方法及びバスシステム |

| JP2010033120A (ja) * | 2008-07-25 | 2010-02-12 | Yokogawa Electric Corp | 二重化制御システム |

| JP2010055472A (ja) * | 2008-08-29 | 2010-03-11 | Internatl Business Mach Corp <Ibm> | シリアルバスシステム、ハングアップスレーブ特定方法及びハングアップスレーブ特定プログラム |

| US20100131801A1 (en) * | 2008-11-21 | 2010-05-27 | Stmicroelectronics S.R.L. | Electronic system for detecting a fault |

| JP2010211810A (ja) * | 2004-05-20 | 2010-09-24 | Qualcomm Inc | 単線バス及び3線バスの相互運用性 |

| JP2010250129A (ja) * | 2009-04-16 | 2010-11-04 | Canon Inc | 画像形成装置 |

-

2011

- 2011-03-22 JP JP2011063404A patent/JP5682392B2/ja active Active

-

2012

- 2012-01-10 US US13/346,820 patent/US8799708B2/en active Active

Patent Citations (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06214895A (ja) * | 1993-01-14 | 1994-08-05 | Mitsubishi Electric Corp | バス監視方法 |

| JPH0934809A (ja) * | 1995-07-18 | 1997-02-07 | Hitachi Ltd | 高信頼化コンピュータシステム |

| JPH10320307A (ja) * | 1997-05-19 | 1998-12-04 | Omron Corp | リモートi/oシステム |

| JP2000181501A (ja) * | 1998-12-14 | 2000-06-30 | Hitachi Ltd | 二重化制御装置 |

| JP2002132535A (ja) * | 2000-10-25 | 2002-05-10 | Chubu Electric Power Co Inc | 分散型計算機システムにおける計算機診断方式 |

| JP2005004745A (ja) * | 2003-06-12 | 2005-01-06 | Hewlett-Packard Development Co Lp | 集積回路間バスルータ |

| JP2010211810A (ja) * | 2004-05-20 | 2010-09-24 | Qualcomm Inc | 単線バス及び3線バスの相互運用性 |

| JP2009003613A (ja) * | 2007-06-20 | 2009-01-08 | Fujitsu Ltd | バス障害検出方法及びバスシステム |

| JP2010033120A (ja) * | 2008-07-25 | 2010-02-12 | Yokogawa Electric Corp | 二重化制御システム |

| JP2010055472A (ja) * | 2008-08-29 | 2010-03-11 | Internatl Business Mach Corp <Ibm> | シリアルバスシステム、ハングアップスレーブ特定方法及びハングアップスレーブ特定プログラム |

| US20100131801A1 (en) * | 2008-11-21 | 2010-05-27 | Stmicroelectronics S.R.L. | Electronic system for detecting a fault |

| JP2010250129A (ja) * | 2009-04-16 | 2010-11-04 | Canon Inc | 画像形成装置 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2015018315A (ja) * | 2013-07-09 | 2015-01-29 | 富士通株式会社 | ストレージ制御装置、制御装置および制御プログラム |

| US9645898B2 (en) | 2013-07-09 | 2017-05-09 | Fujitsu Limited | Storage control device and control device for detecting abnormality of signal line |

| JP2015099487A (ja) * | 2013-11-19 | 2015-05-28 | 富士通株式会社 | 情報処理装置,制御装置及び制御プログラム |

| US9727398B2 (en) | 2013-11-19 | 2017-08-08 | Fujitsu Limited | Information processing apparatus, control device, and computer-readable recording medium having stored control program |

| KR101674529B1 (ko) * | 2015-09-09 | 2016-11-09 | 한국원자력의학원 | 다엽 콜리메이터 제어 장치 및 방법 |

| CN109189619A (zh) * | 2018-08-13 | 2019-01-11 | 光梓信息科技(上海)有限公司 | I2c总线兼容性测试方法、系统、存储介质及设备 |

| CN109189619B (zh) * | 2018-08-13 | 2023-03-17 | 光梓信息科技(上海)有限公司 | I2c总线兼容性测试方法、系统、存储介质及设备 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8799708B2 (en) | 2014-08-05 |

| US20120246510A1 (en) | 2012-09-27 |

| JP5682392B2 (ja) | 2015-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5682392B2 (ja) | 情報処理装置、制御装置および異常ユニット判定方法 | |

| US8812913B2 (en) | Method and apparatus for isolating storage devices to facilitate reliable communication | |

| CN107977299B (zh) | 利用可配置和容错的基板管理控制器安排的方法及系统 | |

| CN105700510B (zh) | Can通信系统的错误分散检测方法及can通信系统 | |

| CN108153622B (zh) | 一种故障处理的方法、装置和设备 | |

| JP4770982B2 (ja) | ストレージシステム、ストレージ装置、ファームウェアの活性交換方法 | |

| JP6003350B2 (ja) | 監視装置、情報処理装置、及び監視方法 | |

| JP3620527B2 (ja) | ループ状インタフェースの障害解析方法及び障害解析機能を有するシステム | |

| US8850255B2 (en) | Storage system control apparatus and control method for utilizing a relay unit of an abnormal control unit | |

| JP2017010390A (ja) | ストレージ制御装置、ストレージ制御プログラム、およびストレージ制御方法 | |

| JP5794137B2 (ja) | 制御システムおよび中継装置 | |

| JP2017507432A (ja) | 複数のセンサを有する測定システム | |

| US20110066884A1 (en) | Power supply control device, a storage system, a control method of the power supply control device, a control method of a disk array unit and a computer readable medium thereof | |

| CN106909307B (zh) | 一种管理双活存储阵列的方法及装置 | |

| CN100418047C (zh) | 磁盘阵列装置以及其控制方法 | |

| CN102636987B (zh) | 双重化控制装置 | |

| CN105549696A (zh) | 具有机箱管理功能的机架式服务器系统 | |

| US7421596B2 (en) | Disk array system | |

| CN109491842B (zh) | 用于故障安全计算系统的模块扩展的信号配对 | |

| US9760460B2 (en) | Storage system, storage device, and monitoring server | |

| JP5332257B2 (ja) | サーバシステム、サーバ管理方法、およびそのプログラム | |

| CN120687286A (zh) | 一种故障处理方法、装置、电子设备和存储介质 | |

| US20140019646A1 (en) | Service Channel For Connecting A Host Computer To Peripheral Devices | |

| CN115408240A (zh) | 一种冗余系统主备方法、装置、设备及储存介质 | |

| CN111522698A (zh) | 前端处理器的自动切换系统及方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140108 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20140919 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140930 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20141127 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20141216 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20141229 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5682392 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |