JP2011522348A - 不揮発性メモリのための高速センスアンプアレイおよび方法 - Google Patents

不揮発性メモリのための高速センスアンプアレイおよび方法 Download PDFInfo

- Publication number

- JP2011522348A JP2011522348A JP2011511667A JP2011511667A JP2011522348A JP 2011522348 A JP2011522348 A JP 2011522348A JP 2011511667 A JP2011511667 A JP 2011511667A JP 2011511667 A JP2011511667 A JP 2011511667A JP 2011522348 A JP2011522348 A JP 2011522348A

- Authority

- JP

- Japan

- Prior art keywords

- node

- memory cell

- sensing

- circuit

- memory cells

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/26—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5642—Sensing or reading circuits; Data output circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

- G11C5/063—Voltage and signal distribution in integrated semi-conductor memory access lines, e.g. word-line, bit-line, cross-over resistance, propagation delay

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/02—Arrangements for writing information into, or reading information out from, a digital store with means for avoiding parasitic signals

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/563—Multilevel memory reading aspects

- G11C2211/5634—Reference cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/06—Sense amplifiers; Associated circuits, e.g. timing or triggering circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

Abstract

Description

したがって、大容量で高性能の不揮発性メモリに対する一般的な需要がある。特に、速度が高められていてノイズの少ない感知回路に対する需要がある。

図1〜図11は、本発明の種々の態様が実施され得るメモリシステムの例を示す。

図12〜図13は、既存の感知回路におけるノイズ問題を示す。

図16〜図19は、ノイズ問題を処理する種々の態様および実施形態を示す。

図20A〜図20Cは、感知のためのアナログ経路と重なるデータ転送のための経路を有するセンスモジュールを示す。

図21A〜図21Cは、感知のためのアナログ経路とは異なるデータ転送のための経路を有するセンスモジュールを示す。

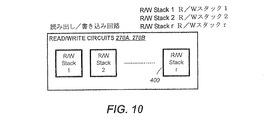

メモリアレイ200は、行デコーダ230(230A、230Bに分割されている)を介してワード線により、さらに列デコーダ260(260A、260Bに分割されている)を介してビット線によりアドレス指定可能である(図4および5も参照)。読み出し/書き込み回路270(270A、270Bに分割されている)は、1ページのメモリセルを並行して読み出すかあるいはプログラムすることができる。データI/Oバス231が読み出し/書き込み回路270に結合されている。

好ましい実施形態では、1ページは、同じワード線を共有するメモリセルの1つの連続する行から構成される。メモリセルの行が複数のページに分割される他の実施形態では、読み出し/書き込み回路270を個々のページに多重化するためにブロックマルチプレクサ250(250Aおよび250Bに分割されている)が設けられる。例えば、メモリセルの奇数列および偶数列によりそれぞれ形成される2ページが読み出し/書き込み回路に多重化される。

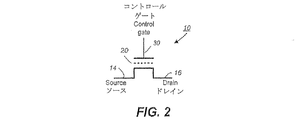

メモリアレイ200は、通例、行および列を成して配列されてワード線およびビット線によりアドレス指定可能なメモリセルの2次元アレイとして編成される。アレイはNORタイプまたはNANDタイプのアーキテクチャに従って形成され得る。

今日使用されている商業的に成功した不揮発性ソリッドステート記憶装置が多くある。これらの記憶装置は、1つ以上の電荷蓄積素子をそれぞれ有するいろいろなタイプのメモリセルを採用することができる。

図6は、一連の交互プログラム/ベリファイサイクルによって1ページのメモリセルをターゲットメモリ状態にプログラムするための代表的な手法を示す。結合されたワード線を介してメモリセルのコントロールゲートにプログラミング電圧VPGM が印加される。VPGM は、初期電圧レベルVPGM0から始まる階段波形の形の一連のプログラミング電圧パルスである。プログラミングを受けるセルは、フローティングゲートに増分電荷をそのたびに加えようとする、この一連のプログラミング電圧パルスにさらされる。プログラミングパルス間に、セルは、そのソース−ドレイン電流をブレークポイントレベルに関して判定するために読み返されるかあるいはベリファイされる。読み返しプロセスは、1つ以上の感知操作を含み得る。セルのためのプログラミングは、それがターゲット状態に達したとベリファイされれば、終了する。使用されるプログラミングパルス列は、メモリセルの電荷蓄積ユニット中にプログラムされ蓄積された電子に対して反作用するために増大する周期あるいは振幅を持つことができる。プログラミング回路は、一般的に、選択されたワード線に一連のプログラミングパルスを印加する。このようにして、そのコントロールゲートがワード線に結合されている1ページのメモリセルが一緒にプログラムされ得る。ページの1つのメモリセルがそのターゲット状態までプログラムされると、プログラム禁止され、他のセルは、ページの全セルがプログラム−ベリファイされ終わるまでプログラミングにさらされ続ける。

図7(1)は、接地状態としての消去済み状態「Gr」と、漸次もっとプログラムされたメモリ状態「A」、「B」および「C」とを有する4状態メモリアレイの例におけるしきい値電圧分布を示す。読み出し中、4つの状態は3つの境界ブレークポイントDA 〜DC によって区分される。

図7(2)は、図7(1)に示されている4つの可能なメモリ状態を表す好ましい2ビットLM符号化を示す。メモリ状態(すなわち、「Gr」、「A」、「B」および「C」)の各々は1対の「上位、下位」符号ビット、すなわち「11」、「01」、「00」および「10」によってそれぞれ表される。「LM」符号は、米国特許第6,657,891号(特許文献15)に開示されていて、電荷の大きな変化を必要とするプログラム操作を避けることによって隣接フローティングゲート間の電界効果結合を減少させるために有益である。符号化は、2つの符号ビット、「下位」および「上位」ビットが別々にプログラムされ読み出され得るように設計されている。下位ビットをプログラムするとき、セルのしきい値レベルは、「消去済み」領域に留まるかあるいはしきい値ウィンドウの「下側中央」領域に移される。上位ビットをプログラムするとき、これら2つの領域のいずれかにあるセルのしきい値レベルは、しきい値ウィンドウの「下側中間」領域にある僅かにより高いレベルにさらに進められる。

図9は、メモリセルのアレイにp個のセンスモジュールのバンクを包含する、図1に示された読み出し/書き込み回路270Aおよび270Bを示す。並行して動作するp個のセンスモジュール480のバンク全体は、1行に沿うp個のセル10の1ブロック(またはページ)を並行して読み出すかあるいはプログラムすることを可能にする。本質的に、センスモジュール1はセル1における電流I1 を感知し、センスモジュール2はセル2における電流I2 を感知し、センスモジュールpはセルpにおける電流IP を感知するなどである。ソース線34から集合ノードCLSRCに、さらにそこから接地へ流れるページについての総セル電流iTOT は、p個のセルの全ての電流の総和である。在来のメモリアーキテクチャでは、1つの共通のワード線を有する1行のメモリセルは2つ以上のページを形成し、ページ中のメモリセルは並行して読み出されプログラムされる。2ページを有する行の場合、1ページは偶数ビット線によりアクセスされ、他方のページは奇数ビット線によりアクセスされる。いつでも1ページの感知回路が偶数ビット線または奇数ビット線に結合されている。その場合、読み出し/書き込み回路270Aおよび270Bを個々のページに対してそれぞれ多重化するためにページマルチプレクサ250Aおよび250Bが設けられる。

データラッチ430のスタックは、スタックに関連付けられた各メモリセルのために1つずつのデータラッチ430−1〜430−kから成る。I/Oモジュール440は、データラッチがI/Oバス231を介して外部とデータを交換することを可能にする。

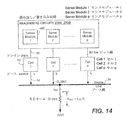

共通プロセッサは、エラー状態などのメモリ操作のステータスを示すステータス信号の出力のための出力507も含む。ステータス信号は、ワイヤードOR構成でフラグバス509に結合されているn形トランジスタ550のゲートを駆動するために使用される。フラグバスは、コントローラ310によって好ましくはプリチャージされ、いずれかの読み出し/書き込みスタックによってステータス信号がアサートされるとプルダウンされる。

その全体が本願明細書において参照により援用されている、米国特許第7,046,568号(特許文献17)は、低供給電圧で動作することのできる低ノイズ感知回路を有する不揮発性記憶装置を開示している。

前の感知回路とは違って、米国特許第7,046,568号(特許文献17)の低ノイズ感知回路は、セル電流を、それがキャパシタとして作用するビット線ではなくて専用キャパシタを放電させる速度によって測定する。このようにして、ビット線電圧は感知中一定に保たれ、これにより、ビット線上の時間変化する電圧に起因するビット線間結合からのノイズを避けることができる。感知回路は、セル電流を判定するために使用される電圧放電のダイナミックレンジを効果的に広げる電圧昇圧回路を組み込むことによって低供給電圧で動作することもできる。

感知は、ビット線電圧クランプ610によってクランプされた固定された電圧のビット線36を用いて行われる。ビット線電圧クランプは、そのソースおよびドレインがビット線およびCOM1ノード481の間で直列になっているn形トランジスタ612により実現されている。n形トランジスタ612のゲート上のアナログ電圧は、ビット線上のクランプされる電圧を決定する。感知操作中、この一定のビット線電圧は、ビット線上の変化する電圧に起因するビット線間に生じ得る結合をなくす。

プリチャージ回路640’は、センスモジュールの種々の操作中ビット線がCOM1ノード481およびSENノード631を介してVddのほうへプルアップされることを可能にする。プリチャージ回路640’は、信号INVによってイネーブルされるp形トランジスタ644により実現されている。

セル電流ディスクリミネータ650は、本質的にメモリセルの伝導電流を基準電流に関して比較する。セル電流が基準電流より大きければセンスアンプはハイ状態の信号INVを出力し、小さければ逆の状態の信号を出力する。いったんセットされれば、信号INVはセンスアンプラッチ660によってラッチされる。

感知の前に、選択されたメモリセルの電極への電圧は、1つ以上のプリチャージ操作で適切なワード線およびビット線を介してセットされなければならない。

ワード線およびビット線の電圧が安定しているとき、選択されたメモリセルの伝導電流あるいはプログラムされたしきい値電圧をセンスアンプ600’によりSENノードにおいて感知することができる。

図12Aおよび前の記述から、ビット線電圧がビット線クランプ610によって所定のVBLでクランプされるならば、クランプが機能するためには、クランプするn形トランジスタ612のドレイン側はソース側より僅かに(例えば、約0.2Vだけ)高い電圧でなければならないということがわかる。したがって、COM1はVBLより約0.2V高くなければならず、これは電圧クランプ622により保証される。これは、SENの電圧レベルが精々COM1よりVT 以内高いところまで下がってもよいということをも意味する。したがって、ノード631におけるSEN信号の放電は、Vddにより与えられる上限と、COM1より僅かに(例えば、約VT だけ)高いVLIMIT により与えられる下限とを有する限られたダイナミックレンジで動作し得るにすぎない。しかし、Vddの源であるより低い供給電圧について、VLIMIT の存在を仮定して、(Vdd−|VTP|)<VLIMIT ならば、p形トランジスタは決してオンにはならない。

比較回路650’は、線703を介してブースト電圧VB をキャパシタ652の一方のプレートに供給する電圧シフタ700の形の昇圧回路を設けることによって低電圧動作に適合させられている。電圧シフタのタイミングは、線702を介してページコントローラ498により制御される。

昇圧回路700は、感知期間中VB を高め、したがってセンスモジュール480’においてノイズ源となり得る。ノイズは、キャパシタ652を介してSENノード631へ、さらにその先へ伝わり得る。センスモジュールが感知操作中アクティブであるときにはセルが電流シンクとして作用していてビット電圧クランプ610とセンスアンプ内の電圧クランプ620との両方がノイズを軽減するように作動しているので、ノイズは重要ではない。

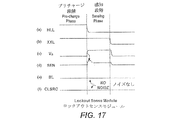

センスモジュール480’は、1ビット線から他への時間変化する電流の結合を避けるために定ビット線電圧で感知するように設計された。セル電流と無関係のどんな電流も単なるノイズであって、セル電流の感知におけるエラーの原因となる。前に説明したように、ロックアウトセンスモジュールは時間変化する電流であるノイズをロックアウトビット線に投入することがある。ロックアウトメモリセルは最早感知されていないとしても、ロックアウトビット線中の変化する電流は、そのセルがなお感知を受けているかもしれない隣接するビット線に結合されることがある。このタイプの結合ノイズは、ロックアウトセルに近い感知されつつあるセルに関しては重要であって、感知におけるエラーに寄与する。

他の1つの問題は、メモリセルのソース側電圧における不確実性と関連する。例えば、ソース側エラーの1つの現れは、ソース線とチップの接地パッドとの間の有限の抵抗に起因する。メモリセルを感知することについての1つの潜在的問題は、有限の抵抗を横断するソース負荷により引き起こされるソース線バイアスである。多数のメモリセルが並行して感知されるとき、それらの総電流は、有限の抵抗を有する接地ループにおいて顕著な電圧降下を生じさせることがある。これは、しきい値電圧感知を使用する読み出し操作においてエラーを引き起こすソース線バイアスをもたらす。

その全体が本願明細書において参照により援用されている、Nguyenらにより2007年6月29日に出願された「METHOD FOR SENSING NEGATIVE THRESHOLD VOLTAGES IN NON-VOLATILE STORAGE USING CURRENT SENSING」という米国特許出願第11/771,982号(特許文献19)は、1ページに沿う各メモリセルのソースを所定ページソース電圧に調整するための記憶装置および方法を開示している。

低められた供給電圧で動作することのできるセンスモジュールの1つの好ましい実施例では、感知される放電電圧のダイナミックレンジを増大させるために昇圧回路が使用される。センスモジュールが基準電流より大きな伝導電流を有するセルを特定すると、そのセルはそれ以上の感知からロックアウトされて、関連するビット線はそのロックアウトセルをオフにするためにページのソース線へ短絡される。このロックアウトモードでは、昇圧回路により生成されるステップアップ電圧はノイズ源となってセルのビット線およびページのソース線へ伝播しやすく、これにより他の動作しているセンスモジュールに干渉する。このノイズ源は、センスモジュールがロックアウトモードに入ると必ずビット線およびソース線に到達しないように絶縁される。ノイズ源と、ビット線およびソース線を昇圧回路に結合させる中間回路との間に絶縁回路が配置される。

他の1つの好ましい実施形態では、転送ゲートは、昇圧回路と放電電圧が感知されるノードとの間に配置される。

ステップ810:不揮発性メモリセルの伝導電流を、そのグループを並行して感知している最中に感知するために、中間回路を介してメモリセルがアクセスし得るノードを設ける。

ステップ820:ノードを初期電圧へプリチャージする。

ステップ830:ノードに結合された昇圧回路を設ける。

ステップ832:ノード上の初期電圧を所定量だけ高める。

ステップ840:伝導電流をノードにおける電圧放電の速度により測定する。

ステップ850:伝導電流が所定値より大きいと判定されるたびに、少なくともメモリセルのグループのための感知が完了するまで昇圧回路をメモリセルの中間回路から絶縁する。

2007年12月28日に出願された米国特許出願第11/966,325号(特許文献20)においてさらに発展させられている、前で与えられたセンスモジュールのための種々の実施形態は、データをセンスアンプのデータラッチからデータ上に読み出すプロセスが、接続されたビット線にプリチャージ素子が供給する同じ経路の一部を使用する構成を使用する。これは、米国特許第7,173,854号(特許文献18)および第7,170,784号(特許文献21)に見出されるものにも当てはまる。例えば、図12Aに示されているように、センスモジュール480’にラッチされたデータ値は、スイッチ488を通してバスノード422へ送り出される。これは、線COM1が481で接続することを伴う。これは、図12Bに示されているように、プリチャージがビット線に供給される同じ経路である。

図21Aの代表的な実施形態は、再び、プリチャージ素子CSA652を中央に、アナログセクションを左側に、デジタルセクションを右側に示す。デジタルセクションは、前のように構成され得るSAラッチ660と、弁別素子650とを含む。Dcrm650の中で、トランジスタ654および656は前のようであるけれども、ノード657を接地に接続するRSTによって制御されるトランジスタ658を持つのではなくて、ノード657は今はトランジスタ2101を通してノード422に接続され、そこからさらにSAバスに接続されている。したがって、ラッチされたデータは、今はこの経路に沿って信号RST_NCOにより制御されるトランジスタ2101を通って外へ転送され、前のNCO信号の機能をRST信号と合体させる。データを外へ転送するための経路は今は完全にデジタル側の中にあるので、NCOによって制御される図20Aの前のスイッチ488は最早この機能を果たさなくてもよい。

対照的に、図21A〜図21Cのような構成では、比較の結果が弁別素子によって行われてラッチされると、転送を次の読み出しのための準備と並行して行うことができて、転送時間を隠すと共にワード線およびビット線値を並行して高めることを可能にする。

Claims (37)

- 並行して感知される不揮発性メモリセルのグループの中のメモリセルの伝導電流を感知してその結果をデータバスに提供するための感知回路であって、

ノードと、

前記ノードを初期電圧に充電するために、前記ノードに結合されているプリチャージ回路と、

前記ノードに結合されて前記メモリセルに接続可能な中間回路であって、これにより前記プリチャージ回路からの電流が前記メモリセルに供給され得る中間回路と、

前記ノードにおける放電の速度によって前記伝導電流の判定を行うために前記ノードに結合された比較回路と、

前記判定の結果を保持するために前記比較回路に結合されたデータラッチと、

前記データラッチに、その中にラッチされている結果を前記ノードから独立して前記データバスに供給するために、結合された転送ゲートと、

を備える感知回路。 - 請求項1記載の感知回路において、

前記プリチャージ回路を、ラッチされた結果を前記データバスに供給すると同時に充電することができる感知回路。 - 請求項1記載の感知回路において、

前記グループの各メモリセルを関連するビット線によりアクセスすることができ、

前記中間回路は、前記関連するビット線に結合される感知回路。 - 請求項1記載の感知回路において、

前記不揮発性メモリセルのグループは、フラッシュEEPROMの一部分である感知回路。 - 請求項4記載の感知回路において、

前記フラッシュEEPROMは、NAND形のものである感知回路。 - 請求項1記載の感知回路において、

個々の不揮発性メモリセルは、電荷蓄積素子をそれぞれ包含する感知回路。 - 請求項6記載の感知回路において、

前記電荷蓄積素子は、フローティングゲートである感知回路。 - 請求項6記載の感知回路において、

前記電荷蓄積素子は、誘電体層である感知回路。 - 請求項1記載の感知回路において、

前記不揮発性メモリセルは、メモリカードにおいて具体化される感知回路。 - 請求項1記載の感知回路において、

前記比較回路は、前記伝導電流を基準値と比較することによって判定を行う感知回路。 - 請求項1記載の感知回路において、

前記データラッチにラッチされた結果は、前記中間回路におけるスイッチングレベルから独立に前記データバスに供給される感知回路。 - 並行して感知される不揮発性メモリセルのグループの中の第1のメモリセルの伝導電流を感知してその結果をデータバスに提供する方法であって、

中間回路を介して1つ以上のメモリセルによりアクセスされ得るノードを設けるステップと、

前記ノードを第1の感知操作のために初期電圧にプリチャージするステップと、

前記メモリセルのうちの第1のメモリセルを通して前記中間回路を介して前記ノードを放電させるステップと、

前記第1のメモリセルを通る伝導電流を前記ノードを放電させるステップの速度によって測定するステップと、

前記測定するステップの結果をラッチするステップと、

ラッチされた結果をデータバスに出力するステップと、

前記ラッチするステップの後で前記出力するステップを完了する前に、前記ノードを第2の感知操作のためにプリチャージするステップと、

を含む方法。 - 請求項12記載の方法において、

前記グループの各メモリセルを関連するビット線によりアクセスすることができ、

前記方法は、放電の前に前記メモリセルのうちの前記第1のメモリセルのための関連するビット線に前記中間回路を結合させるステップをさらに含む方法。 - 請求項12記載の方法において、

前記不揮発性メモリセルのグループは、フラッシュEEPROMの一部分である方法。 - 請求項14記載の方法において、

前記フラッシュEEPROMは、NAND形のものである方法。 - 請求項12記載の方法において、

個々の不揮発性メモリセルは、電荷蓄積素子をそれぞれ包含する方法。 - 請求項16記載の方法において、

前記電荷蓄積素子は、フローティングゲートである方法。 - 請求項16記載の方法において、

前記電荷蓄積素子は、誘電体層である方法。 - 請求項12記載の方法において、

前記測定するステップは、伝導電流を基準値と比較することを含む方法。 - 請求項12記載の方法において、

前記ラッチされた結果を出力するステップは、前記中間回路におけるスイッチングレベルから独立に前記データバスに供給される方法。 - 並行して感知される不揮発性メモリセルのグループの中の第1のメモリセルの伝導電流を感知してその結果をデータバスに提供する方法であって、

中間回路を介して1つ以上のメモリセルによりアクセスされ得るノードを設けるステップと、

前記ノードを第1の感知操作のために初期電圧にプリチャージするステップと、

前記メモリセルのうちの第1のメモリセルを通して前記中間回路を介して前記ノードを放電させるステップと、

前記第1のメモリセルを通る伝導電流を前記ノードを放電させるステップの速度によって測定するステップと、

前記測定するステップの結果をラッチするステップと、

ラッチされた結果を前記ノードおよび前記中間回路から独立の経路によってデータバスに出力するステップと、

を含む方法。 - 請求項21記載の方法において、

前記グループの各メモリセルを関連するビット線によりアクセスすることができ、

前記方法は、放電の前に前記メモリセルのうちの前記第1のメモリセルのための関連するビット線に前記中間回路を結合させるステップをさらに含む方法。 - 請求項21記載の方法において、

前記不揮発性メモリセルのグループは、フラッシュEEPROMの一部分である方法。 - 請求項23記載の方法において、

前記フラッシュEEPROMは、NAND形のものである方法。 - 請求項21記載の方法において、

個々の不揮発性メモリセルは、電荷蓄積素子をそれぞれ包含する方法。 - 請求項25記載の方法において、

前記電荷蓄積素子は、フローティングゲートである方法。 - 請求項25記載の方法において、

前記電荷蓄積素子は、誘電体層である方法。 - 請求項21記載の方法において、

前記測定するステップは、前記伝導電流を基準値と比較することを含む方法。 - 並行して感知される不揮発性メモリセルのグループの中の第1のメモリセルの伝導電流を感知してその結果をデータバスに提供する方法であって、

中間回路を介して1つ以上のメモリセルによりアクセスされ得るノードを設けるステップと、

前記ノードを第1の感知操作のために初期電圧にプリチャージするステップと、

前記メモリセルのうちの第1のメモリセルを通して前記中間回路を介して前記ノードを放電させるステップと、

前記第1のメモリセルを通る伝導電流を前記ノードを放電させるステップの速度によって測定するステップと、

前記測定するステップの結果をラッチするステップと、

ラッチされた結果を中間回路から独立にデータバスに出力するステップであって、これによりその中においてノイズが低減される、ラッチされた結果を出力するステップと、

を含む方法。 - 請求項29記載の方法において、

前記グループの各メモリセルを関連するビット線によりアクセスすることができ、

前記方法は、放電の前に前記メモリセルのうちの前記第1のメモリセルのための関連するビット線に前記中間回路を結合させるステップをさらに含む方法。 - 請求項29記載の方法において、

前記不揮発性メモリセルのグループは、フラッシュEEPROMの一部分である方法。 - 請求項31記載の方法において、

前記フラッシュEEPROMは、NAND形のものである方法。 - 請求項29記載の方法において、

個々の不揮発性メモリセルは、電荷蓄積素子をそれぞれ包含する方法。 - 請求項33記載の方法において、

前記電荷蓄積素子は、フローティングゲートである方法。 - 請求項33記載の方法において、

前記電荷蓄積素子は、誘電体層である方法。 - 請求項29記載の方法において、

前記測定するステップは、伝導電流を基準値と比較することを含む方法。 - 請求項29記載の方法において、

前記ラッチされた結果を出力するステップは、前記中間回路におけるスイッチングレベルから独立に前記データバスに供給される方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US12/128,535 US7957197B2 (en) | 2008-05-28 | 2008-05-28 | Nonvolatile memory with a current sense amplifier having a precharge circuit and a transfer gate coupled to a sense node |

| US12/128,535 | 2008-05-28 | ||

| PCT/US2009/039082 WO2009146057A1 (en) | 2008-05-28 | 2009-04-01 | High speed sense amplifier array and method for nonvolatile memory |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011522348A true JP2011522348A (ja) | 2011-07-28 |

| JP2011522348A5 JP2011522348A5 (ja) | 2012-05-24 |

Family

ID=40674075

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011511667A Pending JP2011522348A (ja) | 2008-05-28 | 2009-04-01 | 不揮発性メモリのための高速センスアンプアレイおよび方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7957197B2 (ja) |

| EP (1) | EP2289070B1 (ja) |

| JP (1) | JP2011522348A (ja) |

| KR (1) | KR101468886B1 (ja) |

| CN (1) | CN102113057B (ja) |

| TW (1) | TWI397921B (ja) |

| WO (1) | WO2009146057A1 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011146100A (ja) * | 2010-01-15 | 2011-07-28 | Toshiba Corp | 半導体記憶装置及びその読出し方法 |

| JP2021527294A (ja) * | 2018-06-15 | 2021-10-11 | シリコン ストーリッジ テクノロージー インコーポレイテッドSilicon Storage Technology, Inc. | フラッシュメモリシステム用の改良されたセンスアンプ |

Families Citing this family (51)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN104282086A (zh) | 2007-01-09 | 2015-01-14 | 功率监视器公司 | 用于智能电路断路器的方法和设备 |

| WO2009111386A2 (en) | 2008-03-04 | 2009-09-11 | Power Monitors, Inc. | Method and apparatus for a voice-prompted electrical hookup |

| US7957197B2 (en) * | 2008-05-28 | 2011-06-07 | Sandisk Corporation | Nonvolatile memory with a current sense amplifier having a precharge circuit and a transfer gate coupled to a sense node |

| US8710907B2 (en) | 2008-06-24 | 2014-04-29 | Sandisk Technologies Inc. | Clock generator circuit for a charge pump |

| US8446773B2 (en) * | 2009-02-25 | 2013-05-21 | Samsung Electronics Co., Ltd. | Memory system and programming method thereof |

| US8339183B2 (en) | 2009-07-24 | 2012-12-25 | Sandisk Technologies Inc. | Charge pump with reduced energy consumption through charge sharing and clock boosting suitable for high voltage word line in flash memories |

| US8773108B2 (en) | 2009-11-10 | 2014-07-08 | Power Monitors, Inc. | System, method, and apparatus for a safe powerline communications instrumentation front-end |

| KR101094944B1 (ko) * | 2009-12-24 | 2011-12-15 | 주식회사 하이닉스반도체 | 센싱 전압을 제어하는 비휘발성 반도체 집적 회로 |

| US10060957B2 (en) | 2010-07-29 | 2018-08-28 | Power Monitors, Inc. | Method and apparatus for a cloud-based power quality monitor |

| EP3324153A1 (en) | 2010-07-29 | 2018-05-23 | Power Monitors, Inc. | Method and apparatus for a demand management monitoring system |

| US8339185B2 (en) | 2010-12-20 | 2012-12-25 | Sandisk 3D Llc | Charge pump system that dynamically selects number of active stages |

| US8294509B2 (en) | 2010-12-20 | 2012-10-23 | Sandisk Technologies Inc. | Charge pump systems with reduction in inefficiencies due to charge sharing between capacitances |

| CN102881331A (zh) * | 2011-07-15 | 2013-01-16 | 复旦大学 | 灵敏放大器的控制电路及包括其的dram |

| US8699247B2 (en) | 2011-09-09 | 2014-04-15 | Sandisk Technologies Inc. | Charge pump system dynamically reconfigurable for read and program |

| US8400212B1 (en) | 2011-09-22 | 2013-03-19 | Sandisk Technologies Inc. | High voltage charge pump regulation system with fine step adjustment |

| US8514628B2 (en) | 2011-09-22 | 2013-08-20 | Sandisk Technologies Inc. | Dynamic switching approach to reduce area and power consumption of high voltage charge pumps |

| US8705293B2 (en) | 2011-10-20 | 2014-04-22 | Sandisk Technologies Inc. | Compact sense amplifier for non-volatile memory suitable for quick pass write |

| US8630120B2 (en) | 2011-10-20 | 2014-01-14 | Sandisk Technologies Inc. | Compact sense amplifier for non-volatile memory |

| WO2013058960A2 (en) | 2011-10-20 | 2013-04-25 | Sandisk Technologies Inc. | Compact sense amplifier for non-volatile memory |

| TWI463497B (zh) * | 2011-11-09 | 2014-12-01 | Macronix Int Co Ltd | 記憶體存取方法及應用其之快閃記憶體 |

| US9293195B2 (en) | 2012-06-28 | 2016-03-22 | Sandisk Technologies Inc. | Compact high speed sense amplifier for non-volatile memory |

| US20140003176A1 (en) * | 2012-06-28 | 2014-01-02 | Man Lung Mui | Compact High Speed Sense Amplifier for Non-Volatile Memory with Reduced layout Area and Power Consumption |

| US8971141B2 (en) * | 2012-06-28 | 2015-03-03 | Sandisk Technologies Inc. | Compact high speed sense amplifier for non-volatile memory and hybrid lockout |

| US9257154B2 (en) | 2012-11-29 | 2016-02-09 | Micron Technology, Inc. | Methods and apparatuses for compensating for source voltage |

| KR20140081027A (ko) * | 2012-12-21 | 2014-07-01 | 에스케이하이닉스 주식회사 | 비휘발성 메모리 장치 |

| JP2014186777A (ja) * | 2013-03-22 | 2014-10-02 | Toshiba Corp | 半導体記憶装置 |

| JP2015036998A (ja) * | 2013-08-13 | 2015-02-23 | 株式会社東芝 | 半導体記憶装置 |

| CN104575606B (zh) * | 2013-10-10 | 2018-05-22 | 无锡华润上华科技有限公司 | 一种带有自检测电路的读出电路及控制方法 |

| US9208895B1 (en) | 2014-08-14 | 2015-12-08 | Sandisk Technologies Inc. | Cell current control through power supply |

| US9349468B2 (en) | 2014-08-25 | 2016-05-24 | SanDisk Technologies, Inc. | Operational amplifier methods for charging of sense amplifier internal nodes |

| US9312018B1 (en) * | 2014-09-24 | 2016-04-12 | Intel Corporation | Sensing with boost |

| US10032509B2 (en) * | 2015-03-30 | 2018-07-24 | Toshiba Memory Corporation | Semiconductor memory device including variable resistance element |

| US9917507B2 (en) | 2015-05-28 | 2018-03-13 | Sandisk Technologies Llc | Dynamic clock period modulation scheme for variable charge pump load currents |

| US9647536B2 (en) | 2015-07-28 | 2017-05-09 | Sandisk Technologies Llc | High voltage generation using low voltage devices |

| US9520776B1 (en) | 2015-09-18 | 2016-12-13 | Sandisk Technologies Llc | Selective body bias for charge pump transfer switches |

| JP6490018B2 (ja) * | 2016-02-12 | 2019-03-27 | 東芝メモリ株式会社 | 半導体記憶装置 |

| CN105913875B (zh) * | 2016-03-31 | 2019-11-26 | 清华大学 | 控制电路、存储装置及操作方法 |

| CN106098098B (zh) * | 2016-06-22 | 2019-07-02 | 上海华虹宏力半导体制造有限公司 | 电流比较电路、存储器及电流比较方法 |

| US9786345B1 (en) * | 2016-09-16 | 2017-10-10 | Micron Technology, Inc. | Compensation for threshold voltage variation of memory cell components |

| US10339989B2 (en) | 2016-11-17 | 2019-07-02 | Samsung Electronics Co., Ltd. | Page buffer, a memory device including the same and a read operation method thereof |

| US10366729B2 (en) | 2017-06-22 | 2019-07-30 | Sandisk Technologies Llc | Sense circuit with two-step clock signal for consecutive sensing |

| JP2019067474A (ja) | 2017-10-05 | 2019-04-25 | 東芝メモリ株式会社 | 半導体記憶装置 |

| US10460814B2 (en) * | 2017-12-12 | 2019-10-29 | Western Digital Technologies, Inc. | Non-volatile memory and method for power efficient read or verify using lockout control |

| US10217496B1 (en) * | 2018-02-28 | 2019-02-26 | Arm Limited | Bitline write assist circuitry |

| CN111462802B (zh) * | 2019-01-22 | 2022-05-13 | 上海汉容微电子有限公司 | 一种nor闪存的读取电路 |

| US11004501B2 (en) * | 2019-06-26 | 2021-05-11 | Macronix International Co., Ltd. | Sensing a memory device |

| KR20210034873A (ko) | 2019-09-23 | 2021-03-31 | 에스케이하이닉스 주식회사 | 메모리 장치 및 그 동작 방법 |

| US11417400B2 (en) | 2020-01-31 | 2022-08-16 | Sandisk Technologies Llc | Controlling timing and ramp rate of program-inhibit voltage signal during programming to optimize peak current |

| US11074956B1 (en) * | 2020-03-02 | 2021-07-27 | Micron Technology, Inc. | Arbitrated sense amplifier |

| US11929125B2 (en) | 2021-06-23 | 2024-03-12 | Sandisk Technologies Llc | Window program verify to reduce data latch usage in memory device |

| US11901018B2 (en) * | 2021-12-27 | 2024-02-13 | Sandisk Technologies Llc | Sense amplifier structure for non-volatile memory with neighbor bit line local data bus data transfer |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0528780A (ja) * | 1991-07-22 | 1993-02-05 | Toshiba Corp | 不揮発性半導体記憶装置 |

| EP0974976A1 (en) * | 1998-07-20 | 2000-01-26 | STMicroelectronics S.r.l. | Circuit and method for reading a non-volatile memory |

| JP2001266585A (ja) * | 2000-03-23 | 2001-09-28 | Toshiba Lsi System Support Kk | Mrom回路 |

| WO2006065501A1 (en) * | 2004-12-16 | 2006-06-22 | Sandisk Corporation | Memory sensing circuit and method for low voltage operation |

Family Cites Families (36)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4785427A (en) | 1987-01-28 | 1988-11-15 | Cypress Semiconductor Corporation | Differential bit line clamp |

| US5095344A (en) | 1988-06-08 | 1992-03-10 | Eliyahou Harari | Highly compact eprom and flash eeprom devices |

| US5070032A (en) | 1989-03-15 | 1991-12-03 | Sundisk Corporation | Method of making dense flash eeprom semiconductor memory structures |

| US5172338B1 (en) | 1989-04-13 | 1997-07-08 | Sandisk Corp | Multi-state eeprom read and write circuits and techniques |

| US5343063A (en) | 1990-12-18 | 1994-08-30 | Sundisk Corporation | Dense vertical programmable read only memory cell structure and processes for making them |

| US6222762B1 (en) | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| US5313421A (en) | 1992-01-14 | 1994-05-17 | Sundisk Corporation | EEPROM with split gate source side injection |

| US5315541A (en) | 1992-07-24 | 1994-05-24 | Sundisk Corporation | Segmented column memory array |

| KR0169267B1 (ko) | 1993-09-21 | 1999-02-01 | 사토 후미오 | 불휘발성 반도체 기억장치 |

| US5661053A (en) | 1994-05-25 | 1997-08-26 | Sandisk Corporation | Method of making dense flash EEPROM cell array and peripheral supporting circuits formed in deposited field oxide with the use of spacers |

| US5721702A (en) * | 1995-08-01 | 1998-02-24 | Micron Quantum Devices, Inc. | Reference voltage generator using flash memory cells |

| US5903495A (en) | 1996-03-18 | 1999-05-11 | Kabushiki Kaisha Toshiba | Semiconductor device and memory system |

| US5768192A (en) | 1996-07-23 | 1998-06-16 | Saifun Semiconductors, Ltd. | Non-volatile semiconductor memory cell utilizing asymmetrical charge trapping |

| US6335149B1 (en) | 1997-04-08 | 2002-01-01 | Corning Incorporated | High performance acrylate materials for optical interconnects |

| US6768165B1 (en) | 1997-08-01 | 2004-07-27 | Saifun Semiconductors Ltd. | Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping |

| JP3883687B2 (ja) * | 1998-02-16 | 2007-02-21 | 株式会社ルネサステクノロジ | 半導体装置、メモリカード及びデータ処理システム |

| JP3983969B2 (ja) * | 2000-03-08 | 2007-09-26 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| ITRM20010001A1 (it) * | 2001-01-03 | 2002-07-03 | Micron Technology Inc | Circuiteria di rilevazione per memorie flash a bassa tensione. |

| KR100381956B1 (ko) | 2001-02-02 | 2003-04-26 | 삼성전자주식회사 | 플래시 메모리 장치의 감지 증폭 회로 |

| US7196931B2 (en) * | 2002-09-24 | 2007-03-27 | Sandisk Corporation | Non-volatile memory and method with reduced source line bias errors |

| US6657891B1 (en) | 2002-11-29 | 2003-12-02 | Kabushiki Kaisha Toshiba | Semiconductor memory device for storing multivalued data |

| JP3920768B2 (ja) | 2002-12-26 | 2007-05-30 | 株式会社東芝 | 不揮発性半導体メモリ |

| JP4322686B2 (ja) * | 2004-01-07 | 2009-09-02 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2005293659A (ja) * | 2004-03-31 | 2005-10-20 | Nec Electronics Corp | メモリ装置とリファレンス電流設定方法 |

| US7095655B2 (en) * | 2004-08-12 | 2006-08-22 | Saifun Semiconductors Ltd. | Dynamic matching of signal path and reference path for sensing |

| US7120051B2 (en) * | 2004-12-14 | 2006-10-10 | Sandisk Corporation | Pipelined programming of non-volatile memories using early data |

| US20060140007A1 (en) | 2004-12-29 | 2006-06-29 | Raul-Adrian Cernea | Non-volatile memory and method with shared processing for an aggregate of read/write circuits |

| KR100680486B1 (ko) * | 2005-03-30 | 2007-02-08 | 주식회사 하이닉스반도체 | 향상된 동작 성능을 가지는 플래시 메모리 장치의 페이지버퍼 회로 및 그 독출 및 프로그램 동작 제어 방법 |

| US7173854B2 (en) | 2005-04-01 | 2007-02-06 | Sandisk Corporation | Non-volatile memory and method with compensation for source line bias errors |

| ITRM20050353A1 (it) * | 2005-07-04 | 2007-01-05 | Micron Technology Inc | Amplificatore di rilevazione di piu' bit a bassa potenza. |

| US7447094B2 (en) | 2005-12-29 | 2008-11-04 | Sandisk Corporation | Method for power-saving multi-pass sensing in non-volatile memory |

| US7564718B2 (en) * | 2006-04-12 | 2009-07-21 | Infineon Technologies Flash Gmbh & Co. Kg | Method for programming a block of memory cells, non-volatile memory device and memory card device |

| US7580291B2 (en) * | 2006-06-08 | 2009-08-25 | Atmel Corporation | Data register with efficient erase, program verify, and direct bit-line memory access features |

| US20080247254A1 (en) * | 2007-04-05 | 2008-10-09 | Hao Thai Nguyen | Method for temperature compensating bit line during sense operations in non-volatile storage |

| US7593265B2 (en) * | 2007-12-28 | 2009-09-22 | Sandisk Corporation | Low noise sense amplifier array and method for nonvolatile memory |

| US7957197B2 (en) * | 2008-05-28 | 2011-06-07 | Sandisk Corporation | Nonvolatile memory with a current sense amplifier having a precharge circuit and a transfer gate coupled to a sense node |

-

2008

- 2008-05-28 US US12/128,535 patent/US7957197B2/en active Active

-

2009

- 2009-04-01 WO PCT/US2009/039082 patent/WO2009146057A1/en active Application Filing

- 2009-04-01 KR KR1020107026690A patent/KR101468886B1/ko active IP Right Grant

- 2009-04-01 CN CN200980129692.7A patent/CN102113057B/zh active Active

- 2009-04-01 JP JP2011511667A patent/JP2011522348A/ja active Pending

- 2009-04-01 EP EP09755420.8A patent/EP2289070B1/en active Active

- 2009-04-20 TW TW098113074A patent/TWI397921B/zh not_active IP Right Cessation

-

2011

- 2011-05-03 US US13/100,164 patent/US8169831B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0528780A (ja) * | 1991-07-22 | 1993-02-05 | Toshiba Corp | 不揮発性半導体記憶装置 |

| EP0974976A1 (en) * | 1998-07-20 | 2000-01-26 | STMicroelectronics S.r.l. | Circuit and method for reading a non-volatile memory |

| JP2001266585A (ja) * | 2000-03-23 | 2001-09-28 | Toshiba Lsi System Support Kk | Mrom回路 |

| WO2006065501A1 (en) * | 2004-12-16 | 2006-06-22 | Sandisk Corporation | Memory sensing circuit and method for low voltage operation |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011146100A (ja) * | 2010-01-15 | 2011-07-28 | Toshiba Corp | 半導体記憶装置及びその読出し方法 |

| JP2021527294A (ja) * | 2018-06-15 | 2021-10-11 | シリコン ストーリッジ テクノロージー インコーポレイテッドSilicon Storage Technology, Inc. | フラッシュメモリシステム用の改良されたセンスアンプ |

| JP7244550B2 (ja) | 2018-06-15 | 2023-03-22 | シリコン ストーリッジ テクノロージー インコーポレイテッド | フラッシュメモリシステム用の改良されたセンスアンプ |

Also Published As

| Publication number | Publication date |

|---|---|

| CN102113057A (zh) | 2011-06-29 |

| EP2289070B1 (en) | 2014-05-07 |

| KR101468886B1 (ko) | 2014-12-11 |

| WO2009146057A1 (en) | 2009-12-03 |

| EP2289070A1 (en) | 2011-03-02 |

| US20110205804A1 (en) | 2011-08-25 |

| US8169831B2 (en) | 2012-05-01 |

| US20090296488A1 (en) | 2009-12-03 |

| CN102113057B (zh) | 2014-11-05 |

| TWI397921B (zh) | 2013-06-01 |

| KR20110034588A (ko) | 2011-04-05 |

| US7957197B2 (en) | 2011-06-07 |

| TW201007757A (en) | 2010-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7957197B2 (en) | Nonvolatile memory with a current sense amplifier having a precharge circuit and a transfer gate coupled to a sense node | |

| US8300472B2 (en) | Low noise sense amplifier array and method for nonvolatile memory | |

| US8705293B2 (en) | Compact sense amplifier for non-volatile memory suitable for quick pass write | |

| KR101974686B1 (ko) | 혼성 록아웃을 가진 비휘발성 메모리를 위한 콤팩트한 고속 감지 증폭기 | |

| US7046568B2 (en) | Memory sensing circuit and method for low voltage operation | |

| US9558836B2 (en) | Compact high speed sense amplifier for non-volatile memory with reduced layout area and power consumption | |

| US8811075B2 (en) | Charge cycling by equalizing and regulating the source, well, and bit line levels during write operations for NAND flash memory: verify to program transition | |

| US8630120B2 (en) | Compact sense amplifier for non-volatile memory | |

| US9293195B2 (en) | Compact high speed sense amplifier for non-volatile memory | |

| US9208895B1 (en) | Cell current control through power supply | |

| WO2013058960A2 (en) | Compact sense amplifier for non-volatile memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120327 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120327 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20120418 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20120425 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20120615 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120820 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120827 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121129 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130205 |