JP2011505589A - 選択的領域堆積と組み合わせて着色マスクを使用する方法 - Google Patents

選択的領域堆積と組み合わせて着色マスクを使用する方法 Download PDFInfo

- Publication number

- JP2011505589A JP2011505589A JP2010534945A JP2010534945A JP2011505589A JP 2011505589 A JP2011505589 A JP 2011505589A JP 2010534945 A JP2010534945 A JP 2010534945A JP 2010534945 A JP2010534945 A JP 2010534945A JP 2011505589 A JP2011505589 A JP 2011505589A

- Authority

- JP

- Japan

- Prior art keywords

- layer

- deposition

- mask

- color

- pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000000034 method Methods 0.000 title claims abstract description 148

- 230000008021 deposition Effects 0.000 title claims abstract description 105

- 239000000463 material Substances 0.000 claims abstract description 262

- 238000000151 deposition Methods 0.000 claims abstract description 126

- 238000000059 patterning Methods 0.000 claims abstract description 70

- 230000002401 inhibitory effect Effects 0.000 claims abstract description 58

- 239000000758 substrate Substances 0.000 claims description 72

- 150000001875 compounds Chemical class 0.000 claims description 46

- 239000010409 thin film Substances 0.000 claims description 32

- 239000003112 inhibitor Substances 0.000 claims description 18

- 238000000231 atomic layer deposition Methods 0.000 claims description 16

- 238000007639 printing Methods 0.000 claims description 16

- 238000001228 spectrum Methods 0.000 claims description 13

- 238000000862 absorption spectrum Methods 0.000 claims description 11

- 239000004925 Acrylic resin Substances 0.000 claims description 6

- 239000000654 additive Substances 0.000 claims description 6

- 238000007646 gravure printing Methods 0.000 claims description 4

- 230000000996 additive effect Effects 0.000 claims description 3

- 238000007641 inkjet printing Methods 0.000 claims description 3

- 239000002243 precursor Substances 0.000 claims description 2

- 125000002524 organometallic group Chemical group 0.000 claims 1

- 238000010926 purge Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 215

- 238000000576 coating method Methods 0.000 description 92

- 239000011248 coating agent Substances 0.000 description 87

- 239000010408 film Substances 0.000 description 79

- 239000000243 solution Substances 0.000 description 55

- 239000006096 absorbing agent Substances 0.000 description 54

- 239000000975 dye Substances 0.000 description 50

- -1 inductors Substances 0.000 description 45

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 38

- 229920000642 polymer Polymers 0.000 description 33

- 238000004519 manufacturing process Methods 0.000 description 29

- 239000000203 mixture Substances 0.000 description 29

- 229920002120 photoresistant polymer Polymers 0.000 description 28

- 239000002346 layers by function Substances 0.000 description 25

- 239000004065 semiconductor Substances 0.000 description 25

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 24

- 238000005530 etching Methods 0.000 description 24

- 125000005375 organosiloxane group Chemical group 0.000 description 24

- RDOXTESZEPMUJZ-UHFFFAOYSA-N anisole Chemical compound COC1=CC=CC=C1 RDOXTESZEPMUJZ-UHFFFAOYSA-N 0.000 description 20

- 230000008569 process Effects 0.000 description 20

- 239000011787 zinc oxide Substances 0.000 description 19

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 18

- 239000004926 polymethyl methacrylate Substances 0.000 description 18

- 239000011521 glass Substances 0.000 description 17

- 239000000047 product Substances 0.000 description 17

- 238000010521 absorption reaction Methods 0.000 description 16

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 239000002904 solvent Substances 0.000 description 14

- 239000004020 conductor Substances 0.000 description 13

- 239000012776 electronic material Substances 0.000 description 13

- 229910052757 nitrogen Inorganic materials 0.000 description 13

- 238000012545 processing Methods 0.000 description 13

- 230000008901 benefit Effects 0.000 description 12

- 238000011161 development Methods 0.000 description 12

- 239000003989 dielectric material Substances 0.000 description 11

- 230000035945 sensitivity Effects 0.000 description 11

- 239000011550 stock solution Substances 0.000 description 11

- FBPFZTCFMRRESA-FSIIMWSLSA-N D-Glucitol Natural products OC[C@H](O)[C@H](O)[C@@H](O)[C@H](O)CO FBPFZTCFMRRESA-FSIIMWSLSA-N 0.000 description 10

- FBPFZTCFMRRESA-JGWLITMVSA-N D-glucitol Chemical compound OC[C@H](O)[C@@H](O)[C@H](O)[C@H](O)CO FBPFZTCFMRRESA-JGWLITMVSA-N 0.000 description 10

- LFQSCWFLJHTTHZ-UHFFFAOYSA-N Ethanol Chemical compound CCO LFQSCWFLJHTTHZ-UHFFFAOYSA-N 0.000 description 10

- 125000004432 carbon atom Chemical group C* 0.000 description 10

- 229920001577 copolymer Polymers 0.000 description 10

- 238000013461 design Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 10

- UZKWTJUDCOPSNM-UHFFFAOYSA-N methoxybenzene Substances CCCCOC=C UZKWTJUDCOPSNM-UHFFFAOYSA-N 0.000 description 10

- 230000003287 optical effect Effects 0.000 description 10

- 239000000600 sorbitol Substances 0.000 description 10

- 230000003595 spectral effect Effects 0.000 description 10

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 10

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 9

- 125000002091 cationic group Chemical group 0.000 description 9

- 238000006243 chemical reaction Methods 0.000 description 9

- 230000006870 function Effects 0.000 description 9

- 239000000178 monomer Substances 0.000 description 9

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 9

- 239000001301 oxygen Substances 0.000 description 9

- 229910052760 oxygen Inorganic materials 0.000 description 9

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 8

- 238000009826 distribution Methods 0.000 description 8

- 239000011159 matrix material Substances 0.000 description 8

- 238000000206 photolithography Methods 0.000 description 8

- 229920006254 polymer film Polymers 0.000 description 8

- 229910052709 silver Inorganic materials 0.000 description 8

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 8

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 7

- 239000011358 absorbing material Substances 0.000 description 7

- 125000000217 alkyl group Chemical group 0.000 description 7

- 230000005764 inhibitory process Effects 0.000 description 7

- 230000000873 masking effect Effects 0.000 description 7

- 125000000962 organic group Chemical group 0.000 description 7

- 239000002491 polymer binding agent Substances 0.000 description 7

- 239000004332 silver Substances 0.000 description 7

- 239000000126 substance Substances 0.000 description 7

- 125000001424 substituent group Chemical group 0.000 description 7

- DAKWPKUUDNSNPN-UHFFFAOYSA-N Trimethylolpropane triacrylate Chemical compound C=CC(=O)OCC(CC)(COC(=O)C=C)COC(=O)C=C DAKWPKUUDNSNPN-UHFFFAOYSA-N 0.000 description 6

- 150000001408 amides Chemical class 0.000 description 6

- 230000008859 change Effects 0.000 description 6

- 238000004132 cross linking Methods 0.000 description 6

- JHIVVAPYMSGYDF-UHFFFAOYSA-N cyclohexanone Chemical compound O=C1CCCCC1 JHIVVAPYMSGYDF-UHFFFAOYSA-N 0.000 description 6

- 238000005516 engineering process Methods 0.000 description 6

- 125000000524 functional group Chemical group 0.000 description 6

- 239000012212 insulator Substances 0.000 description 6

- 239000008204 material by function Substances 0.000 description 6

- 239000000049 pigment Substances 0.000 description 6

- 238000009832 plasma treatment Methods 0.000 description 6

- 229920005596 polymer binder Polymers 0.000 description 6

- 229910052710 silicon Inorganic materials 0.000 description 6

- 238000012546 transfer Methods 0.000 description 6

- 125000000391 vinyl group Chemical group [H]C([*])=C([H])[H] 0.000 description 6

- BTBUEUYNUDRHOZ-UHFFFAOYSA-N Borate Chemical compound [O-]B([O-])[O-] BTBUEUYNUDRHOZ-UHFFFAOYSA-N 0.000 description 5

- NTIZESTWPVYFNL-UHFFFAOYSA-N Methyl isobutyl ketone Chemical compound CC(C)CC(C)=O NTIZESTWPVYFNL-UHFFFAOYSA-N 0.000 description 5

- UIHCLUNTQKBZGK-UHFFFAOYSA-N Methyl isobutyl ketone Natural products CCC(C)C(C)=O UIHCLUNTQKBZGK-UHFFFAOYSA-N 0.000 description 5

- 150000001252 acrylic acid derivatives Chemical class 0.000 description 5

- 150000001732 carboxylic acid derivatives Chemical class 0.000 description 5

- 238000001723 curing Methods 0.000 description 5

- 150000002148 esters Chemical class 0.000 description 5

- RKJUIXBNRJVNHR-UHFFFAOYSA-N indolenine group Chemical group N1=CCC2=CC=CC=C12 RKJUIXBNRJVNHR-UHFFFAOYSA-N 0.000 description 5

- 150000003839 salts Chemical class 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 238000004544 sputter deposition Methods 0.000 description 5

- 125000003396 thiol group Chemical group [H]S* 0.000 description 5

- 229920002554 vinyl polymer Chemical group 0.000 description 5

- 235000012431 wafers Nutrition 0.000 description 5

- NJZHEQOUHLZCOX-WWGRRREGSA-N (3aS,4R,9bR)-golgicide A Chemical compound C1([C@@H]2NC3=C(F)C=C(C=C3[C@@H]3C=CC[C@@H]32)F)=CC=CN=C1 NJZHEQOUHLZCOX-WWGRRREGSA-N 0.000 description 4

- 239000004971 Cross linker Substances 0.000 description 4

- 239000004593 Epoxy Substances 0.000 description 4

- 101100175482 Glycine max CG-3 gene Proteins 0.000 description 4

- IMNFDUFMRHMDMM-UHFFFAOYSA-N N-Heptane Chemical compound CCCCCCC IMNFDUFMRHMDMM-UHFFFAOYSA-N 0.000 description 4

- 101000580354 Rhea americana Rheacalcin-2 Proteins 0.000 description 4

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 4

- 125000001931 aliphatic group Chemical group 0.000 description 4

- 239000007864 aqueous solution Substances 0.000 description 4

- 125000003118 aryl group Chemical group 0.000 description 4

- 239000003990 capacitor Substances 0.000 description 4

- 239000012159 carrier gas Substances 0.000 description 4

- 239000003054 catalyst Substances 0.000 description 4

- 239000007795 chemical reaction product Substances 0.000 description 4

- 238000005137 deposition process Methods 0.000 description 4

- ZBCBWPMODOFKDW-UHFFFAOYSA-N diethanolamine Chemical compound OCCNCCO ZBCBWPMODOFKDW-UHFFFAOYSA-N 0.000 description 4

- KPUWHANPEXNPJT-UHFFFAOYSA-N disiloxane Chemical class [SiH3]O[SiH3] KPUWHANPEXNPJT-UHFFFAOYSA-N 0.000 description 4

- 238000001704 evaporation Methods 0.000 description 4

- 230000008020 evaporation Effects 0.000 description 4

- 239000000945 filler Substances 0.000 description 4

- 238000009472 formulation Methods 0.000 description 4

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 238000001459 lithography Methods 0.000 description 4

- DZVCFNFOPIZQKX-LTHRDKTGSA-M merocyanine Chemical class [Na+].O=C1N(CCCC)C(=O)N(CCCC)C(=O)C1=C\C=C\C=C/1N(CCCS([O-])(=O)=O)C2=CC=CC=C2O\1 DZVCFNFOPIZQKX-LTHRDKTGSA-M 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000005693 optoelectronics Effects 0.000 description 4

- 125000001997 phenyl group Chemical group [H]C1=C([H])C([H])=C(*)C([H])=C1[H] 0.000 description 4

- 238000006116 polymerization reaction Methods 0.000 description 4

- 238000010129 solution processing Methods 0.000 description 4

- 238000001429 visible spectrum Methods 0.000 description 4

- QGKMIGUHVLGJBR-UHFFFAOYSA-M (4z)-1-(3-methylbutyl)-4-[[1-(3-methylbutyl)quinolin-1-ium-4-yl]methylidene]quinoline;iodide Chemical compound [I-].C12=CC=CC=C2N(CCC(C)C)C=CC1=CC1=CC=[N+](CCC(C)C)C2=CC=CC=C12 QGKMIGUHVLGJBR-UHFFFAOYSA-M 0.000 description 3

- PXGZQGDTEZPERC-UHFFFAOYSA-N 1,4-cyclohexanedicarboxylic acid Chemical compound OC(=O)C1CCC(C(O)=O)CC1 PXGZQGDTEZPERC-UHFFFAOYSA-N 0.000 description 3

- WEVYAHXRMPXWCK-UHFFFAOYSA-N Acetonitrile Chemical compound CC#N WEVYAHXRMPXWCK-UHFFFAOYSA-N 0.000 description 3

- KAKZBPTYRLMSJV-UHFFFAOYSA-N Butadiene Chemical compound C=CC=C KAKZBPTYRLMSJV-UHFFFAOYSA-N 0.000 description 3

- CTQNGGLPUBDAKN-UHFFFAOYSA-N O-Xylene Chemical compound CC1=CC=CC=C1C CTQNGGLPUBDAKN-UHFFFAOYSA-N 0.000 description 3

- 239000004793 Polystyrene Substances 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 229920004482 WACKER® Polymers 0.000 description 3

- 235000010724 Wisteria floribunda Nutrition 0.000 description 3

- 238000012644 addition polymerization Methods 0.000 description 3

- 238000007259 addition reaction Methods 0.000 description 3

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 3

- MWPLVEDNUUSJAV-UHFFFAOYSA-N anthracene Chemical compound C1=CC=CC2=CC3=CC=CC=C3C=C21 MWPLVEDNUUSJAV-UHFFFAOYSA-N 0.000 description 3

- 230000004888 barrier function Effects 0.000 description 3

- 239000011230 binding agent Substances 0.000 description 3

- 229920001400 block copolymer Polymers 0.000 description 3

- 150000001735 carboxylic acids Chemical class 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000004140 cleaning Methods 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 238000004040 coloring Methods 0.000 description 3

- 239000000386 donor Substances 0.000 description 3

- BHXIWUJLHYHGSJ-UHFFFAOYSA-N ethyl 3-ethoxypropanoate Chemical compound CCOCCC(=O)OCC BHXIWUJLHYHGSJ-UHFFFAOYSA-N 0.000 description 3

- 230000005669 field effect Effects 0.000 description 3

- 239000007789 gas Substances 0.000 description 3

- 125000000623 heterocyclic group Chemical group 0.000 description 3

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 3

- 238000003384 imaging method Methods 0.000 description 3

- 239000003999 initiator Substances 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 239000007791 liquid phase Substances 0.000 description 3

- VSQYNPJPULBZKU-UHFFFAOYSA-N mercury xenon Chemical compound [Xe].[Hg] VSQYNPJPULBZKU-UHFFFAOYSA-N 0.000 description 3

- 150000002734 metacrylic acid derivatives Chemical class 0.000 description 3

- 125000002496 methyl group Chemical group [H]C([H])([H])* 0.000 description 3

- ZIUHHBKFKCYYJD-UHFFFAOYSA-N n,n'-methylenebisacrylamide Chemical compound C=CC(=O)NCNC(=O)C=C ZIUHHBKFKCYYJD-UHFFFAOYSA-N 0.000 description 3

- 239000002105 nanoparticle Substances 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 238000000016 photochemical curing Methods 0.000 description 3

- 239000003504 photosensitizing agent Substances 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 229920000728 polyester Polymers 0.000 description 3

- 229920002223 polystyrene Polymers 0.000 description 3

- 229920002451 polyvinyl alcohol Polymers 0.000 description 3

- LLHKCFNBLRBOGN-UHFFFAOYSA-N propylene glycol methyl ether acetate Chemical compound COCC(C)OC(C)=O LLHKCFNBLRBOGN-UHFFFAOYSA-N 0.000 description 3

- 230000002829 reductive effect Effects 0.000 description 3

- 239000011347 resin Substances 0.000 description 3

- 229920005989 resin Polymers 0.000 description 3

- 238000004528 spin coating Methods 0.000 description 3

- 239000004094 surface-active agent Substances 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- 239000012808 vapor phase Substances 0.000 description 3

- 239000008096 xylene Substances 0.000 description 3

- NIXOWILDQLNWCW-UHFFFAOYSA-N 2-Propenoic acid Natural products OC(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- INQDDHNZXOAFFD-UHFFFAOYSA-N 2-[2-(2-prop-2-enoyloxyethoxy)ethoxy]ethyl prop-2-enoate Chemical compound C=CC(=O)OCCOCCOCCOC(=O)C=C INQDDHNZXOAFFD-UHFFFAOYSA-N 0.000 description 2

- HCLJOFJIQIJXHS-UHFFFAOYSA-N 2-[2-[2-(2-prop-2-enoyloxyethoxy)ethoxy]ethoxy]ethyl prop-2-enoate Chemical compound C=CC(=O)OCCOCCOCCOCCOC(=O)C=C HCLJOFJIQIJXHS-UHFFFAOYSA-N 0.000 description 2

- TXBCBTDQIULDIA-UHFFFAOYSA-N 2-[[3-hydroxy-2,2-bis(hydroxymethyl)propoxy]methyl]-2-(hydroxymethyl)propane-1,3-diol Chemical compound OCC(CO)(CO)COCC(CO)(CO)CO TXBCBTDQIULDIA-UHFFFAOYSA-N 0.000 description 2

- KXGFMDJXCMQABM-UHFFFAOYSA-N 2-methoxy-6-methylphenol Chemical compound [CH]OC1=CC=CC([CH])=C1O KXGFMDJXCMQABM-UHFFFAOYSA-N 0.000 description 2

- KUDUQBURMYMBIJ-UHFFFAOYSA-N 2-prop-2-enoyloxyethyl prop-2-enoate Chemical compound C=CC(=O)OCCOC(=O)C=C KUDUQBURMYMBIJ-UHFFFAOYSA-N 0.000 description 2

- CDSULTPOCMWJCM-UHFFFAOYSA-N 4h-chromene-2,3-dione Chemical class C1=CC=C2OC(=O)C(=O)CC2=C1 CDSULTPOCMWJCM-UHFFFAOYSA-N 0.000 description 2

- PAYRUJLWNCNPSJ-UHFFFAOYSA-N Aniline Chemical compound NC1=CC=CC=C1 PAYRUJLWNCNPSJ-UHFFFAOYSA-N 0.000 description 2

- RTZKZFJDLAIYFH-UHFFFAOYSA-N Diethyl ether Chemical group CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 2

- BWGNESOTFCXPMA-UHFFFAOYSA-N Dihydrogen disulfide Chemical compound SS BWGNESOTFCXPMA-UHFFFAOYSA-N 0.000 description 2

- 229920002430 Fibre-reinforced plastic Polymers 0.000 description 2

- 229930194542 Keto Natural products 0.000 description 2

- CERQOIWHTDAKMF-UHFFFAOYSA-N Methacrylic acid Chemical compound CC(=C)C(O)=O CERQOIWHTDAKMF-UHFFFAOYSA-N 0.000 description 2

- JLTDJTHDQAWBAV-UHFFFAOYSA-N N,N-dimethylaniline Chemical compound CN(C)C1=CC=CC=C1 JLTDJTHDQAWBAV-UHFFFAOYSA-N 0.000 description 2

- UFWIBTONFRDIAS-UHFFFAOYSA-N Naphthalene Chemical compound C1=CC=CC2=CC=CC=C21 UFWIBTONFRDIAS-UHFFFAOYSA-N 0.000 description 2

- 229940123973 Oxygen scavenger Drugs 0.000 description 2

- 239000002033 PVDF binder Substances 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- 229920002845 Poly(methacrylic acid) Polymers 0.000 description 2

- 239000004952 Polyamide Substances 0.000 description 2

- 239000004642 Polyimide Substances 0.000 description 2

- 239000004721 Polyphenylene oxide Substances 0.000 description 2

- ATUOYWHBWRKTHZ-UHFFFAOYSA-N Propane Chemical compound CCC ATUOYWHBWRKTHZ-UHFFFAOYSA-N 0.000 description 2

- JUJWROOIHBZHMG-UHFFFAOYSA-N Pyridine Chemical compound C1=CC=NC=C1 JUJWROOIHBZHMG-UHFFFAOYSA-N 0.000 description 2

- LOUPRKONTZGTKE-WZBLMQSHSA-N Quinine Chemical compound C([C@H]([C@H](C1)C=C)C2)C[N@@]1[C@@H]2[C@H](O)C1=CC=NC2=CC=C(OC)C=C21 LOUPRKONTZGTKE-WZBLMQSHSA-N 0.000 description 2

- SMWDFEZZVXVKRB-UHFFFAOYSA-N Quinoline Chemical compound N1=CC=CC2=CC=CC=C21 SMWDFEZZVXVKRB-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- FOIXSVOLVBLSDH-UHFFFAOYSA-N Silver ion Chemical compound [Ag+] FOIXSVOLVBLSDH-UHFFFAOYSA-N 0.000 description 2

- PPBRXRYQALVLMV-UHFFFAOYSA-N Styrene Chemical group C=CC1=CC=CC=C1 PPBRXRYQALVLMV-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- KKEYFWRCBNTPAC-UHFFFAOYSA-N Terephthalic acid Chemical compound OC(=O)C1=CC=C(C(O)=O)C=C1 KKEYFWRCBNTPAC-UHFFFAOYSA-N 0.000 description 2

- DZBUGLKDJFMEHC-UHFFFAOYSA-N acridine Chemical compound C1=CC=CC2=CC3=CC=CC=C3N=C21 DZBUGLKDJFMEHC-UHFFFAOYSA-N 0.000 description 2

- 239000011149 active material Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- WNLRTRBMVRJNCN-UHFFFAOYSA-N adipic acid Chemical compound OC(=O)CCCCC(O)=O WNLRTRBMVRJNCN-UHFFFAOYSA-N 0.000 description 2

- 150000001298 alcohols Chemical class 0.000 description 2

- 125000002723 alicyclic group Chemical group 0.000 description 2

- 125000002877 alkyl aryl group Chemical group 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 150000001412 amines Chemical class 0.000 description 2

- 125000000129 anionic group Chemical group 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 125000003710 aryl alkyl group Chemical group 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- GKRVGTLVYRYCFR-UHFFFAOYSA-N butane-1,4-diol;2-methylidenebutanedioic acid Chemical compound OCCCCO.OC(=O)CC(=C)C(O)=O.OC(=O)CC(=C)C(O)=O GKRVGTLVYRYCFR-UHFFFAOYSA-N 0.000 description 2

- 150000001733 carboxylic acid esters Chemical class 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 239000011651 chromium Substances 0.000 description 2

- 229920001940 conductive polymer Polymers 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 238000012937 correction Methods 0.000 description 2

- ZYGHJZDHTFUPRJ-UHFFFAOYSA-N coumarin Chemical compound C1=CC=C2OC(=O)C=CC2=C1 ZYGHJZDHTFUPRJ-UHFFFAOYSA-N 0.000 description 2

- BGTOWKSIORTVQH-UHFFFAOYSA-N cyclopentanone Chemical compound O=C1CCCC1 BGTOWKSIORTVQH-UHFFFAOYSA-N 0.000 description 2

- HQWPLXHWEZZGKY-UHFFFAOYSA-N diethylzinc Chemical compound CC[Zn]CC HQWPLXHWEZZGKY-UHFFFAOYSA-N 0.000 description 2

- CZZYITDELCSZES-UHFFFAOYSA-N diphenylmethane Chemical compound C=1C=CC=CC=1CC1=CC=CC=C1 CZZYITDELCSZES-UHFFFAOYSA-N 0.000 description 2

- 150000002019 disulfides Chemical class 0.000 description 2

- 125000003700 epoxy group Chemical group 0.000 description 2

- 239000003822 epoxy resin Substances 0.000 description 2

- 125000001495 ethyl group Chemical group [H]C([H])([H])C([H])([H])* 0.000 description 2

- 239000011151 fibre-reinforced plastic Substances 0.000 description 2

- 239000012467 final product Substances 0.000 description 2

- YLQWCDOCJODRMT-UHFFFAOYSA-N fluoren-9-one Chemical compound C1=CC=C2C(=O)C3=CC=CC=C3C2=C1 YLQWCDOCJODRMT-UHFFFAOYSA-N 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 229920001519 homopolymer Polymers 0.000 description 2

- LDHQCZJRKDOVOX-IHWYPQMZSA-N isocrotonic acid Chemical compound C\C=C/C(O)=O LDHQCZJRKDOVOX-IHWYPQMZSA-N 0.000 description 2

- 239000012948 isocyanate Substances 0.000 description 2

- 150000002513 isocyanates Chemical class 0.000 description 2

- QQVIHTHCMHWDBS-UHFFFAOYSA-N isophthalic acid Chemical compound OC(=O)C1=CC=CC(C(O)=O)=C1 QQVIHTHCMHWDBS-UHFFFAOYSA-N 0.000 description 2

- 125000000468 ketone group Chemical group 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 230000000670 limiting effect Effects 0.000 description 2

- 238000005259 measurement Methods 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- LVHBHZANLOWSRM-UHFFFAOYSA-N methylenebutanedioic acid Natural products OC(=O)CC(=C)C(O)=O LVHBHZANLOWSRM-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229920003986 novolac Polymers 0.000 description 2

- 229920001568 phenolic resin Polymers 0.000 description 2

- 239000005011 phenolic resin Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 2

- 229920002647 polyamide Polymers 0.000 description 2

- 239000004417 polycarbonate Substances 0.000 description 2

- 229920000515 polycarbonate Polymers 0.000 description 2

- 229920002530 polyetherether ketone Polymers 0.000 description 2

- 229920001223 polyethylene glycol Polymers 0.000 description 2

- 229920000139 polyethylene terephthalate Polymers 0.000 description 2

- 239000005020 polyethylene terephthalate Substances 0.000 description 2

- 229920001721 polyimide Polymers 0.000 description 2

- 239000002861 polymer material Substances 0.000 description 2

- 229920000069 polyphenylene sulfide Polymers 0.000 description 2

- 229920002981 polyvinylidene fluoride Polymers 0.000 description 2

- 238000001556 precipitation Methods 0.000 description 2

- 230000009257 reactivity Effects 0.000 description 2

- 230000010076 replication Effects 0.000 description 2

- CXMXRPHRNRROMY-UHFFFAOYSA-N sebacic acid Chemical compound OC(=O)CCCCCCCCC(O)=O CXMXRPHRNRROMY-UHFFFAOYSA-N 0.000 description 2

- 230000001235 sensitizing effect Effects 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 125000000547 substituted alkyl group Chemical group 0.000 description 2

- 150000005846 sugar alcohols Polymers 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- LDHQCZJRKDOVOX-UHFFFAOYSA-N trans-crotonic acid Natural products CC=CC(O)=O LDHQCZJRKDOVOX-UHFFFAOYSA-N 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- 238000011282 treatment Methods 0.000 description 2

- 125000002023 trifluoromethyl group Chemical group FC(F)(F)* 0.000 description 2

- OAKFFVBGTSPYEG-UHFFFAOYSA-N (4-prop-2-enoyloxycyclohexyl) prop-2-enoate Chemical compound C=CC(=O)OC1CCC(OC(=O)C=C)CC1 OAKFFVBGTSPYEG-UHFFFAOYSA-N 0.000 description 1

- FGTUGLXGCCYKPJ-SPIKMXEPSA-N (Z)-but-2-enedioic acid 2-[2-(2-hydroxyethoxy)ethoxy]ethanol Chemical compound OC(=O)\C=C/C(O)=O.OC(=O)\C=C/C(O)=O.OCCOCCOCCO FGTUGLXGCCYKPJ-SPIKMXEPSA-N 0.000 description 1

- PFNQVRZLDWYSCW-UHFFFAOYSA-N (fluoren-9-ylideneamino) n-naphthalen-1-ylcarbamate Chemical compound C12=CC=CC=C2C2=CC=CC=C2C1=NOC(=O)NC1=CC=CC2=CC=CC=C12 PFNQVRZLDWYSCW-UHFFFAOYSA-N 0.000 description 1

- SORHAFXJCOXOIC-CCAGOZQPSA-N (z)-4-[2-[(z)-3-carboxyprop-2-enoyl]oxyethoxy]-4-oxobut-2-enoic acid Chemical compound OC(=O)\C=C/C(=O)OCCOC(=O)\C=C/C(O)=O SORHAFXJCOXOIC-CCAGOZQPSA-N 0.000 description 1

- LCPUCXXYIYXLJY-UHFFFAOYSA-N 1,1,2,4,4,4-hexafluorobutyl 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OC(F)(F)C(F)CC(F)(F)F LCPUCXXYIYXLJY-UHFFFAOYSA-N 0.000 description 1

- MYWOJODOMFBVCB-UHFFFAOYSA-N 1,2,6-trimethylphenanthrene Chemical compound CC1=CC=C2C3=CC(C)=CC=C3C=CC2=C1C MYWOJODOMFBVCB-UHFFFAOYSA-N 0.000 description 1

- VDYWHVQKENANGY-UHFFFAOYSA-N 1,3-Butyleneglycol dimethacrylate Chemical compound CC(=C)C(=O)OC(C)CCOC(=O)C(C)=C VDYWHVQKENANGY-UHFFFAOYSA-N 0.000 description 1

- OGBWMWKMTUSNKE-UHFFFAOYSA-N 1-(2-methylprop-2-enoyloxy)hexyl 2-methylprop-2-enoate Chemical compound CCCCCC(OC(=O)C(C)=C)OC(=O)C(C)=C OGBWMWKMTUSNKE-UHFFFAOYSA-N 0.000 description 1

- HUDYANRNMZDQGA-UHFFFAOYSA-N 1-[4-(dimethylamino)phenyl]ethanone Chemical compound CN(C)C1=CC=C(C(C)=O)C=C1 HUDYANRNMZDQGA-UHFFFAOYSA-N 0.000 description 1

- JOLQKTGDSGKSKJ-UHFFFAOYSA-N 1-ethoxypropan-2-ol Chemical compound CCOCC(C)O JOLQKTGDSGKSKJ-UHFFFAOYSA-N 0.000 description 1

- VOBUAPTXJKMNCT-UHFFFAOYSA-N 1-prop-2-enoyloxyhexyl prop-2-enoate Chemical compound CCCCCC(OC(=O)C=C)OC(=O)C=C VOBUAPTXJKMNCT-UHFFFAOYSA-N 0.000 description 1

- ZYZYQCACSQDPSB-UHFFFAOYSA-N 12,15-dioxatricyclo[8.6.0.02,7]hexadeca-1(10),2,4,6,8-pentaene-11,16-dione Chemical compound O=C1OCCOC(=O)C2=C1C=CC1=CC=CC=C21 ZYZYQCACSQDPSB-UHFFFAOYSA-N 0.000 description 1

- XWTLWBDPLPQCOR-UHFFFAOYSA-N 2,6-diethyl-n,n-dimethylaniline Chemical compound CCC1=CC=CC(CC)=C1N(C)C XWTLWBDPLPQCOR-UHFFFAOYSA-N 0.000 description 1

- SMZOUWXMTYCWNB-UHFFFAOYSA-N 2-(2-methoxy-5-methylphenyl)ethanamine Chemical compound COC1=CC=C(C)C=C1CCN SMZOUWXMTYCWNB-UHFFFAOYSA-N 0.000 description 1

- JAHNSTQSQJOJLO-UHFFFAOYSA-N 2-(3-fluorophenyl)-1h-imidazole Chemical compound FC1=CC=CC(C=2NC=CN=2)=C1 JAHNSTQSQJOJLO-UHFFFAOYSA-N 0.000 description 1

- APJRQJNSYFWQJD-GGWOSOGESA-N 2-[(e)-but-2-enoyl]oxyethyl (e)-but-2-enoate Chemical compound C\C=C\C(=O)OCCOC(=O)\C=C\C APJRQJNSYFWQJD-GGWOSOGESA-N 0.000 description 1

- APJRQJNSYFWQJD-GLIMQPGKSA-N 2-[(z)-but-2-enoyl]oxyethyl (z)-but-2-enoate Chemical compound C\C=C/C(=O)OCCOC(=O)\C=C/C APJRQJNSYFWQJD-GLIMQPGKSA-N 0.000 description 1

- HWSSEYVMGDIFMH-UHFFFAOYSA-N 2-[2-[2-(2-methylprop-2-enoyloxy)ethoxy]ethoxy]ethyl 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCCOCCOCCOC(=O)C(C)=C HWSSEYVMGDIFMH-UHFFFAOYSA-N 0.000 description 1

- GTELLNMUWNJXMQ-UHFFFAOYSA-N 2-ethyl-2-(hydroxymethyl)propane-1,3-diol;prop-2-enoic acid Chemical class OC(=O)C=C.OC(=O)C=C.OC(=O)C=C.CCC(CO)(CO)CO GTELLNMUWNJXMQ-UHFFFAOYSA-N 0.000 description 1

- TURITJIWSQEMDB-UHFFFAOYSA-N 2-methyl-n-[(2-methylprop-2-enoylamino)methyl]prop-2-enamide Chemical compound CC(=C)C(=O)NCNC(=O)C(C)=C TURITJIWSQEMDB-UHFFFAOYSA-N 0.000 description 1

- YBKWKURHPIBUEM-UHFFFAOYSA-N 2-methyl-n-[6-(2-methylprop-2-enoylamino)hexyl]prop-2-enamide Chemical compound CC(=C)C(=O)NCCCCCCNC(=O)C(C)=C YBKWKURHPIBUEM-UHFFFAOYSA-N 0.000 description 1

- GDHSRTFITZTMMP-UHFFFAOYSA-N 2-methylidenebutanedioic acid;propane-1,2-diol Chemical compound CC(O)CO.OC(=O)CC(=C)C(O)=O.OC(=O)CC(=C)C(O)=O GDHSRTFITZTMMP-UHFFFAOYSA-N 0.000 description 1

- VFZKVQVQOMDJEG-UHFFFAOYSA-N 2-prop-2-enoyloxypropyl prop-2-enoate Chemical compound C=CC(=O)OC(C)COC(=O)C=C VFZKVQVQOMDJEG-UHFFFAOYSA-N 0.000 description 1

- RVBUGGBMJDPOST-UHFFFAOYSA-N 2-thiobarbituric acid Chemical compound O=C1CC(=O)NC(=S)N1 RVBUGGBMJDPOST-UHFFFAOYSA-N 0.000 description 1

- BCHZICNRHXRCHY-UHFFFAOYSA-N 2h-oxazine Chemical compound N1OC=CC=C1 BCHZICNRHXRCHY-UHFFFAOYSA-N 0.000 description 1

- AGIJRRREJXSQJR-UHFFFAOYSA-N 2h-thiazine Chemical compound N1SC=CC=C1 AGIJRRREJXSQJR-UHFFFAOYSA-N 0.000 description 1

- GOLORTLGFDVFDW-UHFFFAOYSA-N 3-(1h-benzimidazol-2-yl)-7-(diethylamino)chromen-2-one Chemical compound C1=CC=C2NC(C3=CC4=CC=C(C=C4OC3=O)N(CC)CC)=NC2=C1 GOLORTLGFDVFDW-UHFFFAOYSA-N 0.000 description 1

- KEPGNQLKWDULGD-UHFFFAOYSA-N 3-(3-prop-2-enoyloxypropoxy)propyl prop-2-enoate Chemical compound C=CC(=O)OCCCOCCCOC(=O)C=C KEPGNQLKWDULGD-UHFFFAOYSA-N 0.000 description 1

- MESJRHHDBDCQTH-UHFFFAOYSA-N 3-(dimethylamino)phenol Chemical compound CN(C)C1=CC=CC(O)=C1 MESJRHHDBDCQTH-UHFFFAOYSA-N 0.000 description 1

- WUPHOULIZUERAE-UHFFFAOYSA-N 3-(oxolan-2-yl)propanoic acid Chemical compound OC(=O)CCC1CCCO1 WUPHOULIZUERAE-UHFFFAOYSA-N 0.000 description 1

- CHHCCYVOJBBCIY-UHFFFAOYSA-N 3-chloro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=CC(Cl)=C1 CHHCCYVOJBBCIY-UHFFFAOYSA-N 0.000 description 1

- JVYPLRBSTQJKSU-UHFFFAOYSA-N 3-ethoxy-n,n-dimethylaniline Chemical compound CCOC1=CC=CC(N(C)C)=C1 JVYPLRBSTQJKSU-UHFFFAOYSA-N 0.000 description 1

- FQMIAEWUVYWVNB-UHFFFAOYSA-N 3-prop-2-enoyloxybutyl prop-2-enoate Chemical compound C=CC(=O)OC(C)CCOC(=O)C=C FQMIAEWUVYWVNB-UHFFFAOYSA-N 0.000 description 1

- XOJWAAUYNWGQAU-UHFFFAOYSA-N 4-(2-methylprop-2-enoyloxy)butyl 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCCCCOC(=O)C(C)=C XOJWAAUYNWGQAU-UHFFFAOYSA-N 0.000 description 1

- JYMNQRQQBJIMCV-UHFFFAOYSA-N 4-(dimethylamino)benzonitrile Chemical compound CN(C)C1=CC=C(C#N)C=C1 JYMNQRQQBJIMCV-UHFFFAOYSA-N 0.000 description 1

- KTZOPXAHXBBDBX-FCXRPNKRSA-N 4-[(e)-but-2-enoyl]oxybutyl (e)-but-2-enoate Chemical compound C\C=C\C(=O)OCCCCOC(=O)\C=C\C KTZOPXAHXBBDBX-FCXRPNKRSA-N 0.000 description 1

- DBCAQXHNJOFNGC-UHFFFAOYSA-N 4-bromo-1,1,1-trifluorobutane Chemical compound FC(F)(F)CCCBr DBCAQXHNJOFNGC-UHFFFAOYSA-N 0.000 description 1

- XYZWMVYYUIMRIZ-UHFFFAOYSA-N 4-bromo-n,n-dimethylaniline Chemical compound CN(C)C1=CC=C(Br)C=C1 XYZWMVYYUIMRIZ-UHFFFAOYSA-N 0.000 description 1

- IONGEXNDPXANJD-UHFFFAOYSA-N 4-chloro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=C(Cl)C=C1 IONGEXNDPXANJD-UHFFFAOYSA-N 0.000 description 1

- NOTZHLDTUSLGBM-UHFFFAOYSA-N 4-ethoxy-n,n-dimethylaniline Chemical compound CCOC1=CC=C(N(C)C)C=C1 NOTZHLDTUSLGBM-UHFFFAOYSA-N 0.000 description 1

- YJEHCGOJNJUOII-UHFFFAOYSA-N 4-fluoro-n,n-dimethylaniline Chemical compound CN(C)C1=CC=C(F)C=C1 YJEHCGOJNJUOII-UHFFFAOYSA-N 0.000 description 1

- JHWGFJBTMHEZME-UHFFFAOYSA-N 4-prop-2-enoyloxybutyl prop-2-enoate Chemical compound C=CC(=O)OCCCCOC(=O)C=C JHWGFJBTMHEZME-UHFFFAOYSA-N 0.000 description 1

- FVLDKFWYESAPIB-UHFFFAOYSA-N 6-ethoxysulfanyl-2-[(6-ethoxysulfanyl-1,3-benzothiazol-2-yl)disulfanyl]-1,3-benzothiazole Chemical compound C1=C(SOCC)C=C2SC(SSC3=NC4=CC=C(C=C4S3)SOCC)=NC2=C1 FVLDKFWYESAPIB-UHFFFAOYSA-N 0.000 description 1

- GJCOSYZMQJWQCA-UHFFFAOYSA-N 9H-xanthene Chemical compound C1=CC=C2CC3=CC=CC=C3OC2=C1 GJCOSYZMQJWQCA-UHFFFAOYSA-N 0.000 description 1

- 229920003026 Acene Polymers 0.000 description 1

- NIXOWILDQLNWCW-UHFFFAOYSA-M Acrylate Chemical compound [O-]C(=O)C=C NIXOWILDQLNWCW-UHFFFAOYSA-M 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- 101150059231 CPI1 gene Proteins 0.000 description 1

- LAKGQRZUKPZJDH-GLIMQPGKSA-N C\C=C/C(=O)OCC(CO)(CO)COC(=O)\C=C/C Chemical compound C\C=C/C(=O)OCC(CO)(CO)COC(=O)\C=C/C LAKGQRZUKPZJDH-GLIMQPGKSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- 239000004215 Carbon black (E152) Substances 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 235000001258 Cinchona calisaya Nutrition 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- RWSOTUBLDIXVET-UHFFFAOYSA-N Dihydrogen sulfide Chemical class S RWSOTUBLDIXVET-UHFFFAOYSA-N 0.000 description 1

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 1

- JOYRKODLDBILNP-UHFFFAOYSA-N Ethyl urethane Chemical compound CCOC(N)=O JOYRKODLDBILNP-UHFFFAOYSA-N 0.000 description 1

- 239000005977 Ethylene Substances 0.000 description 1

- IAYPIBMASNFSPL-UHFFFAOYSA-N Ethylene oxide Chemical compound C1CO1 IAYPIBMASNFSPL-UHFFFAOYSA-N 0.000 description 1

- PXGOKWXKJXAPGV-UHFFFAOYSA-N Fluorine Chemical compound FF PXGOKWXKJXAPGV-UHFFFAOYSA-N 0.000 description 1

- 229910002601 GaN Inorganic materials 0.000 description 1

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 1

- JMASRVWKEDWRBT-UHFFFAOYSA-N Gallium nitride Chemical compound [Ga]#N JMASRVWKEDWRBT-UHFFFAOYSA-N 0.000 description 1

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 1

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 1

- SIKJAQJRHWYJAI-UHFFFAOYSA-N Indole Chemical compound C1=CC=C2NC=CC2=C1 SIKJAQJRHWYJAI-UHFFFAOYSA-N 0.000 description 1

- VQTUBCCKSQIDNK-UHFFFAOYSA-N Isobutene Chemical group CC(C)=C VQTUBCCKSQIDNK-UHFFFAOYSA-N 0.000 description 1

- BZORFPDSXLZWJF-UHFFFAOYSA-N N,N-dimethyl-1,4-phenylenediamine Chemical compound CN(C)C1=CC=C(N)C=C1 BZORFPDSXLZWJF-UHFFFAOYSA-N 0.000 description 1

- LRYAPECLTRYCTR-UHFFFAOYSA-N NC(=O)C=C.NC(=O)C=C.NC(=O)C=C.NCCNCCN Chemical compound NC(=O)C=C.NC(=O)C=C.NC(=O)C=C.NCCNCCN LRYAPECLTRYCTR-UHFFFAOYSA-N 0.000 description 1

- 101100213966 Neurospora crassa (strain ATCC 24698 / 74-OR23-1A / CBS 708.71 / DSM 1257 / FGSC 987) ypi-1 gene Proteins 0.000 description 1

- 239000004677 Nylon Substances 0.000 description 1

- YDMUKYUKJKCOEE-SPIKMXEPSA-N OC(=O)\C=C/C(O)=O.OC(=O)\C=C/C(O)=O.OCC(CO)(CO)CO Chemical compound OC(=O)\C=C/C(O)=O.OC(=O)\C=C/C(O)=O.OCC(CO)(CO)CO YDMUKYUKJKCOEE-SPIKMXEPSA-N 0.000 description 1

- MUBZPKHOEPUJKR-UHFFFAOYSA-N Oxalic acid Chemical compound OC(=O)C(O)=O MUBZPKHOEPUJKR-UHFFFAOYSA-N 0.000 description 1

- 229920000144 PEDOT:PSS Polymers 0.000 description 1

- AMFGWXWBFGVCKG-UHFFFAOYSA-N Panavia opaque Chemical compound C1=CC(OCC(O)COC(=O)C(=C)C)=CC=C1C(C)(C)C1=CC=C(OCC(O)COC(=O)C(C)=C)C=C1 AMFGWXWBFGVCKG-UHFFFAOYSA-N 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N Phenol Chemical compound OC1=CC=CC=C1 ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 206010034972 Photosensitivity reaction Diseases 0.000 description 1

- 239000004696 Poly ether ether ketone Substances 0.000 description 1

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 229920001665 Poly-4-vinylphenol Polymers 0.000 description 1

- 229920001744 Polyaldehyde Polymers 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 239000002202 Polyethylene glycol Substances 0.000 description 1

- 239000004743 Polypropylene Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- OFOBLEOULBTSOW-UHFFFAOYSA-N Propanedioic acid Natural products OC(=O)CC(O)=O OFOBLEOULBTSOW-UHFFFAOYSA-N 0.000 description 1

- 206010070834 Sensitisation Diseases 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- 229920002125 Sokalan® Polymers 0.000 description 1

- FZWLAAWBMGSTSO-UHFFFAOYSA-N Thiazole Chemical compound C1=CSC=N1 FZWLAAWBMGSTSO-UHFFFAOYSA-N 0.000 description 1

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 1

- ZJCCRDAZUWHFQH-UHFFFAOYSA-N Trimethylolpropane Chemical compound CCC(CO)(CO)CO ZJCCRDAZUWHFQH-UHFFFAOYSA-N 0.000 description 1

- OKKRPWIIYQTPQF-UHFFFAOYSA-N Trimethylolpropane trimethacrylate Chemical compound CC(=C)C(=O)OCC(CC)(COC(=O)C(C)=C)COC(=O)C(C)=C OKKRPWIIYQTPQF-UHFFFAOYSA-N 0.000 description 1

- XSQUKJJJFZCRTK-UHFFFAOYSA-N Urea Chemical compound NC(N)=O XSQUKJJJFZCRTK-UHFFFAOYSA-N 0.000 description 1

- 239000005083 Zinc sulfide Substances 0.000 description 1

- GQPVFBDWIUVLHG-UHFFFAOYSA-N [2,2-bis(hydroxymethyl)-3-(2-methylprop-2-enoyloxy)propyl] 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCC(CO)(CO)COC(=O)C(C)=C GQPVFBDWIUVLHG-UHFFFAOYSA-N 0.000 description 1

- CQHKDHVZYZUZMJ-UHFFFAOYSA-N [2,2-bis(hydroxymethyl)-3-prop-2-enoyloxypropyl] prop-2-enoate Chemical compound C=CC(=O)OCC(CO)(CO)COC(=O)C=C CQHKDHVZYZUZMJ-UHFFFAOYSA-N 0.000 description 1

- ULQMPOIOSDXIGC-UHFFFAOYSA-N [2,2-dimethyl-3-(2-methylprop-2-enoyloxy)propyl] 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCC(C)(C)COC(=O)C(C)=C ULQMPOIOSDXIGC-UHFFFAOYSA-N 0.000 description 1

- JUDXBRVLWDGRBC-UHFFFAOYSA-N [2-(hydroxymethyl)-3-(2-methylprop-2-enoyloxy)-2-(2-methylprop-2-enoyloxymethyl)propyl] 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCC(CO)(COC(=O)C(C)=C)COC(=O)C(C)=C JUDXBRVLWDGRBC-UHFFFAOYSA-N 0.000 description 1

- HVVWZTWDBSEWIH-UHFFFAOYSA-N [2-(hydroxymethyl)-3-prop-2-enoyloxy-2-(prop-2-enoyloxymethyl)propyl] prop-2-enoate Chemical compound C=CC(=O)OCC(CO)(COC(=O)C=C)COC(=O)C=C HVVWZTWDBSEWIH-UHFFFAOYSA-N 0.000 description 1

- LAKGQRZUKPZJDH-GGWOSOGESA-N [2-[[(e)-but-2-enoyl]oxymethyl]-3-hydroxy-2-(hydroxymethyl)propyl] (e)-but-2-enoate Chemical compound C\C=C\C(=O)OCC(CO)(CO)COC(=O)\C=C\C LAKGQRZUKPZJDH-GGWOSOGESA-N 0.000 description 1

- SWHLOXLFJPTYTL-UHFFFAOYSA-N [2-methyl-3-(2-methylprop-2-enoyloxy)-2-(2-methylprop-2-enoyloxymethyl)propyl] 2-methylprop-2-enoate Chemical compound CC(=C)C(=O)OCC(C)(COC(=O)C(C)=C)COC(=O)C(C)=C SWHLOXLFJPTYTL-UHFFFAOYSA-N 0.000 description 1

- HSZUHSXXAOWGQY-UHFFFAOYSA-N [2-methyl-3-prop-2-enoyloxy-2-(prop-2-enoyloxymethyl)propyl] prop-2-enoate Chemical compound C=CC(=O)OCC(C)(COC(=O)C=C)COC(=O)C=C HSZUHSXXAOWGQY-UHFFFAOYSA-N 0.000 description 1

- MPIAGWXWVAHQBB-UHFFFAOYSA-N [3-prop-2-enoyloxy-2-[[3-prop-2-enoyloxy-2,2-bis(prop-2-enoyloxymethyl)propoxy]methyl]-2-(prop-2-enoyloxymethyl)propyl] prop-2-enoate Chemical compound C=CC(=O)OCC(COC(=O)C=C)(COC(=O)C=C)COCC(COC(=O)C=C)(COC(=O)C=C)COC(=O)C=C MPIAGWXWVAHQBB-UHFFFAOYSA-N 0.000 description 1

- MNSFIQQZRZGXMM-UHFFFAOYSA-N [N-]=[N+]=[N-].[N-]=[N+]=[N-].N(=[N+]=[N-])C1=CC=C(C=C2C(C(CC(C2)C)=CC2=CC=C(C=C2)N=[N+]=[N-])=O)C=C1 Chemical compound [N-]=[N+]=[N-].[N-]=[N+]=[N-].N(=[N+]=[N-])C1=CC=C(C=C2C(C(CC(C2)C)=CC2=CC=C(C=C2)N=[N+]=[N-])=O)C=C1 MNSFIQQZRZGXMM-UHFFFAOYSA-N 0.000 description 1

- 238000002679 ablation Methods 0.000 description 1

- 150000001242 acetic acid derivatives Chemical class 0.000 description 1

- 125000000218 acetic acid group Chemical group C(C)(=O)* 0.000 description 1

- 239000002253 acid Substances 0.000 description 1

- 239000000999 acridine dye Substances 0.000 description 1

- DZBUGLKDJFMEHC-UHFFFAOYSA-O acridine;hydron Chemical compound C1=CC=CC2=CC3=CC=CC=C3[NH+]=C21 DZBUGLKDJFMEHC-UHFFFAOYSA-O 0.000 description 1

- 125000005396 acrylic acid ester group Chemical group 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 235000011037 adipic acid Nutrition 0.000 description 1

- 239000001361 adipic acid Substances 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 125000003342 alkenyl group Chemical group 0.000 description 1

- 125000005376 alkyl siloxane group Chemical group 0.000 description 1

- 125000000304 alkynyl group Chemical group 0.000 description 1

- 125000003277 amino group Chemical group 0.000 description 1

- 125000004103 aminoalkyl group Chemical group 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 238000000137 annealing Methods 0.000 description 1

- 239000003963 antioxidant agent Substances 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- 150000001540 azides Chemical class 0.000 description 1

- 125000005235 azinium group Chemical group 0.000 description 1

- 239000000987 azo dye Substances 0.000 description 1

- 229910052454 barium strontium titanate Inorganic materials 0.000 description 1

- JRPBQTZRNDNNOP-UHFFFAOYSA-N barium titanate Chemical compound [Ba+2].[Ba+2].[O-][Ti]([O-])([O-])[O-] JRPBQTZRNDNNOP-UHFFFAOYSA-N 0.000 description 1

- 229910002113 barium titanate Inorganic materials 0.000 description 1

- 229910021523 barium zirconate Inorganic materials 0.000 description 1

- DQBAOWPVHRWLJC-UHFFFAOYSA-N barium(2+);dioxido(oxo)zirconium Chemical compound [Ba+2].[O-][Zr]([O-])=O DQBAOWPVHRWLJC-UHFFFAOYSA-N 0.000 description 1

- JUPQTSLXMOCDHR-UHFFFAOYSA-N benzene-1,4-diol;bis(4-fluorophenyl)methanone Chemical compound OC1=CC=C(O)C=C1.C1=CC(F)=CC=C1C(=O)C1=CC=C(F)C=C1 JUPQTSLXMOCDHR-UHFFFAOYSA-N 0.000 description 1

- 125000001797 benzyl group Chemical group [H]C1=C([H])C([H])=C(C([H])=C1[H])C([H])([H])* 0.000 description 1

- 230000001588 bifunctional effect Effects 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000007844 bleaching agent Substances 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 150000001642 boronic acid derivatives Chemical class 0.000 description 1

- 239000005388 borosilicate glass Substances 0.000 description 1

- 125000001246 bromo group Chemical group Br* 0.000 description 1

- OZQCLFIWZYVKKK-UHFFFAOYSA-N butane-1,3-diol 2-methylidenebutanedioic acid Chemical compound CC(O)CCO.OC(=O)CC(=C)C(O)=O.OC(=O)CC(=C)C(O)=O OZQCLFIWZYVKKK-UHFFFAOYSA-N 0.000 description 1

- 125000000484 butyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- 229910052980 cadmium sulfide Inorganic materials 0.000 description 1

- 239000000298 carbocyanine Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 125000003178 carboxy group Chemical group [H]OC(*)=O 0.000 description 1

- 150000001768 cations Chemical class 0.000 description 1

- 229920002678 cellulose Polymers 0.000 description 1

- 229920003086 cellulose ether Polymers 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 238000003486 chemical etching Methods 0.000 description 1

- 239000003638 chemical reducing agent Substances 0.000 description 1

- 125000001309 chloro group Chemical group Cl* 0.000 description 1

- LOUPRKONTZGTKE-UHFFFAOYSA-N cinchonine Natural products C1C(C(C2)C=C)CCN2C1C(O)C1=CC=NC2=CC=C(OC)C=C21 LOUPRKONTZGTKE-UHFFFAOYSA-N 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 238000013329 compounding Methods 0.000 description 1

- 238000006482 condensation reaction Methods 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000008602 contraction Effects 0.000 description 1

- 229960000956 coumarin Drugs 0.000 description 1

- 235000001671 coumarin Nutrition 0.000 description 1

- 101150002418 cpi-2 gene Proteins 0.000 description 1

- 229920006037 cross link polymer Polymers 0.000 description 1

- LDHQCZJRKDOVOX-NSCUHMNNSA-N crotonic acid Chemical compound C\C=C\C(O)=O LDHQCZJRKDOVOX-NSCUHMNNSA-N 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 125000000753 cycloalkyl group Chemical group 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 230000018044 dehydration Effects 0.000 description 1

- 238000006297 dehydration reaction Methods 0.000 description 1

- 239000008367 deionised water Substances 0.000 description 1

- 229910021641 deionized water Inorganic materials 0.000 description 1

- 238000003795 desorption Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 125000004386 diacrylate group Chemical group 0.000 description 1

- FHIVAFMUCKRCQO-UHFFFAOYSA-N diazinon Chemical compound CCOP(=S)(OCC)OC1=CC(C)=NC(C(C)C)=N1 FHIVAFMUCKRCQO-UHFFFAOYSA-N 0.000 description 1

- 239000012954 diazonium Substances 0.000 description 1

- IJGRMHOSHXDMSA-UHFFFAOYSA-O diazynium Chemical compound [NH+]#N IJGRMHOSHXDMSA-UHFFFAOYSA-O 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 239000000539 dimer Substances 0.000 description 1

- 239000004205 dimethyl polysiloxane Substances 0.000 description 1

- HJYACKPVJCHPFH-UHFFFAOYSA-N dimethyl(propan-2-yloxy)alumane Chemical compound C[Al+]C.CC(C)[O-] HJYACKPVJCHPFH-UHFFFAOYSA-N 0.000 description 1

- 238000007598 dipping method Methods 0.000 description 1

- 238000010017 direct printing Methods 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 229920001971 elastomer Polymers 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 230000003628 erosive effect Effects 0.000 description 1

- DAOJMFXILKTYRL-UHFFFAOYSA-N ethane-1,2-diol;2-methylidenebutanedioic acid Chemical compound OCCO.OC(=O)CC(=C)C(O)=O.OC(=O)CC(=C)C(O)=O DAOJMFXILKTYRL-UHFFFAOYSA-N 0.000 description 1

- 125000003754 ethoxycarbonyl group Chemical group C(=O)(OCC)* 0.000 description 1

- STVZJERGLQHEKB-UHFFFAOYSA-N ethylene glycol dimethacrylate Substances CC(=C)C(=O)OCCOC(=O)C(C)=C STVZJERGLQHEKB-UHFFFAOYSA-N 0.000 description 1

- 229920002457 flexible plastic Polymers 0.000 description 1

- 229920005570 flexible polymer Polymers 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 125000001153 fluoro group Chemical group F* 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- 230000009477 glass transition Effects 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 238000009499 grossing Methods 0.000 description 1

- 229910052736 halogen Inorganic materials 0.000 description 1

- 125000005843 halogen group Chemical group 0.000 description 1

- 150000002367 halogens Chemical class 0.000 description 1

- 229930195733 hydrocarbon Natural products 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 239000000852 hydrogen donor Substances 0.000 description 1

- XMBWDFGMSWQBCA-UHFFFAOYSA-N hydrogen iodide Chemical class I XMBWDFGMSWQBCA-UHFFFAOYSA-N 0.000 description 1

- SMWDFEZZVXVKRB-UHFFFAOYSA-O hydron;quinoline Chemical compound [NH+]1=CC=CC2=CC=CC=C21 SMWDFEZZVXVKRB-UHFFFAOYSA-O 0.000 description 1

- 238000005286 illumination Methods 0.000 description 1

- 229910010272 inorganic material Inorganic materials 0.000 description 1

- 239000011147 inorganic material Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000009878 intermolecular interaction Effects 0.000 description 1

- 125000002346 iodo group Chemical group I* 0.000 description 1

- MGFYSGNNHQQTJW-UHFFFAOYSA-N iodonium Chemical compound [IH2+] MGFYSGNNHQQTJW-UHFFFAOYSA-N 0.000 description 1

- 229910052742 iron Inorganic materials 0.000 description 1

- IQPQWNKOIGAROB-UHFFFAOYSA-N isocyanate group Chemical group [N-]=C=O IQPQWNKOIGAROB-UHFFFAOYSA-N 0.000 description 1

- 125000001261 isocyanato group Chemical group *N=C=O 0.000 description 1

- ZFSLODLOARCGLH-UHFFFAOYSA-N isocyanuric acid Chemical compound OC1=NC(O)=NC(O)=N1 ZFSLODLOARCGLH-UHFFFAOYSA-N 0.000 description 1

- 125000001449 isopropyl group Chemical group [H]C([H])([H])C([H])(*)C([H])([H])[H] 0.000 description 1

- 238000010030 laminating Methods 0.000 description 1

- 238000005224 laser annealing Methods 0.000 description 1

- 238000007644 letterpress printing Methods 0.000 description 1

- QDLAGTHXVHQKRE-UHFFFAOYSA-N lichenxanthone Natural products COC1=CC(O)=C2C(=O)C3=C(C)C=C(OC)C=C3OC2=C1 QDLAGTHXVHQKRE-UHFFFAOYSA-N 0.000 description 1

- CDOSHBSSFJOMGT-UHFFFAOYSA-N linalool Chemical compound CC(C)=CCCC(C)(O)C=C CDOSHBSSFJOMGT-UHFFFAOYSA-N 0.000 description 1

- VZCYOOQTPOCHFL-UPHRSURJSA-N maleic acid Chemical compound OC(=O)\C=C/C(O)=O VZCYOOQTPOCHFL-UPHRSURJSA-N 0.000 description 1

- 239000011976 maleic acid Substances 0.000 description 1

- 150000002688 maleic acid derivatives Chemical class 0.000 description 1

- 125000005358 mercaptoalkyl group Chemical group 0.000 description 1

- 239000002082 metal nanoparticle Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 125000005397 methacrylic acid ester group Chemical group 0.000 description 1

- 125000001434 methanylylidene group Chemical group [H]C#[*] 0.000 description 1

- YDKNBNOOCSNPNS-UHFFFAOYSA-N methyl 1,3-benzoxazole-2-carboxylate Chemical compound C1=CC=C2OC(C(=O)OC)=NC2=C1 YDKNBNOOCSNPNS-UHFFFAOYSA-N 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 239000003607 modifier Substances 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- YNAVUWVOSKDBBP-UHFFFAOYSA-O morpholinium Chemical compound [H+].C1COCCN1 YNAVUWVOSKDBBP-UHFFFAOYSA-O 0.000 description 1

- JZBZLRKFJWQZHU-UHFFFAOYSA-N n,n,2,4,6-pentamethylaniline Chemical compound CN(C)C1=C(C)C=C(C)C=C1C JZBZLRKFJWQZHU-UHFFFAOYSA-N 0.000 description 1

- GYVGXEWAOAAJEU-UHFFFAOYSA-N n,n,4-trimethylaniline Chemical compound CN(C)C1=CC=C(C)C=C1 GYVGXEWAOAAJEU-UHFFFAOYSA-N 0.000 description 1

- ALXIOUGHHXXLKX-UHFFFAOYSA-N n,n-dimethyl-2,6-di(propan-2-yl)aniline Chemical compound CC(C)C1=CC=CC(C(C)C)=C1N(C)C ALXIOUGHHXXLKX-UHFFFAOYSA-N 0.000 description 1

- BZFWSDQZPYVFHP-UHFFFAOYSA-N n,n-dimethyl-4-methylsulfanylaniline Chemical compound CSC1=CC=C(N(C)C)C=C1 BZFWSDQZPYVFHP-UHFFFAOYSA-N 0.000 description 1

- 125000001624 naphthyl group Chemical group 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 230000000269 nucleophilic effect Effects 0.000 description 1

- 229920001778 nylon Polymers 0.000 description 1

- 239000000382 optic material Substances 0.000 description 1

- 238000000879 optical micrograph Methods 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 150000001451 organic peroxides Chemical class 0.000 description 1

- 229920000620 organic polymer Polymers 0.000 description 1

- 125000004430 oxygen atom Chemical group O* 0.000 description 1

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- SLIUAWYAILUBJU-UHFFFAOYSA-N pentacene Chemical compound C1=CC=CC2=CC3=CC4=CC5=CC=CC=C5C=C4C=C3C=C21 SLIUAWYAILUBJU-UHFFFAOYSA-N 0.000 description 1

- WXZMFSXDPGVJKK-UHFFFAOYSA-N pentaerythritol Chemical compound OCC(CO)(CO)CO WXZMFSXDPGVJKK-UHFFFAOYSA-N 0.000 description 1

- 125000002080 perylenyl group Chemical group C1(=CC=C2C=CC=C3C4=CC=CC5=CC=CC(C1=C23)=C45)* 0.000 description 1

- CSHWQDPOILHKBI-UHFFFAOYSA-N peryrene Natural products C1=CC(C2=CC=CC=3C2=C2C=CC=3)=C3C2=CC=CC3=C1 CSHWQDPOILHKBI-UHFFFAOYSA-N 0.000 description 1

- 238000005191 phase separation Methods 0.000 description 1

- 150000003009 phosphonic acids Chemical group 0.000 description 1

- XYFCBTPGUUZFHI-UHFFFAOYSA-O phosphonium Chemical compound [PH4+] XYFCBTPGUUZFHI-UHFFFAOYSA-O 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 230000036211 photosensitivity Effects 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920005593 poly(benzyl methacrylate) Polymers 0.000 description 1

- 229920000435 poly(dimethylsiloxane) Polymers 0.000 description 1

- 229920000636 poly(norbornene) polymer Polymers 0.000 description 1

- 229920001467 poly(styrenesulfonates) Polymers 0.000 description 1

- 229920001281 polyalkylene Polymers 0.000 description 1

- 229920000767 polyaniline Polymers 0.000 description 1

- 229920000412 polyarylene Polymers 0.000 description 1

- 229920002721 polycyanoacrylate Polymers 0.000 description 1

- 229920002776 polycyclohexyl methacrylate Polymers 0.000 description 1

- 229920006267 polyester film Polymers 0.000 description 1

- 229920000570 polyether Polymers 0.000 description 1

- 229920000120 polyethyl acrylate Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920002098 polyfluorene Polymers 0.000 description 1

- 229920001228 polyisocyanate Polymers 0.000 description 1

- 239000005056 polyisocyanate Substances 0.000 description 1

- 229920001470 polyketone Polymers 0.000 description 1

- 229920006380 polyphenylene oxide Polymers 0.000 description 1

- 229920001155 polypropylene Polymers 0.000 description 1

- 229920001296 polysiloxane Polymers 0.000 description 1

- 229920000123 polythiophene Polymers 0.000 description 1

- 229920002635 polyurethane Polymers 0.000 description 1

- 239000004814 polyurethane Substances 0.000 description 1

- 150000004032 porphyrins Chemical class 0.000 description 1

- 125000002924 primary amino group Chemical group [H]N([H])* 0.000 description 1

- 125000001436 propyl group Chemical group [H]C([*])([H])C([H])([H])C([H])([H])[H] 0.000 description 1

- JUJWROOIHBZHMG-UHFFFAOYSA-O pyridinium Chemical compound C1=CC=[NH+]C=C1 JUJWROOIHBZHMG-UHFFFAOYSA-O 0.000 description 1

- 125000001453 quaternary ammonium group Chemical group 0.000 description 1

- 229960000948 quinine Drugs 0.000 description 1

- 239000001008 quinone-imine dye Substances 0.000 description 1

- 150000003254 radicals Chemical group 0.000 description 1

- 229920005604 random copolymer Polymers 0.000 description 1

- 239000001022 rhodamine dye Substances 0.000 description 1

- 239000005060 rubber Substances 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 238000012216 screening Methods 0.000 description 1

- 239000000565 sealant Substances 0.000 description 1

- 229910052711 selenium Inorganic materials 0.000 description 1

- 230000008313 sensitization Effects 0.000 description 1

- 229910000077 silane Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 239000002002 slurry Substances 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 150000003440 styrenes Chemical class 0.000 description 1

- 125000005504 styryl group Chemical group 0.000 description 1

- 125000005017 substituted alkenyl group Chemical group 0.000 description 1

- 125000004426 substituted alkynyl group Chemical group 0.000 description 1

- 125000003107 substituted aryl group Chemical group 0.000 description 1

- 238000006467 substitution reaction Methods 0.000 description 1

- RWSOTUBLDIXVET-UHFFFAOYSA-O sulfonium Chemical compound [SH3+] RWSOTUBLDIXVET-UHFFFAOYSA-O 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000000725 suspension Substances 0.000 description 1

- 229920003051 synthetic elastomer Polymers 0.000 description 1

- 239000005061 synthetic rubber Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- 229910001936 tantalum oxide Inorganic materials 0.000 description 1

- 125000000999 tert-butyl group Chemical group [H]C([H])([H])C(*)(C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- 125000003831 tetrazolyl group Chemical group 0.000 description 1

- 239000001016 thiazine dye Substances 0.000 description 1

- 239000001017 thiazole dye Substances 0.000 description 1

- 125000005323 thioketone group Chemical group 0.000 description 1

- OKYDCMQQLGECPI-UHFFFAOYSA-N thiopyrylium Chemical class C1=CC=[S+]C=C1 OKYDCMQQLGECPI-UHFFFAOYSA-N 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 1

- 125000005424 tosyloxy group Chemical group S(=O)(=O)(C1=CC=C(C)C=C1)O* 0.000 description 1

- VZCYOOQTPOCHFL-UHFFFAOYSA-N trans-butenedioic acid Natural products OC(=O)C=CC(O)=O VZCYOOQTPOCHFL-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- 239000001003 triarylmethane dye Substances 0.000 description 1

- CPRPKIMXLHBUGA-UHFFFAOYSA-N triethyltin Chemical group CC[Sn](CC)CC CPRPKIMXLHBUGA-UHFFFAOYSA-N 0.000 description 1

- 125000004950 trifluoroalkyl group Chemical group 0.000 description 1

- 125000004953 trihalomethyl group Chemical group 0.000 description 1

- 239000013638 trimer Substances 0.000 description 1

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 1

- 125000000026 trimethylsilyl group Chemical group [H]C([H])([H])[Si]([*])(C([H])([H])[H])C([H])([H])[H] 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 238000007738 vacuum evaporation Methods 0.000 description 1

- 238000005406 washing Methods 0.000 description 1

- 238000009941 weaving Methods 0.000 description 1

- 238000004804 winding Methods 0.000 description 1

- 239000001018 xanthene dye Substances 0.000 description 1

- 239000001052 yellow pigment Substances 0.000 description 1

- 229910052984 zinc sulfide Inorganic materials 0.000 description 1

- DRDVZXDWVBGGMH-UHFFFAOYSA-N zinc;sulfide Chemical compound [S-2].[Zn+2] DRDVZXDWVBGGMH-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0231—Manufacture or treatment of multiple TFTs using masks, e.g. half-tone masks

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/0005—Production of optical devices or components in so far as characterised by the lithographic processes or materials used therefor

-

- G—PHYSICS

- G03—PHOTOGRAPHY; CINEMATOGRAPHY; ANALOGOUS TECHNIQUES USING WAVES OTHER THAN OPTICAL WAVES; ELECTROGRAPHY; HOLOGRAPHY

- G03F—PHOTOMECHANICAL PRODUCTION OF TEXTURED OR PATTERNED SURFACES, e.g. FOR PRINTING, FOR PROCESSING OF SEMICONDUCTOR DEVICES; MATERIALS THEREFOR; ORIGINALS THEREFOR; APPARATUS SPECIALLY ADAPTED THEREFOR

- G03F7/00—Photomechanical, e.g. photolithographic, production of textured or patterned surfaces, e.g. printing surfaces; Materials therefor, e.g. comprising photoresists; Apparatus specially adapted therefor

- G03F7/20—Exposure; Apparatus therefor

- G03F7/2022—Multi-step exposure, e.g. hybrid; backside exposure; blanket exposure, e.g. for image reversal; edge exposure, e.g. for edge bead removal; corrective exposure

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

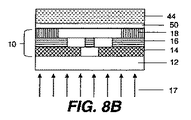

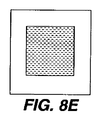

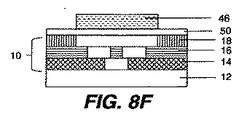

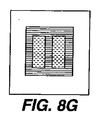

- H10D30/0312—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes

- H10D30/0316—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] characterised by the gate electrodes of lateral bottom-gate TFTs comprising only a single gate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/031—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT]

- H10D30/0321—Manufacture or treatment of FETs having insulated gates [IGFET] of thin-film transistors [TFT] comprising silicon, e.g. amorphous silicon or polysilicon

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/674—Thin-film transistors [TFT] characterised by the active materials

- H10D30/6755—Oxide semiconductors, e.g. zinc oxide, copper aluminium oxide or cadmium stannate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/421—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer

- H10D86/423—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having a particular composition, shape or crystalline structure of the active layer comprising semiconductor materials not belonging to the Group IV, e.g. InGaZnO

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

- H10D86/021—Manufacture or treatment of multiple TFTs

- H10D86/0241—Manufacture or treatment of multiple TFTs using liquid deposition, e.g. printing

Landscapes

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Optical Filters (AREA)

- Thin Film Transistor (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/986,169 US8129098B2 (en) | 2007-11-20 | 2007-11-20 | Colored mask combined with selective area deposition |

| PCT/US2008/012762 WO2009067162A1 (en) | 2007-11-20 | 2008-11-12 | Process using colored mask combined with selective area deposition |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011505589A true JP2011505589A (ja) | 2011-02-24 |

| JP2011505589A5 JP2011505589A5 (enExample) | 2013-01-24 |

Family

ID=40447758

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010534945A Pending JP2011505589A (ja) | 2007-11-20 | 2008-11-12 | 選択的領域堆積と組み合わせて着色マスクを使用する方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8129098B2 (enExample) |

| EP (1) | EP2217969A1 (enExample) |

| JP (1) | JP2011505589A (enExample) |

| CN (1) | CN101868761A (enExample) |

| WO (1) | WO2009067162A1 (enExample) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2020008969A1 (ja) * | 2018-07-05 | 2020-01-09 | 東レ株式会社 | 樹脂組成物、遮光膜、遮光膜の製造方法および隔壁付き基板 |

| JP2021512207A (ja) * | 2018-01-22 | 2021-05-13 | メルク パテント ゲゼルシャフト ミット ベシュレンクテル ハフツングMerck Patent Gesellschaft mit beschraenkter Haftung | 誘電材料 |

| WO2024194943A1 (ja) * | 2023-03-17 | 2024-09-26 | 株式会社レゾナック | 感光性樹脂組成物、感光性エレメント、レジストパターンの形成方法及び配線基板の製造方法 |

| WO2024195410A1 (ja) * | 2023-03-17 | 2024-09-26 | 株式会社レゾナック | 感光性樹脂組成物、感光性エレメント、レジストパターンの形成方法及び配線基板の製造方法 |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8221964B2 (en) * | 2007-11-20 | 2012-07-17 | Eastman Kodak Company | Integrated color mask |

| DE102008054219A1 (de) * | 2008-10-31 | 2010-05-06 | Osram Opto Semiconductors Gmbh | Organisches strahlungsemittierendes Bauelement und Verfahren zur Herstellung eines organischen strahlungsemittierenden Bauelements |

| KR101044279B1 (ko) * | 2009-07-30 | 2011-06-28 | 서강대학교산학협력단 | Cmp 연마패드와 그의 제조방법 |

| TWI449007B (zh) | 2011-09-16 | 2014-08-11 | E Ink Holdings Inc | 可撓性顯示裝置的製造方法 |

| US8927434B2 (en) * | 2012-08-31 | 2015-01-06 | Eastman Kodak Company | Patterned thin film dielectric stack formation |

| US8791023B2 (en) * | 2012-08-31 | 2014-07-29 | Eastman Kodak Company | Patterned thin film dielectric layer formation |

| CN105511227B (zh) * | 2015-12-26 | 2019-08-02 | 杭州福斯特应用材料股份有限公司 | 一种具有良好孔掩蔽功能的干膜抗蚀剂及其层压体 |

| CN106298070B (zh) * | 2016-08-29 | 2017-09-15 | 上海交通大学 | 一种图形化导电薄膜的制备方法 |

| CN108020991A (zh) * | 2016-10-31 | 2018-05-11 | 无锡中微掩模电子有限公司 | 集成电路用掩模版背曝方法 |

| CN108063089B (zh) * | 2016-11-08 | 2020-07-17 | 中国科学院微电子研究所 | 一种mos器件原子层沉积原位制备方法 |

Citations (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5379466A (en) * | 1976-12-23 | 1978-07-13 | Ibm | Method of forming negative mask |

| JPS54114254A (en) * | 1978-01-30 | 1979-09-06 | Eastman Kodak Co | Color filter arraging structure using light fading color |

| JPH01235383A (ja) * | 1988-03-16 | 1989-09-20 | Matsushita Electric Ind Co Ltd | 薄膜電界効果トランジスターの製造方法 |

| JP2002026011A (ja) * | 2000-07-03 | 2002-01-25 | Nec Kagoshima Ltd | パターン形成方法及び薄膜トランジスタの製造方法 |

| JP2002082630A (ja) * | 2000-05-12 | 2002-03-22 | Semiconductor Energy Lab Co Ltd | 電気光学装置 |

| JP2004020743A (ja) * | 2002-06-13 | 2004-01-22 | Dainippon Printing Co Ltd | カラーフィルタの製造方法 |

| JP2009531848A (ja) * | 2006-03-29 | 2009-09-03 | プラスティック ロジック リミテッド | 自己整合電極を有するデバイスの作製方法 |

| JP2009537310A (ja) * | 2006-05-19 | 2009-10-29 | イーストマン コダック カンパニー | 透明構造体を形成するための着色マスキング |

| JP2011503670A (ja) * | 2007-11-20 | 2011-01-27 | イーストマン コダック カンパニー | ディスプレイ回路を製造するための多色マスク方法 |

| JP2011503668A (ja) * | 2007-11-20 | 2011-01-27 | イーストマン コダック カンパニー | 集積化カラーマスク |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4345011A (en) * | 1978-01-30 | 1982-08-17 | Eastman Kodak Company | Color imaging devices and color filter arrays using photo-bleachable dyes |

| FR2595155B1 (fr) | 1986-02-28 | 1988-04-29 | Commissariat Energie Atomique | Procede de realisation de filtres colores en bandes et d'electrodes en bandes auto-alignes pour une cellule d'affichage polychrome a film liquide et cellule correspondante |

| US5262893A (en) * | 1991-11-04 | 1993-11-16 | Massachusetts Institute Of Technology | Method and apparatus for creating multiple phase level optical elements |

| US5391507A (en) * | 1993-09-03 | 1995-02-21 | General Electric Company | Lift-off fabrication method for self-aligned thin film transistors |

| US6338988B1 (en) * | 1999-09-30 | 2002-01-15 | International Business Machines Corporation | Method for fabricating self-aligned thin-film transistors to define a drain and source in a single photolithographic step |

| GB9927287D0 (en) * | 1999-11-19 | 2000-01-12 | Koninkl Philips Electronics Nv | Top gate thin film transistor and method of producing the same |

| CN1265234C (zh) * | 2000-03-10 | 2006-07-19 | 西铁城时计株式会社 | 彩色液晶显示器以及彩色滤波器的制造方法 |

| US6803160B2 (en) * | 2001-12-13 | 2004-10-12 | Dupont Photomasks, Inc. | Multi-tone photomask and method for manufacturing the same |

| US7390597B2 (en) * | 2002-06-13 | 2008-06-24 | Dai Nippon Printing Co., Ltd. | Method for manufacturing color filter |

| US7056834B2 (en) * | 2004-02-10 | 2006-06-06 | Hewlett-Packard Development Company, L.P. | Forming a plurality of thin-film devices using imprint lithography |

| US7259106B2 (en) * | 2004-09-10 | 2007-08-21 | Versatilis Llc | Method of making a microelectronic and/or optoelectronic circuitry sheet |

| US7100510B2 (en) * | 2005-02-09 | 2006-09-05 | Eastman Kodak Company | Method for registering patterns on a web |

| US7160819B2 (en) * | 2005-04-25 | 2007-01-09 | Sharp Laboratories Of America, Inc. | Method to perform selective atomic layer deposition of zinc oxide |

| US20060267136A1 (en) * | 2005-05-24 | 2006-11-30 | International Business Machines Corporation | Integrated circuit (ic) with on-chip programmable fuses |

| US8500985B2 (en) * | 2006-07-21 | 2013-08-06 | Novellus Systems, Inc. | Photoresist-free metal deposition |

-

2007

- 2007-11-20 US US11/986,169 patent/US8129098B2/en not_active Expired - Fee Related

-

2008

- 2008-11-12 WO PCT/US2008/012762 patent/WO2009067162A1/en not_active Ceased

- 2008-11-12 CN CN200880116812A patent/CN101868761A/zh active Pending

- 2008-11-12 EP EP08851673A patent/EP2217969A1/en not_active Withdrawn

- 2008-11-12 JP JP2010534945A patent/JP2011505589A/ja active Pending

Patent Citations (10)