JP2010211179A - 光電気複合配線モジュールおよびその製造方法 - Google Patents

光電気複合配線モジュールおよびその製造方法 Download PDFInfo

- Publication number

- JP2010211179A JP2010211179A JP2009233978A JP2009233978A JP2010211179A JP 2010211179 A JP2010211179 A JP 2010211179A JP 2009233978 A JP2009233978 A JP 2009233978A JP 2009233978 A JP2009233978 A JP 2009233978A JP 2010211179 A JP2010211179 A JP 2010211179A

- Authority

- JP

- Japan

- Prior art keywords

- optical element

- optical

- circuit board

- wiring module

- composite wiring

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/10—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings of the optical waveguide type

- G02B6/12—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings of the optical waveguide type of the integrated circuit kind

-

- G—PHYSICS

- G02—OPTICS

- G02B—OPTICAL ELEMENTS, SYSTEMS OR APPARATUS

- G02B6/00—Light guides; Structural details of arrangements comprising light guides and other optical elements, e.g. couplings

- G02B6/24—Coupling light guides

- G02B6/42—Coupling light guides with opto-electronic elements

- G02B6/4201—Packages, e.g. shape, construction, internal or external details

- G02B6/4204—Packages, e.g. shape, construction, internal or external details the coupling comprising intermediate optical elements, e.g. lenses, holograms

- G02B6/4214—Packages, e.g. shape, construction, internal or external details the coupling comprising intermediate optical elements, e.g. lenses, holograms the intermediate optical element having redirecting reflective means, e.g. mirrors, prisms for deflecting the radiation from horizontal to down- or upward direction toward a device

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/0274—Optical details, e.g. printed circuits comprising integral optical means

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/18—Printed circuits structurally associated with non-printed electric components

- H05K1/182—Printed circuits structurally associated with non-printed electric components associated with components mounted in the printed circuit board, e.g. insert mounted components [IMC]

- H05K1/185—Components encapsulated in the insulating substrate of the printed circuit or incorporated in internal layers of a multilayer circuit

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4602—Manufacturing multilayer circuits characterized by a special circuit board as base or central core whereon additional circuit layers are built or additional circuit boards are laminated

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

- H05K3/4644—Manufacturing multilayer circuits by building the multilayer layer by layer, i.e. build-up multilayer circuits

Abstract

光素子の駆動回路または増幅回路LSIと光素子との電気配線を薄膜配線層により短距離で接続することで、チャネル当たりの伝送速度を高しかつ消費電力の増大を防ぐ。また、伝送装置への接続方式がコネクタ等簡便であり、LSIの実装も従来技術によるものであるため、組立が容易でかつ高信頼が実現できる。すなわち、本発明によれば、性能、量産性ともに優れた光電気複合配線モジュールおよびこれを用いた伝送装置を提供できる。

【解決手段】

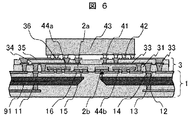

光素子2a、2bを、第一の回路基板1に形成された光導波路11と光結合できるように、第一の回路基板上1に配置し、光素子の上層に電気配線層3を光素子の電極と電気配線層3の配線が電気的に接続されるように積層し、電気配線層3上にLSIを実装して電気的に接続した構造とすることを特徴とする光電気複合配線モジュール。

【選択図】 図1

Description

例えば、特開2006−133763号公報においては、光素子と光伝送路との結合をガイドピンで位置合わせし、ソケットピンを用いて光素子とLSIを実装する構造としている。これにより、比較的容易に光素子と光伝送路の位置合わせが可能となり、またソケットピンで実装することにより、LSIの着脱が容易になっている。

Claims (28)

- 光信号を伝搬する光導波路を有する第一の回路基板と、

前記第一の回路基板上に設けられ、前記光導波路と光結合する光素子と、

前記第一の回路基板及び前記光素子上に設けられた絶縁膜と、

前記絶縁膜上に設けられた配線パッドと、

前記光素子と前記配線パッドを電気的に接続する電気配線と、

前記配線パッド上に設けられて電気的に接続される第一の半導体素子とを備え、

前記光素子は、前記第一の回路基板の前記第一の半導体素子側の面であり、かつ前記第一の半導体素子を前記第一の回路基板に投影した投影面内に設けられていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記光素子は、前記第一の半導体素子と前記光導波路との間に設けられていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記光素子は、当該光素子が接続される前記配線パッドの直下にあることを特徴とする光電気複合配線モジュール。 - 請求項3において、

前記光素子は、当該光素子が接続される前記配線パッドと、当該光素子が光結合する光導波路との間に配置されていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記光素子と前記配線パッドとは、前記絶縁膜内に形成されたビアにより接続されていることを特徴とする光電気複合配線モジュール。 - 請求項5において、

前記光素子は、その前記第一の半導体素子側に、前記ビアに接続される電極を有することを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記光素子は、その前記前記第一の回路基板側に、前記回路基板上の電極と接続された電極を有することを特徴とする光電気複合配線モジュール。 - 請求項1において、

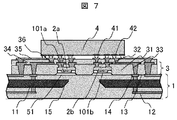

前記光素子を搭載する第二の回路基板を有し、

当該第二の基板は、前記光素子を前記第一の回路基板に向けて搭載されていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

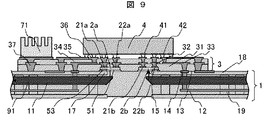

前記第一の回路基板に上に搭載された第二の半導体素子を備え、

当該第二の半導体素子の上に前記絶縁膜が設けられており、

当該第二の半導体素子は、前記光素子と前記第一の半導体素子とに電気的に接続されていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記光素子と前記光導波路との光軸間にレンズが設けられていることを特徴とする光電気複合配線モジュール。 - 請求項1において、

前記第一の回路基板は、その表面に、前記光素子に接続された導体層を有し、

当該導体層は、前記半導体素子の投影面の外まで延在していることを特徴とする光電気複合配線モジュール。 - 請求項11において、

前記第一の回路基板は、前記光素子を搭載した側の表面及びその反対側の表面の両面に前記導体層を有し、

前記両面の導体層は、ビアにより互いに接続されていることを特徴とする光電気複合配線モジュール。 - 請求項11において、

前記絶縁膜上に放熱フィンを有し、

当該放熱フィンと前記導体層は接続されていることを特徴とする光電気複合配線モジュール。 - 請求項1に記載の光電気複合配線モジュールを備え、

前記光導波路は、前記光素子と光結合した側と反対の端部を、光ファイバと光結合し、

光電気複合配線モジュールの有する電気配線が、モジュール外部の電気配線と電気的に接合されていることを特徴とする伝送装置。 - 光導波路を有する第一の回路基板上に、前記光導波路に光結合するように光素子を搭載する工程と、

前記回路基板及び前記光素子上に絶縁膜を形成する工程と、

前記絶縁膜内に、前記光素子に接続される電気配線を形成する工程と、

前記絶縁膜上に、前記電気配線に接続される配線パッドを形成する工程と、

前記配線パッドに半導体素子を接続する工程とを含む光電気複合配線モジュールの製造方法。 - 請求項15において、

前記半導体素子は、前記光素子が搭載された領域の上の領域に搭載されることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項16において、

前記光素子は、前記半導体素子と前記光導波路との間に設けられていることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記配線パッドは、当該配線パッドが接続される前記光素子の直上にあることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項18において、

前記光素子は、当該光素子が接続される前記配線パッドと、当該光素子が光結合する光導波路との間に配置されていることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記光素子と前記配線パッドとは、前記絶縁膜内に形成されたビアにより接続されていることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項20において、

前記光素子は、その前記半導体素子側に、前記ビアに接続される電極を有することを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記光素子は、その前記前記第一の回路基板側に、前記回路基板上の電極と接続される電極を有することを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記光素子は、当該光素子を搭載する第二の回路基板を有しており、

当該光素子は、前記第二の回路基板を前記第一の回路基板とは反対側に向けて搭載されることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記第一の回路基板上に、第二の半導体素子を搭載する工程を含み、

前記絶縁膜は、前記第二の半導体素子上にも形成され、

前記電気配線は、前記第二の半導体素子にも接続されることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記光素子と前記光導波路との光軸間にレンズ設置する工程を含むことを特徴とする光電気複合配線モジュールの製造方法。 - 請求項15において、

前記第一の回路基板は、その表面に導体層を有し、

前記導体層は、前記光素子に接続され、

前記導体層は、前記半導体素子の投影面の外まで延在していることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項26において、

前記第一の回路基板は、前記光素子を搭載する側の表面及びその反対側の表面の両面に前記導体層を有し、

前記両面の導体層は、ビアにより互いに接続されていることを特徴とする光電気複合配線モジュールの製造方法。 - 請求項26において、

前記絶縁膜上の前記導体層に接続されるビアの上に放熱フィンを搭載する工程を有することを特徴とする光電気複合配線モジュールの製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009233978A JP2010211179A (ja) | 2009-02-13 | 2009-10-08 | 光電気複合配線モジュールおよびその製造方法 |

| US12/623,686 US8401347B2 (en) | 2009-02-13 | 2009-11-23 | Photoelectric composite wiring module and method for manufacturing the same |

| CN200910251208.XA CN101900859B (zh) | 2009-02-13 | 2009-12-02 | 光电复合布线模块及其制造方法 |

| KR1020090118963A KR20100092861A (ko) | 2009-02-13 | 2009-12-03 | 광 전기 복합 배선 모듈 및 그 제조 방법 |

| KR1020120053251A KR101238977B1 (ko) | 2009-02-13 | 2012-05-18 | 광 전기 복합 배선 모듈 및 그 제조 방법 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009030637 | 2009-02-13 | ||

| JP2009233978A JP2010211179A (ja) | 2009-02-13 | 2009-10-08 | 光電気複合配線モジュールおよびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010211179A true JP2010211179A (ja) | 2010-09-24 |

| JP2010211179A5 JP2010211179A5 (ja) | 2012-02-09 |

Family

ID=42559962

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009233978A Pending JP2010211179A (ja) | 2009-02-13 | 2009-10-08 | 光電気複合配線モジュールおよびその製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8401347B2 (ja) |

| JP (1) | JP2010211179A (ja) |

| KR (2) | KR20100092861A (ja) |

| CN (1) | CN101900859B (ja) |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014089262A (ja) * | 2012-10-29 | 2014-05-15 | Shinko Electric Ind Co Ltd | 光導波路、光モジュール及び光導波路の製造方法 |

| KR101856230B1 (ko) * | 2011-12-09 | 2018-05-09 | 엘지이노텍 주식회사 | 광 인쇄회로기판 및 그의 제조 방법 |

| KR101856229B1 (ko) * | 2011-12-09 | 2018-05-09 | 엘지이노텍 주식회사 | 광 인쇄회로기판 및 그의 제조 방법 |

| WO2018180785A1 (ja) * | 2017-03-30 | 2018-10-04 | 京セラ株式会社 | 光電気配線基板 |

| WO2019117035A1 (ja) * | 2017-12-12 | 2019-06-20 | 日東電工株式会社 | 光電気混載基板 |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102009001930B4 (de) * | 2009-03-27 | 2018-01-04 | Robert Bosch Gmbh | Sensorbaustein |

| EP2428828B1 (en) * | 2010-09-13 | 2016-06-29 | Tyco Electronics Svenska Holdings AB | Miniaturized high speed optical module |

| CN103370644B (zh) * | 2010-11-25 | 2016-04-20 | Fci公司 | 光学电路板 |

| KR101256000B1 (ko) * | 2011-04-13 | 2013-04-18 | 엘지이노텍 주식회사 | 광 모듈용 인터포저 및 이를 이용한 광모듈, 인터포저의 제조방법 |

| WO2013085225A1 (en) * | 2011-12-08 | 2013-06-13 | Lg Innotek Co., Ltd. | Optical printed circuit board and method of manufacturing the same |

| US9182544B2 (en) * | 2011-12-21 | 2015-11-10 | Intel Corporation | Fabrication of planar light-wave circuits (PLCS) for optical I/O |

| JP6136545B2 (ja) * | 2013-05-07 | 2017-05-31 | 日立金属株式会社 | 光配線基板、光配線基板の製造方法、及び光モジュール |

| CN105493341A (zh) * | 2013-09-02 | 2016-04-13 | 株式会社村田制作所 | 隔离器 |

| JP6287105B2 (ja) * | 2013-11-22 | 2018-03-07 | ソニー株式会社 | 光通信デバイス、受信装置、送信装置及び送受信システム |

| AT14563U1 (de) * | 2014-03-31 | 2016-01-15 | At&S Austria Technologie & Systemtechnik Ag | Verfahren zur Herstellung einer Leiterplatte mit zumindest einer optoelektronischen Komponente |

| WO2015174239A1 (ja) * | 2014-05-13 | 2015-11-19 | ソニー株式会社 | 光電モジュールおよび光素子 |

| CN108627845B (zh) * | 2017-03-15 | 2021-05-28 | 信泰光学(深圳)有限公司 | 雷射驱动电路的电路布局结构 |

| CN109752804B (zh) * | 2017-11-06 | 2020-11-10 | 松下知识产权经营株式会社 | 光模块构造体 |

| WO2021132339A1 (ja) * | 2019-12-27 | 2021-07-01 | 日東電工株式会社 | 光電気混載基板 |

| KR20230082333A (ko) * | 2021-12-01 | 2023-06-08 | 삼성전기주식회사 | 인쇄회로기판 및 인쇄회로기판 패키지 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999017142A1 (fr) * | 1997-10-01 | 1999-04-08 | Hitachi Chemical Company, Ltd. | Processeur optique d'informations |

| JP2004163722A (ja) * | 2002-11-14 | 2004-06-10 | Fujitsu Ltd | 部品内蔵基板 |

| JP2004274155A (ja) * | 2003-03-05 | 2004-09-30 | Canon Inc | 光接続装置、及びこれを含む光電気混載装置 |

| JP2006270037A (ja) * | 2005-02-28 | 2006-10-05 | Sony Corp | ハイブリットモジュール及びその製造方法並びにハイブリット回路装置 |

| JP2007183522A (ja) * | 2005-01-19 | 2007-07-19 | Bridgestone Corp | 光デバイスおよびその製造方法 |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6693736B1 (en) * | 1992-09-10 | 2004-02-17 | Fujitsu Limited | Optical circuit system and components of same |

| JP2004233991A (ja) | 1997-10-01 | 2004-08-19 | Hitachi Chem Co Ltd | 光情報処理装置 |

| JP2001183556A (ja) | 1999-12-27 | 2001-07-06 | Toppan Printing Co Ltd | マルチチップモジュール基板及びマルチチップモジュール |

| JP3750649B2 (ja) * | 2001-12-25 | 2006-03-01 | 住友電気工業株式会社 | 光通信装置 |

| JP3882738B2 (ja) | 2002-10-24 | 2007-02-21 | ソニー株式会社 | 複合チップモジュール及びその製造方法、並びに複合チップユニット及びその製造方法 |

| JP2004177521A (ja) | 2002-11-25 | 2004-06-24 | Fujitsu Ltd | 光電気複合回路基板 |

| JP3897688B2 (ja) * | 2002-12-11 | 2007-03-28 | キヤノン株式会社 | 光電融合配線基板 |

| JP3913175B2 (ja) * | 2003-01-06 | 2007-05-09 | キヤノン株式会社 | 光回路装置における情報伝達方法 |

| JP4845333B2 (ja) | 2003-04-11 | 2011-12-28 | 株式会社リコー | 光電変換素子パッケージ、その作製方法及び光コネクタ |

| US6985645B2 (en) * | 2003-09-24 | 2006-01-10 | International Business Machines Corporation | Apparatus and methods for integrally packaging optoelectronic devices, IC chips and optical transmission lines |

| JPWO2005052666A1 (ja) * | 2003-11-27 | 2008-03-06 | イビデン株式会社 | Icチップ実装用基板、マザーボード用基板、光通信用デバイス、icチップ実装用基板の製造方法、および、マザーボード用基板の製造方法 |

| US7271461B2 (en) * | 2004-02-27 | 2007-09-18 | Banpil Photonics | Stackable optoelectronics chip-to-chip interconnects and method of manufacturing |

| US7092603B2 (en) * | 2004-03-03 | 2006-08-15 | Fujitsu Limited | Optical bridge for chip-to-board interconnection and methods of fabrication |

| JP4626614B2 (ja) | 2004-09-02 | 2011-02-09 | 日本電気株式会社 | 光電気複合モジュール |

| JP2006133763A (ja) | 2004-10-07 | 2006-05-25 | Nec Corp | Lsiパッケージの光電気配線板への実装構造、実装方法、情報処理装置、光インタフェース、光電気配線板 |

| WO2006095676A1 (ja) | 2005-03-07 | 2006-09-14 | Rohm Co., Ltd. | 光通信モジュールおよびその製造方法 |

| JP4533283B2 (ja) * | 2005-08-29 | 2010-09-01 | 新光電気工業株式会社 | 半導体装置の製造方法 |

| TWI309549B (en) * | 2005-08-29 | 2009-05-01 | Via Tech Inc | Printed circuit board with improved thermal dissipating structure and electronic device with the same |

| US7778501B2 (en) * | 2007-04-03 | 2010-08-17 | Hewlett-Packard Development Company, L.P. | Integrated circuits having photonic interconnect layers and methods for fabricating same |

-

2009

- 2009-10-08 JP JP2009233978A patent/JP2010211179A/ja active Pending

- 2009-11-23 US US12/623,686 patent/US8401347B2/en not_active Expired - Fee Related

- 2009-12-02 CN CN200910251208.XA patent/CN101900859B/zh not_active Expired - Fee Related

- 2009-12-03 KR KR1020090118963A patent/KR20100092861A/ko active Search and Examination

-

2012

- 2012-05-18 KR KR1020120053251A patent/KR101238977B1/ko not_active IP Right Cessation

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO1999017142A1 (fr) * | 1997-10-01 | 1999-04-08 | Hitachi Chemical Company, Ltd. | Processeur optique d'informations |

| JP2004163722A (ja) * | 2002-11-14 | 2004-06-10 | Fujitsu Ltd | 部品内蔵基板 |

| JP2004274155A (ja) * | 2003-03-05 | 2004-09-30 | Canon Inc | 光接続装置、及びこれを含む光電気混載装置 |

| JP2007183522A (ja) * | 2005-01-19 | 2007-07-19 | Bridgestone Corp | 光デバイスおよびその製造方法 |

| JP2006270037A (ja) * | 2005-02-28 | 2006-10-05 | Sony Corp | ハイブリットモジュール及びその製造方法並びにハイブリット回路装置 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101856230B1 (ko) * | 2011-12-09 | 2018-05-09 | 엘지이노텍 주식회사 | 광 인쇄회로기판 및 그의 제조 방법 |

| KR101856229B1 (ko) * | 2011-12-09 | 2018-05-09 | 엘지이노텍 주식회사 | 광 인쇄회로기판 및 그의 제조 방법 |

| JP2014089262A (ja) * | 2012-10-29 | 2014-05-15 | Shinko Electric Ind Co Ltd | 光導波路、光モジュール及び光導波路の製造方法 |

| WO2018180785A1 (ja) * | 2017-03-30 | 2018-10-04 | 京セラ株式会社 | 光電気配線基板 |

| WO2019117035A1 (ja) * | 2017-12-12 | 2019-06-20 | 日東電工株式会社 | 光電気混載基板 |

| JP2019105718A (ja) * | 2017-12-12 | 2019-06-27 | 日東電工株式会社 | 光電気混載基板 |

| JP7176842B2 (ja) | 2017-12-12 | 2022-11-22 | 日東電工株式会社 | 光電気混載基板 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8401347B2 (en) | 2013-03-19 |

| CN101900859A (zh) | 2010-12-01 |

| KR20120061788A (ko) | 2012-06-13 |

| CN101900859B (zh) | 2014-11-05 |

| KR20100092861A (ko) | 2010-08-23 |

| US20100209041A1 (en) | 2010-08-19 |

| KR101238977B1 (ko) | 2013-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101238977B1 (ko) | 광 전기 복합 배선 모듈 및 그 제조 방법 | |

| JP5178650B2 (ja) | 光電気複合配線モジュールおよびその製造方法 | |

| JP5439080B2 (ja) | 光i/oアレイモジュール | |

| JP4425936B2 (ja) | 光モジュール | |

| KR100460703B1 (ko) | 일체화된 광송수신 모듈과 광도파로를 구비하는 광백플레인 | |

| JP4859677B2 (ja) | 光電モジュールの製作システムおよび方法 | |

| US9647762B2 (en) | Integrated parallel optical transceiver | |

| TW200536134A (en) | Lsi package provided with interface module, and transmission line header employed in the package | |

| Doany et al. | Terabit/sec-class board-level optical interconnects through polymer waveguides using 24-channel bidirectional transceiver modules | |

| JP2009003253A (ja) | 光電気混載基板と光電気パッケージとの構造体 | |

| JP2011081071A (ja) | 光モジュール | |

| JP2012226342A (ja) | 光モジュール、光モジュールの製造方法、及び、光通信装置 | |

| CN103579376A (zh) | 具有倒装芯片衬底安装的光电子系统 | |

| TW200405036A (en) | Manufacturable optical connection assemblies | |

| JP2008041772A (ja) | 光モジュール | |

| JP4246563B2 (ja) | 光部品支持基板及びその製造方法、光部品付き光部品支持基板及びその製造方法 | |

| WO2012020532A1 (ja) | 光電気複合配線モジュールおよびその製造方法 | |

| JP2012013726A (ja) | 光インターコネクションモジュールおよびそれを用いた光電気混載回路ボード | |

| JPWO2009001822A1 (ja) | 光モジュール | |

| WO2014141458A1 (ja) | 光モジュールおよび伝送装置 | |

| JP2012088634A (ja) | 光導波路デバイス及びその製造方法 | |

| JP5981145B2 (ja) | 回路基板および通信システム | |

| KR101071550B1 (ko) | 광전변환모듈 | |

| WO2014069290A1 (ja) | レンズ間の接続構造、光学機器、光電気複合配線モジュール、および伝送装置 | |

| TW201409103A (zh) | 可使光源準確對位的光電電路板 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111215 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111215 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121120 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130717 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130910 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140128 |