JP2010061701A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010061701A JP2010061701A JP2008223290A JP2008223290A JP2010061701A JP 2010061701 A JP2010061701 A JP 2010061701A JP 2008223290 A JP2008223290 A JP 2008223290A JP 2008223290 A JP2008223290 A JP 2008223290A JP 2010061701 A JP2010061701 A JP 2010061701A

- Authority

- JP

- Japan

- Prior art keywords

- word line

- substrate bias

- array

- margin

- timing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/41—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger

- G11C11/412—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming static cells with positive feedback, i.e. cells not needing refreshing or charge regeneration, e.g. bistable multivibrator or Schmitt trigger using field-effect transistors only

Abstract

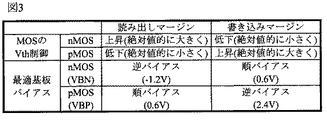

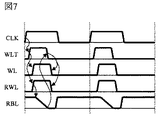

【解決手段】半導体装置は、ワード線の選択期間を決めるためのワード線タイミング信号と基準信号とを比較し、その比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを印加し、逆にその比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを印加する。基準信号は、ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合、プロセス変動(閾値電圧のばらつき)によって変動する動作マージンを補償する場合に応じて選択される。ワード線パルス幅により基板バイアスを制御することで、ワード線パルス幅によって変動する動作マージンを改善し、また、製造時の閾値電圧のばらつきによって変動する動作マージンを改善する。

【選択図】図1

Description

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にpチャンネル型MOSトランジスタに逆方向基板バイアスを印加する。これによって書き込みマージンを改善する。

ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にnチャンネル型MOSトランジスタに順方向基板バイアスを印加する。これによって書き込みマージンを改善する。

ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にnチャンネル型MOSトランジスタに逆方向基板バイアスを印加する。これによって読出しマージンを改善する。

ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にpチャンネル型MOSトランジスタに順方向基板バイアスを印加する。これによって読出しマージンを改善する。

プロセス変動(MOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合(nチャンネル型MOSトランジスタの閾値電圧の絶対値が小さいことに起因して読出しマージンが劣化し、ワード線選択信号の変化も早くなっている場合)にpチャンネル型MOSトランジスタに順方向基板バイアスを印加する。これによって読出しマージンを改善する。

プロセス変動(MOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合(nチャンネル型MOSトランジスタの閾値電圧の絶対値が小さいことに起因して読出しマージンが劣化し、ワード線選択信号の変化も早くなっている場合)にnチャンネル型MOSトランジスタに逆方向基板バイアスを印加する。これによって読出しマージンを改善する。

プロセス変動(MOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合(nチャンネル型MOSトランジスタの閾値電圧の絶対値が大きいことに起因して、書き込みマージンが劣化し、ワード線選択信号の変化も遅くなっている場合)にnチャンネル型MOSトランジスタに順方向基板バイアスを印加する。これによって書き込みマージンを改善する。

プロセス変動(MOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合には、その観点による基準信号がワード線タイミング信号と比較される。項3の半導体装置において、前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合(nチャンネル型MOSトランジスタの閾値電圧の絶対値が大きいことに起因して、書き込みマージンが劣化し、ワード線選択信号の変化も遅くなっている場合)にpチャンネル型MOSトランジスタに逆方向基板バイアスを印加する。これによって書き込みマージンを改善する。

実施の形態について更に詳述する。以下、本発明を実施するための形態を図面に基づいて詳細に説明する。なお、発明を実施するための形態を説明するための全図において、同一の機能を有する要素には同一の符号を付して、その繰り返しの説明を省略する。

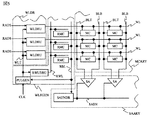

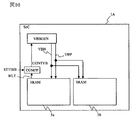

図1には本発明に係る半導体装置の一例が示される。同図に示される半導体装置1はシステムオンチップ(SoC)の所謂システムLSIとして構成される。半導体装置1は、特に制限されないが、単結晶シリコンのような1個の半導体基板にCMOS集積回路製造技術などによって構成される。

上記ではワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合について説明した。以下においては、プロセス変動(MOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合について説明する。ここではプロセス変動によるMOSトランジスタの閾値電圧のばらつきをワード線タイミング信号WLTのワード線パルス幅で検出する場合を一例とする。前述のように、ワード線パルス幅は図6で説明したレプリカセルRMCのnMOSトランジスタN1,N3を介するディスチャージ速度に依存するから、特にnMOSトランジスタの閾値電圧のばらつきに着目する。この場合の半導体装置の回路構成は、図1に代表される上述の構成に比べて、信号CONTVBに基づいて基板バイアス電圧VBN,VBPを発生させる基板バイアス発生回路VBBGENの制御論理が相違され、その他の構成は同一であってよい。よってこの観点による半導体装置の構成については単独で図示することを省略してある。STTIMEに代表される基準信号は、第1の観点によるワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合と、第2の観点によるプロセス変動(nMOSトランジスタの閾値電圧のばらつき)によって変動する動作マージンを補償する場合とでは相違されることになる。

2 CPU

3,3a、3b、3c、3d SRAM部

WL…ワード線

BLT、BLB…ビット線

VBN…nMOSトランジスタの基板端子

VBP…pMOSトランジスタの基板端子

Vdd…電源電圧

Vss…グランド電圧

MCELL…メモリセル

MARRAY…メモリセルアレイ

WLTGEN、WLTGEN1、WLTGEN2…ワード線のタイミングを生成回路

WLT…ワード線タイミング信号

STTIME、STTIME2…基準信号

COMPP、COMPP1、COMPP2…タイミング比較回路

CLK…クロック信号

VBBGEN…基板バイアス発生回路

CONTVB、CONTVB1、CONTVB2…基板バイアス制御信号

WLDR…ワード線ドライバ

MC…メモリセル

SA…センスアンプ

SAEN…センスアンプ活性化信号

SAENDR…センスアンプ駆動回路

PULGEN…パルス生成回路

RWL…レプリカワード線

RBL…レプリカビット線

RC…レプリカセル

RWLDR…レプリカワード線駆動回路

DELAY…遅延回路

Claims (16)

- 選択端子がワード線に接続されデータ端子がビット線に接続された複数のメモリセルのアレイと、

ワード線の選択期間を決めるためのワード線タイミング信号を生成するワード線タイミング生成回路と、

前記ワード線タイミング信号と基準信号を比較する比較回路と、

前記比較回路による比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを印加し、逆にその比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを印加する基板バイアス制御回路と、を有する半導体装置。 - 前記メモリセルは相互に一方の入力を他方の出力に結合した一対のCMOSインバータを有するスタティック型メモリセルである、請求項1記載の半導体装置。

- 前記ワード線タイミング生成回路は、前記メモリセルと読出し動作の電気的特性が等価なレプリカセルを有し、ワード線の選択に呼応して選択された前記レプリカセルのローレベル出力が確定するタイミングで前記ワード線タイミング信号を変化させる、請求項2記載の半導体装置。

- ワード線タイミング生成回路は、前記メモリセルのアレイにおけるワード線本数に依存してワード線タイミング信号の変化タイミングを決定する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にpチャンネル型MOSトランジスタに逆方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にnチャンネル型MOSトランジスタに順方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にnチャンネル型MOSトランジスタに逆方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にpチャンネル型MOSトランジスタに順方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にpチャンネル型MOSトランジスタに順方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも短い場合にnチャンネル型MOSトランジスタに逆方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にnチャンネル型MOSトランジスタに順方向基板バイアスを印加する、請求項3記載の半導体装置。

- 前記基板バイアス制御回路は、ワード線選択タイミングから前記ワード線タイミング信号の変化までの期間が基準信号よりも長い場合にpチャンネル型MOSトランジスタに逆方向基板バイアスを印加する、請求項3記載の半導体装置。

- 選択端子がワード線に接続されデータ端子がビット線に接続された複数のメモリセルの第1アレイと、

前記第1アレイにおけるワード線の選択期間を決めるための第1ワード線タイミング信号を生成する第1ワード線タイミング生成回路と、

前記第1ワード線タイミング信号と基準信号を比較する第1比較回路と、

前記第1比較回路による比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを前記第1アレイに印加し、前記比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを前記第1アレイに印加する第1基板バイアス制御回路と、

選択端子がワード線に接続されデータ端子がビット線に接続された複数のメモリセルの第2アレイと、

前記第2アレイにおけるワード線の選択期間を決めるための第2ワード線タイミング信号を生成する第2ワード線タイミング生成回路と、

前記第2ワード線タイミング信号と基準信号を比較する第2比較回路と、

前記第2比較回路による比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを前記第2アレイに印加し、前記比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを前記第2アレイに印加する第2基板バイアス制御回路と、を有する半導体装置。 - 前記第1アレイと第2アレイのワード線本数が相違される、請求項13記載の半導体装置。

- 選択端子がワード線に接続されデータ端子がビット線に接続された複数のメモリセルの第1アレイと、

前記第1アレイにおけるワード線の選択期間を決めるための第1ワード線タイミング信号を生成する第1ワード線タイミング生成回路と、

選択端子がワード線に接続されデータ端子がビット線に接続された複数のメモリセルの第2アレイと、

前記第2アレイにおけるワード線の選択期間を決めるための第2ワード線タイミング信号を生成する第2ワード線タイミング生成回路と、

前記第2ワード線タイミング信号と基準信号を比較する比較回路と、

前記第2比較回路による比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを前記第1アレイ及び第2アレイに印加し、前記比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを前記第1アレイ及び第2アレイに印加する基板バイアス制御回路と、を有する半導体装置。 - 前記第1アレイと第2アレイのワード線本数が等しくされる、請求項15記載の半導体装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008223290A JP5197241B2 (ja) | 2008-09-01 | 2008-09-01 | 半導体装置 |

| US12/543,499 US8125837B2 (en) | 2008-09-01 | 2009-08-18 | Semiconductor memory device with read/write margin control using back-gate bias |

| CN2009101682933A CN101667452B (zh) | 2008-09-01 | 2009-08-24 | 半导体器件 |

| US13/353,949 US8270230B2 (en) | 2008-09-01 | 2012-01-19 | Semiconductor device |

| US13/587,900 US8493775B2 (en) | 2008-09-01 | 2012-08-16 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008223290A JP5197241B2 (ja) | 2008-09-01 | 2008-09-01 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010061701A true JP2010061701A (ja) | 2010-03-18 |

| JP5197241B2 JP5197241B2 (ja) | 2013-05-15 |

Family

ID=41725262

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008223290A Active JP5197241B2 (ja) | 2008-09-01 | 2008-09-01 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US8125837B2 (ja) |

| JP (1) | JP5197241B2 (ja) |

| CN (1) | CN101667452B (ja) |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102237129A (zh) * | 2010-04-29 | 2011-11-09 | 台湾积体电路制造股份有限公司 | 内存装置与静态随机存取内存装置 |

| JP2013054795A (ja) * | 2011-09-02 | 2013-03-21 | Fujitsu Semiconductor Ltd | メモリ装置 |

| JP2013069372A (ja) * | 2011-09-22 | 2013-04-18 | Renesas Electronics Corp | 半導体装置 |

| KR20140063800A (ko) * | 2011-09-12 | 2014-05-27 | 퀄컴 인코포레이티드 | 다중-포트 sram에 대한 적응형 판독 워드라인 전압 부스팅 장치 및 방법 |

| JP2014220020A (ja) * | 2013-04-30 | 2014-11-20 | 富士通株式会社 | 電子回路 |

| JP2020155196A (ja) * | 2019-03-14 | 2020-09-24 | 株式会社東芝 | 半導体記憶装置 |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8618870B2 (en) * | 2009-06-12 | 2013-12-31 | Semiconductor Technology Academic Research Center | Voltage characteristic regulating method of latch circuit, voltage characteristic regulating method of semiconductor device, and voltage characteristic regulator of latch circuit |

| US8362807B2 (en) * | 2010-10-13 | 2013-01-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Offset compensation for sense amplifiers |

| US10629250B2 (en) * | 2010-11-16 | 2020-04-21 | Texas Instruments Incorporated | SRAM cell having an n-well bias |

| US8385140B2 (en) * | 2010-11-18 | 2013-02-26 | Advanced Micro Devices, Inc. | Memory elements having shared selection signals |

| US8611132B2 (en) | 2011-04-29 | 2013-12-17 | Qualcomm Incorporated | Self-body biasing sensing circuit for resistance-based memories |

| US8755218B2 (en) | 2011-05-31 | 2014-06-17 | Altera Corporation | Multiport memory element circuitry |

| US8467233B2 (en) * | 2011-06-06 | 2013-06-18 | Texas Instruments Incorporated | Asymmetric static random access memory cell with dual stress liner |

| US8406067B2 (en) * | 2011-07-21 | 2013-03-26 | Elite Semiconductor Memory Technology Inc. | Semiconductor memory device |

| US9012963B2 (en) * | 2011-08-22 | 2015-04-21 | Institute of Microelectronics, Chinese Academy of Sciences | Semiconductor device |

| US8705268B2 (en) * | 2011-12-27 | 2014-04-22 | Broadcom Corporation | Quantifying the read and write margins of memory bit cells |

| CN102723110B (zh) * | 2012-07-12 | 2015-06-24 | 苏州兆芯半导体科技有限公司 | 一种写余量控制电路 |

| US9583178B2 (en) | 2012-08-03 | 2017-02-28 | Qualcomm Incorporated | SRAM read preferred bit cell with write assist circuit |

| US9443574B2 (en) * | 2012-10-31 | 2016-09-13 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory architecture |

| US9076557B2 (en) * | 2012-11-19 | 2015-07-07 | Texas Instruments Incorporated | Read margin measurement in a read-only memory |

| KR102168115B1 (ko) | 2014-01-21 | 2020-10-20 | 에스케이하이닉스 주식회사 | 메모리 및 이를 포함하는 메모리 시스템 |

| JP6660773B2 (ja) * | 2016-03-04 | 2020-03-11 | ルネサスエレクトロニクス株式会社 | 半導体装置、光源制御装置および光源制御システム |

| US9799393B1 (en) * | 2016-05-31 | 2017-10-24 | Globalfoundries Inc. | Methods, apparatus and system for providing NMOS-only memory cells |

| US9762245B1 (en) * | 2016-06-14 | 2017-09-12 | Globalfoundries Inc. | Semiconductor structure with back-gate switching |

| JP6538629B2 (ja) | 2016-09-06 | 2019-07-03 | 株式会社東芝 | 半導体記憶装置 |

| US10276223B2 (en) * | 2017-04-24 | 2019-04-30 | Taiwan Semiconductor Manufacturing Company Limited | Memory device for generating word line signals having varying pulse widths |

| JP7086795B2 (ja) * | 2018-09-03 | 2022-06-20 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR102520496B1 (ko) * | 2019-01-03 | 2023-04-11 | 삼성전자주식회사 | 오티피 메모리 장치 및 오피 메모리 장치의 테스트 방법 |

| KR20210081049A (ko) * | 2019-12-23 | 2021-07-01 | 에스케이하이닉스 주식회사 | 저항성 메모리 장치 및 그의 동작 방법 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05504648A (ja) * | 1990-08-28 | 1993-07-15 | アナログ・ディバイセス・インコーポレーテッド | ランダム・アクセス・メモリー用センス可能化タイミング回路 |

| JP2005085349A (ja) * | 2003-09-08 | 2005-03-31 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| JP2007035171A (ja) * | 2005-07-27 | 2007-02-08 | Fujitsu Ltd | 半導体記憶装置およびその試験方法 |

| JP2007179593A (ja) * | 2005-12-26 | 2007-07-12 | Toshiba Corp | 半導体記憶装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004103089A (ja) * | 2002-09-06 | 2004-04-02 | Sharp Corp | 不揮発性半導体記憶装置およびその再書き込み方法 |

| JP4388274B2 (ja) * | 2002-12-24 | 2009-12-24 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| JP2004213722A (ja) * | 2002-12-27 | 2004-07-29 | Matsushita Electric Ind Co Ltd | 半導体記憶装置及び半導体集積回路装置 |

| JP4553185B2 (ja) * | 2004-09-15 | 2010-09-29 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| KR100672984B1 (ko) * | 2004-12-14 | 2007-01-24 | 삼성전자주식회사 | 프로그램 시간을 줄일 수 있는 플래시 메모리 장치 |

| US7826253B2 (en) * | 2005-02-03 | 2010-11-02 | Nec Corporation | Semiconductor memory device and driving method thereof |

| CN101689399A (zh) * | 2007-06-29 | 2010-03-31 | Nxp股份有限公司 | 静态存储器件 |

-

2008

- 2008-09-01 JP JP2008223290A patent/JP5197241B2/ja active Active

-

2009

- 2009-08-18 US US12/543,499 patent/US8125837B2/en active Active

- 2009-08-24 CN CN2009101682933A patent/CN101667452B/zh active Active

-

2012

- 2012-01-19 US US13/353,949 patent/US8270230B2/en active Active

- 2012-08-16 US US13/587,900 patent/US8493775B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05504648A (ja) * | 1990-08-28 | 1993-07-15 | アナログ・ディバイセス・インコーポレーテッド | ランダム・アクセス・メモリー用センス可能化タイミング回路 |

| JP2005085349A (ja) * | 2003-09-08 | 2005-03-31 | Matsushita Electric Ind Co Ltd | 半導体記憶装置 |

| JP2007035171A (ja) * | 2005-07-27 | 2007-02-08 | Fujitsu Ltd | 半導体記憶装置およびその試験方法 |

| JP2007179593A (ja) * | 2005-12-26 | 2007-07-12 | Toshiba Corp | 半導体記憶装置 |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102237129A (zh) * | 2010-04-29 | 2011-11-09 | 台湾积体电路制造股份有限公司 | 内存装置与静态随机存取内存装置 |

| JP2013054795A (ja) * | 2011-09-02 | 2013-03-21 | Fujitsu Semiconductor Ltd | メモリ装置 |

| KR20140063800A (ko) * | 2011-09-12 | 2014-05-27 | 퀄컴 인코포레이티드 | 다중-포트 sram에 대한 적응형 판독 워드라인 전압 부스팅 장치 및 방법 |

| JP2014526767A (ja) * | 2011-09-12 | 2014-10-06 | クアルコム,インコーポレイテッド | マルチポートsramのための適応型読取りワード線電圧ブースティング装置および方法 |

| KR101585551B1 (ko) | 2011-09-12 | 2016-01-22 | 퀄컴 인코포레이티드 | 다중-포트 sram에 대한 적응형 판독 워드라인 전압 부스팅 장치 및 방법 |

| JP2013069372A (ja) * | 2011-09-22 | 2013-04-18 | Renesas Electronics Corp | 半導体装置 |

| JP2014220020A (ja) * | 2013-04-30 | 2014-11-20 | 富士通株式会社 | 電子回路 |

| JP2020155196A (ja) * | 2019-03-14 | 2020-09-24 | 株式会社東芝 | 半導体記憶装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20120307572A1 (en) | 2012-12-06 |

| US20120120738A1 (en) | 2012-05-17 |

| JP5197241B2 (ja) | 2013-05-15 |

| CN101667452B (zh) | 2012-10-31 |

| US8125837B2 (en) | 2012-02-28 |

| US8493775B2 (en) | 2013-07-23 |

| CN101667452A (zh) | 2010-03-10 |

| US8270230B2 (en) | 2012-09-18 |

| US20100054049A1 (en) | 2010-03-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5197241B2 (ja) | 半導体装置 | |

| US6853593B1 (en) | Semiconductor memory device having over-driving scheme | |

| US7512030B2 (en) | Memory with low power mode for WRITE | |

| JP4768437B2 (ja) | 半導体記憶装置 | |

| US7830727B2 (en) | Apparatus and method for low power, single-ended sensing in a multi-port SRAM using pre-discharged bit lines | |

| US7940581B2 (en) | Method for low power sensing in a multi-port SRAM using pre-discharged bit lines | |

| JP4907117B2 (ja) | 半導体装置 | |

| JP2010009674A (ja) | 半導体装置 | |

| US20050162969A1 (en) | Semiconductor integrated circuit device | |

| JP2006120301A (ja) | 半導体メモリ素子の漏洩電流制御装置 | |

| US7170805B2 (en) | Memory devices having bit line precharge circuits with off current precharge control and associated bit line precharge methods | |

| JP2008027493A (ja) | 半導体記憶装置 | |

| JP2005085454A (ja) | メモリアレイを含む集積回路装置、およびセンスアンプを有するメモリを組込んだ集積回路装置においてパワーゲートするための方法 | |

| JP2009134840A (ja) | 半導体記憶装置 | |

| JP2009020957A (ja) | 半導体記憶装置 | |

| US6704238B2 (en) | Semiconductor memory device including data bus pairs respectively dedicated to data writing and data reading | |

| US7489581B2 (en) | Semiconductor memory | |

| US20130135948A1 (en) | Semiconductor storage device | |

| US7675804B2 (en) | Semiconductor integrated circuit device and semiconductor device including plurality of semiconductor circuits | |

| JP2008198243A (ja) | 半導体記憶装置 | |

| US7684231B2 (en) | Methods and apparatus for low power SRAM based on stored data | |

| JPH1021688A (ja) | 半導体記憶装置 | |

| US7596040B2 (en) | Methods and apparatus for improved write characteristics in a low voltage SRAM | |

| US8400856B2 (en) | Memory device with data prediction based access time acceleration | |

| KR20060097055A (ko) | 셀프 타이밍 회로를 갖는 반도체 메모리 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110812 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130124 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130205 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5197241 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |