JP2010054463A - 半導体検査装置及びその製造方法 - Google Patents

半導体検査装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010054463A JP2010054463A JP2008222285A JP2008222285A JP2010054463A JP 2010054463 A JP2010054463 A JP 2010054463A JP 2008222285 A JP2008222285 A JP 2008222285A JP 2008222285 A JP2008222285 A JP 2008222285A JP 2010054463 A JP2010054463 A JP 2010054463A

- Authority

- JP

- Japan

- Prior art keywords

- inspection apparatus

- semiconductor inspection

- substrate

- probe needle

- hole

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/4824—Connecting between the body and an opposite side of the item with respect to the body

Abstract

【課題】 本発明は、X−X方向及びY−Y方向に多ピン化及び狭ピッチ化することが可能なプローブ構造を有する半導体検査装置及びその製造方法を提供することを目的とする。

【解決手段】

基板の一方の面から他方の面に貫通する貫通孔を形成する貫通孔形成工程と、前記基板の前記一方の面にランドを形成するランド形成工程と、前記貫通孔に前記貫通孔の壁面と接触しないようにボンディングワイヤを挿入し、前記ボンディングワイヤの先端部を前記他方の面から突出させるボンディングワイヤ挿入工程と、前記ボンディングワイヤの前記貫通孔に挿入されていない部分を前記ランドにワイヤボンディングし、プローブ針を形成するプローブ針形成工程と、を有する半導体検査装置の製造方法である。

【選択図】 図3

【解決手段】

基板の一方の面から他方の面に貫通する貫通孔を形成する貫通孔形成工程と、前記基板の前記一方の面にランドを形成するランド形成工程と、前記貫通孔に前記貫通孔の壁面と接触しないようにボンディングワイヤを挿入し、前記ボンディングワイヤの先端部を前記他方の面から突出させるボンディングワイヤ挿入工程と、前記ボンディングワイヤの前記貫通孔に挿入されていない部分を前記ランドにワイヤボンディングし、プローブ針を形成するプローブ針形成工程と、を有する半導体検査装置の製造方法である。

【選択図】 図3

Description

本発明は、半導体チップの電極パッドに複数のプローブ針を接触させて、半導体チップの電気的特性を検査する半導体検査装置及びその製造方法に関する。

従来から、半導体チップの検査工程においては、半導体ウェハに形成されている半導体チップの電極パッドに半導体検査装置のプローブ針の先端を直接押し当て、外部の試験装置と半導体チップとを一時的に電気的に接続することにより、各回路間の導通の良否を判別するプロービング検査、高温中において熱的、電気的ストレスを回路に付与して不良を加速選別するバーンイン検査、及び、最終的に高周波で検査を行う最終検査等の電気的特性の検査が行われていた。

近年、半導体チップにおいては、素子の高集積化および処理信号数の増加によって、半導体チップに形成される電極パッドの数が増加(多ピン化)するとともに、電極パッドの狭ピッチ化が進んでいる。これにともない半導体チップの電気的特性の検査を行なう半導体検査装置のプローブ針においても多ピン化及び狭ピッチ化が必要となりつつある。

図1は、従来の半導体検査装置100を例示する断面図である。図1を参照するに、半導体検査装置100は、支持基板101と、中継基板102と、接続端子103と、プローブ104とを有する。108は半導体装置、109は電極パッドである。図2は、従来の半導体検査装置100を構成するプローブ104を例示する斜視図である。同図中、図1と同一部品については、同一符号を付し、その説明は省略する場合がある。

図1及び図2を参照するに、半導体検査装置100において、支持基板101の下面には中継基板102が設けられている。支持基板101及び中継基板102には所定の配線(図示せず)が形成されており、中継基板102の配線(図示せず)とプローブ104の電極パッド104gとは、はんだボールからなる接続端子103を介して電気的に接続されている。支持基板101の配線(図示せず)は、ケーブル等(図示せず)により、外部の試験装置(図示せず)と電気的に接続されている。

プローブ104は、プローブ形成基板104aと、グランド層104bと、絶縁層104cと、配線104dとを有する。104eはプローブ104の突起部、104fはプローブ104の片持ち梁部を示している。プローブ104において、グランド層104b、絶縁層104c、配線104dは、プローブ形成基板104a上に順次積層されている。プローブ形成基板104aは、シリコンからなる。

プローブ104には、変形が容易な片持ち梁部104fが形成され、片持ち梁部104fの先端部又はその近傍には、突起部104eが形成されている。プローブ形成基板104aには、グランド層104b及び絶縁層104cを介して配線104dが、突起部104eから片持ち梁部104fの先端部に沿って、突起部104eが形成されている面の反対側の面に形成されている電極パッド104gまで連続的に形成されている。

電極パッド104gは、接続端子103と接続可能な位置に形成されており、電極パッド104gと接続端子103とは電気的に接続されている。半導体検査装置100は、Z−Z方向に移動可能な機構(図示せず)を有する。半導体装置108の電気的特性の検査時に、半導体検査装置100は、Z−Z方向に半導体装置108側に移動し、半導体検査装置100の突起部104eの部分の配線104dは、被測定物である半導体装置108の電極パッド109と電気的に接続される。

又、この際、片持ち梁部104fがたわむことによりバネ性が生じ、突起部104eの部分の配線104dを適切な圧力で、電極パッド109に押し当てることができ、安定的な電気的接続が実現される。片持ち梁部104fのたわみ量は、例えば、10μm程度である。

半導体検査装置100において、プローブ104はX−X方向に4個設けられている。又、プローブ104において、先端部104e、片持ち梁部104fはY−Y方向に4組設けられている。従って、先端部104eは、被測定物である半導体装置108の16個の電極パッド109と同時に電気的に接続可能である。

なお、半導体検査装置100において、プローブ104をX−X方向に5個以上設けることや、プローブ104において、先端部104e、片持ち梁部104fをY−Y方向に5組以上設けることにより、電極パッド109と同時に電気的に接続可能な先端部104eの数を増やすこともできる(例えば、特許文献1参照)。

特表平11−514493号公報

特開2001−91543号公報

特開2003−98190号公報

しかしながら、従来の半導体検査装置100では、プローブ104の突起部104eを、図2におけるY−Y方向に多ピン化及び狭ピッチ化することは容易であるが、片持ち梁部104fのたわみによるバネ性で生じる圧力により、突起部104eの部分の配線104dと電極パッド109とを電気的に接続する構造を有するため、片持ち梁部104fには所定以上の長さが必要であり、プローブ104の突起部104eを、図1におけるX−X方向に多ピン化及び狭ピッチ化することは困難であるという問題があった。

本発明は、上記に鑑みてなされたもので、X−X方向及びY−Y方向に多ピン化及び狭ピッチ化することが可能なプローブ構造を有する半導体検査装置及びその製造方法を提供することを目的とする。

上記目的を達成するため、第1の発明は、基板の一方の面から他方の面に貫通する貫通孔を形成する貫通孔形成工程と、前記基板の前記一方の面にランドを形成するランド形成工程と、前記貫通孔に前記貫通孔の壁面と接触しないようにボンディングワイヤを挿入し、前記ボンディングワイヤの先端部を前記他方の面から突出させるボンディングワイヤ挿入工程と、前記ボンディングワイヤの前記貫通孔に挿入されていない部分を前記ランドにワイヤボンディングし、プローブ針を形成するプローブ針形成工程と、を有する半導体検査装置の製造方法である。

第2の発明は、基板と、前記基板の一方の面に形成されたランドと、前記基板の一方の面から他方の面に貫通する貫通孔と、一方の端部が前記ランドに固定され、他方の端部が前記貫通孔の壁面と接触しないように前記貫通孔に挿入され前記他方の面から突出するプローブ針と、を有し、電極パッドを有する半導体チップの電気的検査を行う際に、前記プローブ針の前記他方の端部が前記電極パッドと接触することを特徴とする半導体検査装置である。

本発明によれば、X−X方向及びY−Y方向に多ピン化及び狭ピッチ化することが可能なプローブ構造を有する半導体検査装置及びその製造方法を提供することができる。

次に、図面に基づいて本発明の実施の形態について説明する。

〈第1の実施の形態〉

[本発明の第1の実施の形態に係る半導体検査装置の構造]

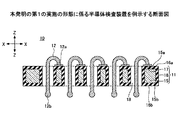

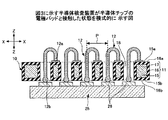

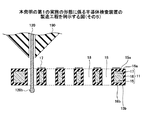

始めに本発明の第1の実施の形態に係る半導体検査装置の構造について説明する。図3は、本発明の第1の実施の形態に係る半導体検査装置を例示する断面図である。図4は、図3に示す半導体検査装置が半導体チップの電極パッドと接触した状態を模式的に示す図である。又、図5は、図3に示すプローブ針を平面視した図である。図3及び図4において、X−X方向は、基板本体15の上面15aと平行な方向を、Z−Z方向は、紙面内におけるX−X方向に垂直な方向をそれぞれ示している。又、X−X方向及びZ−Z方向と直交する方向(紙面に垂直な方向)をY−Y方向とする。図4及び図5において、図3に示す半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

[本発明の第1の実施の形態に係る半導体検査装置の構造]

始めに本発明の第1の実施の形態に係る半導体検査装置の構造について説明する。図3は、本発明の第1の実施の形態に係る半導体検査装置を例示する断面図である。図4は、図3に示す半導体検査装置が半導体チップの電極パッドと接触した状態を模式的に示す図である。又、図5は、図3に示すプローブ針を平面視した図である。図3及び図4において、X−X方向は、基板本体15の上面15aと平行な方向を、Z−Z方向は、紙面内におけるX−X方向に垂直な方向をそれぞれ示している。又、X−X方向及びZ−Z方向と直交する方向(紙面に垂直な方向)をY−Y方向とする。図4及び図5において、図3に示す半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

図3〜図5を参照するに、第1の実施の形態に係る半導体検査装置10は、基板11と、プローブ針12とを有する。基板11は、基板本体15と、絶縁膜16と、ランド17とを有する。基板本体15は板状とされており、複数の貫通孔18を有する。貫通孔18は、プローブ針12をZ−Z方向に移動可能に収容するための孔である。貫通孔18の直径は、例えば、50μmとすることができる。貫通孔18のピッチは、例えば、100μmとすることができる。

基板本体15の材料としては、シリコン、樹脂(例えば、絶縁樹脂)、セラミックス、金属(例えば、Cu)等を用いることができる。なお、基板本体15の材料として絶縁樹脂を用いた場合、図3〜図5に示す絶縁膜16は不要となる。又、半導体チップ25に設けられた半導体基板(図示せず)がシリコン基板の場合、基板本体15の材料としては、例えばシリコンを用いるとよい。

このように、基板本体15の材料としてシリコンを用いることにより、半導体検査装置10と半導体チップ25との間の熱膨張係数の差が緩和されるため、半導体チップ25に設けられた電極パッド26にプローブ針12を精度良く接触させることができる。基板本体15の材料としてシリコンを用いた場合、基板本体15の厚さは、例えば300μmとすることができる。

絶縁膜16は、基板本体15の表面(貫通孔18の側面に対応する部分の基板本体15の面も含む)を覆うように設けられている。絶縁膜16は、基板本体15とプローブ針12との間を絶縁するための膜である。絶縁膜16としては、例えば、酸化膜(例えば、熱酸化膜)を用いることができる。絶縁膜16として、熱酸化膜を用いた場合、絶縁膜16の厚さは、例えば0.5μm〜1.0μmとすることができる。

プローブ針12は、基板本体15及び絶縁膜16と接触しないように、貫通孔18に配置されている。プローブ針12の端部12a(一方の端部)は、基板11を構成するランド17にワイヤボンディングされている。プローブ針12の端部12b(他方の端部)は、基板本体15の下面15bに設けられた絶縁膜16の面16b(基板11の他方の面)よりも突出している。

プローブ針12の端部12bは、半導体検査装置10が半導体チップ25の電気的検査を行う際、半導体チップ25の電極パッド26と接触する部分である。プローブ針12の端部12bの形状は、例えばレーザ光を照射されて溶融し、ボール状となっている。プローブ針12のXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば25μmとすることができる。プローブ針12の端部12bのXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば40μmとすることができる。

プローブ針12は、導電性を有するボンディングワイヤにより構成されている。プローブ針12を係る形状にすることで、プローブ針12はバネ性を有し、プローブ針12の端部12bをZ−Z方向に移動可能な状態で支持することができる。図4に示すように、プローブ針12の端部12bが電極パッド26と接触すると、プローブ針12の端部12bと電極パッド26とが一定の力で接触した状態で、プローブ針12の端部12bは上方に移動する。

プローブ針12を構成するボンディングワイヤの材料としては、例えばAuを用いることができるが、これに限られるものではなく、例えばAuを含む合金、Al、Alを含む合金、Cu、Cuを含む合金等他の材料を用いても構わない。

このように、バネ性を有するプローブ針12を、基板本体15及び絶縁膜16と接触しないように貫通孔18に配置し、端部12bが基板11の下面(具体的には、絶縁膜16の面16b)から突出するように半導体検査装置10に設けることにより、プローブ針12の配設ピッチPを狭くすることが可能となるため、半導体チップ25に設けられた電極パッド26が狭ピッチで配置された場合や電極パッド26がマトリックス配置された場合でも電極パッド26にプローブ針12の端部12bを精度良く接触させることができる。プローブ針12の配設ピッチPは、例えば80μm〜100μmの範囲で適宜選択することが可能である。

[本発明の第1の実施の形態に係る半導体検査装置の製造方法]

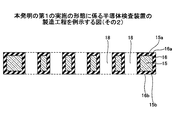

続いて本発明の第1の実施の形態に係る半導体検査装置の製造方法について説明する。図6〜図10は、本発明の第1の実施の形態に係る半導体検査装置の製造工程を例示する図である。図6〜図10において、図3に示す第1の実施の形態の半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

続いて本発明の第1の実施の形態に係る半導体検査装置の製造方法について説明する。図6〜図10は、本発明の第1の実施の形態に係る半導体検査装置の製造工程を例示する図である。図6〜図10において、図3に示す第1の実施の形態の半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

図6〜図10を参照して、第1の実施の形態に係る半導体検査装置10の製造方法について説明する。始めに、図6に示す工程では、複数の貫通孔18を有すると共に、板状とされた基板本体15を形成する。基板本体15の材料としては、シリコン、樹脂(例えば、絶縁樹脂)、セラミックス、金属(例えば、Cu)等を用いることができる。半導体チップ25に設けられた半導体基板(図示せず)がシリコン基板の場合、基板本体15の材料としては、例えばシリコンを用いるとよい。

このように、基板本体15の材料としてシリコンを用いることにより、半導体検査装置10と半導体チップ25との間の熱膨張係数の差が緩和されるため、半導体チップ25に設けられた電極パッド26にプローブ針12を精度良く接触させることができる。基板本体15の材料としてシリコンを用いた場合、基板本体15の厚さは、例えば300μmとすることができる。又、基板本体15の材料としてシリコンを用いた場合、貫通孔18は、例えば異方性エッチング法(例えば、ドライエッチング)により形成することができる。この場合、貫通孔18の直径は、例えば50μmとすることができる。又、貫通孔18のピッチは、例えば100μmとすることができる。なお、第1の実施の形態では、基板本体15の材料としてシリコンを用いた場合を例に挙げて以下の説明を行う。

次いで、図7に示す工程では、図6に示す基板本体15の表面(貫通孔18の壁面に対応する部分の基板本体15の面も含む)を覆う絶縁膜16を形成する。絶縁膜16としては、例えば、酸化膜(例えば、熱酸化膜)を用いることができる。絶縁膜16として熱酸化膜を用いた場合、例えばシリコンからなる基板本体15を熱酸化することで、基板本体15の表面を覆う熱酸化膜を形成する。絶縁膜16として熱酸化膜を用いる場合、絶縁膜16の厚さは、例えば0.5μm〜1.0μmとすることができる。

次いで、図8に示す工程では、絶縁膜16上にランド17を形成する。これにより、基板本体15、絶縁膜16及びランド17を有する基板11が形成される。ランド17は、例えばサブトラクティブ法やセミアディティブ法等により形成することができる。ランド17の材料としては、例えばCu、Al等を用いることができる。ランド17の厚さは、例えば5μm〜10μmとすることができる。

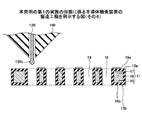

次いで、図9に示す工程では、ボンディングヘッド190を有するワイヤボンディング装置(図示せず)を起動させ、搬送機構(図示せず)によって図8に示す構造体をボンディング用ステージ(図示せず)に搬送し位置決めを行う。位置決めは、ボンディングヘッド190が挟持するボンディングワイヤ120の端部120bが、貫通孔18の真上に来るように行う。

ボンディングワイヤ120の材料としては、例えばAuを用いることができるが、これに限られるものではなく、例えばAuを含む合金、Al、Alを含む合金、Cu、Cuを含む合金等他の材料を用いても構わない。ボンディングワイヤ120のXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば25μmとすることができる。ボンディングワイヤ120の端部120bのXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば40μmとすることができる。なお、ボンディングワイヤ120は、最終的にプローブ針12となるものである。又、ボンディングワイヤ120の端部120bは、最終的にプローブ針12の端部12bとなるものである。

次いで、図10に示す工程では、ワイヤボンディング装置(図示せず)を制御し、ボンディングワイヤ120を貫通孔18に挿入し、端部120bが絶縁膜16の面16bから突出する位置で停止させる。更に、ボンディングヘッド190をランド17の方向に移動させ、ボンディングワイヤ120をランド17にワイヤボンディングすることにより、プローブ針12を形成する。他の貫通孔18に対しても同様にしてプローブ針12を形成する。これにより、図3に示す本発明の第1の実施の形態に係る半導体検査装置10が製造される。なお、ボンディングヘッド190の幅は数百μm程度であり、直径が50μm程度である貫通孔18よりも遙かに大きいため、ボンディングヘッド190を貫通孔18に挿入することはできない。

図10に示す工程の後に、プローブ針12の表面に金属層を形成しても構わない。金属層は、プローブ針12の機械的強度を高めるために形成する。金属層は、例えば電解めっき法や無電解めっき法等で形成することができる。金属層の厚さは例えば5μmとすることができる。金属層は、例えばNiめっき層とAuめっき層をこの順に積層したNi/Auめっき層や、Niめっき層とPdめっき層とAuめっき層をこの順に積層したNi/Pd/Auめっき層等とすることができる。

本発明の第1の実施の形態の半導体検査装置10によれば、バネ性を有するプローブ針12を、基板本体15及び絶縁膜16と接触しないように貫通孔18に配置し、端部12bが基板11の下面(具体的には、絶縁膜16の面16b)から突出するように半導体検査装置10に設けることにより、プローブ針12の配設ピッチPを狭くすることが可能となるため、半導体チップ25に設けられた電極パッド26が狭ピッチで配置された場合や電極パッド26がマトリックス配置された場合でも電極パッド26にプローブ針12の端部12bを精度良く接触させることができる。

〈第2の実施の形態〉

[本発明の第2の実施の形態に係る半導体検査装置の構造]

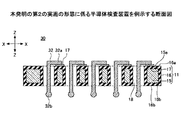

始めに本発明の第2の実施の形態に係る半導体検査装置の構造について説明する。図11は、本発明の第2の実施の形態に係る半導体検査装置を例示する断面図である。図11において、図3に示す半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

[本発明の第2の実施の形態に係る半導体検査装置の構造]

始めに本発明の第2の実施の形態に係る半導体検査装置の構造について説明する。図11は、本発明の第2の実施の形態に係る半導体検査装置を例示する断面図である。図11において、図3に示す半導体検査装置10と同一構成部分には同一符号を付し、その説明を省略する場合がある。

図11を参照するに、第2の実施の形態に係る半導体検査装置30は、プローブ針12がプローブ針32に置換された以外は、第1の実施の形態の半導体検査装置10と同様に構成される。以下、第1の実施の形態とは異なるプローブ針32についてのみ説明をする。

プローブ針32はXZ平面と平行な方向の断面形状がL字型に形成されており、基板本体15及び絶縁膜16と接触しないように、貫通孔18に配置されている。プローブ針32の端部32a(一方の端部)は、基板11を構成するランド17にワイヤボンディングされている。プローブ針32の端部32b(他方の端部)は、基板本体15の下面15bに設けられた絶縁膜16の面16b(基板11の他方の面)よりも突出している。

プローブ針32の端部32bは、半導体検査装置30が半導体チップ25の電気的検査を行う際、半導体チップ25の電極パッド26と接触する部分である。プローブ針32の端部32bの形状は、例えばレーザ光を照射されて溶融し、ボール状となっている。プローブ針32のXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば25μmとすることができる。プローブ針32の端部32bのXY平面と平行な方向の断面形状は例えば略円形であり、その直径は、例えば40μmとすることができる。

プローブ針32は、導電性を有するボンディングワイヤにより構成されている。プローブ針32を係る形状にすることで、プローブ針32はバネ性を有し、プローブ針32の端部32bをZ−Z方向に移動可能な状態で支持することができる。図4に示すプローブ針12の場合と同様に、プローブ針32の端部32bが電極パッド26と接触すると、プローブ針32の端部32bと電極パッド26とが一定の力で接触した状態で、プローブ針32の端部32bは上方に移動する。

プローブ針32を構成するボンディングワイヤの材料としては、例えばAuを用いることができるが、これに限られるものではなく、例えばAuを含む合金、Al、Alを含む合金、Cu、Cuを含む合金等他の材料を用いても構わない。

このように、バネ性を有するプローブ針32を、基板本体15及び絶縁膜16と接触しないように貫通孔18に配置し、端部32bが基板11の下面(具体的には、絶縁膜16の面16b)から突出するように半導体検査装置30に設けることにより、プローブ針32の配設ピッチPを狭くすることが可能となるため、半導体チップ25に設けられた電極パッド26が狭ピッチで配置された場合や電極パッド26がマトリックス配置された場合でも電極パッド26にプローブ針32の端部32bを精度良く接触させることができる。プローブ針32の配設ピッチPは、例えば80μm〜100μmの範囲で適宜選択することが可能である。

[本発明の第2の実施の形態に係る半導体検査装置の製造方法]

続いて本発明の第2の実施の形態に係る半導体検査装置の製造方法について説明する。図11に示すプローブ針32は、図6〜図10に示す工程と同様の工程により形成することができる。ただし、プローブ針32をランド17にワイヤボンディングする際に、ボンディングヘッド190を基板11に沿ってX−X方向に動作させる。ボンディングヘッド190を基板11に沿ってX−X方向に動作させることにより、XZ平面と平行な方向の断面形状がL字型のプローブ針32が形成される。

続いて本発明の第2の実施の形態に係る半導体検査装置の製造方法について説明する。図11に示すプローブ針32は、図6〜図10に示す工程と同様の工程により形成することができる。ただし、プローブ針32をランド17にワイヤボンディングする際に、ボンディングヘッド190を基板11に沿ってX−X方向に動作させる。ボンディングヘッド190を基板11に沿ってX−X方向に動作させることにより、XZ平面と平行な方向の断面形状がL字型のプローブ針32が形成される。

本発明の第2の実施の形態の半導体検査装置30によれば、本発明の第1の実施の形態の半導体検査装置10と同様の効果を奏する。

以上、本発明の好ましい実施の形態について詳説したが、本発明は、上述した実施の形態に制限されることはなく、本発明の範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

10,30 半導体検査装置

11 基板

12,32 プローブ針

12a,32a プローブ針12の一方の端部

12b,32b プローブ針12の他方の端部

15 基板本体

15a 基板本体15の上面

15b 基板本体15の下面

16 絶縁膜

16a,16b 絶縁膜16の面

17 ランド

18 貫通孔

25 半導体チップ

26 電極パッド

120 ボンディングワイヤ

120b ボンディングワイヤの端部

190 ボンディングヘッド

P 配設ピッチ

11 基板

12,32 プローブ針

12a,32a プローブ針12の一方の端部

12b,32b プローブ針12の他方の端部

15 基板本体

15a 基板本体15の上面

15b 基板本体15の下面

16 絶縁膜

16a,16b 絶縁膜16の面

17 ランド

18 貫通孔

25 半導体チップ

26 電極パッド

120 ボンディングワイヤ

120b ボンディングワイヤの端部

190 ボンディングヘッド

P 配設ピッチ

Claims (10)

- 基板の一方の面から他方の面に貫通する貫通孔を形成する貫通孔形成工程と、

前記基板の前記一方の面にランドを形成するランド形成工程と、

前記貫通孔に前記貫通孔の壁面と接触しないようにボンディングワイヤを挿入し、前記ボンディングワイヤの先端部を前記他方の面から突出させるボンディングワイヤ挿入工程と、

前記ボンディングワイヤの前記貫通孔に挿入されていない部分を前記ランドにワイヤボンディングし、プローブ針を形成するプローブ針形成工程と、を有する半導体検査装置の製造方法。 - 更に、前記貫通孔に前記ボンディングワイヤを挿入する前に、前記ボンディングワイヤの前記先端部を溶融し、前記ボンディングワイヤの前記先端部の形状をボール状にする溶融工程を有することを特徴とする請求項1記載の半導体検査装置の製造方法。

- 更に、前記プローブ針の表面に金属層を形成する金属層形成工程を有することを特徴とする請求項1又は2記載の半導体検査装置の製造方法。

- 更に、前記貫通孔形成工程の後に、前記基板の表面に絶縁膜を形成する絶縁膜形成工程を有することを特徴とする請求項1乃至3の何れか一項記載の半導体検査装置の製造方法。

- 基板と、

前記基板の一方の面に形成されたランドと、

前記基板の一方の面から他方の面に貫通する貫通孔と、

一方の端部が前記ランドに固定され、他方の端部が前記貫通孔の壁面と接触しないように前記貫通孔に挿入され前記他方の面から突出するプローブ針と、を有し、

電極パッドを有する半導体チップの電気的検査を行う際に、前記プローブ針の前記他方の端部が前記電極パッドと接触することを特徴とする半導体検査装置。 - 前記プローブ針は、ボンディングワイヤにより構成されていることを特徴とする請求項5記載の半導体検査装置。

- 前記貫通孔は、前記基板に行列状に複数個設けられていることを特徴とする請求項5又は6記載の半導体検査装置。

- 前記基板は、シリコンから構成されていることを特徴とする請求項5乃至7の何れか一項記載の半導体検査装置。

- 前記一方の端部は、前記ランドとワイヤボンディングにより電気的に接続されていることを特徴とする請求項5乃至8の何れか一項記載の半導体検査装置。

- 前記他方の端部の形状は、ボール状であることを特徴とする請求項5乃至9の何れか一項記載の半導体検査装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222285A JP2010054463A (ja) | 2008-08-29 | 2008-08-29 | 半導体検査装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008222285A JP2010054463A (ja) | 2008-08-29 | 2008-08-29 | 半導体検査装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010054463A true JP2010054463A (ja) | 2010-03-11 |

| JP2010054463A5 JP2010054463A5 (ja) | 2011-07-28 |

Family

ID=42070535

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008222285A Pending JP2010054463A (ja) | 2008-08-29 | 2008-08-29 | 半導体検査装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2010054463A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103869109A (zh) * | 2012-12-12 | 2014-06-18 | 华邦电子股份有限公司 | 探针卡及其焊接方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09113537A (ja) * | 1995-10-17 | 1997-05-02 | Nippon Denshi Zairyo Kk | 垂直作動型プローブカード |

| JPH1019931A (ja) * | 1996-06-28 | 1998-01-23 | Shin Etsu Polymer Co Ltd | 検査用プローブ |

| JPH11211754A (ja) * | 1998-01-30 | 1999-08-06 | Shin Etsu Polymer Co Ltd | 電気コネクタ及びその製造方法 |

| JP2007003525A (ja) * | 2005-06-23 | 2007-01-11 | Feinmetall Gmbh | 接触装置 |

| JP2007512540A (ja) * | 2003-11-26 | 2007-05-17 | フォームファクター, インコーポレイテッド | 垂直の電気的なフィードスルー構造を作る方法 |

-

2008

- 2008-08-29 JP JP2008222285A patent/JP2010054463A/ja active Pending

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09113537A (ja) * | 1995-10-17 | 1997-05-02 | Nippon Denshi Zairyo Kk | 垂直作動型プローブカード |

| JPH1019931A (ja) * | 1996-06-28 | 1998-01-23 | Shin Etsu Polymer Co Ltd | 検査用プローブ |

| JPH11211754A (ja) * | 1998-01-30 | 1999-08-06 | Shin Etsu Polymer Co Ltd | 電気コネクタ及びその製造方法 |

| JP2007512540A (ja) * | 2003-11-26 | 2007-05-17 | フォームファクター, インコーポレイテッド | 垂直の電気的なフィードスルー構造を作る方法 |

| JP2007003525A (ja) * | 2005-06-23 | 2007-01-11 | Feinmetall Gmbh | 接触装置 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103869109A (zh) * | 2012-12-12 | 2014-06-18 | 华邦电子股份有限公司 | 探针卡及其焊接方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4862017B2 (ja) | 中継基板、その製造方法、プローブカード | |

| JP5426161B2 (ja) | プローブカード | |

| KR100415245B1 (ko) | 프로브 카드, 그에 사용되는 프로브 기판 및 스페이스 트랜스포머, 이들의 제조 방법 | |

| JP2008070146A (ja) | 検査用ソケット | |

| JP2009042008A (ja) | プローブカード、半導体検査装置および半導体装置の製造方法 | |

| JP2009192309A (ja) | 半導体検査装置 | |

| KR20060028780A (ko) | 프로브 카드 및 프로브 시트 또는 프로브 카드를 이용한반도체 검사 장치 및 반도체 장치의 제조 방법 | |

| KR20070111327A (ko) | 전송 회로, 접속용 시트, 프로브 시트, 프로브 카드,반도체 검사 장치, 및 반도체 장치의 제조 방법 | |

| JP2004317492A (ja) | プローブカードのニードルアセンブリ | |

| JP2007171140A (ja) | プローブカード、インターポーザおよびインターポーザの製造方法 | |

| JPWO2004072661A1 (ja) | 電気的接続装置 | |

| JP2009276316A (ja) | プローブカード | |

| KR100393452B1 (ko) | 반도체소자검사용 기판의 제조방법 | |

| KR101990458B1 (ko) | 프로브 카드 및 그 제조방법 | |

| JP2004144742A (ja) | プローブシート、プローブカード、半導体検査装置および半導体装置の製造方法 | |

| JP2013168400A (ja) | 半導体デバイス検査装置用配線基板及びその製造方法 | |

| JP2007279009A (ja) | 接触子組立体 | |

| JP4962929B2 (ja) | プローバ装置及びこれに用いるプローブ組立体 | |

| JP5145089B2 (ja) | 電気特性測定用配線基板、及び電気特性測定用配線基板の製造方法 | |

| JP2010054463A (ja) | 半導体検査装置及びその製造方法 | |

| JP2004235591A (ja) | 電気的接続装置 | |

| JP2010256371A (ja) | 半導体ウェハの検査方法および半導体装置の製造方法 | |

| JP2012141274A (ja) | プローブカード用セラミック基板及びその製造方法 | |

| KR101066551B1 (ko) | 프로브 카드 제조에 사용되는 핀 어레이 틀 | |

| JP2009098153A (ja) | 薄膜プローブの製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110614 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110614 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121219 |

|

| A02 | Decision of refusal |

Effective date: 20130507 Free format text: JAPANESE INTERMEDIATE CODE: A02 |