JP2010033675A - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP2010033675A JP2010033675A JP2008196366A JP2008196366A JP2010033675A JP 2010033675 A JP2010033675 A JP 2010033675A JP 2008196366 A JP2008196366 A JP 2008196366A JP 2008196366 A JP2008196366 A JP 2008196366A JP 2010033675 A JP2010033675 A JP 2010033675A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- line

- column

- voltage

- bit line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/408—Address circuits

- G11C11/4087—Address decoders, e.g. bit - or word line decoders; Multiple line decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/08—Word line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, for word lines

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/02—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using elements whose operation depends upon chemical change

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0004—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements comprising amorphous/crystalline phase transition cells

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0009—RRAM elements whose operation depends upon chemical change

- G11C13/0011—RRAM elements whose operation depends upon chemical change comprising conductive bridging RAM [CBRAM] or programming metallization cells [PMCs]

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C13/00—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00

- G11C13/0002—Digital stores characterised by the use of storage elements not covered by groups G11C11/00, G11C23/00, or G11C25/00 using resistive RAM [RRAM] elements

- G11C13/0021—Auxiliary circuits

- G11C13/0023—Address circuits or decoders

- G11C13/0028—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/02—Disposition of storage elements, e.g. in the form of a matrix array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/06—Arrangements for interconnecting storage elements electrically, e.g. by wiring

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/71—Three dimensional array

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2213/00—Indexing scheme relating to G11C13/00 for features not covered by this group

- G11C2213/70—Resistive array aspects

- G11C2213/72—Array wherein the access device being a diode

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Computer Hardware Design (AREA)

- Semiconductor Memories (AREA)

Abstract

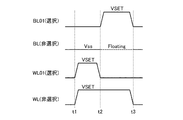

【解決手段】半導体記憶装置は、ダイオードDiと可変抵抗素子VRとが直列接続されたメモリセルMCが複数のビット線BL及び複数のワード線の交差部に配置されたメモリセルアレイMAと、ビット線BL及びワード線WLを選択駆動する制御回路とを備える。制御回路は、選択されたビット線BL01及び選択されたワード線WL01の交差部に配置された選択メモリセルMC11に電位差VSETがかかるよう、選択されたビット線BL01に電圧VSETを印加し、選択されたワード線WL01に電圧0Vを印加するとともに、非選択のビット線BL00、02、03の少なくとも1本をフローティング状態にする。

【選択図】図2

Description

図1は、本発明の実施の形態に係る抵抗変化メモリ装置の基本構成、すなわち半導体基板1上のグローバルバス等の配線が形成される配線領域3とその上に積層されたメモリブロック2の構成を示している。

次に、本発明に係る抵抗変化メモリ装置の第2の実施の形態について図3〜図12を参照して説明する。図3は、抵抗変化メモリ装置のメモリセルアレイMAの配線を示す図である。また、図4は抵抗変化メモリ装置のカラム/ロウ制御回路の配置例を示すブロック図である。そして、図5〜図12は抵抗変化メモリ装置のカラム/ロウ制御回路の構成例を示す回路図である。ここで、第2の実施形態に係る抵抗変化メモリ装置の基本構成は、第1の実施形態に係る抵抗変化メモリ装置と同様である。第2の実施の形態に係る抵抗変化メモリ装置において、第1の実施の形態と同一の構成を有する箇所には、同一の符号を付すことによりその説明を省略する。

次に、ビット線BL及びワード線WLにこのような電圧を印加するためのカラム制御回路及びロウ制御回路の構成について説明する。ここでも、ワード線方向に2Kbit(=2048bit)、ビット線方向に512bitのメモリセルMCを配列して1MbitのメモリセルアレイMAを構成する場合を例として説明する。図4は、抵抗変化メモリ装置のカラム制御回路及びロウ制御回路の配置例を示すブロック図である。

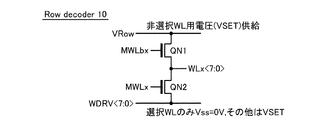

図4及び図5に示されるように、ロウデコーダ10には256対のメインワード線MWLx及びMWLbx(x=<255:0>)のいずれか一対、ロウ電源線VRow並びに書き込み駆動線WDRV<7:0>が接続されている。また、ロウデコーダ10には、ワード線群WLx<7:0>が接続されており、このワード線群WLx<7:0>は一列に並んで設けられた複数のメモリセルMCに接続されている。前述のように1つのロウデコーダ10に接続されるワード線群WLx<7:0>はワード線WLx0〜ワード線WLx7までの8本の配線からなる。同様に、書き込み駆動線WDRV<7:0>は、WDRV0〜WDRV7までの8本の配線からなる配線である。

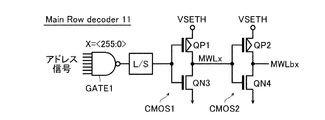

図4及び図6に示されるように、メインロウデコーダ11には256対のメインワード線MWLx及びMWLbx(x=<255:0>)、並びにアドレス信号線が接続されている。本実施の形態に係る抵抗変化メモリ装置のワード線WLは階層化構造を有している。メインロウデコーダ11はプリデコーダであり、一組のメインワード線MWLx、MWLbxは1つのロウデコーダ10内の8つのトランジスタ対(図5のQN1、QN2)にそれぞれ接続され、1つのロウデコーダ10は8本のワード線WLx<7:0>のいずれか1本を選択することができる。メインロウデコーダ11は、図6に示すような回路を、1対のメインワード線MWLx、MWLbxごとに有している。

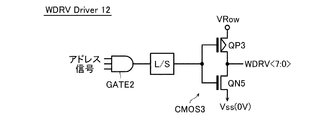

図4及び図7に示されるように、書き込み駆動線ドライバ12には、ロウ電源線VRow及びアドレス信号線が接続されている。ここで、書き込み駆動線ドライバ12も、プリデコーダである。

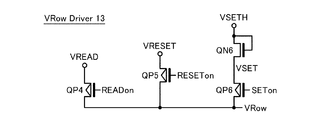

図4及び図8に示されるように、ロウ電源線ドライバ13には、ロウ電源線VRow及び制御信号線が接続されている。ロウ電源線ドライバ13において、電源VREADがPMOSトランジスタQP4を介して、電源VRESETがPMOSトランジスタQP5を介してそれぞれロウ電源線VRowに接続されている。トランジスタQP4のゲートには制御信号READonが供給され、トランジスタQP5のゲートには制御信号RESETonが供給される。制御信号READon、RESETonは、それぞれデータ読み出し時、リセット動作時に“H”状態から“L”状態となる。

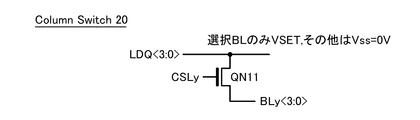

図4及び図9に示されるように、カラムスイッチ20には128本のカラム選択線CSLy(y=<127:0>)のいずれか一本及びローカルデータ線LDQ<3:0>が接続されている。また、カラムスイッチ20には、ビット線群BLy<3:0>が接続されており、このビット線BLは一列に並んで設けられた複数のメモリセルMCに接続されている。前述のように、1つのカラムスイッチ20に接続されるビット線群BLy<3:0>はビット線BLy0〜ビット線BLy3までの4本の配線からなる。同様に、ローカルデータ線LDQ<3:0>は、LDQ0〜LDQ3までの4本の配線からなる配線である。

図4及び図10に示されるように、カラムデコーダ21には128本のカラム選択線CSLy(y=<127:0>)及びアドレス信号線が接続されている。本実施の形態に係る抵抗変化メモリ装置において、一本のカラム選択線CSLyは1つのカラムスイッチ20内の4つのトランジスタ(図9のQN11)にそれぞれ接続され、1つのカラムスイッチ20は4本のビット線群BLy<3:0>のいずれか1本を選択することができる。カラムデコーダ21は、図10に示すような回路を、一本のカラム選択線CSLy毎に有している。

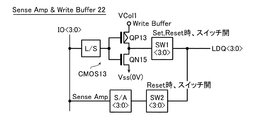

図4及び図11に示されるように、センスアンプ/書き込みバッファ22には、カラム電源線VCol1、ローカルデータ線LDQ<3:0>及びデータ入出力線IO<3:0>が接続されている。まず、書き込みバッファ部分について、その構成を説明する。センスアンプ/書き込みバッファ22に接続されたデータ入出力線IO<3:0>は、レベルシフタL/Sを介してPMOSトランジスタQP13及びNMOSトランジスタQN15からなるCMOSインバータCMOS13に接続される。トランジスタQP13のソースにはカラム電源線VCol1が接続されている。カラム電源線VCol1には後述するように電圧VSETが印加されている。また、トランジスタQN15のソースは接地されている。そして、トランジスタQP13及びQN15のドレインはともにスイッチSW1を介してローカルデータ線LDQ<3:0>に接続されている。

図4及び図12に示されるように、カラム電源線ドライバ23には、カラム電源線VCol1及び制御信号線が接続されている。カラム電源線ドライバ23において、電源VRESETがPMOSトランジスタQP15を介してカラム電源線VCol1に接続されている。トランジスタQP15のゲートには制御信号RESETonが供給される。また、電源VSETHがNMOSトランジスタQN16のドレイン及びゲートに接続され、トランジスタQN16のソースはPMOSトランジスタQP14を介してカラム電源線VCol1に接続されている。トランジスタQP14のゲートには制御信号SETonが供給される。

セット動作時には、ロウ電源線ドライバ13において、トランジスタQP6のゲートに供給されていた制御信号(SETon信号)が“L”状態になり導通する。電源VSETHの電圧VSETHはNMOSトランジスタQN6により転送されて電圧VSETとなる。セット動作時に、ロウ電源線ドライバ13はロウ電源線VRowを電圧VSETに駆動する。

書き込み駆動線ドライバ12の論理ゲートGATE2には、アドレス信号が入力される。このアドレス信号に基づき、論理ゲートGATE2は、アドレス信号に対応する一の書き込み駆動線(例えばWDRV1)について、“H”信号を、対応しない他の書き込み駆動線について“L”信号をCMOSインバータCMOS3の入力端子に供給する。アドレス信号に対応する書き込み駆動線(例えばWDRV1)の場合、CMOSインバータCMOS3の入力端子には“H”信号が供給され、導通したトランジスタQN5を介して接地電圧Vss(例えば0V)が書き込み駆動線WDRV1に印加される。アドレス信号に対応しない書き込み駆動線の場合、CMOSインバータCMOS3の入力端子には“L”信号が供給され、導通したトランジスタQP3を介してロウ電源線VRowの電圧(VSET)が書き込み駆動線WDRVに印加される。

メインロウデコーダ11の論理ゲートGATE1の入力端子にも、アドレス信号が供給される。このアドレス信号に基づき、論理ゲートGATE1は、x=<255:0>のうち選択されたx(例えばx=0)について“L”信号を、選択されていないxについて“H”信号をCMOSインバータCMOS1の入力端子に供給する。まず、選択されたx(例えばx=0)について説明する。選択されたx(例えばx=0)の場合、CMOSインバータCMOS1の入力端子には“L”信号が供給され、導通したトランジスタQP1を介して電源VSETHの“H”信号がメインワード線MWL0に供給される。また、メインワード線MWL0の“H”信号は、CMOSインバータCMOS2の入力端子に供給され、導通したトランジスタQN4を介して接地電圧Vssの“L”信号がメインワード線MWLb0に供給される。すなわち、選択されたx(例えばx=0)の場合、メインワード線MWL0には、“H”信号、メインワード線MWLb0には“L”信号が供給される。

ロウデコーダ10は、メインワード線MWLx及びMWLbxに供給された信号に基づき、ロウ電源線VRow又は書き込み駆動線WDRVの電圧をワード線WLに対して印加する。選択されたx(例えばx=0)の場合、メインワード線MWL0には、“H”信号、メインワード線MWLb0には“L”信号が供給されている。ロウデコーダ10のトランジスタQN1のゲートに“L”信号が供給され、トランジスタQN2のゲートに“H”信号が供給されるため、ワード線群WL0<7:0>には導通したトランジスタQN2を介して書き込み駆動線WDRV<7:0>の電圧が印加される。ここで、アドレス信号に対応する書き込み駆動線(例えばWDRV1)には、接地電圧(例えば0V)が印加され、アドレス信号に対応しないその他の書き込み駆動線には、ロウ電源線VRowの電圧(例えばVSET)が印加されている。ワード線群WL0<7:0>のうち、アドレス信号に対応するワード線WL01の1本のみに接地電圧(例えば0V)が印加され、その他のワード線WLには電圧VSETが印加される。

セット動作時には、カラム電源線ドライバ23において、トランジスタQP14のゲートに供給されていた制御信号(SETon信号)が“L”状態になり導通する。電源VSETHの電圧VSETHはNMOSトランジスタQN16により転送されて電圧VSETとなり、電圧VSETでカラム電源線VCol1を駆動する。

センスアンプ/書き込みバッファ22において、セット動作時に書き込みバッファ部のスイッチSW1がオンとなり導通状態になるとともに、センスアンプ部のスイッチSW2がオフとなり非導通状態になる。センスアンプ/書き込みバッファ22には、データ入出力線IO<3:0>より書き込みデータが供給される。この書き込みデータがレベルシフタL/Sを介してCMOSインバータCMOS13の入力端子に供給される。このデータに応じてローカルデータ線LDQ<3:0>には電圧VSET又は接地電圧(Vss=0V)が印加される。

カラムデコーダ21の論理ゲートGATE3の入力端子には、アドレス信号が供給される。このアドレス信号に基づき、論理ゲートGATE3は、y=<127:0>のうち選択されたy(例えばy=0)について“L”信号を、選択されていないyについて“H”信号をCMOSインバータCMOS11の入力端子に供給する。まず、選択されたy(例えばy=0)について説明する。選択されたy(例えばy=0)の場合、CMOSインバータCMOS11の入力端子には“L”信号が供給され、導通したトランジスタQP11を介して電源VSETHの“H”信号がカラム選択線CSL0に供給される。次に、選択されていないyについて説明する。選択されていないyの場合、CMOSインバータCMOS11の入力端子には“H”信号が供給され、導通したトランジスタQN13を介して接地電圧Vssの“L”信号がカラム選択線CSLyに供給される。

カラムスイッチ20は、カラム選択線CSLyに供給された信号に基づき、ローカルデータ線LDQの電圧をビット線BLに対して印加する。選択されたy(例えばy=0)の場合、カラム選択線CSL0には、“H”信号が供給されている。カラムスイッチ20のトランジスタQN11のゲートに“H”信号が供給されるため、ビット線群BL0<3:0>には導通したトランジスタQN12を介してローカルデータ線LDQ<3:0>の電圧が印加される。ここで、アドレス信号に対応するローカルデータ線(例えばLDQ1)には、カラム電源線VCol1の電圧(VSET)が印加され、アドレス信号に対応しないその他のローカルデータ線には、接地電圧Vss(=0V)が印加されている。ビット線群BL0<3:0>のうち、アドレス信号に対応するビット線BL01の1本のみにカラム電源線VCol1の電圧(VSET)が印加され、その他のビット線BLには接地電圧Vss(=0V)が印加される。

次に、本発明に係る抵抗変化メモリ装置の第3の実施の形態について図13を参照して説明する。図13は、抵抗変化メモリ装置のカラム/ロウ制御回路の動作タイミングを示すタイミングチャートである。ここで、第3の実施形態に係る抵抗変化メモリ装置の制御回路の構成は第1及び第2の実施形態に係る抵抗変化メモリ装置と同様である。第3の実施の形態に係る抵抗変化メモリ装置において、第1及び第2の実施の形態と同一の構成を有する箇所には、同一の符号を付すことによりその説明を省略する。本実施の形態に係る抵抗変化メモリ装置は、セット動作を実行する際にワード線WL及びビット線BLに電圧を印加するタイミングを異ならせる点において、第1及び第2の実施の形態と異なる。

次に、本発明に係る抵抗変化メモリ装置の第4の実施の形態について図14〜図16を参照して説明する。図14は抵抗変化メモリ装置のカラム/ロウ制御回路の配置例を示すブロック図である。そして、図15〜図16は抵抗変化メモリ装置のカラム制御回路の構成例を示す回路図である。図14〜図16に示す本実施の形態に係る抵抗変化メモリ装置において、第1〜第3の実施の形態と同一の構成を有する箇所には、同一符号を付すことによりその説明を省略する。

Claims (5)

- 整流素子と可変抵抗素子とを直列接続してなるメモリセルが複数の第1配線及び複数の第2配線の交差部に配置されたメモリセルアレイと、

前記第1配線及び前記第2配線を選択駆動する制御回路と

を備え、

前記制御回路は、

選択された前記第1配線及び選択された前記第2配線の交差部に配置された選択メモリセルに所定の電位差がかかるよう、選択された前記第1配線に第1の電圧を印加し、選択された前記第2配線に第2の電圧を印加するとともに、

非選択の前記第1配線の少なくとも1本をフローティング状態にする

ことを特徴とする半導体記憶装置。 - 前記制御回路は、

選択された前記第2配線に第2の電圧を印加した後に、

選択された前記第1配線に第1の電圧を印加し、非選択の前記第1配線をフローティング状態にする

ことを特徴とする請求項1記載の半導体記憶装置。 - 前記制御回路は、

前記第1配線に接続され、前記第1配線が選択されるときに導通して前記第1配線に第1の電圧を印加するとともに、前記第1配線が非選択のときは非導通状態になり前記第1配線をフローティング状態にする1つのトランジスタからなる第1配線選択部を有する

ことを特徴とする請求項1又は2記載の半導体記憶装置。 - 所定の本数の前記第1配線からなる複数の第1配線群をさらに備え、

前記制御回路は、

選択された前記第1配線を含む前記第1配線群内の選択された前記第1配線に第1の電圧を、非選択の前記第1配線に第2の電圧を印加し、

選択された前記第1配線を含まない前記第1配線群のうち、

選択された前記第1配線を含む前記第1配線群に隣接する前記第1配線群内の前記第1配線に第2の電圧を印加し、

選択された前記第1配線を含む前記第1配線群に隣接しない前記第1配線群内の前記第1配線をフローティング状態にする

ことを特徴とする請求項1乃至3のいずれか記載の半導体記憶装置。 - 前記制御回路は、

非選択の前記第2配線に前記第1の電圧を印加する

ことを特徴とする請求項1乃至4のいずれか記載の半導体記憶装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196366A JP5100555B2 (ja) | 2008-07-30 | 2008-07-30 | 半導体記憶装置 |

| TW098120891A TWI451419B (zh) | 2008-07-30 | 2009-06-22 | Semiconductor memory device |

| US12/510,798 US8094477B2 (en) | 2008-07-30 | 2009-07-28 | Resistance change semiconductor storage device |

| KR1020090069284A KR101087408B1 (ko) | 2008-07-30 | 2009-07-29 | 반도체 기억 장치 |

| US13/309,334 US8451681B2 (en) | 2008-07-30 | 2011-12-01 | Semiconductor storage device including memory cells each having a variable resistance element |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008196366A JP5100555B2 (ja) | 2008-07-30 | 2008-07-30 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010033675A true JP2010033675A (ja) | 2010-02-12 |

| JP5100555B2 JP5100555B2 (ja) | 2012-12-19 |

Family

ID=41608191

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008196366A Expired - Fee Related JP5100555B2 (ja) | 2008-07-30 | 2008-07-30 | 半導体記憶装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US8094477B2 (ja) |

| JP (1) | JP5100555B2 (ja) |

| KR (1) | KR101087408B1 (ja) |

| TW (1) | TWI451419B (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012160863A1 (en) | 2011-05-26 | 2012-11-29 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| JP2013137850A (ja) * | 2011-12-28 | 2013-07-11 | Toshiba Corp | 半導体記憶装置 |

| US8605485B2 (en) | 2011-03-02 | 2013-12-10 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor storage device and forming method |

| US8687406B2 (en) | 2012-03-26 | 2014-04-01 | Kabushiki Kaisha Toshiba | Semiconductor memory device and method of controlling the same |

| US8804402B2 (en) | 2012-08-31 | 2014-08-12 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| US9190146B2 (en) | 2013-02-28 | 2015-11-17 | Kabushiki Kaisha Toshiba | Variable resistance memory system with redundancy lines and shielded bit lines |

| US9214226B2 (en) | 2011-03-24 | 2015-12-15 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| CN110021324A (zh) * | 2018-01-10 | 2019-07-16 | 爱思开海力士有限公司 | 可变电阻存储器件 |

Families Citing this family (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7768812B2 (en) | 2008-01-15 | 2010-08-03 | Micron Technology, Inc. | Memory cells, memory cell programming methods, memory cell reading methods, memory cell operating methods, and memory devices |

| JP5049814B2 (ja) | 2008-02-14 | 2012-10-17 | 株式会社東芝 | 不揮発性半導体記憶装置のデータ書き込み方法 |

| US8034655B2 (en) | 2008-04-08 | 2011-10-11 | Micron Technology, Inc. | Non-volatile resistive oxide memory cells, non-volatile resistive oxide memory arrays, and methods of forming non-volatile resistive oxide memory cells and memory arrays |

| US8211743B2 (en) | 2008-05-02 | 2012-07-03 | Micron Technology, Inc. | Methods of forming non-volatile memory cells having multi-resistive state material between conductive electrodes |

| US8134137B2 (en) | 2008-06-18 | 2012-03-13 | Micron Technology, Inc. | Memory device constructions, memory cell forming methods, and semiconductor construction forming methods |

| US9343665B2 (en) | 2008-07-02 | 2016-05-17 | Micron Technology, Inc. | Methods of forming a non-volatile resistive oxide memory cell and methods of forming a non-volatile resistive oxide memory array |

| JP5100555B2 (ja) | 2008-07-30 | 2012-12-19 | 株式会社東芝 | 半導体記憶装置 |

| US8427859B2 (en) | 2010-04-22 | 2013-04-23 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8411477B2 (en) | 2010-04-22 | 2013-04-02 | Micron Technology, Inc. | Arrays of vertically stacked tiers of non-volatile cross point memory cells, methods of forming arrays of vertically stacked tiers of non-volatile cross point memory cells, and methods of reading a data value stored by an array of vertically stacked tiers of non-volatile cross point memory cells |

| US8289763B2 (en) | 2010-06-07 | 2012-10-16 | Micron Technology, Inc. | Memory arrays |

| US8351242B2 (en) | 2010-09-29 | 2013-01-08 | Micron Technology, Inc. | Electronic devices, memory devices and memory arrays |

| US8759809B2 (en) | 2010-10-21 | 2014-06-24 | Micron Technology, Inc. | Integrated circuitry comprising nonvolatile memory cells having platelike electrode and ion conductive material layer |

| US8526213B2 (en) | 2010-11-01 | 2013-09-03 | Micron Technology, Inc. | Memory cells, methods of programming memory cells, and methods of forming memory cells |

| US8796661B2 (en) | 2010-11-01 | 2014-08-05 | Micron Technology, Inc. | Nonvolatile memory cells and methods of forming nonvolatile memory cell |

| US9454997B2 (en) | 2010-12-02 | 2016-09-27 | Micron Technology, Inc. | Array of nonvolatile memory cells having at least five memory cells per unit cell, having a plurality of the unit cells which individually comprise three elevational regions of programmable material, and/or having a continuous volume having a combination of a plurality of vertically oriented memory cells and a plurality of horizontally oriented memory cells; array of vertically stacked tiers of nonvolatile memory cells |

| US8431458B2 (en) | 2010-12-27 | 2013-04-30 | Micron Technology, Inc. | Methods of forming a nonvolatile memory cell and methods of forming an array of nonvolatile memory cells |

| US8791447B2 (en) | 2011-01-20 | 2014-07-29 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| US8488365B2 (en) | 2011-02-24 | 2013-07-16 | Micron Technology, Inc. | Memory cells |

| US8537592B2 (en) * | 2011-04-15 | 2013-09-17 | Micron Technology, Inc. | Arrays of nonvolatile memory cells and methods of forming arrays of nonvolatile memory cells |

| KR20140044355A (ko) * | 2011-06-01 | 2014-04-14 | 가부시키가이샤 엔티티 도코모 | 소형 노드 디바이스들을 이용한 모바일 통신에서의 향상된 로컬 액세스 |

| JP2013122985A (ja) * | 2011-12-12 | 2013-06-20 | Toshiba Corp | 半導体記憶装置 |

| KR20150103723A (ko) | 2013-01-03 | 2015-09-11 | 메타 컴퍼니 | 가상 또는 증강매개된 비전을 위한 엑스트라미시브 공간 이미징 디지털 아이 글래스 |

| US11984163B2 (en) | 2013-03-15 | 2024-05-14 | Hefei Reliance Memory Limited | Processing unit with fast read speed memory device |

| US9230641B2 (en) * | 2013-03-15 | 2016-01-05 | Rambus Inc. | Fast read speed memory device |

| US9123410B2 (en) | 2013-08-27 | 2015-09-01 | Intel Corporation | Memory controller for reducing capacitive coupling in a cross-point memory |

| KR102261813B1 (ko) | 2014-11-26 | 2021-06-07 | 삼성전자주식회사 | 저항성 메모리 장치 및 저항성 메모리 장치의 동작 방법 |

| TWI560714B (en) * | 2014-12-24 | 2016-12-01 | Winbond Electronics Corp | Resistance random access memory |

| IT201600088225A1 (it) * | 2016-08-30 | 2018-03-02 | St Microelectronics Srl | Circuito traslatore di livello, in particolare per l'utilizzo in un dispositivo di memoria, e relativo dispositivo di memoria |

| JP2020047317A (ja) * | 2018-09-14 | 2020-03-26 | キオクシア株式会社 | 不揮発性記憶装置 |

| JP2020087493A (ja) * | 2018-11-26 | 2020-06-04 | キオクシア株式会社 | 半導体記憶装置 |

| JP2021144771A (ja) * | 2020-03-12 | 2021-09-24 | キオクシア株式会社 | 半導体記憶装置及びメモリシステム |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006127583A (ja) * | 2004-10-26 | 2006-05-18 | Elpida Memory Inc | 不揮発性半導体記憶装置及び相変化メモリ |

| JP2007073176A (ja) * | 2005-09-08 | 2007-03-22 | Samsung Electronics Co Ltd | 相変化メモリ装置 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7767993B2 (en) * | 2002-04-04 | 2010-08-03 | Kabushiki Kaisha Toshiba | Resistance change memory device |

| KR100642186B1 (ko) | 2002-04-04 | 2006-11-10 | 가부시끼가이샤 도시바 | 상-변화 메모리 디바이스 |

| JP2008077697A (ja) * | 2006-09-19 | 2008-04-03 | Toshiba Corp | 半導体記憶装置 |

| KR100827697B1 (ko) * | 2006-11-10 | 2008-05-07 | 삼성전자주식회사 | 3차원 구조를 가지는 반도체 메모리 장치 및 셀 어레이구조 |

| JP5100555B2 (ja) | 2008-07-30 | 2012-12-19 | 株式会社東芝 | 半導体記憶装置 |

-

2008

- 2008-07-30 JP JP2008196366A patent/JP5100555B2/ja not_active Expired - Fee Related

-

2009

- 2009-06-22 TW TW098120891A patent/TWI451419B/zh not_active IP Right Cessation

- 2009-07-28 US US12/510,798 patent/US8094477B2/en active Active

- 2009-07-29 KR KR1020090069284A patent/KR101087408B1/ko not_active Expired - Fee Related

-

2011

- 2011-12-01 US US13/309,334 patent/US8451681B2/en active Active

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2006127583A (ja) * | 2004-10-26 | 2006-05-18 | Elpida Memory Inc | 不揮発性半導体記憶装置及び相変化メモリ |

| JP2007073176A (ja) * | 2005-09-08 | 2007-03-22 | Samsung Electronics Co Ltd | 相変化メモリ装置 |

Cited By (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8605485B2 (en) | 2011-03-02 | 2013-12-10 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor storage device and forming method |

| US9520188B2 (en) | 2011-03-24 | 2016-12-13 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US9214226B2 (en) | 2011-03-24 | 2015-12-15 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| TWI471860B (zh) * | 2011-05-26 | 2015-02-01 | Toshiba Kk | 半導體記憶裝置 |

| KR20140012178A (ko) | 2011-05-26 | 2014-01-29 | 가부시끼가이샤 도시바 | 반도체 메모리 장치 |

| WO2012160863A1 (en) | 2011-05-26 | 2012-11-29 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US9245621B2 (en) | 2011-05-26 | 2016-01-26 | Kabushiki Kaisha Toshiba | Semiconductor memory device executing a write operation with first and second voltage applications |

| JP2012248242A (ja) * | 2011-05-26 | 2012-12-13 | Toshiba Corp | 半導体記憶装置 |

| US8665632B2 (en) | 2011-12-28 | 2014-03-04 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| US9135991B2 (en) | 2011-12-28 | 2015-09-15 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| JP2013137850A (ja) * | 2011-12-28 | 2013-07-11 | Toshiba Corp | 半導体記憶装置 |

| US8687406B2 (en) | 2012-03-26 | 2014-04-01 | Kabushiki Kaisha Toshiba | Semiconductor memory device and method of controlling the same |

| US8804402B2 (en) | 2012-08-31 | 2014-08-12 | Kabushiki Kaisha Toshiba | Nonvolatile semiconductor memory device |

| US9190146B2 (en) | 2013-02-28 | 2015-11-17 | Kabushiki Kaisha Toshiba | Variable resistance memory system with redundancy lines and shielded bit lines |

| CN110021324A (zh) * | 2018-01-10 | 2019-07-16 | 爱思开海力士有限公司 | 可变电阻存储器件 |

| CN110021324B (zh) * | 2018-01-10 | 2023-05-05 | 爱思开海力士有限公司 | 可变电阻存储器件 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8451681B2 (en) | 2013-05-28 |

| US20120075915A1 (en) | 2012-03-29 |

| TW201013678A (en) | 2010-04-01 |

| JP5100555B2 (ja) | 2012-12-19 |

| KR20100013269A (ko) | 2010-02-09 |

| US20100027308A1 (en) | 2010-02-04 |

| US8094477B2 (en) | 2012-01-10 |

| TWI451419B (zh) | 2014-09-01 |

| KR101087408B1 (ko) | 2011-11-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5100555B2 (ja) | 半導体記憶装置 | |

| JP5178472B2 (ja) | 半導体記憶装置 | |

| JP5106297B2 (ja) | 半導体記憶装置 | |

| JP4856202B2 (ja) | 半導体記憶装置 | |

| JP5127665B2 (ja) | 半導体記憶装置 | |

| JP4806046B2 (ja) | 半導体記憶装置 | |

| JP4846813B2 (ja) | 不揮発性半導体記憶装置 | |

| JP5161981B2 (ja) | 半導体装置 | |

| JP5175769B2 (ja) | 半導体記憶装置 | |

| JP2009266312A (ja) | 半導体記憶装置 | |

| JP5214693B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2010020811A (ja) | 半導体記憶装置 | |

| JP5086919B2 (ja) | 半導体記憶装置 | |

| JP2012069217A (ja) | 不揮発性半導体記憶装置 | |

| JP5630742B2 (ja) | 半導体記憶装置 | |

| JP2010123820A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120806 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120828 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120925 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151005 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5100555 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151005 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |