JP2009158622A - 半導体記憶装置及びその製造方法 - Google Patents

半導体記憶装置及びその製造方法 Download PDFInfo

- Publication number

- JP2009158622A JP2009158622A JP2007333306A JP2007333306A JP2009158622A JP 2009158622 A JP2009158622 A JP 2009158622A JP 2007333306 A JP2007333306 A JP 2007333306A JP 2007333306 A JP2007333306 A JP 2007333306A JP 2009158622 A JP2009158622 A JP 2009158622A

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- region

- active region

- semiconductor substrate

- gate insulating

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 96

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 41

- 230000002093 peripheral effect Effects 0.000 claims abstract description 85

- 239000000758 substrate Substances 0.000 claims abstract description 52

- 239000012535 impurity Substances 0.000 claims abstract description 36

- 238000005468 ion implantation Methods 0.000 claims description 32

- 238000002955 isolation Methods 0.000 claims description 31

- 239000000463 material Substances 0.000 claims description 18

- 238000000034 method Methods 0.000 claims description 14

- 230000008569 process Effects 0.000 claims description 8

- 238000003860 storage Methods 0.000 claims description 7

- 230000001154 acute effect Effects 0.000 claims description 3

- 230000000149 penetrating effect Effects 0.000 claims 1

- 238000002513 implantation Methods 0.000 abstract description 16

- 239000010410 layer Substances 0.000 description 65

- 229910052796 boron Inorganic materials 0.000 description 46

- -1 boron ions Chemical class 0.000 description 34

- 239000011229 interlayer Substances 0.000 description 23

- 230000015556 catabolic process Effects 0.000 description 19

- 229910052751 metal Inorganic materials 0.000 description 15

- 239000002184 metal Substances 0.000 description 15

- 150000002500 ions Chemical class 0.000 description 13

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 12

- 230000015572 biosynthetic process Effects 0.000 description 12

- 230000006870 function Effects 0.000 description 12

- 238000009792 diffusion process Methods 0.000 description 11

- 230000000694 effects Effects 0.000 description 8

- 238000009826 distribution Methods 0.000 description 6

- 238000001020 plasma etching Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000007257 malfunction Effects 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 239000000470 constituent Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 238000001459 lithography Methods 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 2

- 239000007943 implant Substances 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 229920002120 photoresistant polymer Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 229910015900 BF3 Inorganic materials 0.000 description 1

- 229910019001 CoSi Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910016006 MoSi Inorganic materials 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- 229910005883 NiSi Inorganic materials 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 229910008484 TiSi Inorganic materials 0.000 description 1

- 229910008812 WSi Inorganic materials 0.000 description 1

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical group Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 description 1

- WTEOIRVLGSZEPR-UHFFFAOYSA-N boron trifluoride Chemical compound FB(F)F WTEOIRVLGSZEPR-UHFFFAOYSA-N 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- OKZIUSOJQLYFSE-UHFFFAOYSA-N difluoroboron Chemical compound F[B]F OKZIUSOJQLYFSE-UHFFFAOYSA-N 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000010248 power generation Methods 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26586—Bombardment with radiation with high-energy radiation producing ion implantation characterised by the angle between the ion beam and the crystal planes or the main crystal surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40114—Multistep manufacturing processes for data storage electrodes the electrodes comprising a conductor-insulator-conductor-insulator-semiconductor structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/401—Multistep manufacturing processes

- H01L29/4011—Multistep manufacturing processes for data storage electrodes

- H01L29/40117—Multistep manufacturing processes for data storage electrodes the electrodes comprising a charge-trapping insulator

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42324—Gate electrodes for transistors with a floating gate

- H01L29/42336—Gate electrodes for transistors with a floating gate with one gate at least partly formed in a trench

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/4234—Gate electrodes for transistors with charge trapping gate insulator

- H01L29/42352—Gate electrodes for transistors with charge trapping gate insulator with the gate at least partly formed in a trench

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/788—Field effect transistors with field effect produced by an insulated gate with floating gate

- H01L29/7881—Programmable transistors with only two possible levels of programmation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/792—Field effect transistors with field effect produced by an insulated gate with charge trapping gate insulator, e.g. MNOS-memory transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/40—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region

- H10B41/41—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the peripheral circuit region of a memory region comprising a cell select transistor, e.g. NAND

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/30—EEPROM devices comprising charge-trapping gate insulators characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B43/00—EEPROM devices comprising charge-trapping gate insulators

- H10B43/40—EEPROM devices comprising charge-trapping gate insulators characterised by the peripheral circuit region

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Ceramic Engineering (AREA)

- Manufacturing & Machinery (AREA)

- High Energy & Nuclear Physics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Semiconductor Memories (AREA)

- Element Separation (AREA)

- Non-Volatile Memory (AREA)

Abstract

【解決手段】メモリMOSトランジスタが配置される第1活性領域と、周辺MOSトランジスタが配置される第2活性領域と、半導体基板10中に形成され、側壁において第1活性領域が露出される第1トレンチ43と、第1トレンチ43内を埋め込む絶縁膜を備え、隣接する第1活性領域間を電気的に分離する第1素子分離領域と、半導体基板10中に形成され、側壁において第2活性領域が露出される第2トレンチ43と、第2トレンチ43内を埋め込む絶縁膜27を備え、隣接する第2活性領域間を電気的に分離する第2素子分離領域35とを具備し、第2活性領域の不純物濃度は中心部より高く、第1活性領域AAの不純物濃度は中心部と等しい。

【選択図】図6

Description

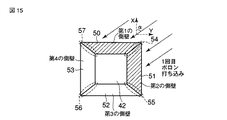

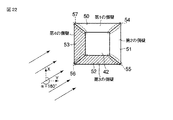

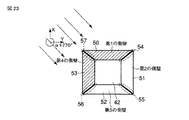

前記半導体基板中に形成され、第2MOSトランジスタが配置される第2活性領域と、前記第1活性領域の周囲の前記半導体基板中に形成され、側壁において前記第1活性領域が露出される第1トレンチと該第1トレンチ内を埋め込む絶縁膜とを備え、隣接する前記第1活性領域間を電気的に分離する第1素子分離領域と、前記第2活性領域の周囲の前記半導体基板中に形成され、側壁において前記第2活性領域が露出される第2トレンチと該第2トレンチ内を埋め込む絶縁膜とを備え、隣接する前記第2活性領域間を電気的に分離する第2素子分離領域とを具備し、前記半導体基板中において前記第2素子分離領域の側面部分における前記第2活性領域の不純物濃度は中心部より高く、前記第1素子分離領域の側面部における前記第1活性領域の不純物濃度は中心部と等しい。

この発明に第1の実施形態に係る半導体記憶装置及びその製造方法について図1を用いて説明する。図1は本実施形態に係るNAND型フラッシュメモリのブロック図である。

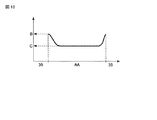

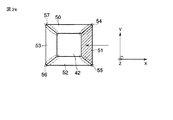

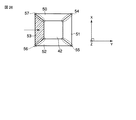

但し、S1は前述の通り溝44の幅であり、Hはゲート絶縁膜34とp型半導体基板10の界面から絶縁膜42表面までの高さである。例えば幅S1は10nm〜100nmとされ、HはS2の6倍程度の値(60nm〜600nm)とされる。従ってこの場合、チルト角θは10度となる。

(1)動作信頼性を向上出来る。

上記本効果つき、従来の半導体記憶装置及びその製造方法と比較しつつ、以下詳細に説明する。

次に、この発明の第2の実施形態に係る半導体記憶装置及びその製造方法について説明する。本実施形態は、上記第1の実施形態に示す図12(a)〜(c)の製造工程において、イオンの打ち込み回数及び回転角度αを変えたものである。

(3)p型半導体基板に対する接合耐圧の低下を防ぐことができる。

Claims (5)

- 半導体基板中に形成され、電荷蓄積層と制御ゲートとを含む積層ゲートを備えた第1MOSトランジスタが配置される第1活性領域と、

前記半導体基板中に形成され、第2MOSトランジスタが配置される第2活性領域と、

前記第1活性領域の周囲の前記半導体基板中に形成され、側壁において前記第1活性領域が露出される第1トレンチと該第1トレンチ内を埋め込む絶縁膜とを備え、隣接する前記第1活性領域間を電気的に分離する第1素子分離領域と、

前記第2活性領域の周囲の前記半導体基板中に形成され、側壁において前記第2活性領域が露出される第2トレンチと該第2トレンチ内を埋め込む絶縁膜とを備え、隣接する前記第2活性領域間を電気的に分離する第2素子分離領域とを具備し、

前記半導体基板中において前記第2素子分離領域の側面部分における前記第2活性領域の不純物濃度は中心部より高く、前記第1素子分離領域の側面部における前記第1活性領域の不純物濃度は中心部と等しい

ことを特徴とする半導体記憶装置。 - 前記第2活性領域の2つの側面の辺が互いに接する領域は、前記2つの側面と比べて不純物濃度が高いことを特徴とする請求項1記載の半導体記憶装置。

- 前記第1MOSトランジスタは、前記第1活性領域上に形成された第1ゲート絶縁膜と、

前記第1ゲート絶縁膜上に形成された前記積層ゲートとを備え、

前記第2MOSトランジスタは、前記第2活性領域上に形成された第2ゲート絶縁膜と、

前記第2ゲート絶縁膜上に形成されたゲート電極とを備え、

前記第2ゲート絶縁膜の膜厚は前記第1ゲート絶縁膜よりも厚い

ことを特徴とする請求項1または2記載の半導体記憶装置。 - 半導体基板上にあってメモリセルトランジスタを形成すべき第1領域と、前記メモリセルトランジスタを制御する周辺トランジスタを形成する第2領域上に、それぞれ第1ゲート絶縁膜及び第2ゲート絶縁膜を形成する工程と、

前記第1ゲート絶縁膜及び第2ゲート絶縁膜上に、それぞれ第1導電層を形成する工程と、

前記第1導電層上に、マスク材を形成する工程と、

前記第1領域内において前記マスク材、前記第1導電層、及び前記第1ゲート絶縁膜を貫通して前記半導体基板中に達する第1トレンチと、前記第2領域内において前記マスク材、前記第1導電層、及び前記第2ゲート絶縁膜を貫通して前記半導体基板中に達し第1の側壁及び前記第1の側壁と接する第2の側壁を形成し、前記第1トレンチの幅よりも広い幅を有する第2トレンチを形成する工程と、

前記半導体基板の主平面の法線に対して斜め方向から、かつ、前記第1の側壁の法線に対して前記第2側壁の方向に鋭角の角度で前記第1領域及び前記第2領域にイオン注入を行うことにより、不純物を注入する工程と

を具備することを特徴とする半導体記憶装置の製造方法。 - 前記第1トレンチの幅をS、前記半導体基板表面から前記マスク材の上面までの高さをHとした際、前記イオン注入は前記法線に対して、

θ≧tan−1(S/H)

の角度で行われる

ことを特徴とする請求項4記載の半導体記憶装置の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007333306A JP2009158622A (ja) | 2007-12-25 | 2007-12-25 | 半導体記憶装置及びその製造方法 |

| US12/338,417 US8159019B2 (en) | 2007-12-25 | 2008-12-18 | Semiconductor memory device with stacked gate including charge storage layer and control gate and method of manufacturing the same |

| US13/426,664 US8394689B2 (en) | 2007-12-25 | 2012-03-22 | Semiconductor memory device with stacked gate including charge storage layer and control gate and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007333306A JP2009158622A (ja) | 2007-12-25 | 2007-12-25 | 半導体記憶装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009158622A true JP2009158622A (ja) | 2009-07-16 |

| JP2009158622A5 JP2009158622A5 (ja) | 2011-06-16 |

Family

ID=40787564

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007333306A Pending JP2009158622A (ja) | 2007-12-25 | 2007-12-25 | 半導体記憶装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8159019B2 (ja) |

| JP (1) | JP2009158622A (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011003614A (ja) | 2009-06-16 | 2011-01-06 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2011100946A (ja) * | 2009-11-09 | 2011-05-19 | Toshiba Corp | 半導体記憶装置 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000340791A (ja) * | 1999-05-28 | 2000-12-08 | Nec Corp | 半導体装置の製造方法 |

| JP2003060073A (ja) * | 2001-08-10 | 2003-02-28 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2004349393A (ja) * | 2003-05-21 | 2004-12-09 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2007027622A (ja) * | 2005-07-21 | 2007-02-01 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH104137A (ja) | 1996-06-17 | 1998-01-06 | Matsushita Electron Corp | 半導体装置の製造方法 |

| US6835987B2 (en) | 2001-01-31 | 2004-12-28 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device in which selection gate transistors and memory cells have different structures |

| DE10131704A1 (de) * | 2001-06-29 | 2003-01-16 | Atmel Germany Gmbh | Verfahren zur Dotierung eines Halbleiterkörpers |

| US6855985B2 (en) * | 2002-09-29 | 2005-02-15 | Advanced Analogic Technologies, Inc. | Modular bipolar-CMOS-DMOS analog integrated circuit & power transistor technology |

| US7550355B2 (en) * | 2005-08-29 | 2009-06-23 | Toshiba America Electronic Components, Inc. | Low-leakage transistor and manufacturing method thereof |

| JP4959990B2 (ja) | 2006-03-01 | 2012-06-27 | 株式会社東芝 | 半導体装置 |

| TWI302355B (en) * | 2006-04-20 | 2008-10-21 | Promos Technologies Inc | Method of fabricating a recess channel array transistor |

| JP2011003614A (ja) | 2009-06-16 | 2011-01-06 | Toshiba Corp | 半導体記憶装置及びその製造方法 |

| JP2011100946A (ja) | 2009-11-09 | 2011-05-19 | Toshiba Corp | 半導体記憶装置 |

-

2007

- 2007-12-25 JP JP2007333306A patent/JP2009158622A/ja active Pending

-

2008

- 2008-12-18 US US12/338,417 patent/US8159019B2/en active Active

-

2012

- 2012-03-22 US US13/426,664 patent/US8394689B2/en active Active

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000340791A (ja) * | 1999-05-28 | 2000-12-08 | Nec Corp | 半導体装置の製造方法 |

| JP2003060073A (ja) * | 2001-08-10 | 2003-02-28 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2004349393A (ja) * | 2003-05-21 | 2004-12-09 | Renesas Technology Corp | 半導体装置の製造方法 |

| JP2007027622A (ja) * | 2005-07-21 | 2007-02-01 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20120178229A1 (en) | 2012-07-12 |

| US8159019B2 (en) | 2012-04-17 |

| US8394689B2 (en) | 2013-03-12 |

| US20090159961A1 (en) | 2009-06-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9412747B2 (en) | Semiconductor device and a method of manufacturing the same | |

| US8014204B2 (en) | Semiconductor device | |

| JP4764461B2 (ja) | 半導体装置 | |

| US9070743B2 (en) | Semiconductor memory and manufacturing method of the same | |

| JP2008130676A (ja) | 不揮発性半導体記憶装置 | |

| US8236679B2 (en) | Manufacturing method of semiconductor memory device using insulating film as charge storage layer | |

| JP2008098519A (ja) | 不揮発性半導体メモリ | |

| JP4843412B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2009054941A (ja) | 半導体装置及び半導体記憶装置 | |

| JP5458526B2 (ja) | 半導体装置及びその製造方法 | |

| US20150060995A1 (en) | Nonvolatile semiconductor storage device | |

| JP2009081202A (ja) | 半導体記憶装置及びその製造方法 | |

| US8394689B2 (en) | Semiconductor memory device with stacked gate including charge storage layer and control gate and method of manufacturing the same | |

| US8377814B2 (en) | Semiconductor memory device and manufacturing method thereof | |

| JP2008166415A (ja) | 半導体装置及びその製造方法 | |

| JP2010212506A (ja) | 半導体記憶装置及びその製造方法 | |

| JP2014022394A (ja) | 不揮発性半導体記憶装置 | |

| US20150263105A1 (en) | Nonvolatile semiconductor storage device | |

| JP2010147491A (ja) | 半導体記憶装置の製造方法 | |

| JP2007287736A (ja) | 不揮発性半導体記憶装置 | |

| JP2013004675A (ja) | 半導体記憶装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100224 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110428 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20120529 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120706 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120710 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130108 |