JP2008269727A - 昇圧回路、半導体記憶装置およびその駆動方法 - Google Patents

昇圧回路、半導体記憶装置およびその駆動方法 Download PDFInfo

- Publication number

- JP2008269727A JP2008269727A JP2007113820A JP2007113820A JP2008269727A JP 2008269727 A JP2008269727 A JP 2008269727A JP 2007113820 A JP2007113820 A JP 2007113820A JP 2007113820 A JP2007113820 A JP 2007113820A JP 2008269727 A JP2008269727 A JP 2008269727A

- Authority

- JP

- Japan

- Prior art keywords

- booster

- potential

- circuit

- booster circuit

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/30—Power supply circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/145—Applications of charge pumps; Boosted voltage circuits; Clamp circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Read Only Memory (AREA)

Abstract

【解決手段】半導体記憶装置は、コントロールゲートを有し、情報を保持するメモリセルが行列状に複数個配置されてなるメモリセルアレイと、行方向に延び、それぞれが1つの行のメモリセルのコントロールゲートに接続された複数のワード線と、列方向に延び、メモリセルのソースまたはドレインに接続された複数のビット線と、複数のワード線から任意のワード線を選択するローデコーダと、複数のビット線から任意のビット線を選択するカラムデコーダと、電源電圧よりも高い電圧を生成する昇圧回路と、ローデコーダと昇圧回路との接続経路上に設けられた第1のスイッチとを備えている。

【選択図】図4

Description

図1(a)は、本発明の第1の実施形態に係る半導体記憶装置において、メモリセル100を示す図であり、(b)〜(d)は、各動作モードでメモリセル100に印加する電位を生成するために必要となる昇圧回路とレギュレータを示す図である。メモリセル100はMONOSなどのフラッシュメモリであり、各動作モードで各部に印加される電位は例えば従来例と同じく表1に示す電位となっている。

図1(b)〜(d)では、各動作モードを実現する回路構成例を示したが、本発明の第2の実施形態として、面積増加をともなわずに図1(b)〜(d)に示す動作モードを実現できる半導体記憶装置について説明する。

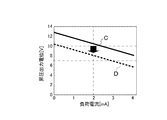

ここで、ILは正側電源ノード528のリーク電流であり、tPは時刻t2〜t3の書込み時間であり、Csは正側電源ノード528の寄生容量を意味するものとする。

図1および図4で説明したように、書込み動作時に選択されたメモリセルのコントロールゲートへ与える10V程度の電位と、チャネル電流を供給するために選択されたメモリセルのドレインへ与える4〜7V程度の電位とを一つの昇圧回路で供給するメモリ構成とする場合での、効率的な電圧発生を可能とする昇圧回路構成例を以下に説明する。

図7は、本発明の第4の実施形態に係る昇圧回路の構成例を示す図である。本実施形態の昇圧回路700は、動作状態に応じて構成を切り替えることにより電源回路のサイズ縮小を実現する昇圧回路である。

図8は、本発明の第5の実施形態に係る半導体記憶装置の書込み時の駆動方法を示す波形図である。本実施形態の方法によれば、ページモード書込みなどのように、同一ワード線に接続されたメモリセルを順次選択して、連続的な書込みを行なう場合においても、コントロールゲートに印加する10V程度の電位を維持することが可能となる。半導体記憶装置の回路構成は図4に示すとおりとする。

102 正昇圧回路

104 ビット線電位発生回路

105 読み出しバイアストランジスタ

106 ゲート電位レギュレータ

108 ドレイン電位レギュレータ

110 負電位発生回路

112、410、708、710 スイッチ

114 容量

402 メモリセルアレイ

406 カラム選択ゲート

407 ソース・ドレイン選択ゲート

408 センスアンプ

412 書込み回路

414 ローデコーダ

416 カラムデコーダ

418 ソース・ドレインデコーダ

422、424 マルチプレクサ

426 コントロール回路

428 検知回路

430 検知信号

500 選択回路

502 デコード部

504 レベルシフタ部

506 ドライバ部

508 NAND回路

510 インバータ

512、514 Nチャネル型トランジスタ

516、518 Pチャネル型トランジスタ

520、522 トランジスタ

524 Nウェル

526 負側電源ノード

528 正側電源ノード

600 昇圧回路

602、702 昇圧ユニット

604、704、706 昇圧ブロック

608 電荷転送トランジスタ

610 トランジスタ

612 ポンピング容量

614 昇圧容量

700 昇圧回路

BL0、BL1、BL2、BL3 ビット線

SD0、SD1 選択信号

WL0、WL2 ワード線

YG0〜YG3 選択信号

Claims (16)

- コントロールゲートを有し、情報を保持するメモリセルが行列状に複数個配置されてなるメモリセルアレイと、

行方向に延び、それぞれが1つの行の前記メモリセルの前記コントロールゲートに接続された複数のワード線と、

列方向に延び、前記メモリセルのソースまたはドレインに接続された複数のビット線と、

前記複数のワード線から任意のワード線を選択するローデコーダと、

前記複数のビット線から任意のビット線を選択するカラムデコーダと、

電源電圧よりも高い電圧を生成する昇圧回路と、

前記ローデコーダと前記昇圧回路との接続経路上に設けられた第1のスイッチとを備えている半導体記憶装置。 - 前記昇圧回路の出力が供給され、入力された書込みデータに応じて前記カラムデコーダにより選択された任意のビット線に書込み電位を出力する書込み回路と、

前記書込み回路および前記第1のスイッチの動作タイミングを制御するコントロール回路とをさらに備えていることを特徴とする請求項1に記載の半導体記憶装置。 - 前記昇圧回路と前記書込み回路の間に電圧レギュレータをさらに備えたことを特徴とする請求項2に記載の半導体記憶装置。

- 前記第1のスイッチは、前記メモリセルへのデータ書込み時に所定の期間導通して前記ローデコーダ内の電源ノードを充電した後、非導通となることを特徴とする請求項2または3に記載の半導体記憶装置。

- 前記コントロール回路は、前記第1のスイッチが非導通となった後に昇圧された前記昇圧回路からの出力を選択された前記ワード線に供給するように制御信号を出力することを特徴とする請求項4に記載の半導体記憶装置。

- 前記ローデコーダに負電位を供給する負電位発生回路をさらに備えていることを特徴とする請求項4または5に記載の半導体記憶装置。

- 前記半導体記憶装置は、前記ローデコーダに供給される電位を検知し、検知結果を前記コントロール回路に出力する検知回路をさらに備え、

前記コントロール回路は、前記メモリセルへのデータ書込み時に前記第1のスイッチが非導通状態となった後に前記ローデコーダに供給される電位が所定値以下になった場合、前記第1のスイッチを導通させ、前記ローデコーダ内の電源ノードを充電させることを特徴とする請求項4〜6のうちいずれか1つに記載の半導体記憶装置。 - 前記昇圧回路は、入力電圧を昇圧し、第1の昇圧容量を有する第1の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第1の昇圧ブロックと、入力電圧を昇圧し、第2の昇圧容量を有する第2の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第2の昇圧ブロックとを有していることを特徴とする請求項2〜7のうちいずれか1つに記載の半導体記憶装置。

- 前記第2の昇圧容量は前記第1の昇圧容量よりも容量が小さく、前記第1の昇圧ブロックの出力部は前記第2の昇圧ブロックの入力部に接続され、

前記第2の昇圧ブロックの出力電位は書込み動作時に前記ローデコーダに供給され、前記第1の昇圧ブロックの出力電位は前記書込み回路を介して選択された前記ビット線に供給されることを特徴とする請求項8に記載の半導体記憶装置。 - 前記昇圧回路は、前記第1の昇圧ブロックと前記第2の昇圧ブロックとを直列に接続させる第2のスイッチと、前記第1の昇圧ブロックの出力部と前記第2の昇圧ブロックの出力部との間に設けられた第3のスイッチとをさらに有しており、前記第2のスイッチおよび前記第3のスイッチにより前記第2の昇圧ブロックは、前記第1の昇圧ブロックと直列に接続するか並列に接続するかが切り替えられることを特徴とする請求項8に記載の半導体記憶装置。

- コントロールゲートを有し、情報を保持するメモリセルが行列状に複数個配置されてなるメモリセルアレイと、

行方向に延び、それぞれが1つの行の前記メモリセルの前記コントロールゲートに接続された複数のワード線と、

列方向に延び、前記メモリセルのソースまたはドレインに接続された複数のビット線と、

前記複数のワード線から任意のワード線を選択するローデコーダと、

前記複数のビット線から任意のビット線を選択するカラムデコーダと、

入力電圧を昇圧し、第1の昇圧容量を有する第1の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第1の昇圧ブロックと、入力電圧を昇圧し、第2の昇圧容量を有する第2の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第2の昇圧ブロックとを有しており、電源電圧よりも高い第1の電圧と前記第1の電圧より低い第2の電圧とを生成する昇圧回路と、

前記ローデコーダと前記昇圧回路との接続経路上に設けられたスイッチとを備えている半導体記憶装置。 - 入力電圧を昇圧し、第1の昇圧容量を有する第1の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第1の昇圧ブロックと、

入力電圧を昇圧し、第2の昇圧容量を有する第2の昇圧ユニットが直列に複数段接続されてなり、出力部を有する第2の昇圧ブロックとを備え、

電源電圧よりも高い第1の電圧と前記第1の電圧より低い第2の電圧とを生成する昇圧回路。 - 前記第2の昇圧容量は前記第1の昇圧容量よりも容量が小さく、前記第1の昇圧ブロックの出力部は前記第2の昇圧ブロックの入力部に接続され、

前記第2の電圧は前記第1の昇圧ブロックから出力され、

前記第1の電圧は前記第2の昇圧ブロックから出力されることを特徴とする請求項12に記載の昇圧回路。 - 前記昇圧回路は、前記第1の昇圧ブロックと前記第2の昇圧ブロックとを直列に接続させる第2のスイッチと、前記第1の昇圧ブロックの出力部と前記第2の昇圧ブロックの出力部との間に設けられた第3のスイッチとをさらに有しており、前記第2のスイッチおよび前記第3のスイッチにより前記第2の昇圧ブロックは、前記第1の昇圧ブロックと直列に接続するか並列に接続するかが切り替えられることを特徴とする請求項12に記載の昇圧回路。

- コントロールゲートを有し、情報を保持するメモリセルが行列状に複数個配置されてなるメモリセルアレイと、行方向に延び、それぞれが1つの行の前記メモリセルの前記コントロールゲートに接続された複数のワード線と、列方向に延び、前記メモリセルのソースまたはドレインに接続された複数のビット線と、前記複数のワード線から任意のワード線を選択するローデコーダと、前記複数のビット線から任意のビット線を選択するカラムデコーダと、電源電圧よりも高い電圧を生成する昇圧回路と、前記ローデコーダと前記昇圧回路との接続経路上に設けられたスイッチとを備えている半導体記憶装置の駆動方法であって、

前記メモリセルへのデータ書込み時に、前記スイッチを導通状態にして前記ローデコーダ内の電源ノードを充電するステップ(a)と、

前記ステップ(a)の後、前記スイッチを非導通にして昇圧された前記昇圧回路からの出力を選択された前記ワード線に供給してデータ書込みを行うステップ(b)とを備えている半導体記憶装置の駆動方法。 - 前記半導体記憶装置は、

前記昇圧回路の出力が供給され、入力された書込みデータに応じて前記カラムデコーダにより選択された任意のビット線に書込み電位を出力する書込み回路と、

前記書込み回路および前記第1のスイッチの動作タイミングを制御するコントロール回路と

前記ローデコーダに供給される電位を検知し、検知結果を前記コントロール回路に出力する検知回路とをさらに備え、

前記ステップ(b)は、

前記ローデコーダに選択された前記メモリセルにデータを順次連続的に書き込むステップ(b1)と、

前記ローデコーダに供給される電位が所定値以下になった場合、前記スイッチを導通させ、前記ローデコーダ内の電源ノードを充電させてから前記メモリセルにデータを書込む

ステップ(b2)とを有していることを特徴とする請求項15に記載の半導体記憶装置の駆動方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007113820A JP2008269727A (ja) | 2007-04-24 | 2007-04-24 | 昇圧回路、半導体記憶装置およびその駆動方法 |

| US12/108,948 US7706194B2 (en) | 2007-04-24 | 2008-04-24 | Charge pump circuit, semiconductor memory device, and method for driving the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007113820A JP2008269727A (ja) | 2007-04-24 | 2007-04-24 | 昇圧回路、半導体記憶装置およびその駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008269727A true JP2008269727A (ja) | 2008-11-06 |

| JP2008269727A5 JP2008269727A5 (ja) | 2010-01-28 |

Family

ID=39886792

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007113820A Pending JP2008269727A (ja) | 2007-04-24 | 2007-04-24 | 昇圧回路、半導体記憶装置およびその駆動方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7706194B2 (ja) |

| JP (1) | JP2008269727A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010182845A (ja) * | 2009-02-05 | 2010-08-19 | Seiko Epson Corp | 不揮発性メモリー装置 |

| US8379464B2 (en) | 2010-03-31 | 2013-02-19 | Fujitsu Semiconductor Limited | Semiconductor integrated circuit device |

| JP2013192338A (ja) * | 2012-03-13 | 2013-09-26 | Renesas Electronics Corp | 半導体装置 |

| JP5661099B2 (ja) * | 2010-03-10 | 2015-01-28 | パナソニック株式会社 | メモリセルのドレイン電圧用及びゲート電圧用のレギュレータを共有したフラッシュメモリ |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8619489B2 (en) | 2010-04-30 | 2013-12-31 | Stmicroelectronics S.R.L. | Driving circuit for memory device |

| US8559229B2 (en) * | 2010-09-30 | 2013-10-15 | Samsung Electronics Co., Ltd. | Flash memory device and wordline voltage generating method thereof |

| KR101682189B1 (ko) * | 2011-01-04 | 2016-12-05 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 워드라인 전압 발생 방법 |

| US9025391B2 (en) * | 2012-11-27 | 2015-05-05 | Infineon Technologies Ag | Circuit arrangement and method for operating a circuit arrangement |

| KR102053944B1 (ko) * | 2013-02-21 | 2019-12-11 | 삼성전자주식회사 | 불 휘발성 메모리 장치 및 그것을 포함하는 메모리 시스템 |

| JP2014211941A (ja) * | 2014-07-03 | 2014-11-13 | スパンションエルエルシー | 半導体集積回路装置 |

| US9779819B1 (en) | 2016-06-24 | 2017-10-03 | Micron Technology, Inc. | Connecting memory cells to a data line sequentially while applying a program voltage to the memory cells |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07111095A (ja) * | 1993-08-17 | 1995-04-25 | Toshiba Corp | 昇圧回路及び昇圧回路を備えた不揮発性半導体記憶装置 |

| JP2000149582A (ja) * | 1998-09-08 | 2000-05-30 | Toshiba Corp | 昇圧回路,電圧発生回路及び半導体メモリ |

| JP2001338493A (ja) * | 2000-05-25 | 2001-12-07 | Toshiba Corp | 半導体装置 |

| JP2003272396A (ja) * | 2001-12-27 | 2003-09-26 | Toshiba Corp | 半導体装置 |

| JP2004348806A (ja) * | 2003-03-26 | 2004-12-09 | Sharp Corp | 半導体記憶装置およびそれを備えた携帯電子機器 |

| JP2005176590A (ja) * | 2003-12-11 | 2005-06-30 | Samsung Electronics Co Ltd | マルチレベル高電圧発生装置 |

| JP2005267734A (ja) * | 2004-03-18 | 2005-09-29 | Renesas Technology Corp | 昇圧回路及びそれを用いた不揮発性メモリ |

| WO2005112039A1 (en) * | 2004-05-10 | 2005-11-24 | Sandisk Corporation | Latched programming of memory and method |

| JP2007102991A (ja) * | 2005-10-05 | 2007-04-19 | Samsung Electronics Co Ltd | 半導体メモリ装置およびそのリダンダンシ駆動方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5375083A (en) * | 1993-02-04 | 1994-12-20 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor integrated circuit including a substrate having a memory cell array surrounded by a well structure |

| US6222779B1 (en) * | 1998-04-24 | 2001-04-24 | Kabushiki Kaisha Toshiba | Semiconductor storage device with automatic write/erase function |

| EP0953984B1 (en) * | 1998-04-30 | 2003-07-02 | STMicroelectronics S.r.l. | Method for saving data in the event of unwanted interruptions in the programming cycle of a nonvolatile memory, and a nonvolatile memory |

| US6842383B2 (en) | 2003-01-30 | 2005-01-11 | Saifun Semiconductors Ltd. | Method and circuit for operating a memory cell using a single charge pump |

| ITVA20060011A1 (it) * | 2006-02-22 | 2007-08-23 | St Microelectronics Srl | Dispositivo di memoria e relativo metodo di controllo |

-

2007

- 2007-04-24 JP JP2007113820A patent/JP2008269727A/ja active Pending

-

2008

- 2008-04-24 US US12/108,948 patent/US7706194B2/en active Active

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07111095A (ja) * | 1993-08-17 | 1995-04-25 | Toshiba Corp | 昇圧回路及び昇圧回路を備えた不揮発性半導体記憶装置 |

| JP2000149582A (ja) * | 1998-09-08 | 2000-05-30 | Toshiba Corp | 昇圧回路,電圧発生回路及び半導体メモリ |

| JP2001338493A (ja) * | 2000-05-25 | 2001-12-07 | Toshiba Corp | 半導体装置 |

| JP2003272396A (ja) * | 2001-12-27 | 2003-09-26 | Toshiba Corp | 半導体装置 |

| JP2004348806A (ja) * | 2003-03-26 | 2004-12-09 | Sharp Corp | 半導体記憶装置およびそれを備えた携帯電子機器 |

| JP2005176590A (ja) * | 2003-12-11 | 2005-06-30 | Samsung Electronics Co Ltd | マルチレベル高電圧発生装置 |

| JP2005267734A (ja) * | 2004-03-18 | 2005-09-29 | Renesas Technology Corp | 昇圧回路及びそれを用いた不揮発性メモリ |

| WO2005112039A1 (en) * | 2004-05-10 | 2005-11-24 | Sandisk Corporation | Latched programming of memory and method |

| JP2007102991A (ja) * | 2005-10-05 | 2007-04-19 | Samsung Electronics Co Ltd | 半導体メモリ装置およびそのリダンダンシ駆動方法 |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010182845A (ja) * | 2009-02-05 | 2010-08-19 | Seiko Epson Corp | 不揮発性メモリー装置 |

| JP5661099B2 (ja) * | 2010-03-10 | 2015-01-28 | パナソニック株式会社 | メモリセルのドレイン電圧用及びゲート電圧用のレギュレータを共有したフラッシュメモリ |

| US8379464B2 (en) | 2010-03-31 | 2013-02-19 | Fujitsu Semiconductor Limited | Semiconductor integrated circuit device |

| JP2013192338A (ja) * | 2012-03-13 | 2013-09-26 | Renesas Electronics Corp | 半導体装置 |

| US9201439B2 (en) | 2012-03-13 | 2015-12-01 | Renesas Electronics Corporation | Semiconductor device |

| US9614439B2 (en) | 2012-03-13 | 2017-04-04 | Renesas Electronics Corporation | Semiconductor device |

| US10192594B2 (en) | 2012-03-13 | 2019-01-29 | Renesas Electronics Corporation | Semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US20080266968A1 (en) | 2008-10-30 |

| US7706194B2 (en) | 2010-04-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3913952B2 (ja) | 半導体記憶装置 | |

| JP2008269727A (ja) | 昇圧回路、半導体記憶装置およびその駆動方法 | |

| CN1866544B (zh) | 非易失性半导体存储装置 | |

| CN107527654B (zh) | 非易失性半导体存储装置及其字线的驱动方法 | |

| US8994440B2 (en) | Voltage select circuit and intergrated circuit including the same | |

| US8233328B2 (en) | Nonvolatile semiconductor memory | |

| US6456541B2 (en) | Booster circuit for raising voltage by sequentially transferring charges from input terminals of booster units to output terminals thereof in response to clock signals having different phases | |

| US6243292B1 (en) | Nonvolatile semiconductor memory device capable of reducing memory array area | |

| US6480057B2 (en) | Charge pump circuit allowing efficient electric charge transfer | |

| JP2010073246A (ja) | 不揮発性半導体記憶装置 | |

| US10083755B2 (en) | Discharge circuit and semiconductor memory device | |

| JPH07169282A (ja) | 半導体不揮発性記憶装置 | |

| US9865358B2 (en) | Flash memory device and erase method thereof capable of reducing power consumption | |

| US7649775B2 (en) | Flash memory device applying erase voltage | |

| US7362614B2 (en) | Non-volatile semiconductor storage apparatus | |

| US8483004B2 (en) | Semiconductor device with transistor storing data by change in level of threshold voltage | |

| US6738292B2 (en) | Nonvolatile semiconductor storage device | |

| US20100232233A1 (en) | Nonvolatile semiconductor memory device | |

| JP3935592B2 (ja) | 内部電位発生回路 | |

| JP2000030473A (ja) | 不揮発性半導体記憶装置 | |

| JP4284614B2 (ja) | 強誘電体メモリ装置 | |

| JP5183677B2 (ja) | 半導体記憶装置 | |

| JPH11238391A (ja) | 半導体回路 | |

| JP3392438B2 (ja) | 不揮発性半導体記憶装置 | |

| JP6744893B2 (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091207 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091207 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120124 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120220 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120228 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120703 |