JP2008103548A - 多層プリント配線板及びその製造方法 - Google Patents

多層プリント配線板及びその製造方法 Download PDFInfo

- Publication number

- JP2008103548A JP2008103548A JP2006285140A JP2006285140A JP2008103548A JP 2008103548 A JP2008103548 A JP 2008103548A JP 2006285140 A JP2006285140 A JP 2006285140A JP 2006285140 A JP2006285140 A JP 2006285140A JP 2008103548 A JP2008103548 A JP 2008103548A

- Authority

- JP

- Japan

- Prior art keywords

- conductive layer

- via hole

- wiring board

- printed wiring

- multilayer printed

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

- H05K3/4038—Through-connections; Vertical interconnect access [VIA] connections

- H05K3/4053—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques

- H05K3/4069—Through-connections; Vertical interconnect access [VIA] connections by thick-film techniques for via connections in organic insulating substrates

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/46—Manufacturing multilayer circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K1/00—Printed circuits

- H05K1/02—Details

- H05K1/11—Printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/40—Forming printed elements for providing electric connections to or between printed circuits

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2201/00—Indexing scheme relating to printed circuits covered by H05K1/00

- H05K2201/03—Conductive materials

- H05K2201/0332—Structure of the conductor

- H05K2201/0388—Other aspects of conductors

- H05K2201/0394—Conductor crossing over a hole in the substrate or a gap between two separate substrate parts

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K2203/00—Indexing scheme relating to apparatus or processes for manufacturing printed circuits covered by H05K3/00

- H05K2203/14—Related to the order of processing steps

- H05K2203/1453—Applying the circuit pattern before another process, e.g. before filling of vias with conductive paste, before making printed resistors

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05K—PRINTED CIRCUITS; CASINGS OR CONSTRUCTIONAL DETAILS OF ELECTRIC APPARATUS; MANUFACTURE OF ASSEMBLAGES OF ELECTRICAL COMPONENTS

- H05K3/00—Apparatus or processes for manufacturing printed circuits

- H05K3/22—Secondary treatment of printed circuits

- H05K3/28—Applying non-metallic protective coatings

- H05K3/281—Applying non-metallic protective coatings by means of a preformed insulating foil

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Printing Elements For Providing Electric Connections Between Printed Circuits (AREA)

Abstract

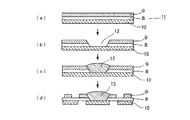

【解決手段】基材、前記基材の一方の表面上に設けられた第一の導電層、及び前記基材の他方の表面上に設けられた第二の導電層を有する両面基板を準備する工程、前記第一の導電層及び前記第二の導電層を選択的に除去して配線形成する工程、前記基材を選択的に除去することにより、前記第二の導電層を底面とし、前記基材及び前記第一の導電層を壁面とするブラインドビアホールを形成する工程、前記ブラインドビアホールの外周である第一の導電層表面と前記ブラインドビアホールの底面とに連続するように導電性ペーストを塗布する工程、を有し、前記第一の導電層と前記第二の導電層を電気的に接続することを特徴とする多層プリント配線板の製造方法。

【選択図】 図4

Description

ポリイミドフィルムの両面に、接着剤を用いずに銅箔を貼り合わせた両面銅貼基板(ポリイミドフィルム厚み:25μm、銅箔厚み:12μm)を準備し、両面の銅箔をエッチング加工して配線形成した。さらにYAGレーザにより有底のブラインドビアホール(開口径100μm)を開け、ウエットブラスト処理を施した。ブラインドビアホールは1296個形成した。

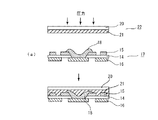

導電性ペーストを塗布した両面基板の両面に、カバーレイフィルム(厚み20μmの接着剤層が片面に積層された厚み12μmのポリイミドフィルム)を積層し、真空プレスを行ったこと以外は実施例1と同様の条件で、1296個のビアホールがデイジーチェーン構造で接続された多層プリント配線板2を作製した。

導電性ペーストを塗布した両面基板の両面に、カバーレイフィルム(厚み20μmの接着剤層が片面に積層された厚み12μmのポリイミドフィルム)を積層し、導電性ペーストの塗布径を100μmとした以外は、真空プレスを行ったこと以外は実施例1と同様の条件で、1296個のビアホールがデイジーチェーン構造で接続された多層プリント配線板2を作製した。

導電性ペーストを塗布した両面基板の両面に、カバーレイフィルム(厚み20μmの接着剤層が片面に積層された厚み12μmのポリイミドフィルム)を積層し、導電性ペーストの塗布径を350μmとした以外は、真空プレスを行ったこと以外は実施例1と同様の条件で、1296個のビアホールがデイジーチェーン構造で接続された多層プリント配線板2を作製した。

得られた多層プリント配線板について、接続抵抗を測定した。測定はデイジーチェーンの両端から、4端子法により、抵抗を測定することにより実施した。なお、抵抗値は1296個のビアホール内に充填された導電性ペーストの抵抗、導電層の抵抗、及び導電性ペーストと導電層の接触抵抗の合計と考えられる。

さらに、多層プリント配線板をピーク温度260℃のリフロー炉に6回通した後接続抵抗を測定し、抵抗上昇率を求めた。

2 配線層

3 片面銅箔貼り基材

4 剥離用フィルム

5 ブラインドビアホール

6 導電性ペースト

7 金属フィルム

8 基材

9 第一の金属層

10 第二の金属層

11 基板

12 孔

13 金属

14 基材

15 第一の導電層

16 第二の導電層

17 両面基板

18 ブラインドビアホール

19 導電性ペースト

20 絶縁性基材

21 接着層

22 絶縁層(カバーレイフィルム)

Claims (6)

- 基材、前記基材の一方の表面上に設けられた第一の導電層、及び前記基材の他方の表面上に設けられた第二の導電層を有する両面基板を準備する工程、

前記第一の導電層及び前記第二の導電層を選択的に除去して配線形成する工程、

前記基材を選択的に除去することにより、前記第二の導電層を底面とし、前記基材及び前記第一の導電層を壁面とするブラインドビアホールを形成する工程、

前記ブラインドビアホールの外周である第一の導電層表面と前記ブラインドビアホールの底面とに連続するように導電性ペーストを塗布する工程、

を有し、前記第一の導電層と前記第二の導電層を電気的に接続することを特徴とする、多層プリント配線板の製造方法。 - 前記ブラインドビアホールの径が30μm以上200μm以下であることを特徴とする、請求項1に記載の多層プリント配線板の製造方法。

- 前記導電性ペーストの塗布は、前記ブラインドビアホールの外周全体を被覆するように塗布することを特徴とする、請求項1又は2に記載の多層プリント配線板の製造方法。

- 前記導電性ペーストの塗布径をAとし、前記ブラインドビアホールの径をBとしたとき、AとBの差が20μm以上200μm以下であることを特徴とする、請求項3に記載の多層プリント配線板の製造方法。

- さらに、前記両面基板の少なくとも一方の表面を被覆する絶縁層を積層する工程を含み、

前記導電性ペーストを塗布する工程の後、前記絶縁層を積層し、その後プレスし、前記絶縁層を前記両面配線基板に接着させることを特徴とする、請求項1〜4のいずれかに記載の多層プリント配線板の製造方法。 - 基材、前記基材の一方の表面上に設けられた第一の導電層、及び前記基材の他方の表面上に設けられた第二の導電層を有し、前記第一の導電層と前記第二の導電層が導電性ペーストの硬化物で電気的に接続されている多層プリント配線板であって、

前記第二の導電層を底面とし、前記基材及び前記第一の導電層を壁面とするブラインドビアホールを有し、

前記ブラインドビアホールの外周である第一の導電層表面と、前記ブラインドビアホールの底面とに連続するように導電性ペーストの硬化物が設けられていることを特徴とする、多層プリント配線板。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006285140A JP2008103548A (ja) | 2006-10-19 | 2006-10-19 | 多層プリント配線板及びその製造方法 |

| CNA2007800389997A CN101530014A (zh) | 2006-10-19 | 2007-10-12 | 多层印刷线路板及其制造方法 |

| KR1020097006805A KR20090068227A (ko) | 2006-10-19 | 2007-10-12 | 다층 프린트 배선판 및 그 제조 방법 |

| PCT/JP2007/069976 WO2008047718A1 (fr) | 2006-10-19 | 2007-10-12 | Tableau de connexions imprimées multicouche et procédé de fabrication de celui-ci |

| TW096138824A TWI406619B (zh) | 2006-10-19 | 2007-10-17 | 多層印刷配線板及其製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006285140A JP2008103548A (ja) | 2006-10-19 | 2006-10-19 | 多層プリント配線板及びその製造方法 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011031759A Division JP5429646B2 (ja) | 2011-02-17 | 2011-02-17 | 両面プリント配線板の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008103548A true JP2008103548A (ja) | 2008-05-01 |

| JP2008103548A5 JP2008103548A5 (ja) | 2010-09-02 |

Family

ID=39313949

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006285140A Pending JP2008103548A (ja) | 2006-10-19 | 2006-10-19 | 多層プリント配線板及びその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| JP (1) | JP2008103548A (ja) |

| KR (1) | KR20090068227A (ja) |

| CN (1) | CN101530014A (ja) |

| TW (1) | TWI406619B (ja) |

| WO (1) | WO2008047718A1 (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010205909A (ja) * | 2009-03-03 | 2010-09-16 | Sumitomo Electric Ind Ltd | 多層プリント配線板およびその製造方法 |

| WO2012011165A1 (ja) * | 2010-07-20 | 2012-01-26 | 住友電気工業株式会社 | 多層プリント配線板およびその製造方法 |

| CN103002673A (zh) * | 2012-12-21 | 2013-03-27 | 景旺电子科技(龙川)有限公司 | 一种铝基和线路层导通板的制作方法 |

| WO2013183692A1 (ja) * | 2012-06-08 | 2013-12-12 | 住友電気工業株式会社 | フレキシブルプリント配線板およびフレキシブルプリント配線板の製造方法 |

| CN105307405A (zh) * | 2014-05-29 | 2016-02-03 | 景硕科技股份有限公司 | 利用聚亚酰胺蚀刻的线路板制作方法 |

| WO2016106428A1 (en) * | 2014-12-23 | 2016-06-30 | Sanmina Corporation | Hole plug for thin laminate |

| US20160219703A1 (en) * | 2014-12-23 | 2016-07-28 | Sanmina Corporation | Hole plug for thin laminate |

| JP2020184610A (ja) * | 2019-04-26 | 2020-11-12 | 日亜化学工業株式会社 | 発光モジュールの製造方法及び発光モジュール |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101895416B1 (ko) * | 2011-12-23 | 2018-09-06 | 엘지이노텍 주식회사 | 인쇄회로기판 및 그 제조방법 |

| US10149392B2 (en) * | 2015-02-16 | 2018-12-04 | Nippo Mektron, Ltd. | Manufacturing method of flexible printed wiring board |

| CN109803490A (zh) * | 2019-03-13 | 2019-05-24 | 盐城维信电子有限公司 | 一种导电银浆连接上下层的双面柔性线路板及其制备方法 |

| CN114980521A (zh) * | 2022-06-06 | 2022-08-30 | 北京梦之墨科技有限公司 | 一种电子结构及其制作方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04199782A (ja) * | 1990-11-29 | 1992-07-20 | Sharp Corp | フレキシブル基板のスルーホール作成方法 |

| JP2001024323A (ja) * | 1999-07-12 | 2001-01-26 | Ibiden Co Ltd | 導電性ペーストの充填方法および多層プリント配線板用の片面回路基板の製造方法 |

| JP2002009441A (ja) * | 2000-06-22 | 2002-01-11 | Toshiba Corp | プリント配線板およびその製造方法 |

| JP2003031917A (ja) * | 2001-07-19 | 2003-01-31 | Fujikura Ltd | 回路基板の有底穴への導電性ペースト埋込構造 |

| JP2005353785A (ja) * | 2004-06-10 | 2005-12-22 | Mitsubishi Plastics Ind Ltd | 多層配線基板用導電性ペースト組成物 |

| JP2006287019A (ja) * | 2005-04-01 | 2006-10-19 | Hitachi Metals Ltd | 貫通電極付基板およびその製造方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7059044B2 (en) * | 2001-07-18 | 2006-06-13 | Matsushita Electric Industrial Co., Ltd. | Method and material for manufacturing circuit-formed substrate |

-

2006

- 2006-10-19 JP JP2006285140A patent/JP2008103548A/ja active Pending

-

2007

- 2007-10-12 CN CNA2007800389997A patent/CN101530014A/zh active Pending

- 2007-10-12 WO PCT/JP2007/069976 patent/WO2008047718A1/ja active Application Filing

- 2007-10-12 KR KR1020097006805A patent/KR20090068227A/ko not_active Application Discontinuation

- 2007-10-17 TW TW096138824A patent/TWI406619B/zh active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04199782A (ja) * | 1990-11-29 | 1992-07-20 | Sharp Corp | フレキシブル基板のスルーホール作成方法 |

| JP2001024323A (ja) * | 1999-07-12 | 2001-01-26 | Ibiden Co Ltd | 導電性ペーストの充填方法および多層プリント配線板用の片面回路基板の製造方法 |

| JP2002009441A (ja) * | 2000-06-22 | 2002-01-11 | Toshiba Corp | プリント配線板およびその製造方法 |

| JP2003031917A (ja) * | 2001-07-19 | 2003-01-31 | Fujikura Ltd | 回路基板の有底穴への導電性ペースト埋込構造 |

| JP2005353785A (ja) * | 2004-06-10 | 2005-12-22 | Mitsubishi Plastics Ind Ltd | 多層配線基板用導電性ペースト組成物 |

| JP2006287019A (ja) * | 2005-04-01 | 2006-10-19 | Hitachi Metals Ltd | 貫通電極付基板およびその製造方法 |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010205909A (ja) * | 2009-03-03 | 2010-09-16 | Sumitomo Electric Ind Ltd | 多層プリント配線板およびその製造方法 |

| WO2012011165A1 (ja) * | 2010-07-20 | 2012-01-26 | 住友電気工業株式会社 | 多層プリント配線板およびその製造方法 |

| WO2013183692A1 (ja) * | 2012-06-08 | 2013-12-12 | 住友電気工業株式会社 | フレキシブルプリント配線板およびフレキシブルプリント配線板の製造方法 |

| JP2013254910A (ja) * | 2012-06-08 | 2013-12-19 | Sumitomo Electric Ind Ltd | フレキシブルプリント配線板およびフレキシブルプリント配線板の製造方法 |

| CN103002673A (zh) * | 2012-12-21 | 2013-03-27 | 景旺电子科技(龙川)有限公司 | 一种铝基和线路层导通板的制作方法 |

| CN105307405A (zh) * | 2014-05-29 | 2016-02-03 | 景硕科技股份有限公司 | 利用聚亚酰胺蚀刻的线路板制作方法 |

| WO2016106428A1 (en) * | 2014-12-23 | 2016-06-30 | Sanmina Corporation | Hole plug for thin laminate |

| US20160219703A1 (en) * | 2014-12-23 | 2016-07-28 | Sanmina Corporation | Hole plug for thin laminate |

| KR20170098239A (ko) * | 2014-12-23 | 2017-08-29 | 산미나 코포레이션 | 얇은 라미네이트를 위한 홀 플러그 |

| US10237983B2 (en) * | 2014-12-23 | 2019-03-19 | Sanmina Corporation | Method for forming hole plug |

| US11246226B2 (en) | 2014-12-23 | 2022-02-08 | Sanmina Corporation | Laminate structures with hole plugs and methods of forming laminate structures with hole plugs |

| KR102594179B1 (ko) * | 2014-12-23 | 2023-10-26 | 산미나 코포레이션 | 얇은 라미네이트를 위한 홀 플러그 |

| JP2020184610A (ja) * | 2019-04-26 | 2020-11-12 | 日亜化学工業株式会社 | 発光モジュールの製造方法及び発光モジュール |

| JP7004921B2 (ja) | 2019-04-26 | 2022-01-21 | 日亜化学工業株式会社 | 発光モジュールの製造方法及び発光モジュール |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200829115A (en) | 2008-07-01 |

| TWI406619B (zh) | 2013-08-21 |

| WO2008047718A1 (fr) | 2008-04-24 |

| KR20090068227A (ko) | 2009-06-25 |

| CN101530014A (zh) | 2009-09-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2008103548A (ja) | 多層プリント配線板及びその製造方法 | |

| JP3729092B2 (ja) | 導電性接合材、多層型プリント配線基板及び多層型プリント配線基板の製造方法 | |

| WO2015040878A1 (ja) | 多層プリント配線板の製造方法、および多層プリント配線板 | |

| WO2001045478A1 (fr) | Carte a circuit imprime multicouche et procede de production | |

| US8541687B2 (en) | Coreless layer buildup structure | |

| JPH07263828A (ja) | プリント配線基板及びその製造方法 | |

| JP2003086944A (ja) | 多層配線回路基板の製造方法 | |

| US9351408B2 (en) | Coreless layer buildup structure with LGA and joining layer | |

| JP5077800B2 (ja) | 多層プリント配線板の製造方法 | |

| US8536459B2 (en) | Coreless layer buildup structure with LGA | |

| JP6058321B2 (ja) | 配線基板の製造方法 | |

| JP5429646B2 (ja) | 両面プリント配線板の製造方法 | |

| JP3705370B2 (ja) | 多層プリント配線板の製造方法 | |

| JPH09246728A (ja) | 多層配線板用材料、その製造方法およびそれを用いた多層配線板の製造方法 | |

| JP2008181915A (ja) | 多層プリント配線板及びその製造方法 | |

| JP2008181914A (ja) | 多層プリント配線板及びその製造方法 | |

| KR100733814B1 (ko) | 인쇄회로기판 제조방법 | |

| JP4200664B2 (ja) | 積層基板およびその製造方法 | |

| KR100754071B1 (ko) | 전층 ivh 공법의 인쇄회로기판의 제조방법 | |

| JPH1174640A (ja) | プリント配線基板の製造方法 | |

| JP2004296481A (ja) | 多層配線回路基板 | |

| JP3973654B2 (ja) | プリント配線基板の製造方法 | |

| JPH10261872A (ja) | 多層配線板用材料とその製造法並びにそれを用いた多層配線板の製造法 | |

| JP3855670B2 (ja) | 多層回路基板の製造方法 | |

| JP2006147748A (ja) | 多層プリント配線板およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081009 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100714 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100714 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100805 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100831 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101029 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101221 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110517 |