JP2006517054A - 銅裏面金属構造を備えるGaAs薄型ダイ - Google Patents

銅裏面金属構造を備えるGaAs薄型ダイ Download PDFInfo

- Publication number

- JP2006517054A JP2006517054A JP2004557131A JP2004557131A JP2006517054A JP 2006517054 A JP2006517054 A JP 2006517054A JP 2004557131 A JP2004557131 A JP 2004557131A JP 2004557131 A JP2004557131 A JP 2004557131A JP 2006517054 A JP2006517054 A JP 2006517054A

- Authority

- JP

- Japan

- Prior art keywords

- die

- gaas substrate

- backside metal

- copper

- gaas

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 229910001218 Gallium arsenide Inorganic materials 0.000 title claims abstract description 56

- 229910052751 metal Inorganic materials 0.000 title claims abstract description 39

- 239000002184 metal Substances 0.000 title claims abstract description 39

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 title claims abstract description 38

- 229910052802 copper Inorganic materials 0.000 title claims abstract description 38

- 239000010949 copper Substances 0.000 title claims abstract description 38

- 239000000758 substrate Substances 0.000 claims abstract description 39

- 239000004065 semiconductor Substances 0.000 claims abstract description 37

- 229910000679 solder Inorganic materials 0.000 claims abstract description 27

- 238000009792 diffusion process Methods 0.000 claims description 12

- 230000004888 barrier function Effects 0.000 claims description 10

- 238000007789 sealing Methods 0.000 claims description 2

- 238000010438 heat treatment Methods 0.000 claims 1

- 238000000034 method Methods 0.000 abstract description 18

- 238000004806 packaging method and process Methods 0.000 abstract description 6

- 230000017525 heat dissipation Effects 0.000 abstract description 5

- 238000005516 engineering process Methods 0.000 abstract description 3

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 46

- 238000007254 oxidation reaction Methods 0.000 description 12

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 11

- 229910052737 gold Inorganic materials 0.000 description 11

- 239000010931 gold Substances 0.000 description 11

- 230000003647 oxidation Effects 0.000 description 11

- 230000008569 process Effects 0.000 description 8

- 238000012858 packaging process Methods 0.000 description 4

- 230000002411 adverse Effects 0.000 description 3

- 239000000919 ceramic Substances 0.000 description 3

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- 238000007796 conventional method Methods 0.000 description 2

- 238000005304 joining Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 229920001187 thermosetting polymer Polymers 0.000 description 2

- 239000004593 Epoxy Substances 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000003064 anti-oxidating effect Effects 0.000 description 1

- 230000002180 anti-stress Effects 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000005520 cutting process Methods 0.000 description 1

- 238000006073 displacement reaction Methods 0.000 description 1

- 230000005496 eutectics Effects 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000002787 reinforcement Effects 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 238000012360 testing method Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/31—Structure, shape, material or disposition of the layer connectors after the connecting process

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/482—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of lead-in layers inseparably applied to the semiconductor body

- H01L23/4827—Materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L24/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L24/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04026—Bonding areas specifically adapted for layer connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/28—Structure, shape, material or disposition of the layer connectors prior to the connecting process

- H01L2224/29—Structure, shape, material or disposition of the layer connectors prior to the connecting process of an individual layer connector

- H01L2224/29001—Core members of the layer connector

- H01L2224/29099—Material

- H01L2224/291—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2224/29101—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of less than 400°C

- H01L2224/29111—Tin [Sn] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32245—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/44—Structure, shape, material or disposition of the wire connectors prior to the connecting process

- H01L2224/45—Structure, shape, material or disposition of the wire connectors prior to the connecting process of an individual wire connector

- H01L2224/45001—Core members of the connector

- H01L2224/45099—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/85—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a wire connector

- H01L2224/8538—Bonding interfaces outside the semiconductor or solid-state body

- H01L2224/85399—Material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01015—Phosphorus [P]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0105—Tin [Sn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01073—Tantalum [Ta]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/0132—Binary Alloys

- H01L2924/01322—Eutectic Alloys, i.e. obtained by a liquid transforming into two solid phases

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/049—Nitrides composed of metals from groups of the periodic table

- H01L2924/0495—5th Group

- H01L2924/04953—TaN

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/1026—Compound semiconductors

- H01L2924/1032—III-V

- H01L2924/10329—Gallium arsenide [GaAs]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/156—Material

- H01L2924/157—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

- H01L2924/15738—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof the principal constituent melting at a temperature of greater than or equal to 950 C and less than 1550 C

- H01L2924/15747—Copper [Cu] as principal constituent

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Ceramic Engineering (AREA)

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Die Bonding (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

- Electrodes Of Semiconductors (AREA)

Abstract

Description

で使用する「約」は通常、プロセス限界を表す。例えば、半導体基板を研磨する特定のプロセスを従来の方法により所望のプロセスパラメータの10%以内の精度で実施する場合、約1ミル(約25ミクロン)の公称厚さを有する基板は、0.9ミル(約22ミクロン)から1.1ミル(約28ミクロン)の実際の厚さを有することになる。

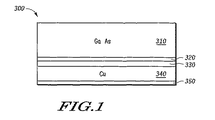

を補強するために約11〜15ミクロンの厚さを有する銅裏面金属層340を含むことができる。

し、耐酸化層540の材料(例えば金)は軟質はんだ層590の内部、及び軟質はんだ層590と銅裏面金属層530との境界に存在する。一旦、半導体ダイをフラッグ560に接合すると、フラッグ560は半導体ダイの極めて良好なヒートシンクとなる。

Claims (3)

- 50ミクロン未満の厚さを有するGaAs基板であって、能動表面及び裏面を有するGaAs基板と、

前記裏面上に重なる拡散バリア層と、

銅を含み、かつ前記拡散バリア上に重なる裏面金属層と、

GaAs基板を封止するプラスチック製のダイパッケージとを含む半導体装置。 - 約50ミクロン未満の厚さを有するGaAsダイを、軟質はんだを含むダイ接合面を有するリードフレームの上に載置する工程と、

軟質はんだを加熱して、前記ダイをリードフレームに接合する工程とを含む、方法。 - 約15ミクロン〜50ミクロンの範囲の厚さを有するGaAs基板と、

前記GaAs基板上に重なる拡散バリア層と、

銅を含み、かつ前記拡散バリア上に重なり、約11ミクロン〜15ミクロンの範囲の公称厚さを有する銅含有裏面金属層とを含む半導体装置。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/306,834 US6870243B2 (en) | 2002-11-27 | 2002-11-27 | Thin GaAs die with copper back-metal structure |

| PCT/US2003/030861 WO2004051733A1 (en) | 2002-11-27 | 2003-09-30 | Thin gaas die with copper back-metal structure |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006517054A true JP2006517054A (ja) | 2006-07-13 |

| JP2006517054A5 JP2006517054A5 (ja) | 2006-11-24 |

Family

ID=32325776

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004557131A Pending JP2006517054A (ja) | 2002-11-27 | 2003-09-30 | 銅裏面金属構造を備えるGaAs薄型ダイ |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US6870243B2 (ja) |

| JP (1) | JP2006517054A (ja) |

| KR (1) | KR20050085143A (ja) |

| CN (1) | CN1720610B (ja) |

| AU (1) | AU2003277129A1 (ja) |

| TW (1) | TWI339425B (ja) |

| WO (1) | WO2004051733A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008028295A (ja) * | 2006-07-25 | 2008-02-07 | Toyota Central Res & Dev Lab Inc | パワー半導体モジュール及びその製造方法 |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6870243B2 (en) * | 2002-11-27 | 2005-03-22 | Freescale Semiconductor, Inc. | Thin GaAs die with copper back-metal structure |

| US6833289B2 (en) * | 2003-05-12 | 2004-12-21 | Intel Corporation | Fluxless die-to-heat spreader bonding using thermal interface material |

| US20050085084A1 (en) * | 2003-10-16 | 2005-04-21 | Chang Edward Y. | Method of fabricating copper metallization on backside of gallium arsenide devices |

| US7221055B2 (en) * | 2005-05-23 | 2007-05-22 | Texas Instruments Incorporated | System and method for die attach using a backside heat spreader |

| US7923842B2 (en) * | 2006-03-16 | 2011-04-12 | Skyworks Solutions, Inc. | GaAs integrated circuit device and method of attaching same |

| CN100449740C (zh) * | 2006-06-19 | 2009-01-07 | 上海集成电路研发中心有限公司 | 降低半导体器件发热的散热方法、相应器件及其制造方法 |

| EP2089901A4 (en) * | 2006-11-09 | 2011-05-18 | Interplex Qlp Inc | MICROCIRCUIT HOUSING HAVING A DUCTILE LAYER |

| US20090108437A1 (en) * | 2007-10-29 | 2009-04-30 | M/A-Com, Inc. | Wafer scale integrated thermal heat spreader |

| JP5103245B2 (ja) * | 2008-03-31 | 2012-12-19 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US8987878B2 (en) | 2010-10-29 | 2015-03-24 | Alpha And Omega Semiconductor Incorporated | Substrateless power device packages |

| US8415805B2 (en) | 2010-12-17 | 2013-04-09 | Skyworks Solutions, Inc. | Etched wafers and methods of forming the same |

| JP2013098481A (ja) * | 2011-11-04 | 2013-05-20 | Sumitomo Electric Device Innovations Inc | 半導体装置 |

| US8900969B2 (en) | 2012-01-27 | 2014-12-02 | Skyworks Solutions, Inc. | Methods of stress balancing in gallium arsenide wafer processing |

| CN103377914A (zh) * | 2012-04-18 | 2013-10-30 | 稳懋半导体股份有限公司 | 半导体元件背面铜金属的改良结构及其加工方法 |

| US9093506B2 (en) | 2012-05-08 | 2015-07-28 | Skyworks Solutions, Inc. | Process for fabricating gallium arsenide devices with copper contact layer |

| JP2014099547A (ja) * | 2012-11-15 | 2014-05-29 | Mitsubishi Electric Corp | 電力半導体モジュールおよびその製造方法 |

| US9530719B2 (en) | 2014-06-13 | 2016-12-27 | Skyworks Solutions, Inc. | Direct die solder of gallium arsenide integrated circuit dies and methods of manufacturing gallium arsenide wafers |

| TWI660471B (zh) * | 2017-10-06 | 2019-05-21 | 財團法人工業技術研究院 | 晶片封裝 |

| US11133241B2 (en) | 2019-06-28 | 2021-09-28 | Stmicroelectronics, Inc. | Semiconductor package with a cavity in a die pad for reducing voids in the solder |

| CN112989744B (zh) * | 2021-02-08 | 2023-11-17 | 泰凌微电子(上海)股份有限公司 | 一种半导体芯片的封装设计方法以及装置 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04225536A (ja) * | 1990-12-27 | 1992-08-14 | Nikko Kyodo Co Ltd | 化合物半導体装置の製造方法 |

| JPH05243396A (ja) * | 1992-03-02 | 1993-09-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JPH06244320A (ja) * | 1993-02-16 | 1994-09-02 | Hitachi Ltd | 樹脂封止型半導体装置 |

| JPH09306932A (ja) * | 1996-05-17 | 1997-11-28 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP2003045875A (ja) * | 2001-07-30 | 2003-02-14 | Nec Kagobutsu Device Kk | 半導体装置およびその製造方法 |

Family Cites Families (25)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3755720A (en) * | 1972-09-25 | 1973-08-28 | Rca Corp | Glass encapsulated semiconductor device |

| US3942186A (en) * | 1973-10-09 | 1976-03-02 | Westinghouse Electric Corporation | High frequency, field-effect transistor |

| US4321099A (en) * | 1979-11-13 | 1982-03-23 | Nasa | Method of fabricating Schottky barrier solar cell |

| US4543442A (en) * | 1983-06-24 | 1985-09-24 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | GaAs Schottky barrier photo-responsive device and method of fabrication |

| JPS61174723A (ja) * | 1985-01-30 | 1986-08-06 | Mitsubishi Electric Corp | 半導体装置の製造方法 |

| US4929516A (en) | 1985-03-14 | 1990-05-29 | Olin Corporation | Semiconductor die attach system |

| US4872047A (en) * | 1986-11-07 | 1989-10-03 | Olin Corporation | Semiconductor die attach system |

| US4989117A (en) * | 1990-02-12 | 1991-01-29 | Rogers Corporation | Molded integrated circuit package incorporating thin decoupling capacitor |

| US5545289A (en) * | 1994-02-03 | 1996-08-13 | Applied Materials, Inc. | Passivating, stripping and corrosion inhibition of semiconductor substrates |

| IT1274129B (it) * | 1994-11-29 | 1997-07-15 | Soriani & Moser Manufacturers | Giostra di divertimento di tipo perfezionato |

| JP2757805B2 (ja) * | 1995-01-27 | 1998-05-25 | 日本電気株式会社 | 半導体装置 |

| US5528076A (en) * | 1995-02-01 | 1996-06-18 | Motorola, Inc. | Leadframe having metal impregnated silicon carbide mounting area |

| US5622305A (en) * | 1995-05-10 | 1997-04-22 | Lucent Technologies Inc. | Bonding scheme using group VB metallic layer |

| US6105865A (en) * | 1998-07-17 | 2000-08-22 | Hardesty; Laurence Daniel | Financial transaction system with retirement saving benefit |

| US6010966A (en) * | 1998-08-07 | 2000-01-04 | Applied Materials, Inc. | Hydrocarbon gases for anisotropic etching of metal-containing layers |

| JP3690171B2 (ja) * | 1999-03-16 | 2005-08-31 | 株式会社日立製作所 | 複合材料とその製造方法及び用途 |

| US6609106B1 (en) * | 1999-05-07 | 2003-08-19 | Steven C. Robertson | System and method for providing electronic multi-merchant gift registry services over a distributed network |

| US6211550B1 (en) * | 1999-06-24 | 2001-04-03 | Intersil Corporation | Backmetal drain terminal with low stress and thermal resistance |

| US6426289B1 (en) * | 2000-03-24 | 2002-07-30 | Micron Technology, Inc. | Method of fabricating a barrier layer associated with a conductor layer in damascene structures |

| TWI248384B (en) * | 2000-06-12 | 2006-02-01 | Hitachi Ltd | Electronic device |

| US6551852B2 (en) * | 2001-06-11 | 2003-04-22 | Micron Technology Inc. | Method of forming a recessed magnetic storage element |

| US6583500B1 (en) * | 2002-02-11 | 2003-06-24 | Texas Instruments Incorporated | Thin tin preplated semiconductor leadframes |

| US6787910B2 (en) * | 2002-07-23 | 2004-09-07 | National Chiao Tung University | Schottky structure in GaAs semiconductor device |

| US6870243B2 (en) * | 2002-11-27 | 2005-03-22 | Freescale Semiconductor, Inc. | Thin GaAs die with copper back-metal structure |

| US20040146138A1 (en) * | 2003-01-23 | 2004-07-29 | Motorola, Inc. | Large flat panel gallium arsenide arrays on silicon substrate for low dose X-ray digital imaging |

-

2002

- 2002-11-27 US US10/306,834 patent/US6870243B2/en not_active Expired - Lifetime

-

2003

- 2003-09-30 WO PCT/US2003/030861 patent/WO2004051733A1/en active Application Filing

- 2003-09-30 AU AU2003277129A patent/AU2003277129A1/en not_active Abandoned

- 2003-09-30 KR KR1020057009331A patent/KR20050085143A/ko not_active Application Discontinuation

- 2003-09-30 JP JP2004557131A patent/JP2006517054A/ja active Pending

- 2003-09-30 CN CN038254352A patent/CN1720610B/zh not_active Expired - Fee Related

- 2003-11-27 TW TW092133454A patent/TWI339425B/zh not_active IP Right Cessation

-

2005

- 2005-02-03 US US11/050,079 patent/US7092890B2/en not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04225536A (ja) * | 1990-12-27 | 1992-08-14 | Nikko Kyodo Co Ltd | 化合物半導体装置の製造方法 |

| JPH05243396A (ja) * | 1992-03-02 | 1993-09-21 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JPH06244320A (ja) * | 1993-02-16 | 1994-09-02 | Hitachi Ltd | 樹脂封止型半導体装置 |

| JPH09306932A (ja) * | 1996-05-17 | 1997-11-28 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

| JP2003045875A (ja) * | 2001-07-30 | 2003-02-14 | Nec Kagobutsu Device Kk | 半導体装置およびその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008028295A (ja) * | 2006-07-25 | 2008-02-07 | Toyota Central Res & Dev Lab Inc | パワー半導体モジュール及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20050127480A1 (en) | 2005-06-16 |

| US20040099932A1 (en) | 2004-05-27 |

| TW200416970A (en) | 2004-09-01 |

| CN1720610A (zh) | 2006-01-11 |

| US6870243B2 (en) | 2005-03-22 |

| AU2003277129A1 (en) | 2004-06-23 |

| KR20050085143A (ko) | 2005-08-29 |

| TWI339425B (en) | 2011-03-21 |

| US7092890B2 (en) | 2006-08-15 |

| CN1720610B (zh) | 2010-10-13 |

| WO2004051733A1 (en) | 2004-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7092890B2 (en) | Method for manufacturing thin GaAs die with copper-back metal structures | |

| KR970010678B1 (ko) | 리드 프레임 및 이를 이용한 반도체 패키지 | |

| US6846704B2 (en) | Semiconductor package and method for manufacturing the same | |

| US6590281B2 (en) | Crack-preventive semiconductor package | |

| US5646829A (en) | Resin sealing type semiconductor device having fixed inner leads | |

| US20090189261A1 (en) | Ultra-Thin Semiconductor Package | |

| US8945992B2 (en) | Power device package comprising metal tab die attach paddle (DAP) and method of fabricating the package | |

| US7030496B2 (en) | Semiconductor device having aluminum and metal electrodes and method for manufacturing the same | |

| JP2003133508A (ja) | 半導体装置 | |

| US10707158B2 (en) | Package with vertical interconnect between carrier and clip | |

| JP2018085480A (ja) | 半導体装置およびその製造方法 | |

| JP2008543049A (ja) | 半導体パッケージ及び同パッケージを形成する方法 | |

| US7811862B2 (en) | Thermally enhanced electronic package | |

| JP2000269166A (ja) | 集積回路チップの製造方法及び半導体装置 | |

| JPS59139636A (ja) | ボンデイング方法 | |

| JPH10270626A (ja) | 半導体装置およびその製造方法 | |

| JP2007242684A (ja) | 積層型半導体装置及びデバイスの積層方法 | |

| JPH0697349A (ja) | 樹脂封止型半導体装置とその製造方法 | |

| JP2003068959A (ja) | 半導体装置 | |

| KR102371636B1 (ko) | 양면 기판 반도체 제조 방법 | |

| US20240258372A1 (en) | Electronic component and package including stress release structure as lateral edge portion of semiconductor body | |

| JPH06209071A (ja) | 樹脂封止半導体装置およびその製造方法 | |

| KR0159985B1 (ko) | 반도체 패키지 히트싱크구조 | |

| JP3858857B2 (ja) | 半導体装置 | |

| JP3145892B2 (ja) | 樹脂封止型半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061002 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061002 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090513 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090526 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090826 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100608 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20101102 |