JP2005309767A - 電源制御装置、電子機器、及び携帯電話端末 - Google Patents

電源制御装置、電子機器、及び携帯電話端末 Download PDFInfo

- Publication number

- JP2005309767A JP2005309767A JP2004125833A JP2004125833A JP2005309767A JP 2005309767 A JP2005309767 A JP 2005309767A JP 2004125833 A JP2004125833 A JP 2004125833A JP 2004125833 A JP2004125833 A JP 2004125833A JP 2005309767 A JP2005309767 A JP 2005309767A

- Authority

- JP

- Japan

- Prior art keywords

- timing

- cpu

- power supply

- count value

- power

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- LPQOADBMXVRBNX-UHFFFAOYSA-N ac1ldcw0 Chemical compound Cl.C1CN(C)CCN1C1=C(F)C=C2C(=O)C(C(O)=O)=CN3CCSC1=C32 LPQOADBMXVRBNX-UHFFFAOYSA-N 0.000 claims abstract 3

- 238000001514 detection method Methods 0.000 claims description 22

- 238000004891 communication Methods 0.000 claims description 7

- 239000000470 constituent Substances 0.000 claims 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 abstract description 6

- 229910052782 aluminium Inorganic materials 0.000 abstract description 6

- 238000012937 correction Methods 0.000 abstract description 4

- 238000006243 chemical reaction Methods 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 3

- 230000003321 amplification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000003199 nucleic acid amplification method Methods 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000006870 function Effects 0.000 description 1

- 230000007274 generation of a signal involved in cell-cell signaling Effects 0.000 description 1

- 239000004973 liquid crystal related substance Substances 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 230000005055 memory storage Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 230000002265 prevention Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/24—Resetting means

Abstract

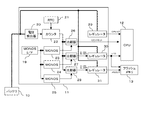

【解決手段】 電圧検出器20はバッテリ10からの電源供給の開始を検出する。カウンタ22は、電圧検出器20が電源供給の開始を検出すると、RTCのクロックのカウントを開始する。比較器26は、MONOS23が記憶しているカウント値Mと、カウンタ22のカウント値を比較し、それらが一致したときCPUリセット解除信号を出力する。比較器27は、MONOS24が記憶しているカウント値Nと、カウンタ22のカウント値を比較し、それらが一致したとき、CPU12のI/O電源を出力するレギュレータ30をパワーオンさせる。

【選択図】 図1

Description

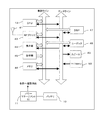

図1には、本発明の電源制御装置の一実施形態であるパワーマネージメントIC11と、バッテリ10の電源が当該パワーマネージメントIC11を介して供給されるCPU12及びフラッシュメモリ13とからなる構成例を示す。また、図2には、図1の各構成要素の動作タイミングチャートを示す。

本実施形態のパワーマネージメントIC11は、例えばPDA(Personal Digital Assistant)やディジタルカメラ、携帯型や据え置き型のテレビジョン受像機やパーソナルコンピュータ等の各種の電子機器や携帯電話端末等に適用可能である。

Claims (5)

- 電源供給の開始を検出する検出手段と、

上記検出手段にて電源供給の開始が検出された後に、CPUのリセット解除のタイミングとCPUへのI/O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、

上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、

上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを有する

ことを特徴とする電源制御装置。 - 請求項1記載の電源制御装置であって、

上記不揮発性記憶手段は、上記制御値として、CPUのリセット解除のタイミングを制御するための第1のカウント値と、CPUへのI/O電源供給のタイミングを制御するための第2のカウント値とを記憶しており、

上記タイミング決定手段は、上記検出手段にて電源供給の開始が検出された後に基準クロックのカウントを開始するカウント手段と、上記不揮発性記憶手段が記憶している第1のカウント値と上記カウント手段からのカウント値とを比較する第1の比較手段と、上記不揮発性記憶手段が記憶している第2のカウント値と上記カウント手段からのカウント値とを比較する第2の比較手段とを備え、上記不揮発性記憶手段の第1のカウント値とカウント手段のカウント値との一致を上記第1の比較手段が検出したタイミングを、上記CPUのリセット解除のタイミングに決定し、上記不揮発性記憶手段の第2のカウント値とカウント手段のカウント値との一致を上記第2の比較手段が検出したタイミングを、上記CPUへのI/O電源供給のタイミングに決定することを特徴とする電源制御装置。 - 請求項1又は請求項2記載の電源制御装置であって、

上記不揮発性記憶手段は、MONOS型のメモリであることを特徴とする電源制御装置。 - CPUと、

上記CPUにより動作制御がなされる他の各構成要素と、

電源供給の開始を検出する検出手段と、上記検出手段にて電源供給の開始が検出された後に、CPUのリセット解除のタイミングとCPUへのI/O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを備えた電源制御回路と有する

ことを特徴とする電子機器。 - 無線電話通信を行うための通信手段と、

少なくとも無線電話通信の制御を行うためのCPUと、

電源供給の開始を検出する検出手段と、上記検出手段にて電源供給の開始が検出された後に、CPUのリセット解除のタイミングとCPUへのI/O電源供給のタイミングのうち、少なくとも一方のタイミングを決定するタイミング決定手段と、上記決定手段にて決定されるタイミングを制御するための制御値を記憶する、書き換え可能な不揮発性記憶手段と、上記不揮発性記憶手段に記憶されている制御値を書き換えるための書換インターフェイス手段とを備えた電源制御回路とを有する

ことを特徴とする携帯電話端末。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004125833A JP2005309767A (ja) | 2004-04-21 | 2004-04-21 | 電源制御装置、電子機器、及び携帯電話端末 |

| US11/107,803 US7434077B2 (en) | 2004-04-21 | 2005-04-18 | Power control apparatus, electronic apparatus, and portable communications terminal |

| EP05008793A EP1589402A3 (en) | 2004-04-21 | 2005-04-21 | Power control apparatus, electronic apparatus, and portable communications terminal |

| KR1020050033239A KR20060047357A (ko) | 2004-04-21 | 2005-04-21 | 전원 제어 장치, 전자 기기, 및 휴대 통신 단말기 |

| CNB2005100656859A CN100339795C (zh) | 2004-04-21 | 2005-04-21 | 功率控制装置、电子装置及便携通信终端 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004125833A JP2005309767A (ja) | 2004-04-21 | 2004-04-21 | 電源制御装置、電子機器、及び携帯電話端末 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005309767A true JP2005309767A (ja) | 2005-11-04 |

| JP2005309767A5 JP2005309767A5 (ja) | 2005-12-15 |

Family

ID=34935557

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004125833A Pending JP2005309767A (ja) | 2004-04-21 | 2004-04-21 | 電源制御装置、電子機器、及び携帯電話端末 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7434077B2 (ja) |

| EP (1) | EP1589402A3 (ja) |

| JP (1) | JP2005309767A (ja) |

| KR (1) | KR20060047357A (ja) |

| CN (1) | CN100339795C (ja) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008220099A (ja) * | 2007-03-06 | 2008-09-18 | Canon Inc | 電源装置及びこれを有する機器 |

| JP2009251738A (ja) * | 2008-04-02 | 2009-10-29 | Ricoh Co Ltd | データ転送装置及びその初期化方法、並びに画像形成装置 |

| JP2013182603A (ja) * | 2012-03-05 | 2013-09-12 | Ricoh Co Ltd | 電源起動制御装置 |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7627353B2 (en) * | 2007-03-01 | 2009-12-01 | Aerielle Technologies, Inc. | Circuit and method for providing an auto-off capability for a wireless transmitter |

| US7337342B1 (en) * | 2005-04-28 | 2008-02-26 | Summit Microelectronics, Inc. | Power supply sequencing distributed among multiple devices with linked operation |

| US7542445B2 (en) * | 2006-06-14 | 2009-06-02 | Sony Ericsson Mobile Communications Ab | Method and system for maintaining autonomous system clock accuracy for a mobile radio terminal |

| JP2011114953A (ja) * | 2009-11-26 | 2011-06-09 | Seiko Instruments Inc | 通電時間計測回路及び電源装置 |

| WO2013147874A1 (en) * | 2012-03-30 | 2013-10-03 | Intel Corporation | Methods and apparatus for communicating available battery power |

| US11385692B2 (en) * | 2019-11-27 | 2022-07-12 | Chao-Cheng Yu | Remote automatic control power supply system |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS62210521A (ja) | 1986-03-11 | 1987-09-16 | Fujitsu Ltd | リセツト処理方式 |

| JPH087742B2 (ja) | 1990-05-28 | 1996-01-29 | ローム株式会社 | ワンチップマイクロコンピュータ |

| US5396639A (en) | 1991-09-16 | 1995-03-07 | Rohm Co., Ltd. | One chip microcomputer having programmable I/O terminals programmed according to data stored in nonvolatile memory |

| US5530879A (en) * | 1994-09-07 | 1996-06-25 | International Business Machines Corporation | Computer system having power management processor for switching power supply from one state to another responsive to a closure of a switch, a detected ring or an expiration of a timer |

| JP3355879B2 (ja) | 1995-08-01 | 2002-12-09 | 株式会社デンソー | 制御回路 |

| JPH10105296A (ja) * | 1996-09-30 | 1998-04-24 | Casio Comput Co Ltd | 電源制御装置 |

| KR100253076B1 (ko) * | 1997-05-02 | 2000-05-01 | 윤종용 | 순차 로직들을 위한 파워-온 리셋 회로(power-on reset circuit for sequential logics) |

| US6173436B1 (en) * | 1997-10-24 | 2001-01-09 | Vlsi Technology, Inc. | Standard cell power-on-reset circuit |

| US6154821A (en) * | 1998-03-10 | 2000-11-28 | Rambus Inc. | Method and apparatus for initializing dynamic random access memory (DRAM) devices by levelizing a read domain |

| FR2788145B1 (fr) * | 1999-01-05 | 2001-08-17 | St Microelectronics Sa | Procede d'initialisation d'un microcontroleur |

| US6946753B2 (en) | 2002-11-14 | 2005-09-20 | Fyre Storm, Inc. | Switching power converter controller with watchdog timer |

| US7302600B2 (en) * | 2004-06-30 | 2007-11-27 | Marvell International Ltd. | Power supply detection method, apparatus, and system |

-

2004

- 2004-04-21 JP JP2004125833A patent/JP2005309767A/ja active Pending

-

2005

- 2005-04-18 US US11/107,803 patent/US7434077B2/en not_active Expired - Fee Related

- 2005-04-21 KR KR1020050033239A patent/KR20060047357A/ko not_active Application Discontinuation

- 2005-04-21 EP EP05008793A patent/EP1589402A3/en not_active Withdrawn

- 2005-04-21 CN CNB2005100656859A patent/CN100339795C/zh not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008220099A (ja) * | 2007-03-06 | 2008-09-18 | Canon Inc | 電源装置及びこれを有する機器 |

| JP2009251738A (ja) * | 2008-04-02 | 2009-10-29 | Ricoh Co Ltd | データ転送装置及びその初期化方法、並びに画像形成装置 |

| JP2013182603A (ja) * | 2012-03-05 | 2013-09-12 | Ricoh Co Ltd | 電源起動制御装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| KR20060047357A (ko) | 2006-05-18 |

| US7434077B2 (en) | 2008-10-07 |

| CN1690922A (zh) | 2005-11-02 |

| EP1589402A3 (en) | 2007-07-04 |

| US20050240789A1 (en) | 2005-10-27 |

| CN100339795C (zh) | 2007-09-26 |

| EP1589402A2 (en) | 2005-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7434077B2 (en) | Power control apparatus, electronic apparatus, and portable communications terminal | |

| KR101941510B1 (ko) | 전력 소모를 줄이기 위한 방법 및 그 전자 장치 | |

| US8423815B2 (en) | Information processing device capable of performing a timer control operation | |

| JP5497196B2 (ja) | 電力制御装置、電力制御方法、電力制御プログラム及び記録媒体 | |

| JP2022068168A (ja) | 逆方向充電装置、逆方向充電電流調整方法及び装置 | |

| JP4793095B2 (ja) | 携帯電話機、該携帯電話機に用いられるカメラ動作休止方法及びカメラ動作休止制御プログラム | |

| EP2996253B1 (en) | Power control method of wireless terminal | |

| JP4166743B2 (ja) | 端末装置及びプログラム | |

| US20100016017A1 (en) | Power saving mobile phone and method thereof | |

| JP3922989B2 (ja) | 充電制御装置及び充電制御方法 | |

| KR100849326B1 (ko) | 피디에이 폰의 소비 전력 제어 장치 | |

| JP2006211259A (ja) | 携帯端末の受信帯域切替回路及びその方法 | |

| JP6177662B2 (ja) | 携帯端末 | |

| KR100605820B1 (ko) | 피디에이 기능과 폰 기능을 구비한 피디에이폰에서사용자데이터 보호방법 | |

| JP3733904B2 (ja) | 携帯電話装置及びその制御方法 | |

| JP2011038999A (ja) | 携帯端末機および携帯端末機の制御方法 | |

| KR100618426B1 (ko) | 모드 다이얼이 구비된 개인 휴대단말기 및 이의 키패드설정방법 | |

| KR101089194B1 (ko) | 알람시간전 배터리 잔량표시 이동통신단말기 | |

| KR100620745B1 (ko) | 배터리 잔류량 표시 기능을 가지는 전자기기 및 그 방법 | |

| JP5604134B2 (ja) | 携帯電子機器及び機器システム | |

| JP5200671B2 (ja) | 携帯端末装置 | |

| JP5067300B2 (ja) | 携帯端末装置 | |

| JP2009213312A (ja) | 携帯通信端末 | |

| JP2011114933A (ja) | 保護回路 | |

| KR100687611B1 (ko) | 슬립 모드 상태의 이동통신 단말기에서 절전 기능을제공하는 방법 및 이동통신 단말기 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050929 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050929 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20071011 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080326 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080716 |